数字信号处理器及方法

1.相关申请的交叉引用

2.本技术要求于2021年6月4日提交的法国专利申请第fr2105905号的优先权,该申请通过引用结合于此。

技术领域

3.本发明整体涉及专用于信号处理的电路领域,并且在具体实施例中涉及实现cordic算法的电子电路。

背景技术:

4.cordic(“坐标旋转数字计算机”)算法允许执行向量的旋转。

5.jack e volder在题为“cordic trigonometric computing technique”,ire transaction electronic computer ec-8:330-334(1959)的文章中描述了这样一种算法。

6.有专用于实现cordic算法的处理电路。

7.这种专用处理电路例如被配置为通过连续迭代来执行参考系中的变化,通常将向量的笛卡尔坐标转换为极坐标。在cordic算法的每次迭代过程中,向量经历一个单一特征的伪旋转。

8.专用处理电路通常被配置为对定点格式的数据进行操作,例如,向量的坐标被处理为定点值。

9.希望在数字信号处理器中实现cordic算法。

10.还希望在这样的数字信号处理器内加速cordic算法的处理。

技术实现要素:

11.根据一个方面,提出了一种数字信号处理器,包括处理级,例如用于以浮点格式接收向量的笛卡尔坐标的输入数据,并以浮点格式输出向量的极坐标。

12.处理级包括至少一个第一电子电路,第一电子电路被配置成通过时钟信号定时地来迭代地实现浮点格式的cordic算法。

13.因此,可以在信号处理器的处理级直接处理cordic算法。

14.此外,处理级允许处理以浮点格式表示的坐标。

15.以浮点格式实现cordic算法具体具有避免必须转换在处理级和以浮点操作的其他处理单元之间循环的数据(例如坐标)的格式的优点,这在处理时间方面特别有利。

16.根据一个实施例,处理级被配置为在实现cordic算法的期间,通过针对每一次除法减去对应于相应数据项的指数的幂的值,对以浮点格式表示的数据,执行2的整数次幂的除法。

17.因此,通过利用浮点格式,处理级允许比在其他专用电路中更快地处理cordic算法的迭代,这些专用电路使用传统的除法器来执行这些2的整数次幂的除法。

18.更具体地说,处理级允许通过只处理浮点数据项的指数位来执行算法的除法,这

有助于减少处理算法的每次迭代的关键路径。

19.可以节省硅空间。

20.根据一个变型,处理级被配置成实现每个时钟信号周期的cordic算法的一次迭代。

21.根据该变型的一个实施例,处理级包括计数器,计数器的当前值i对应于算法的当前迭代的秩,并且第一电子电路包括第一电路输入、第二电路输入和第三电路输入。

22.第一电路包括第一除法器模块,第一除法器模块具有连接到第二电路输入的输入和第一减法器,第一减法器用于从存在于第二电路输入的数据项的指数中减去计数器的当前值,第一除法器模块的输出传送存在于第二电路输入处的所述数据项除以2i。

23.第一电路还包括第二除法器模块,该第二除法器模块具有连接到第一电路输入的输入和第二减法器,第二减法器用于从存在于第一电路输入处的数据项的指数中减去计数器的当前值,第二除法器模块的输出传送存在于第一电路输入处的所述数据项除以2i。

24.第一电子电路包括第一加法器/减法器,具有连接到第一电路输入的第一输入,并具有连接到第一减法器的输出的第二输入。

25.第一电子电路还包括第二加法器/减法器,具有连接到第二电路输入的第一输入并具有连接到第二减法器的输出的第二输入。

26.第一电子电路还包括第三加法器/减法器,具有连接到第三电路输入的第一输入以及用于接收与计数器的当前值相关联的角间距(angular pitch)值的第二输入。

27.作为加法器或作为减法器的每个加法器/减法器的配置由存在于第二电路输入的数据项的符号限定。

28.因此,假定第一电路允许处理cordic算法的迭代,那么执行2的整数次幂除法的第一减法器模块和第二减法器模块允许减少第一电路的关键路径,并因此加速每个迭代的处理。

29.实际上,第一模块和第二模块允许通过简单地减去当前迭代的秩i的数据项的指数,来执行除以2i。

30.根据一个实施例,处理级还包括控制器,例如由状态机和/或由逻辑电路制成。

31.控制器被配置成在算法的第一迭代开始时,在第一电路输入传送表示向量横坐标的初始横坐标数据项,在第二电路输入传送表示向量纵坐标的初始纵坐标数据项,以及在第三电路输入传送初始角值。

32.控制器还被配置为在算法的每个后续新迭代时递增计数器。

33.控制器还被配置为在该第一电路的第三加法器/减法器的第二输入上传送与计数器的当前值相关联的角间距值。

34.因此,控制器允许初始化cordic算法的实现,并且具体是对于第一电路,管理当前迭代的秩的增加并提供相应的角间距值。

35.根据一个实施例,控制器被配置为在当前迭代结束时,在第一电路输入上传送第一加法器/减法器的输出值,在第二电路输入上传送第二加法器/减法器的输出值,在第三电路输入上传送第三加法器/减法器的输出值,以便每时钟信号周期处理一次迭代。

36.因此,控制器允许循环回cordic算法,使得输出值被反馈到第一电路的输入。

37.根据另一个特别有利的变型,处理级被配置成在不使用传统的除法器执行2的整

数次幂除法的同时,在每个时钟信号周期实现cordic算法的两次迭代,这允许显著减少处理级的输入和输出之间的关键路径。

38.因此,处理级允许更快地处理cordic算法。

39.根据该另一变型的一个实施例,处理级包括第一电子电路和第二电子电路,第二电子电路具有类似于第一电子电路的结构,连接在第一电子电路的下游。

40.第一电子电路旨在在时钟周期期间实现算法的当前迭代,第二电子电路旨在在该时钟周期期间实现算法的下一迭代。

41.因此,第一电路和第二电路的组合允许每个时钟信号周期进行两次cordic算法的迭代。

42.此外,第一电路具有类似于第二电路的结构,这允许简化处理级的设计。

43.第一电子电路有利地配置为实现偶数秩的迭代,并且第二电子电路有利地配置为实现奇数秩的迭代。

44.根据一个实施例,处理级包括计数器,计数器的当前值i对应于算法的偶数秩的当前迭代的秩的一半,并且第一电子电路包括:第一电路输入、第二电路输入、第三电路输入;第一除法器模块,具有连接到第二电路输入的输入和第一减法器,第一减法器用于从存在于第二电路输入的数据项的指数中减去值2i,第一除法器模块的输出传送存在于第二电路输入的除以2

2i

的数据项;第二除法器模块,具有连接到第一电路输入的输入和第二减法器,用于从存在于第一电路输入的数据项的指数中减去值2i,第二除法器模块的输出传送存在于第一电路输入的除以2

2i

的所述数据项;第一加法器/减法器,具有连接到第一电路输入的第一输入,连接到第一减法器的输出的第二输入;第二加法器/减法器,具有连接到第二电路输入的第一输入,连接到第二减法器的输出的第二输入;第三加法器/减法器,具有连接到第三电路输入的第一输入和用于接收与值2i相关联的角间距值的第二输入;以及作为加法器或作为减法器的每个加法器/减法器的配置由存在于第二电路输入的数据项的符号限定。

45.此外,根据一个实施例:第二电路的第一加法器/减法器的第一输入连接到第一电路的第一加法器/减法器的输出;第二电路的第二加法器/减法器的第一输入连接到第一电路的第二加法器/减法器的输出;第二电路的第三加法器/减法器的第一输入连接到第一电路的第三加法器/减法器的输出;第二电路的第一除法器模块的输入连接到第一电路的第二加法器/减法器的输出,以及第二电路的第一除法器模块的第一减法器被配置为从存在于电路的第一电路的第二加法器/减法器的输出处的数据项的指数中减去值2i 1,第二电路的第一除法器模块的输出传送存在于第一电路的第二加法器/减法器输出处的除以2

2i

1的所述数据项;第二电路的第二除法器模块的输入连接到第一电路的第一加法器/减法器的输出,并且第二电路的第二除法器模块的第二减法器被配置为从存在于电路的第一电路的第一加法器/减法器的输出处的数据项的指数中减去值2i 1,第二电路的第二除法器模块的输出传送存在于电路的第一电路的第一加法器/减法器的输出处的除以2

2i

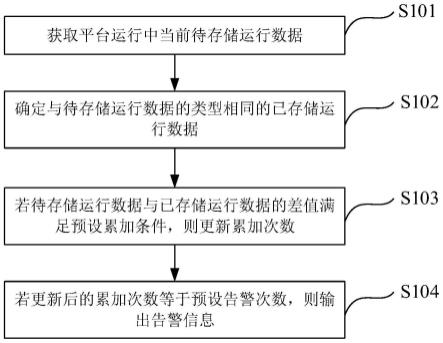

1的所述数据项;第三加法器/减法器的第二输入用于接收与值2i 1相关联的角间距值;并且该第二电路的每个加法器/减法器的加法器或减法器配置由存在于第一电路的第二加法器/减法器输出处的数据项的符号来限定。

46.因此,通过利用浮点格式来加速算法的处理,处理级允许每时钟周期处理cordic

算法的两个迭代中的每一个。

47.根据一个实施例,所述处理级还包括控制器,所述控制器被配置为:在例如秩0的迭代的所述算法的第一迭代开始时,在所述第一电路输入上传送表示所述向量的横坐标的初始横坐标数据项、在所述第二电路输入上传送表示所述向量的纵坐标的初始纵坐标数据项和在所述第三电路输入上传送初始角值;在算法的每次后续新迭代时递增计数器;在该第一电路的第三加法器/减法器的第二输入传送与值2i相关联的角间距值;并在第二电路的第三加法器/减法器的第二输入传送与值2i 1相关联的角间距值。

48.控制器还被配置为在偶数秩迭代之后的奇数秩迭代结束时,在第一电路输入上传送第二电路的第一加法器/减法器的输出值,在第二电路输入上传送第二电路的第二加法器/减法器的输出值,在第三电路输入上传送第二电路的第三加法器/减法器的输出值,以便在同一时钟信号周期期间处理所述偶数秩迭代和所述奇数秩迭代。

49.因此,控制器允许向第二电路提供与值2i 1相对应的角间距。

50.此外,控制器允许循环回cordic算法,使得第二电路的输出值在下一次迭代时反馈到第一电路的输入。

51.根据一个实施例,处理级还包括初始化电子电路,其被配置为根据向量的横坐标和纵坐标传送初始横坐标数据项、初始纵坐标数据项和初始角值。

52.根据一个实施例,初始化电路被配置为传送以下值分别作为初始横坐标数据项、初始纵坐标数据项和初始角值:在向量的横坐标为正的情况下,向量的横坐标、向量的纵坐标和零角值;在向量的横坐标和纵坐标为负的情况下,向量的纵坐标的相反值、向量的横坐标、以及等于的角值;并且在向量的横坐标是负的以及在向量的纵坐标是正的情况下,向量的纵坐标、向量的横坐标的相反值、以及等于的角值。

53.因此,初始化电子电路允许向第一电路提供cordic算法能够由此收敛的初始三元组(初始横坐标、初始纵坐标、初始角值)。

54.具体地,初始化电路允许处理器能够通过将平面的任何向量变换成其角值包括在与之间的初始向量,来处理该平面的任何向量。

55.根据另一个方面,提出了一种伺服系统,包括与电机连接的集成上述数字信号处理器的伺服环路。

56.因此,伺服系统受益于信号处理器的计算速度,这允许提高伺服回路的精度。

附图说明

57.在检查实施例和实施方式以及附图的详细描述时,将出现其他优点和特征,这些实施例和实施方式绝不是限制性的,其中:

58.图1示意性地示出了根据一些实施例的数字信号处理器的示例;

59.图2示意性地示出了根据一些实施例的数字信号处理器的处理级;

60.图3示出了根据一些实施例的处理级的除法器模块;

61.图4示意性地示出了根据一些其他实施例的数字信号处理器的处理级;

62.图5示意性地示出了根据一些其他实施例的数字信号处理器的初始化电路;以及

63.图6示意性地示出了根据一些实施例的集成数字信号处理器的系统。

具体实施方式

64.图1示意性地示出了适于在浮点数据上实现cordic算法迭代的数字信号处理器dsp的示例。

65.具体地,数字信号处理器dsp允许通过cordic算法将笛卡尔坐标转换为极坐标来执行坐标系的变化。

66.为此,数字信号处理器dsp包括专用于实现cordic算法并被配置为处理浮点数据的处理级et_float,以及用于产生旨在对处理级et_float进行时钟定时的时钟信号clk的时钟发生器gen_clk。

67.按照惯例,笛卡尔坐标包括横坐标abs和纵坐标ord,极坐标包括相对于原点测量的模数(modulus)mod和角度值ang。

68.处理级et_float被配置为接收浮点格式的向量的笛卡尔坐标abs、ord,并处理算法的连续迭代,以便以浮点格式提供向量的极坐标mod、ang。

69.为此,处理级et_float级包括至少一个能够处理浮点格式数据的第一电子电路c1。

70.电路c1被配置成逐个实现由时钟信号clk定时的cordic算法的迭代。

71.通常,算法的每次迭代包括2的整数次幂除法。

72.有利地,如下面将更详细地看到的,处理级et_float,具体是第一电路c1,被配置为通过不使用传统的除法器,而是通过简单地使要被除的浮点数据项的指数减去相应的2次幂的值,来执行2的整数次幂的除法。

73.图2示意性地示出在此包括第一电路c1的处理级et_float的示例。

74.处理级et_float还包括用于监视和管理每个迭代的控制器mc,用于指示算法的连续迭代的秩的计数器cpt,以及初始化电子电路ce_init,用于向第一电路提供在第一迭代期间要处理的初始数据。

75.计数器cpt旨在例如由时钟信号clk定时而递增,并在第一电路c1中的处理期间传送与迭代的秩相对应的当前值i。

76.处理级et_float包括适于存储cordic算法特性的一组角间距值αi的存储器mm。角间距值αi被预先计算并存储在存储器mm中。或者,存储器mm可以位于处理级et_float之外。

77.第一电路c1被配置为每个时钟信号周期clk实现cordic算法的单次迭代。

78.为此,第一电子电路c1包括三个块,第一块处理数据项x并传送数据项x

′

,第二块处理数据项y并传送数据项y

′

,第三块处理数据项α并传送数据项α

′

。

79.第一电子电路c1在第一块中包括第一除法器模块md1_c1和第一加法器/减法器a1_c1,在第二块中包括第二除法器模块md2_c1和第二加法器/减法器a2_c1,在第三块中包括第三加法器/减法器a3_c1。

80.第一电路c1被配置为使得在预定次数的迭代之后,数据项x'基本上等于极坐标系中向量的模,以及数据项α是极坐标系中向量与原点的角度的近似。

81.迭代次数最多可等于24次以获得最大精度,但可以减少到10次以获得较低精度。

82.关于第一电路c1的输入,它们包括用于接收数据项x的第一电路输入e1_c1、用于

接收数据项y的第二电路输入e2_c1、用于接收数据项α的第三电路输入e3_c1、以及用于接收角间距αi的第四电路输入e4_c1。

83.关于第一电路c1的输出,它们包括用于传送数据项x'的第一电路输出s1_c1、用于传送数据项y'的第二电路输出s2_c1和用于传送数据项α'的第三电路输出s3_c1。

84.关于第一电路c1的除法器模块,第一除法器模块md1_c1被配置为从数据项y的指数中减去计数器的当前值i,以传送值y/2i。

85.第一除法器模块md1_c1具有连接到第二电路输入e2_c1并用于接收数据项y的输入e1md1_c1,具有连接到计数器cpt并用于接收当前迭代的值i的输入e2md1_c1,以及具有连接到第一加法器/减法器a1_c1的第二输入e2a1_c1并用于传送除以2i的数据项y的输出smd1_c1。

86.图3更详细地说明了包括第一减法器s10_c1的第一除法器模块md1_c1。

87.数据项y通常以浮点格式包括形成指数y_exp的位和形成尾数y_mant的位。

88.第一除法器模块包括用于循环数据项y的位的数据总线。

89.总线被分成两个分支,第一分支被配置为在第一除法器模块md1_c1的第一输入e1md1_c1和输出smd1_c1之间循环数据项y的尾数y_mant的位,第二分支被配置为循环数据项y的指数y_exp到第一减法器s10-c1的位。

90.在这方面,第一减法器s10_c1包括连接到第一除法器模块md1_c1的第一输入e1md1_c1以接收数据项y的指数y_exp的第一输入。

91.第一减法器s10_c1还包括连接到第一除法器模块md1_c1的第二输入e2md1的第二输入,用于接收第一电路c1中的当前迭代的秩i的值。

92.第一减法器s10_c1被配置为从数据项y的指数中减去当前迭代的秩i的值。

93.第一减法器s10_c1中的减法如图3所示,通过隔离指数并通过对构成指数的位的量i执行无符号减法来实现。

94.第一减法器s1_c1还包括连接到第一除法器模块md1_c1的输出smd1_c1的输出,以传送减法的结果y_exp-i。

95.因此,第一除法器模块md1_c1的输出smd1_c1传送具有指数y_exp-i和尾数y_mant的数据项y/2i。

96.第二除法器模块md2_c1被配置为从数据项x的指数中减去计数器的当前值i,以传送数据项x/2i。

97.回到图1,第二除法器模块md2_c1具有输入e1md2_c1,连接到第一电路输入e1_c1并用于接收数据项x;输入e2md2_c1,连接到计数器cpt并用于接收当前迭代的值i;以及输出smd2_c1,连接到第二加法器/减法器a2_c1的第二输入e2a2_c1并用于传送除以2i的数据项x。

98.具体包括第二减法器的第二除法器模块md2_c1的结构和操作类似于关于图3描述的第一除法器模块md1_c1的结构和操作。

99.第一加法器/减法器a1_c1具有连接到第一电路输入e1_c1的第一输入e1a1_c1、连接到第一除法器模块md1_c1的输出的第二输入e2a1_c1、以及用于接收数据项y的最高有效位msb_y的第三输入e3a1_c1。

100.第一加法器/减法器a1_c1还具有输出sa1_c1,该输出sa1_c1连接到第一电路输出

s1_c1并用于传送数据项x',该数据项x'是用于当前迭代的第二块的输出值。

101.第二加法器/减法器a2_c1具有连接到第二电路输入e2_c1的第一输入e1a2_c1、具有连接到第二除法器模块md2_c1的输出的第二输入e2a2_c1,它也恰好是第二减法器的输出,并具有用于接收数据项y的最高有效位msb_y的第三输入e3a2_c1。

102.第二加法器/减法器a2_c1还具有输出sa2_c1,该输出sa2_c1连接到第二电路输出s2_c1并用于传送数据项y',该数据项y'是用于当前迭代的第二块的输出值。

103.第三加法器/减法器a3_c1具有连接到第三电路输入e3_c1的第一输入e1a3_c1、具有连接到第四电路输入e4_c1的第二输入e2a3_c1,用于接收与计数器cpt的当前值相关联的角间距值αi,并具有用于接收数据项y的最高有效位msb_y的第三输入e3a3_c1。

104.第三加法器/减法器a3_c1还具有输出sa3_c1,该输出sa3_c1连接到第三电路输出s3_c1并用于传送数据项α',该数据项α'是用于当前迭代的第三块的输出值。

105.作为加法器或作为减法器的每个加法器/减法器的配置取决于表示数据项y的符号的最高有效位msb_y。

106.例如,如果数据项y的最高有效位msb_y等于1,则相应的加法器/减法器执行减法,如果数据项y的最高有效位msb_y等于0,则该加法器/减法器执行加法。

107.因此,如果数据项y的符号为正,则第一加法器/减法器a1_c1被配置为将数据项y与除以2i的数据项x相加,或者如果数据项y的符号为负,则从除以2i的数据项x中减去数据项y。

108.第二加法器/减法器a2_c1被配置为,如果数据项y的符号为正,则从数据项y中减去除以2i的数据项x,或者如果数据项y的符号为负,则将数据项y与除以2i的数据项x相加。

109.第三加法器/减法器a3_c1被配置为,如果数据项y的符号为正,则将当前迭代的角间距值αi与数据项α相加,或者如果数据项y的符号为负,则从数据项α减去当前迭代的角间距值αi。

110.控制器mc被配置为控制初始化电路ce_init,以便在算法的第一次迭代开始时向第一电路c1传送初始数据三元组。

111.初始数据三元组包括在第一电路输入e1_c1上传送的表示向量横坐标的初始横坐标x_init、在第二电路输入e2_c1上传送的表示向量纵坐标的初始纵坐标数据项y_init,以及在第三电路输入e3_c1上传送的初始角值α_init。

112.在与图5相关的描述中,将更详细地讨论初始化电路ce_init和初始数据三元组x_init、y_init、α_init的获得。

113.控制器mc还被配置为在cordic算法的每次新迭代时控制计数器cpt的增量。

114.控制器mc还被配置为控制存储器mm中与计数器cpt的当前值相关联的角间距值αi的读取,并将该值传送到第三加法器/减法器a3_c1的第二输入e2a3_c1。

115.控制器mc被配置为在时钟信号的每个周期(除了最后一个)结束时,即在一个实施例中,在cordic算法的每个迭代(除了最后一个)之后,控制在每个块的输出处获得的值回送到其各自的输入。

116.具体地,控制器mc被配置为在当前迭代结束时,在第一电路输入e1_c1上回送第一加法器/减法器a1_c1的输出值x

′

、在第二电路输入e2_c1上回送第二加法器/减法器a2_c1的输出值y

′

、以及在第三电路输入e3_c1上回送第三加法器/减法器a3_c3的输出值α

′

。

117.在最后一次迭代结束时:数据项x'代表向量的模(前提是得到的幅值是初始向量的模乘以取决于迭代次数的常数k),数据α'表示其角度,并且数据y'为零或几乎为零。

118.更具体地说,对于24次迭代,k等于1.646760255,更一般地,k等于乘积(1 2-0

)

1/2

.(1 2-2

)

1/2

…

(1 2-(n-2)

)

1/2

。

119.图4示意性地示出处理级et_float被配置为每个时钟信号周期clk处理cordic算法的两次迭代的实施例。

120.这可以通过除法器模块的存在来实现,该除法器模块允许在不使用除法器的情况下执行2的整数次幂的除法,这减少了处理级的关键路径的长度。

121.这个尤其有利的实施例允许更快地确定向量的模量和角度。

122.例如,在40nm cmos技术中,时钟信号clk的频率可能在250mhz的范围内。

123.因此,处理级et_float包括如关于前述附图描述的第一电路c1和连接在第一电路c1下游的结构类似于第一电子电路c1的第二电路c2。如图4所示,在这种情况下,当电路包括以相同方式连接的相同元件时,电路具有类似的结构。

124.在时钟信号clk的周期期间,第一电子电路c1旨在执行cordic算法的偶数秩的当前迭代,并且第二电子电路c2旨在执行奇数秩的下一迭代,总是在相同的时钟信号周期clk期间。

125.更具体地,计数器cpt再次由控制器mc由时钟信号clk定时而递增,但其当前值i对应于算法的偶数秩的当前迭代的秩2i的一半。

126.因此,计数器cpt最终只对请求的迭代次数的一半进行计数。

127.第一迭代是秩为0的偶数迭代。

128.第一电路c1以关于图2和图3描述的方式实现秩2i的当前迭代,不同之处在于,第一电路在此包括从计数器cpt接收值i并在输入e2md1_c1和e2md2_c1处传送值2i的模块mdd1。

129.因此,模块md1_c1和md2_c1对分别存在于这两个模块的输入处的数据执行除以2

2i

。

130.一种实现在模块mdd1中执行的乘2的特别简单的方式,可以包括使用i位的初始字在i位总线上传送数字i,例如5位,并在模块mdd1的输出与输入e2md1_c1和e2md2_c1(i 1位的总线,例如6位)之间连接,以便向这些输入呈现i 1位的字,其最低有效位被强制为0,其i个其他位对应于表示数字i的初始字的i个位。

131.此外,控制器mc被配置为控制存储器mm中与值2i相关联的角间距值α

2i

的读取,并在第三加法器/减法器a3_c1的第二输入e2a3_c1上传送该值。

132.第二电路c2以与第一电路实现秩2i的迭代相同的方式实现秩2i 1的下一迭代,不同的是,这次由第二电路c2执行2

2i 1

的除法,而不是由第一电路c1执行2

2i

的除法。

133.第二电路c2的大多数元件与第一电路c1的元件相似,具体是从它们的结构和操作的观点来看。

134.因此,为了简洁起见,与第二电路c2的元件相关联的参考与和第一电路c1的元件相关联的参考相似。

135.第一电路和第二电路的参考之间的区别在于提及“_c1”指代第一电路,而提及“_c2”指代第二电路。

136.在结构上,如上所述,第二电路c2连接在第一电子电路c1的下游。

137.具体地,第二电路c2的第一电路输入e1_c2连接到第一电路c1的传送数据项x'的第一电路输出s1_c1。

138.第二电路c2的第二电路输入e2_c2连接到传送数据项y'的第一电路c1的第二输出s2_c1。

139.第二电路c2的电路e3_c2的第三电路输入连接到第一电路c1的传送数据α'的第三电路输出s3_c1。

140.与第一电路c1不同,此处第二电路包括模块mdd2,从计数器cpt接收值i,并将值2i 1传送到输入e2md1_c2和e2md2_c2。

141.因此,模块md1_c2和md2_c2对分别存在于这两个模块的输入的数据执行2

2i 1

的除法。

142.一种实现乘以2再增加1的特别简单的方式,在模块mdd2中执行,可以包括:在i位(例如5位)总线上使用i位的初始字传送数字i,以及在模块mdd2的输出与输入e2md1_c2和e2md2_c2(i 1位的总线,例如6位)之间连接,以便向这些输入呈现i 1位的字,其最低有效位被强制为1,并且其i个其他位对应于表示数字i的初始字的i个位。

143.因此,在第二电路c2的第一块中,第一除法器模块md1_c2被配置为从数据项y'的指数中减去值2i 1。

144.因此,该第二电路的第一除法器模块md1_c2的输出传送除以2

2i 1

的数据项y'。

145.然后,第二电路c2的第一加法器/减法器a1_c2的输出在秩2i 1的迭代时传送数据x”,该数据x”是第二电路c2的第一块的输出值。

146.并行地,关于第二电路c2的第二块,第二除法器模块md2_c2被配置为从数据项x'的指数中减去值2i 1。

147.因此,该第二电路的第二除法器模块md2_c2的输出传送除以2

2i 1

的数据项x'。

148.然后,第二电路c2的第二加法器/减法器a2_c2的输出在秩2i 1的迭代时传送数据项y”,该数据项y”是第二电路c2的第二块的输出值。

149.关于第二电路c2的第三块,第三加法器/减法器a3_c2的第二输入旨在接收与值2i 1相关联的角间距值α

2i 1

。

150.因此,第二电路c2的第三加法器a3_c2的输出在秩2i 1的迭代时传送数据α”,数据α”为第二电路c2的第三块的输出值。

151.在该实施例中,控制器mc被配置为控制与秩2i 1的迭代相关联的角间距值α

2i 1

的读数,以期其在第二电路c2的第四电路输入上传送。

152.此外,控制器mc随后被配置为在第一电路c1的块的相应输入上回送第二电路c2的块的输出。

153.具体地,控制器mc被配置为在秩2i 1的迭代结束时,在第一电路输入e1_c1上传送第二电路c2的第二块的输出值x”、在第二电路输入e2_c1上传送第二电路c2的第二块的输出值y”以及在第三电路输入e3_c1上传送第二电路的第三块的输出值α”。

154.在最后一次迭代结束时,数据x”表示向量的模(在常数k内),数据α”表示其角度,而数据y”为零或几乎为零。

155.图5示意性地说明了上面与图2和图4相关的初始化电子电路ce_init。

156.初始化电路被配置为根据向量的横坐标abs和纵坐标ord产生初始数据三元组,该三元组一方面包括由初始横坐标数据项x_init和初始纵坐标数据项y_init形成的初始向量,另一方面包括初始角值α_init。

157.由初始化电子电路ce_init产生的数据三元组由控制器mc控制(见图2和图4)。

158.关于初始向量,初始化电路ce_init被配置为如果旨在改变参考系的笛卡尔向量位于负横坐标的半平面中,则执行旋转。

159.通常,对于位于该半平面中的笛卡尔向量,cordic算法不收敛,因此有利的是生成位于正横坐标平面中的初始向量,该初始向量由笛卡尔向量的旋转或旋转获得,该旋转取决于纵坐标ord的符号是负还是正。

160.然后初始角值α_init总是根据纵坐标ord的符号分别取值或值这允许考虑笛卡尔向量的初始旋转。

161.反之,如果笛卡尔向量位于正横坐标的半平面内,则初始向量等于笛卡尔向量,并且初始角值α_init被设为零。

162.图6示意性地示出了伺服系统sys,它集成了监控单元uc,例如是微控制器,如stmicroelectronics公司销售的参考标号为stm32的微控制器,连接到电机m。

163.监控单元uc包括上述处理单元cpu和数字信号处理器dsp,以实现对电机m的伺服控制。

164.在电机m的伺服控制中,在参考系中将向量笛卡尔坐标变换为极坐标,例如是有利的。

165.具体地,如果这些参考系中的变化是快速实现的,例如,如果它们涉及电机的旋转,则更加有利,如果电机的旋转速度很大,则更是如此。

166.因此,伺服环路实现如上所述的数字信号处理器dsp是有利的,例如在图2或图4的实施例中,以便快速实现cordic算法的迭代。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。