1.本公开的实施例大体上涉及存储器子系统,且更具体地说,涉及顺序字线擦除验证方案。

背景技术:

2.一种存储器子系统可包含存储数据的一或多个存储器装置。存储器装置可为例如非易失性存储器装置和易失性存储器装置。通常,主机系统可利用存储器子系统以在存储器装置处存储数据并且从存储器装置检索数据。

技术实现要素:

3.在一方面中,本公开提供一种存储器装置,其包括:存储器阵列,其包括多个字线群组;以及控制逻辑,其以操作方式与存储器阵列耦合,以执行包括以下的操作:致使相对于多个字线群组中的每一字线群组顺序地执行第一擦除验证;识别经确定为未通过第一擦除验证的未通过字线群组的集合;以及致使相对于未通过字线群组的集合中的每一字线群组顺序地执行第二擦除验证。

4.在另一方面中,本公开提供一种方法,其包括:通过处理装置致使相对于与存储器装置相关联的多个字线群组中的每一字线群组顺序地执行第一擦除验证;通过处理装置致使相对于经确定为已通过第一擦除验证的通过字线群组的集合中的每一字线群组施加禁止偏置电压;以及通过处理装置致使相对于经确定为未通过第一擦除验证的未通过字线群组的集合中的每一字线群组顺序地执行第二擦除验证。

5.在又一方面中,本公开进一步提供一种包括指令的非暂时性计算机可读存储媒体,所述指令在由处理装置执行时致使处理装置执行包括以下的操作:致使在擦除偏置电压处的擦除脉冲施加到与存储器装置相关联的信道;在施加擦除脉冲之后,致使相对于字线群组的集合中的字线群组顺序地执行擦除验证;基于目标擦除阈值电压而确定字线群组的集合中的每一字线群组已通过擦除验证;以及响应于确定多个字线群组中的每一字线群组已通过擦除验证,致使擦除验证过程终止。

附图说明

6.根据下文给出的详细描述且根据本公开的各种实施例的附图将更充分地理解本公开。然而,图式不应视为将本公开限于具体实施例,而是仅用于解释和理解。

7.图1说明根据本公开的一些实施例的包含存储器子系统的实例计算系统。

8.图2为根据本公开的一些实施例的与存储器子系统的存储器子系统控制器通信的存储器装置的框图。

9.图3为根据本公开的一些实施例的执行顺序字线擦除验证方案的方法的流程图。

10.图4a-4c为说明根据本公开的一些实施例的在相应擦除循环期间顺序字线擦除验证方案的操作的图表。

11.图5a-5c为说明根据本公开的一些实施例的在相应擦除循环期间顺序字线擦除验证方案的操作的波形图。

12.图6为其中可操作本公开的实施例的实例计算机系统的框图。

具体实施方式

13.本公开的方面涉及顺序字线擦除验证方案。存储器子系统可为存储装置、存储器模块或存储装置与存储器模块的组合。下文结合图1描述存储装置和存储器模块的实例。通常,主机系统可利用包含一或多个例如存储数据的存储器装置的组件的存储器子系统。主机系统可提供将存储在存储器子系统处的数据且可请求将从存储器子系统检索的数据。

14.存储器子系统可包含高密度非易失性存储器装置,其中在没有电力被供应到存储器装置时需要数据的保持。非易失性存储器装置的一个实例为与非(nand)存储器装置。下文结合图1描述非易失性存储器装置的其它实例。非易失性存储器装置为一或多个裸片的封装。每一裸片可由一或多个平面组成。对于一些类型的非易失性存储器装置(例如,nand装置),每一平面由物理块集合组成。每一块由页集合组成。每一页由存储器单元(“单元”)集合组成。单元为存储信息的电子电路。取决于单元类型,单元可存储二进制信息的一或多个位,并且具有与正存储的位数目相关的各种逻辑状态。逻辑状态可表示为二进制值,例如“0”和“1”,或此类值的组合。

15.存储器装置可包含布置在二维或三维网格中的多个位。存储器单元蚀刻到列(下文也称为位线)和行(下文也称为字线)的阵列中的硅晶片上。字线可指存储器装置的存储器单元的一或多个行,所述一或多个行与一或多个位线一起使用以产生存储器单元中的每一个的地址。位线和字线的相交点构成存储器单元的地址。在下文中,块是指用于存储数据的存储器装置的单元,并且可包含存储器单元的群组、字线群组、字线或个别存储器单元。可将一或多个块分组在一起以形成存储器装置的平面,以便允许在每一平面上进行并发操作。存储器装置可包含执行两个或更多个存储器平面的并发存储器页存取的电路系统。举例来说,存储器装置可包含用于存储器装置的每一平面的相应存取线驱动器电路和电力电路以促进对包含不同页类型的两个或更多个存储器平面的页进行并发存取。

16.三维(3d)替换栅极存储器装置(例如,3d替换栅极nand)为具有使用字线堆叠的替换栅极结构的存储器装置。举例来说,3d替换栅极存储器装置可包含夹在层集合之间的字线、选择栅极等,所述层集合包含信道(例如,多晶硅信道)、隧道氧化物层、电荷阱(ct)层和电介质(例如,氧化物)层。3d替换栅极存储器装置可具有对应于源极侧的“顶部叠组”和对应于漏极侧的“底部叠组”。3d替换栅极存储器装置中的数据可存储为1位/单元(slc)、2位/单元(mlc)、3位/单元(tlc)等。对应于阈值电压分布的谷值之间的距离的读取窗口预算(rwb)容限可随着位/单元的数目增加而减小。

17.擦除验证为在擦除操作期间执行的过程。在一些装置,例如三维(3d)替换栅极存储器装置(例如,3d替换栅极nand)中,跨越字线或页的擦除速度可存在较大差异(例如,由于支柱的形状)。擦除速度的此类差异可导致跨越对应于浅擦除字线的存储器单元(“浅擦除存储器单元”)以及对应于深擦除字线的存储器单元(“深擦除存储器单元”)的较大擦除深度或应力变化,其中浅擦除存储器单元为比深擦除存储器单元更慢擦除的存储器单元。相较于平均存储器单元,在擦除操作之后,浅擦除存储器单元具有较高擦除阈值电压(v

t

),

而深擦除存储器单元具有较低擦除v

t

。在擦除操作之后,浅擦除存储器单元的擦除v

t

更接近擦除验证电平,而深擦除存储器单元具有低得多的擦除v

t

。举例来说,浅擦除存储器单元与深擦除存储器单元之间的擦除v

t

差可超过例如850mv。这意味着相较于浅擦除存储器单元,深擦除存储器单元可在编程/擦除循环期间经受更大的擦除应力,并且可因此导致快速降级和更差的数据保持。此外,可能难以更深地擦除浅擦除存储器单元,因为这样做可能会导致深擦除存储器单元的进一步降级。深擦除还可导致擦除v

t

加宽且可不利地影响读取窗口预算(rwb)。即使在擦除脉冲之后对所有存储器单元进行擦除检验,继续擦除或停止擦除的决策可取决于来自最浅擦除存储器单元的擦除v

t

,因为在接近验证通过条件时,来自最深擦除存储器单元的擦除v

t

可远离擦除验证目标。也就是说,仅有效地验证浅擦除存储器单元,而不控制深擦除存储器单元的擦除v

t

。因此,由于擦除验证可主要取决于浅擦除存储器单元的擦除后v

t

,因此擦除验证操作不可有效地验证所有存储器单元。

18.本公开的方面通过实施顺序字线擦除验证方案以改进擦除深度均一性来解决以上和其它缺陷。举例来说,本文中所描述的擦除验证方案可经实施以在3d替换栅极存储器装置(例如,3d替换栅极nand)的上下文内执行擦除验证。更具体地说,本文中所描述的顺序字线擦除验证方案可独立地验证和禁止存储器单元的字线群组(wg),因此其相应wg的所有存储器单元的擦除深度可取决于其相应擦除速度。为了禁止wg,本文中所描述的顺序字线擦除验证方案可将禁止偏置电压施加到具有在先前擦除循环期间已通过擦除验证的字线的wg。禁止偏置电压可根据所有wg的擦除速度而调整,因此减少wg跨越块、单元、晶片、温度和编程/擦除循环的擦除深度变化。因此,本文中所描述的顺序字线擦除验证方案可防止对较快擦除深存储器单元的过度擦除,同时实现对较慢擦除浅存储器单元的更深擦除,由此使得wg的存储器单元具有更接近的擦除v

t

。因此,可实现较小擦除v

t

差和改进的擦除深度均一性。

19.本公开的优点包含但不限于跨越字线的改进的应力变化、可跨越编程/擦除循环、温度等维持的跨越字线的改进的擦除深度均一性和/或减少的擦除深度变化,以及改进的可靠性(例如,在编程/擦除循环数据保持之后)。

20.图1说明根据本公开的一些实施例的包含存储器子系统110的实例计算系统100。存储器子系统110可包含媒体,例如一或多个易失性存储器装置(例如,存储器装置140)、一或多个非易失性存储器装置(例如,存储器装置130)或此类的组合。

21.存储器子系统110可为存储装置、存储器模块或存储装置与存储器模块的组合。存储装置的实例包含固态驱动器(ssd)、快闪驱动器、通用串行总线(usb)快闪驱动器、嵌入式多媒体控制器(emmc)驱动器、通用快闪存储(ufs)驱动器、安全数字(sd)卡和硬盘驱动器(hdd)。存储器模块的实例包含双列直插式存储器模块(dimm)、小外形dimm(so-dimm)和各种类型的非易失性双列直插式存储器模块(nvdimm)。

22.计算系统100可为计算装置,例如台式计算机、膝上型计算机、网络服务器、移动装置、运载工具(例如,飞机、无人机、火车、汽车或其它运输工具)、支持物联网(iot)的装置、嵌入式计算机(例如,包含在运载工具、工业设备或联网商业装置中的嵌入式计算机),或包含存储器和处理装置的此类计算装置。

23.计算系统100可包含耦合到一或多个存储器子系统110的主机系统120。在一些实施例中,主机系统120耦合到不同类型的多个存储器子系统110。图1说明耦合到一个存储器

子系统110的主机系统120的一个实例。如本文中所使用,“耦合到”或“与...耦合”通常是指组件之间的连接,其可为间接通信连接或直接通信连接(例如,不具有中间组件),无论有线还是无线,包含例如电连接、光学连接、磁性连接等连接。

24.主机系统120可包含处理器芯片组和由处理器芯片组执行的软件堆叠。处理器芯片组可包含一或多个核心、一或多个高速缓存器、存储器控制器(例如,nvdimm控制器),和存储协议控制器(例如,pcie控制器、sata控制器)。主机系统120使用存储器子系统110,例如将数据写入到存储器子系统110和从存储器子系统110读取数据。

25.主机系统120可经由物理主机接口耦合到存储器子系统110。物理主机接口的实例包含但不限于串行高级技术附件(sata)接口、外围组件互连高速(pcie)接口、通用串行总线(usb)接口、光纤信道、串行附接scsi(sas)、双数据速率(ddr)存储器总线、小型计算机系统接口(scsi)、双列直插式存储器模块(dimm)接口(例如,支持双数据速率(ddr)的dimm套接接口)等。物理主机接口可用于在主机系统120与存储器子系统110之间传输数据。在存储器子系统110通过物理主机接口(例如,pcie总线)与主机系统120耦合时,主机系统120可进一步利用nvm高速(nvme)接口来存取组件(例如,存储器装置130)。物理主机接口可提供用于在存储器子系统110与主机系统120之间传递控制、地址、数据和其它信号的接口。图1说明存储器子系统110作为实例。通常,主机系统120可经由同一通信连接、多个单独通信连接和/或通信连接的组合存取多个存储器子系统。

26.存储器装置130、140可包含不同类型的非易失性存储器装置和/或易失性存储器装置的任何组合。易失性存储器装置(例如,存储器装置140)可为但不限于随机存取存储器(ram),例如动态随机存取存储器(dram)和同步动态随机存取存储器(sdram)。

27.非易失性存储器装置(例如,存储器装置130)的一些实例包含与非(nand)型快闪存储器和就地写入存储器,例如三维交叉点(“3d交叉点”)存储器装置,其为非易失性存储器单元的交叉点阵列。非易失性存储器单元的交叉点阵列可结合可堆叠交叉网格化数据存取阵列基于体电阻的改变而执行位存储。另外,与许多基于快闪的存储器对比,交叉点非易失性存储器可执行就地写入操作,其中可在不预先擦除非易失性存储器单元的情况下对非易失性存储器单元进行编程。nand型快闪存储器包含例如二维nand(2dnand)和三维nand(3d nand)。

28.存储器装置130中的每一个可包含一或多个存储器单元阵列。一种类型的存储器单元,例如单层级单元(slc)可每单元存储一个位。其它类型的存储器单元,例如多层级单元(mlc)、三层级单元(tlc)、四层级单元(qlc)和五层级单元(plc)可每单元存储多个位。在一些实施例中,存储器装置130中的每一个可包含一或多个存储器单元阵列,例如slc、mlc、tlc、qlc、plc或此类的任何组合。在一些实施例中,特定存储器装置可包含存储器单元的slc部分,以及mlc部分、tlc部分、qlc部分或plc部分。存储器装置130的存储器单元可分组为页,所述页可指用于存储数据的存储器装置的逻辑单元。在一些类型的存储器(例如,nand)的情况下,页可经分组以形成块。

29.虽然描述了非易失性存储器组件,例如3d交叉点非易失性存储器单元阵列和nand型快闪存储器(例如,2d nand、3d nand),但存储器装置130可基于任何其它类型的非易失性存储器,例如只读存储器(rom)、相变存储器(pcm)、自选存储器、其它基于硫属化物的存储器、铁电晶体管随机存取存储器(fetram)、铁电随机存取存储器(feram)、磁随机存取存

储器(mram)、自旋转移力矩(stt)-mram、导电桥接ram(cbram)、电阻性随机存取存储器(rram)、基于氧化物的rram(oxram)、或非(nor)快闪存储器或电可擦除可编程只读存储器(eeprom)。

30.存储器子系统控制器115(或为简单起见,控制器115)可与存储器装置130通信以执行操作,例如在存储器装置130处读取数据、写入数据或擦除数据和其它此类操作。存储器子系统控制器115可包含硬件,例如一或多个集成电路和/或离散组件、缓冲存储器或其组合。硬件可包含具有专用(即,硬译码)逻辑的数字电路系统以执行本文中所描述的操作。存储器子系统控制器115可为微控制器、专用逻辑电路系统(例如,现场可编程门阵列(fpga)、专用集成电路(asic)等)或其它合适的处理器。

31.存储器子系统控制器115可包含处理装置,所述处理装置包含被配置成执行存储在本地存储器119中的指令的一或多个处理器(例如,处理器117)。在所说明实例中,存储器子系统控制器115的本地存储器119包含被配置成存储指令的嵌入式存储器,所述指令用于执行控制存储器子系统110的操作(包含处置存储器子系统110与主机系统120之间的通信)的各种过程、操作、逻辑流程和例程。

32.在一些实施例中,本地存储器119可包含存储器寄存器,其存储存储器指针、获取的数据等。本地存储器119还可包含用于存储微码的只读存储器(rom)。虽然图1中的实例存储器子系统110已说明为包含存储器子系统控制器115,但在本公开的另一实施例中,存储器子系统110不包含存储器子系统控制器115,而是可依靠外部控制(例如,由外部主机或由与存储器子系统分开的处理器或控制器提供)。

33.通常,存储器子系统控制器115可从主机系统120接收命令或操作,并且可将所述命令或操作转换为指令或适当命令以实现对存储器装置130的所要存取。存储器子系统控制器115可负责其它操作,例如耗损均衡操作、垃圾收集操作、错误检测和错误校正码(ecc)操作、加密操作、高速缓存操作和与存储器装置130相关联的逻辑地址(例如,逻辑块地址(lba)、名字空间)和物理地址(例如,物理块地址)之间的地址翻译。存储器子系统控制器115可进一步包含主机接口电路系统,以经由物理主机接口与主机系统120通信。主机接口电路系统可将从主机系统接收到的命令转换为存取存储器装置130的命令指令,以及将与存储器装置130相关联的响应转换为用于主机系统120的信息。

34.存储器子系统110还可包含未说明的额外电路系统或组件。在一些实施例中,存储器子系统110可包含高速缓存器或缓冲器(例如,dram)和地址电路系统(例如,行解码器和列解码器),所述地址电路系统可从存储器子系统控制器115接收地址且对所述地址进行解码以存取存储器装置130。

35.在一些实施例中,存储器装置130包含本地媒体控制器135,其结合存储器子系统控制器115操作以对存储器装置130的一或多个存储器单元执行操作。外部控制器(例如,存储器子系统控制器115)可在外部管理存储器装置130(例如,对存储器装置130执行媒体管理操作)。在一些实施例中,存储器子系统110为受管理存储器装置,其为具有在裸片上的控制逻辑(例如,本地控制器132)和用于同一存储器装置封装内的媒体管理的控制器(例如,存储器子系统控制器115)的原始存储器装置130。受管理存储器装置的实例为受管理nand(mnand)装置。

36.本地媒体控制器135可实施擦除验证(ev)组件137,其可执行顺序字线擦除验证方

案以实现擦除深度均一性。对于擦除循环,ev组件137可致使在擦除偏置电压(v

era

)处的擦除脉冲施加在信道上以及禁止偏置电压施加在某些字线(例如,0v)上。更具体地说,擦除脉冲可施加到源极和位线,使得信道电位增加。举例来说,信道可为nand信道。在一些实施例中,v

era

可在约15v到约20v的范围内。在施加擦除脉冲之后,擦除验证可经执行以按实现对wg中的字线的所有存储器单元的独立校验的方式相对于wg顺序地擦除验证。在一些实施例中,独立地验证对应于块的子分区的子块。举例来说,给定子块可包含耦合到位线的竖直串。

37.在一些实施例中,相对于wg内的字线(即,相对于对应于wg内的字线的所有存储器单元)同时应用由ev组件137执行的顺序字线擦除验证方案。在一些实施例中,相对于wg内的交替字线应用由ev组件137执行的顺序字线擦除验证方案。作为说明性实例,可首先相对于第一wg中的偶数编号字线,接着相对于第一wg中的奇数编号字线,接着相对于第二wg中的偶数编号字线,接着相对于第二wg中的奇数编号字线等执行擦除验证。

38.如果所有wg具有通过擦除验证的存储器单元,则擦除操作可结束。否则,将存在通过wg的集合和未通过wg的集合,并且可在起始下一擦除循环之前(例如,在施加下一擦除循环的擦除脉冲之前)相对于通过wg的集合中的wg施加禁止偏置电压。ev组件137可迭代足够数目个擦除循环,包含相对于所有通过wg施加禁止偏置电压,直到所有wg通过擦除验证。下文将参考图3描述关于ev组件137的操作的另外细节。

39.图2为根据实施例的呈存储器装置130的形式的第一设备与呈存储器子系统(例如,图1的存储器子系统110)的存储器子系统控制器115的形式的第二设备通信的简化框图。电子系统的一些实例包含个人计算机、个人数字助理(pda)、数字相机、数字媒体播放器、数字记录器、游戏、电气设备、运载工具、无线装置、移动电话等。存储器子系统控制器115(例如,存储器装置130外部的控制器)可为存储器控制器或其它外部主机装置。

40.存储器装置130包含以行和列逻辑地布置的存储器单元阵列204。逻辑行的存储器单元通常连接到同一存取线(例如,字线),而逻辑列的存储器单元通常选择性地连接到同一数据线(例如,位线)。单个存取线可与存储器单元的多于一个逻辑行相关联,并且单个数据线可与多于一个逻辑列相关联。存储器单元阵列204的至少一部分的存储器单元(图2中未展示)能够编程为至少两个目标数据状态中的一个。

41.提供行解码电路系统208和列解码电路系统210以对地址信号进行解码。接收地址信号且对其进行解码以存取存储器单元阵列204。存储器装置130还包含输入/输出(i/o)控制电路系统260以管理命令、地址和数据到存储器装置130的输入以及数据和状态信息从存储器装置130的输出。地址寄存器214与i/o控制电路系统260和行解码电路系统208以及列解码电路系统210通信以在解码之前锁存地址信号。命令寄存器224与i/o控制电路系统260和本地媒体控制器135通信以锁存传入的命令。

42.控制器(例如,存储器装置130内部的本地媒体控制器135)响应于命令而控制对存储器单元阵列204的存取,并且产生外部存储器子系统控制器115的状态信息,即,本地媒体控制器135被配置成对存储器单元阵列204执行存取操作(例如,读取操作、编程操作和/或擦除操作)。本地媒体控制器135与行解码电路系统208和列解码电路系统210通信,以响应于地址而控制行解码电路系统208和列解码电路系统210。在一个实施例中,本地媒体控制器135包含ev组件137,其可在对存储器装置130的擦除操作期间实施本文中所描述的顺序

字线擦除验证方案。

43.本地媒体控制器135还与高速缓存寄存器218通信。高速缓存寄存器218锁存如由本地媒体控制器135引导的传入或传出数据以暂时存储数据,同时存储器单元阵列204正忙于分别写入或读取其它数据。在编程操作(例如,写入操作)期间,可将数据从高速缓存寄存器218传递到数据寄存器270以用于传送到存储器单元阵列204;接着可将新数据从i/o控制电路系统260锁存在高速缓存寄存器218中。在读取操作期间,数据可从高速缓存寄存器218传递到i/o控制电路系统260以用于输出到存储器子系统控制器115;接着可将新数据从数据寄存器270传递到高速缓存寄存器218。高速缓存寄存器218和/或数据寄存器270可形成存储器装置130的页缓冲器(例如,可形成其一部分)。页缓冲器可进一步包含感测装置(图2中未展示)以感测存储器单元阵列204的存储器单元的数据状态,例如,通过感测连接到所述存储器单元的数据线的状态。状态寄存器222可与i/o控制电路系统260和本地存储器控制器135通信以锁存状态信息以用于输出到存储器子系统控制器115。

44.存储器装置130经由控制链路232从本地媒体控制器135接收存储器子系统控制器115处的控制信号。举例来说,控制信号可包含芯片启用信号ce#、命令锁存启用信号cle、地址锁存启用信号ale、写入启用信号we#、读取启用信号re#和写入保护信号wp#。取决于存储器装置130的性质,可进一步经由控制链路232接收额外或替代的控制信号(未展示)。在一个实施例中,存储器装置130经由多路复用的输入/输出(i/o)总线236从存储器子系统控制器115接收命令信号(其表示命令)、地址信号(其表示地址)和数据信号(其表示数据),并且经由i/o总线236将数据输出到存储器子系统控制器115。

45.举例来说,可经由i/o控制电路系统260处的i/o总线236的输入/输出(i/o)引脚[7:0]接收命令,并且可接着将命令写入到命令寄存器224中。可经由i/o控制电路系统260处的i/o总线236的输入/输出(i/o)引脚[7:0]接收地址,并且可接着将地址写入到地址寄存器214中。可经由i/o控制电路系统260处用于8位装置的输入/输出(i/o)引脚[7:0]或用于16位装置的输入/输出(i/o)引脚[15:0]接收数据,并且接着可将数据写入到高速缓存寄存器218中。随后可将数据写入到数据寄存器270中以用于对存储器单元阵列204进行编程。

[0046]

在实施例中,可省略高速缓存寄存器218,并且可将数据直接写入到数据寄存器270中。还可经由用于8位装置的输入/输出(i/o)引脚[7:0]或用于16位装置的输入/输出(i/o)引脚[15:0]输出数据。虽然可参考i/o引脚,但其可包含实现通过外部装置(例如,存储器子系统控制器115)电连接到存储器装置130的任何导电节点,例如常用的导电衬垫或导电凸块。

[0047]

所属领域的技术人员应了解,可提供额外的电路系统和信号,并且已简化图2的存储器装置130。应认识到,参考图2所描述的各种块组件的功能性可不必与集成电路装置的不同组件或组件部分分离。举例来说,集成电路装置的单个组件或组件部分可适于执行图2的多于一个块组件的功能性。替代地,可组合集成电路装置的一或多个组件或组件部分以执行图2的单个块组件的功能性。另外,虽然根据各种信号的接收和输出的流行惯例而描述具体i/o引脚,但应注意,可在各种实施例中使用i/o引脚(或其它i/o节点结构)的其它组合或其它数目个i/o引脚(或其它i/o节点结构)。

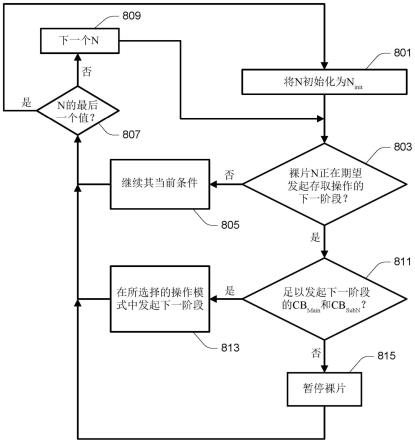

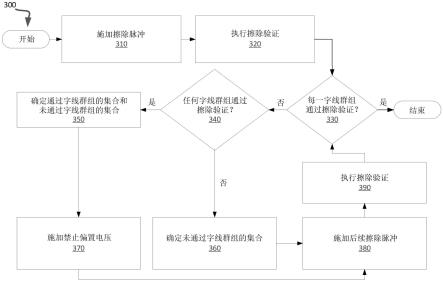

[0048]

图3为根据本公开的一些实施例的执行顺序字线擦除验证方案以实现擦除深度均一性的实例方法300的流程图。方法300可由处理逻辑执行,所述处理逻辑可包含硬件(例

如,处理装置、电路系统、专用逻辑、可编程逻辑、微码、装置的硬件、集成电路等)、软件(例如,在处理装置上运行或执行的指令)或其组合。在一些实施例中,方法300由图1和2的ev组件137执行。虽然以特定顺序或次序来展示,但除非另外指定,否则可修改过程的次序。因此,所说明实施例应仅作为实例理解,并且所说明过程可以不同次序执行,并且一些过程可并行执行。另外,可在各种实施例中省略一或多个过程。因此,并非每一个实施例中都需要所有过程。其它过程流程是可能的。在一些实施例中,方法300可经实施以相对于3d替换栅极存储器装置(例如,3d替换栅极nand)执行擦除验证。

[0049]

在操作310处,施加擦除脉冲。举例来说,处理逻辑(例如,由本地媒体控制器135实施的ev组件137)致使擦除脉冲在擦除循环期间施加到信道。更具体地说,擦除脉冲可施加到源极和位线,使得信道电位增加。举例来说,信道可为nand信道。更具体地说,擦除脉冲可在擦除偏置电压(v

era

)处施加。举例来说,v

era

可在约15v到约20v的范围内。

[0050]

在操作320处,执行擦除验证。举例来说,处理逻辑致使相对于存储器装置的存储器阵列的字线群组(wg)顺序地执行擦除验证。举例来说,存储器装置可为图1的存储器装置130。更具体地说,与存储器单元相关联的字线可在擦除验证之前分区为wg。每一wg的边界可基于与连续字线相关联的擦除v

t

值的“接近性”的分析而确定。举例来说,如果与连续字线相关联的擦除v

t

值相对接近(例如,在彼此的阈值范围内),则所述字线可分组在一起。然而,如果相对于一个字线的擦除v

t

值与相对于下一字线的擦除v

t

值之间存在较大差异(例如,大于给定阈值),则这可表明新wg可从下一字线开始形成。因此,wg可在擦除脉冲的施加之前预表征。

[0051]

擦除验证可基于目标擦除v

t

而以实现所有wg的独立校验的方式相对于wg顺序地执行(例如,通过子块)。如果所有wg通过擦除验证(例如,所有存储器单元通过擦除验证),则擦除操作可结束。否则,将存在通过wg的第一集合和未通过wg的第一集合。在一些实施例中,相对于wg内的所有字线同时应用擦除验证。在一些实施例中,相对于wg内的交替字线应用擦除验证。作为说明性实例,可首先相对于第一wg中的偶数编号字线,接着相对于第一wg中的奇数编号字线,接着相对于第二wg中的偶数编号字线,接着相对于第二wg中的奇数编号字线等执行擦除验证。

[0052]

在操作330处,进行擦除验证通过确定。举例来说,处理逻辑确定每一wg是否通过擦除验证。如果对应于wg的所有擦除v

t

值小于或等于目标擦除v

t

,则wg经确定为已通过擦除验证,并且如果对应于wg的至少一个擦除v

t

值大于目标擦除v

t

,则wg经确定为未通过擦除验证。如果在操作330处每一wg经确定为已通过擦除验证,则这意味着不需要执行更多擦除循环且擦除验证过程结束。

[0053]

否则,如果至少一个wg经确定为未通过擦除验证,则在操作340处,处理逻辑确定在操作340处任何wg是否已通过擦除验证。如果是,则在操作350处,处理逻辑确定通过wg的集合和未通过wg的集合。更具体地说,通过wg的集合可包含在操作330处经确定为已通过擦除验证的wg,并且未通过wg的集合可包含在操作330处经确定为未通过擦除验证的wg。如果无wg已确定为通过擦除验证,则这意味着每一个wg未通过擦除验证。因而,在操作360处,处理逻辑确定未通过wg的集合。

[0054]

如果在操作350处,处理逻辑确定通过wg的集合和未通过wg的集合,则在操作370处,施加禁止偏置电压。举例来说,处理逻辑基于擦除偏置电压和后续擦除偏置电压而致使

相对于通过wg的集合施加禁止偏置电压。禁止偏置电压禁止通过wg的集合的存储器单元在后续擦除循环期间被擦除。后续擦除偏置电压可具有比先前擦除偏置电压高的量值。

[0055]

禁止偏置电压可与δv

era

的倍数成比例,所述δv

era

对应于在先前擦除循环期间施加的先前施加的擦除偏置电压与在后续擦除循环期间施加的后续擦除偏置电压之间的差。在一些实施例中,禁止偏置电压被设置为δv

era

c,其中c为额外偏置值。额外偏置值经添加以确保相对于通过wg的集合中的每一wg的恰当禁止。

[0056]

在一些实施例中,额外偏置值为可调整的增值。可调整的增值经选择为足够大的以足以确保给定擦除循环内的恰当禁止。可调整的增值可经调整以考虑擦除验证过程期间的变化。举例来说,可调整的增值可能需要基于擦除脉冲的持续时间和/或存储器单元擦除特性的调整。因此,可调整的增值可基于此类评估而预定。可调整的增值的可调整性可增加复杂性,因为其将需要在擦除期间相对于不同wg的不同禁止偏置。

[0057]

在一些实施例中,额外偏置值为静态值。在这些实施例中,额外偏置值可经选择为可考虑擦除验证过程期间的几乎所有变化的足够大的值。然而,较大的静态值可能在wg边界处引入错误。因此,虽然与可调整的增值相比较不复杂,但相较于可调整的增值,较大的静态值可能导致较低的准确性。

[0058]

在操作380处,施加后续擦除脉冲。举例来说,处理逻辑致使在后续擦除偏置电压处的后续擦除脉冲在后续擦除循环期间施加到信道。更具体地说,后续擦除脉冲可在v

era

δv

era

的电压处施加。由于在操作370处已相对于经确定为已通过擦除验证的任何wg施加禁止偏置电压,因此相对于经禁止wg的擦除v

t

不受后续擦除脉冲影响。

[0059]

在操作390处,执行后续擦除验证。举例来说,类似于操作320,处理逻辑致使对未通过wg的集合中的wg顺序地执行后续擦除验证。过程接着恢复到操作330以确定未通过wg的集合中的每一wg是否已通过擦除验证。如果是,则过程结束。如果否,则在操作340处确定未通过wg的集合中的任何wg是否已通过擦除验证。如果未通过wg的集合中的至少一个wg已通过擦除验证,则在操作350处确定通过wg的后续集合和未通过wg的后续集合。更具体地说,通过wg的后续集合包含通过wg的先前集合中的wg和已确定在后续擦除循环期间已通过的任何新wg。否则,在操作360处确定未通过wg的后续集合。

[0060]

在操作370处,施加禁止偏置电压。举例来说,处理逻辑致使相对于通过wg的后续集合施加禁止偏置电压。更具体地说,禁止偏置电压相对于先前通过wg重新施加且相对于新添加的通过wg施加。举例来说,如果禁止偏置电压为δv

era

c,则可相对于先前通过wg施加2δv

era

c的禁止偏置电压,并且可相对于新添加的通过wg施加δv

era

c的禁止偏置电压。过程可接着继续到如上文所描述的操作380和390,以确定在操作330处未通过wg的后续集合中的每一wg是否已通过擦除验证。下文现在将参考图3-4描述关于操作310-390的另外细节。

[0061]

图4a为说明根据本公开的一些实施例的在第一擦除循环期间顺序字线擦除验证方案的操作的图表400a,图4b为说明根据本公开的一些实施例的在第二擦除循环期间顺序字线擦除验证方案的操作的图表400b,并且图4c为说明根据本公开的一些实施例的在第三擦除循环期间顺序字线擦除验证方案的操作的图表400c。图表400a-c中的每一个具有指示字线(wl)的x轴和指示擦除阈值电压(v

t

)的y轴。展示数个字线群组(wg),包含wg1 410-1、wg2 410-2、wg3 410-3、wg4 410-4、wg5 410-5和wg6 410-6。此外,线经展示为指示目标擦

除v

t

,即目标v

t 420。

[0062]

参考图表400a,假设在此实例中所展示的第一擦除循环为初始擦除循环。因此,wg 410-1到410-6最初未被禁止被擦除。在第一擦除循环的擦除脉冲为v

era

期间,相对于wg 410-1到410-6中的每一个施加第一擦除偏置电压。接着,在第一擦除循环期间执行的擦除验证期间,擦除验证可以实现wg 410-1到410-6的全部的独立校验的方式相对于wg 410-1到410-6中的每一个顺序地执行(例如,通过子块)。在一些实施例中,同时相对于wg 410-1到410-6中的一个内的所有字线施加擦除验证。在一些实施例中,相对于wg 410-1到410-6中的一个内的交替字线施加擦除验证。作为说明性实例,可首先相对于wg1 410-1中的偶数编号字线,接着相对于wg1 410-1中的奇数编号字线,接着相对于wg2 410-2中的偶数编号字线,接着相对于wg2 410-2中的奇数编号字线等执行擦除验证。

[0063]

wg1 410-1和wg4 410-4已通过擦除验证,因为其相关联的擦除v

t

电平经确定为处于或低于目标v

t 420。因此,通过wg的第一集合包含wg1 410-1和wg4 410-4,并且未通过wg的第一集合包含wg2 410-2、wg3 410-3、wg5 410-5和wg6 410-6。因此,可相对于wg1 410-1和wg4 410-4施加δv

era

c的禁止偏置电压,其中δv

era

为第一擦除偏置电压与待在图表400b中所展示的第二擦除循环期间施加的第二擦除偏置电压之间的差,并且c为额外偏置(例如,可调整的增值或静态值)。

[0064]

现在参考图表400b,在相对于wg1 410-1和wg4 410-4施加禁止电压之后,v

era

δv

era

的擦除偏置电压在第二擦除循环的擦除脉冲期间施加到信道。接着,在第二擦除循环期间执行的擦除验证期间,擦除验证可以实现wg2 410-2、wg3 410-3、wg5 410-5和wg6 410-6的独立校验的方式相对于wg2 410-2、wg3 410-3、wg5 410-5和wg6 410-6中的每一个顺序地执行(类似于图表400a)。

[0065]

除wg1 410-1和wg4 410-4之外,现在wg2 410-2和wg5 410-5已通过擦除验证,因为其相关联的擦除v

t

电平经确定为处于或低于目标v

t 420。因此,通过wg的第二集合包含wg1 410-1、wg2 410-2、wg4 410-4和wg5 410-5,并且未通过wg的第二集合包含wg3 410-3和wg6 410-6。因此,可相对于wg1 410-1、wg2 410-2、wg4 410-4和wg5 410-5施加δv

era

c的禁止偏置电压。

[0066]

此时,已通过2δv

era

c禁止wg1 410-1和wg4 410-4,并且已通过δv

era

c禁止wg2 410-2和wg5 410-5。现在参考图表400c,在施加禁止电压之后,v

era

2δv

era

的擦除偏置电压在第三擦除循环的擦除脉冲期间施加到信道。接着,在第三擦除循环期间执行的擦除验证期间,擦除验证可以实现wg3 410-3和wg6 410-6的独立校验的方式相对于wg3 410-3和wg6 410-6中的每一个顺序地执行(类似于图表400a和400b)。如图表400c中所展示,除wg1 410-1、wg2 410-2、wg4 410-4和wg5 410-5之外,现在wg3 410-3和wg6 410-6已通过擦除验证,因为其相关联的擦除v

t

电平经确定为处于或低于目标v

t 420。因此,wg 410-1到410-6的全部已通过擦除验证且擦除操作完成。

[0067]

图5a为说明根据本公开的一些实施例的在第一擦除循环期间顺序字线擦除验证方案的操作的波形图500a,图5b为说明根据本公开的一些实施例的在第二擦除循环期间顺序字线擦除验证方案的操作的波形图500b,并且图5c为说明根据本公开的一些实施例的在第三擦除循环期间顺序字线擦除验证方案的操作的波形图500c。

[0068]

图500a-500c中的每一个描绘信道510、具有字线的偶数集合(wgx

even

)520-1和字

线的奇数集合(wgx

odd

)520-2的第x字线群组wgx以及具有字线的偶数集合(wgy

even

)530-1和字线的奇数集合(wgy

odd

)530-2的第y字线群组wgy。

[0069]

参考图500a,擦除脉冲540a在擦除偏置电压(v

era

)处施加到信道510。接着,在擦除脉冲540a的施加之后的某一短时间内,顺序地执行擦除验证550a以验证wgx和wgy。举例来说,可验证wgx

even 520-1,之后验证wgx

odd 520-2,接着验证wgy

even

530-1,并且接着验证wgy

odd 530-2。每一擦除验证波形可包含控制栅极电压(v

cg

)波形分量和通路电压(v

pass

)波形分量。举例来说,wgx

even 520-1可包含v

cg

波形分量552和v

pass

波形分量554。

[0070]

现在参考图500b,已确定wgx已在图500a中所展示的第一擦除循环中通过擦除验证。因此,禁止偏置电压施加到wgx

even 520-1和wgx

odd 520-2以禁止wgx在第二擦除循环期间被擦除,如由波形560-1所表示。更具体地说,禁止偏置电压可为如上文所描述的δv

era

c。擦除脉冲540b在v

era

δv

era

的擦除偏置电压处施加到信道510。接着,在擦除脉冲540b的施加之后的某一短时间内,顺序地执行擦除验证550b以验证wgy(例如,wgy

even 530-1且接着wgy

odd 530-2)。

[0071]

现在参考图500c,另一禁止偏置电压施加到wgx

even 520-1和wgx

odd 520-2以禁止wgx在第二擦除循环期间被擦除,如由波形560-2所表示。更具体地说,禁止偏置电压可为如上文所描述的2δvera c。擦除脉冲540c在(v

era

δv

era

) δv

era

=v

era

2δv

era

的擦除偏置电压处施加到信道510。此处,wgy仍未通过擦除验证,这就是其具有如图5b中所展示的类似波形的原因。

[0072]

图6说明计算机系统600的实例机器,在所述实例机器内可执行用于致使机器执行本文中所论述的方法中的任何一或多种的指令集。在一些实施例中,计算机系统600可对应于包含、耦合到或利用存储器子系统(例如,图1的存储器子系统110)的主机系统(例如,图1的主机系统120)或可用于执行控制器的操作(例如,执行操作系统以执行对应于图1的ev组件137的操作)。在替代实施例中,机器可连接(例如,联网)到lan、内联网、外联网和/或因特网中的其它机器。机器可作为对等(或分布式)网络环境中的对等机器或作为云计算基础设施或环境中的服务器或客户端机器而在客户端-服务器网络环境中的服务器或客户端机器的容量中进行操作。

[0073]

机器可为个人计算机(pc)、平板pc、机顶盒(stb)、个人数字助理(pda)、蜂窝式电话、网络器具、服务器、网络路由器、交换机或桥接器,或能够执行(顺序或以其它方式)指定待由所述机器采取的动作的指令集的任何机器。此外,虽然说明了单个机器,但术语“机器”还应被认为包含机器的任何集合,所述机器单独地或共同地执行指令集(或多个指令集)以执行本文中所论述的方法中的任一或多种。

[0074]

实例计算机系统600包含处理装置602、主存储器604(例如,只读存储器(rom)、快闪存储器、动态随机存取存储器(dram),例如同步dram(sdram)或rdram等)、静态存储器606(例如,快闪存储器、静态随机存取存储器(sram)等),以及数据存储系统618,其经由总线630彼此通信。

[0075]

处理装置602表示一或多个通用处理装置,例如微处理器、中央处理单元等。更确切地说,处理装置可为复杂指令集计算(cisc)微处理器、精简指令集计算(risc)微处理器、超长指令字(vliw)微处理器,或实施其它指令集的处理器,或实施指令集的组合的处理器。处理装置602还可为一或多个专用处理装置,例如专用集成电路(asic)、现场可编程门阵列

(fpga)、数字信号处理器(dsp)、网络处理器等。处理装置602被配置成执行用于执行本文中所论述的操作和步骤的指令626。计算机系统600可进一步包含网络接口装置508以经由网络620通信。

[0076]

数据存储系统618可包含机器可读存储媒体624(也称为计算机可读媒体),其上存储有一或多个指令集626或体现本文中所描述的方法或功能中的任何一或多种的软件。指令626还可在其由计算机系统600执行期间完全地或至少部分地驻存在主存储器604内和/或处理装置602内,主存储器604和处理装置602也构成机器可读存储媒体。机器可读存储媒体624、数据存储系统618和/或主存储器604可对应于图1的存储器子系统110。

[0077]

在一个实施例中,指令626包含实施对应于ev组件(例如,图1的ev组件137)的功能性的指令。虽然在实例实施例中将机器可读存储媒体624展示为单个媒体,但术语“机器可读存储媒体”应被认为包含存储一或多个指令集的单个媒体或多个媒体。术语“机器可读存储媒体”还应被认为包含能够存储或编码供机器执行的指令集且致使机器执行本公开的方法中的任一或多种的任何媒体。因此,术语“机器可读存储媒体”应被认为包含但不限于固态存储器、光学媒体和磁性媒体。

[0078]

已依据计算机存储器内的数据位的操作的算法和符号表示呈现了先前详细描述的一些部分。这些算法描述和表示为数据处理领域的技术人员用于将其工作的主旨最有效地传达给所属领域的其他技术人员的方式。算法在此处且通常被认为是产生所要结果的操作的自洽序列。操作为要求对物理数量进行物理操控的操作。这些数量通常但未必呈能够被存储、组合、比较和以其它方式操控的电或磁信号的形式。有时,主要出于通用的原因,已证明将这些信号称作位、值、元件、符号、字符、术语、编号等是方便的。

[0079]

然而,应牢记,所有这些和类似术语应与适当物理数量相关联,并且仅仅是应用于这些数量的方便标签。本公开可指操控和变换计算机系统的寄存器和存储器内的表示为物理(电子)数量的数据为计算机系统存储器或寄存器或其它此类信息存储系统内的类似地表示为物理数量的其它数据的计算机系统或类似电子计算装置的动作和过程。

[0080]

本公开还涉及用于执行本文中的操作的设备。此设备可出于所需目的而专门构造,或其可包含通过存储在计算机中的计算机程序选择性地激活或重新配置的通用计算机。此类计算机程序可存储在计算机可读存储媒体中,例如任何类型的盘(包含软盘、光盘、cd-rom和磁性光盘)、只读存储器(rom)、随机存取存储器(ram)、eprom、eeprom、磁卡或光卡,或适合于存储电子指令的任何类型的媒体,其各自耦合到计算机系统总线。

[0081]

本文中所呈现的算法和显示器在本质上并不与任何特定计算机或其它设备相关。各种通用系统可与根据本文中的教示的程序一起使用,或其可证明构造用于执行所述方法更加专用的设备是方便的。将如下文描述中所阐述的那样来呈现多种这些系统的结构。另外,不参考任何特定编程语言来描述本公开。应了解,可使用多种编程语言来实施如本文中所描述的本公开的教示。

[0082]

本公开可提供为计算机程序产品或软件,其可包含在其上存储有可用于对计算机系统(或其它电子装置)进行编程以执行根据本公开的过程的指令的机器可读媒体。机器可读媒体包含用于以机器(例如,计算机)可读的形式存储信息的任何机构。在一些实施例中,机器可读(例如,计算机可读)媒体包含机器(例如,计算机)可读存储媒体,例如只读存储器(“rom”)、随机存取存储器(“ram”)、磁盘存储媒体、光学存储媒体、快闪存储器组件等。

[0083]

在前述说明书中,已参考其具体实例实施例描述了本公开的实施例。将显而易见的是,可在不脱离如所附权利要求书中阐述的本公开的实施例的更广精神和范围的情况下对本公开进行各种修改。因此,应在说明性意义上而不是限制性意义上看待说明书和图式。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。