1.本发明属于通信电路领域,特别是涉及一种最小值和次最小值检索电路。

背景技术:

2.在很多领域中,都会涉及到数与数的比较,例如查找一组数的最小值和次最小值。在软件算法领域存在很多种解决方式,但是对应到fpga的电路应用时,需要充分考虑硬件实现的复杂度和获取结果的精确度。

3.例如,在fpga应用中,一般采用直接两两比较的树形结构的硬件电路,如图1所示,图中比较器的结构共分为5级,每一级由一个或多个二输入比较器组成,每个比较器将输入的两个数值进行比较,输出较小的那一个,然后再输入到下一级进行比较,直至最后一级的比较器输出最小值。在最后第5级比较的两个值当中,较小值作为最小值输出,较大值则作为次小值输出。这种电路结构实现简单,但是会存在一定的失误,从而导致无法找准确的次小值。例如,当真正的次小值在第2至第4级中与最小值相遇了,真正的次小值与最小值同时输入某一个二输入比较器进行比较,则这个真正的次小值就会被最小值淘汰,从而无法走到最后一级,也就是第5级。因此,最终获得的次小值并不是真正的次小值,而是一个大于次小值的伪次小值。

技术实现要素:

4.本发明主要解决的技术问题是提供一种最小值和次最小值检索电路,获取最小值和真正的次小值,即紧邻最小值的次小值结果。

5.为解决上述技术问题,本发明采用的技术方案是:

6.提供一种最小值和次最小值检索电路,对并行输入2n个互不相同的输入数据检索出其中的最小值和次最小值,n大于等于1,包括n级比较电路;

7.第一级比较电路包括2

n-1

个结构相同的第一级比较单元,其中,第1个第一级比较单元包括输入端[din_1、din_2]、输出端[smin_1_1、min_1_1],输入端[din_1、din_2]对应输入数据中的最小值由min_1_1输出,次小值由smin_1_1输出;

[0008]

第2个第一级比较单元包括输入端[din_3、din_4]、输出端[smin_1_2、min_1_2],输入端[din_3、din_4]对应输入数据中的最小值由min_1_2输出,次小值由smin_1_2输出;

[0009]

依此类推,第2

n-1

个第一级比较单元包括输入端[din_2

n-1、din_2n]、输出端[smin_1_2

n-1

、min_1_2

n-1

],输入端[din_2

n-1、din_2n]对应输入数据中的最小值由min_1_2

n-1

输出,次小值由smin_1_2

n-1

输出;

[0010]

第二级比较电路包括2

n-2

个结构相同的第二级比较单元,其中,第1个第二级比较单元包括的输入端与第一级比较电路的输出端[smin_1_1、smin_1_2、min_1_1、min_1_2]相对应,以及包括输出端[smin_2_1_1、smin_2_1_2、min_2_1];

[0011]

第2个第二级比较单元包括的输入端与第一级比较电路的输出端[smin_1_3、smin_1_4、min_1_3、min_1_4]相对应,以及包括输出端[smin_2_2_1、smin_2_2_2、min_2_

2];

[0012]

依此类推,第2

n-2

个第二级比较单元与第一级比较电路的输出端[smin_1_(2

n-1-1)、smin_1_2

n-1

、min_1_(2

n-1-1)、min_1_2

n-1

]相对应,以及包括输出端[smin_2_2

n-2

_1、smin_2_2

n-2

_2、min_2_2

n-2

];

[0013]

第三级比较电路包括2

n-3

个结构相同的第三级比较单元,其中,第1个第三级比较单元包括的输入端与第二级比较电路的输出端

[0014]

[smin_2_1_1、smin_2_2_1、smin_2_1_2、smin_2_2_2、min_2_1、min_2_2]相对应,以及包括输出端[smin_3_1_1、smin_3_1_2、smin_3_1_3、min_3_1];

[0015]

第2个第三级比较单元包括的输入端与第二级比较电路的输出端[smin_2_3_1、smin_2_4_1、smin_2_3_2、smin_2_4_2、min_2_3、min_2_4]相对应,以及包括输出端[smin_3_2_1、smin_3_2_2、smin_3_2_3、min_3_2];

[0016]

依此类推,第2

n-3

个第三级比较单元与第二级比较电路的输出端[smin_2_(2

n-2-1)_1、smin_2_2

n-2

_1、smin_2_(2

n-2-1)_2、smin_2_2

n-2

_2、min_2_(2

n-2-1)、min_2_2

n-2

]相对应,以及包括输出端[smin_3_2

n-3

_1、smin_3_2

n-3

_2、smin_3_2

n-3

_3、min_3_2

n-3

];

[0017]

以此类推,第n级比较电路包括输入端与第n-1级比较电路的输出端[smin_(n-1)_1_1、smin_(n-1)_2_1、smin_(n-1)_1_2、smin_(n-1)_2_2、

……

、smin_(n-1)_1_(n-1)、smin_(n-1)_2_(n-1)、min_(n-1)_1、min_(n-1)_2]相对应,以及包括输出端[smin_n_1、smin_n_2、

……

、smin_n_n、min_n];其中输出端min_n产生输出2n个输入数据中的最小值。

[0018]

优选的,第n级比较电路的输出端[smin_n_1、smin_n_2、

……

、smin_n_n]输入到次小值比较电路,产生输出的最小值,即是2n个输入数据中的次最小值。

[0019]

优选的,第一级比较单元包括一个比较器b1和第一选择器s11、第二选择器s12,比较器b1包括两个输入端,用于输入两个输入数据,比较器b1的输出端分别电连接第一选择器s11、第二选择器s12的选择控制端;

[0020]

其中,第一选择器s11的第一输入端电连接比较器b1的第一输入端,第一选择器s11的第二输入端电连接比较器b1的第二输入端;

[0021]

第二选择器s12的第一输入端电连接比较器b1的第二输入端,第二选择器s12的第二输入端电连接比较器b1的第一输入端;

[0022]

第一选择器s11的输出端用于输出两个输入数据中的第一级最小值,第二选择器s12的输出端用于输出两个输入数据中的第一级伴随次小值,第一级比较单元输出的每个第一级最小值都对应有1个第一级伴随次小值。

[0023]

优选的,第二级比较单元包括一个比较器b2和第一选择器s21、第二选择器s22和第三选择器s23,其中,比较器b2包括两个输入端,用于输入第一级比较电路输出的两个第一级最小值,比较器b2的输出端分别电连接第一选择器s21、第二选择器s22和第三选择器s23的选择控制端;

[0024]

其中,第一选择器s21的第一输入端电连接比较器b2的第一输入端,第一选择器s21的第二输入端电连接比较器b2的第二输入端;第二选择器s22的第一输入端电连接比较器b2的第二输入端,第二选择器s22的第二输入端电连接比较器b2的第一输入端;第三选择器s23的第一输入端和第二输入端分别用于对应输入第一级比较电路输出的两个第一级伴随次小值;

[0025]

第一选择器s21的输出端用于输出两个第一级最小值中的最小值作为第二级最小值,第二选择器s22的输出端用于输出两个第一级最小值中的次小值,作为第二级最小值对应的1个第二级伴随次小值,第三选择器s23的输出端,用于输出与两个第一级最小值中的最小值对应的第一级伴随次小值,作为第二级最小值对应的另1个第二级伴随次小值,第二级比较单元输出的第二级最小值对应有2个第二级伴随次小值。

[0026]

优选的,第三级比较单元包括一个比较器b3和第一选择器s31、第二选择器s32、第三选择器s33和第四选择器s34,其中,比较器b3包括两个输入端,用于输入第二级比较电路输出的两个第二级最小值,比较器b3的输出端分别电连接第一选择器s31、第二选择器s32、第三选择器s33和第四选择器s34的选择控制端;

[0027]

第一选择器s31的第一输入端电连接比较器b3的第一输入端,第一选择器s31的第二输入端电连接比较器b3的第二输入端;第二选择器s32的第一输入端电连接比较器b3的第二输入端,第二选择器s32的第二输入端电连接比较器b3的第一输入端;第三选择器s33、第四选择器s34各自的第一输入端和第二输入端,分别用于对应输入第二级比较电路输出的两个第二级伴随次小值;

[0028]

第一选择器s31的输出端用于输出两个第二级最小值中的最小值作为第三级最小值,第二选择器s32的输出端用于输出两个第二级最小值中的次小值,作为第三级最小值对应的1个第三级伴随次小值,第三选择器s33、第四选择器s34的输出端,各自用于输出与两个第二级最小值中的最小值对应的第二级伴随次小值,作为第三级最小值对应的另2个第三级伴随次小值;第三级比较单元输出的第三级最小值都对应有3个第三级伴随次小值。

[0029]

优选的,第n级比较电路包括一个比较器bn和第一选择器sn1至第n 1选择器sn(n 1),其中,比较器bn包括两个输入端,用于输入第n-1级比较电路输出的两个第n-1级最小值,比较器bn的输出端分别电连接第一选择器sn1至第n 1选择器sn(n 1)的选择控制端;

[0030]

其中第一选择器sn1的第一输入端电连接比较器bn的第一输入端,第一选择器sn1的第二输入端电连接比较器bn的第二输入端;第二选择器sn2的第一输入端电连接比较器bn的第二输入端,第二选择器sn2的第二输入端电连接比较器bn的第一输入端;第三选择器sn3至第n 1选择器sn(n 1)各自的第一输入端和第二输入端,分别用于对应输入第n-1级比较电路输出的两个第n-1级伴随次小值;第一选择器sn1的输出端用于输出两个第n-1级最小值中的最小值,作为第n级最小值,即为2n个输入数据中的最小值,第二选择器sn2的输出端用于输出两个第n-1级最小值中的次小值,作为第n级最小值对应的1个第n级伴随次小值,

[0031]

第三选择器sn3至第n 1选择器sn(n 1)的输出端,各自用于输出与两个第n-1级最小值中的最小值对应的第n-1级伴随次小值,分别作为第n级最小值对应的另外n-1个第n级伴随次小值,第n级最小值对应有n个第n级伴随次小值。

[0032]

优选的,次小值比较电路包含m级树形比较电路,其中m为大于0的整数,每一级树形比较电路由一个或多个二输入比较器组成,每个比较器将输入的两个数值进行比较,输出较小的那一个,然后再输入到下一级树形比较电路进行比较,直至最后一级树形比较电路输出最小值。

[0033]

优选的,对于每一级树形比较电路,当输入至树形比较电路的数值的个数为偶数a时,树形比较电路包括a/2个比较器,用于对输入的a个数值进行两两比较,将比较获得的a/

2个较小值输入至下一级树形比较电路,其中a为大于零的偶数。

[0034]

优选的,对于每一级树形比较电路,当输入至树形比较电路的数值的个数为奇数b时,树形比较电路包括(b-1)/2个比较器,用于对输入的第1至第b-1个数进行两两比较,获得(b-1)/2个较小值,并将输入的第b个数和(b-1)/2个较小值输入到下一级树形比较电路,其中b为大于1的奇数。

[0035]

优选的,在最小值和次最小值检索电路中插入一级或多级流水线。

[0036]

本发明的有益效果是:通过设计一种最小值和次最小值检索,通过保留与最小值比较过的伴随次小值,获取更精确的最小值和次小值结果。

附图说明

[0037]

图1是现有技术中查找一组数据的最小值和次小值的电路结构示意图;

[0038]

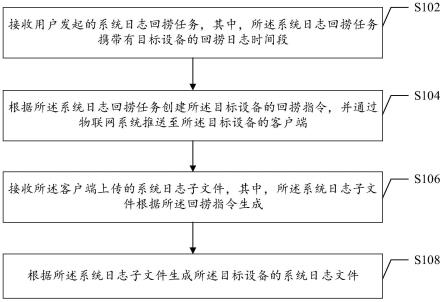

图2是本发明检索方法一实施例的流程图;

[0039]

图3是图2中步骤s101的子流程图;

[0040]

图4是本发明检索电路一实施例第1-n级比较电路框架示意图;

[0041]

图5是本发明检索电路一实施例第一级比较单元结构示意图;

[0042]

图6是本发明检索电路一实施例第二级比较单元结构示意图;

[0043]

图7是本发明检索电路一实施例第三级比较单元结构示意图;

[0044]

图8是本发明检索电路一实施例第n级比较电路结构示意图;

[0045]

图9是本发明检索电路一实施例第五级比较电路结构示意图;

[0046]

图10是本发明检索电路一实施例n个次小值比较电路结构示意图;

[0047]

图11是本发明检索电路一实施例5个次小值比较电路结构示意图;

[0048]

图12是本发明检索电路一实施例第1-n级比较电路框架示意图;

[0049]

图13是本发明检索电路一实施例第二级比较单元结构示意图;

[0050]

图14是本发明检索电路一实施例第三级比较单元结构示意图;

[0051]

图15是本发明检索电路一实施例第n级比较电路结构示意图。

具体实施方式

[0052]

为了便于理解本发明,下面结合附图和具体实施例,对本发明进行更详细的说明。附图中给出了本发明的较佳的实施例。但是,本发明可以以许多不同的形式来实现,并不限于本说明书所描述的实施例。相反地,提供这些实施例的目的是使对本发明的公开内容的理解更加透彻全面。

[0053]

需要说明的是,除非另有定义,本说明书所使用的所有的技术和科学术语与属于本发明的技术领域的技术人员通常理解的含义相同。在本发明的说明书中所使用的术语只是为了描述具体的实施例的目的,不是用于限制本发明。

[0054]

实施例一

[0055]

针对图1中的比较器,可以看出,该输入的32个数的最小值的次小值只可能存在于同该最小值比较过的5个值当中,基于此,本发明提出一种最小值和次最小值检索方法,该检索方法是对2n个互不相同的数进行n级比较,在每一级获得最小值的同时,保留该级最小值对应的伴随次小值,该伴随次小值是与本级中最小值比较过,但大于最小值的那些值,通

常会有多个这样的伴随次小值。

[0056]

进一步地,在下一级时,将获得的最小值对应的上一级的伴随次小值继承下来,作为本级最小值的伴随次小值。

[0057]

从而到达n级时,比较获得最终正确的最小值时,还能获得该最小值对应的伴随次小值数组,该伴随次小值数组中的值,就是与该最小值比较过的值,真正的次小值一定存在于该伴随次小值数组中,再从该伴随次小值数组中找到最小值,从而保证获取最精确的次小值。

[0058]

具体地,参考图2所示的本发明检索方法一实施例的流程图,如图所示,本发明提供一种最小值和次最小值检索方法,包括步骤:

[0059]

s101:将2n个互不相同的数据进行n级比较,获得最小值和n个伴随次小值,其中n为大于0的整数;

[0060]

s102:将n个伴随次小值两两比较,经过多级树形比较获得真正的次小值;

[0061]

s103:输出最小值和次小值。

[0062]

进一步地,参考图3所示,步骤s101还包括:

[0063]

s1011:第一级比较:将2n个互不相同的数据进行两两比较,获得长度为2

n-1

的第一级最小值数组和第一级伴随次小值数组;其中,第一级最小值为两两比较的数据中较小的,第一级伴随次小值为两两比较的数据中较大的,从而每个所述第一级最小值对应有1个伴随次小值;

[0064]

s1012:第二级比较:将第一级最小值进行两两比较,获得长度为2

n-2

的第二级最小值数组和第二级伴随次小值数组;其中,第二级最小值为两两比较的数据中较小的,第二级伴随次小值为两两比较的数据中较大的;进一步地,将第一级伴随次小值数组中与第二级最小值对应的2

n-2

个数据添加进对应的第二级伴随次小值数组,从而每个所述第二级最小值对应有2个伴随次小值;

[0065]

s1013:第三级比较:将第二级最小值进行两两比较,获得长度为2

n-3

的第三级最小值数组和第三级伴随次小值数组;其中,第三级最小值为两两比较的数据中较小的,第三级伴随次小值为两两比较的数据中较大的;进一步地,将第二级伴随次小值数组中与第三级最小值对应的2

n-3

个数据添加进对应的第三级伴随次小值数组,从而每个所述第三级最小值对应有3个伴随次小值;

[0066]

s1014:以此类推,进行逐级比较直至第n级比较,获得长度为1的第n级最小值数组和第n级伴随次小值数组;其中,第n级最小值为两两比较的数据中较小的,第n级伴随次小值为两两比较的数据中较大的;进一步地,将第n-1级伴随次小值数组中与第n级最小值对应的数据添加进对应的第n级伴随次小值数组,从而一共获得n个伴随次小值。

[0067]

综上,本发明提供的方法在对输入的2n个数值进行多级两两比较的基础上,在每一级获得最小值的同时,保留该级最小值对应的伴随次小值,该伴随次小值是与本级中最小值比较过,但大于最小值的那些值,并最终将最后一级的伴随次小值再进行两两比较,从而获得紧邻最小值的次小值结果。通过本发明的方法,相比于现有技术,可以获得更为精确的次小值结果,同时本发明方法设计简单,也便于电路实现,降低电路设计的复杂性。

[0068]

实施例二

[0069]

参考图4,图4为本发明检索电路一实施例第1-n级示意图。

[0070]

如图所示,本发明提供一种最小值和次最小值检索电路,实现实施例一中的检索方法,对并行输入2n个互不相同的输入数据检索出其中的最小值和次小值,n大于等于1,包括n级比较电路;

[0071]

第一级比较电路包括2

n-1

个结构相同的第一级比较单元,其中,第1个第一级比较单元包括输入端[din_1、din_2]、输出端[smin_1_1、min_1_1],输入端[din_1、din_2]对应输入数据中的最小值由min_1_1输出,次小值由smin_1_1输出;第2个第一级比较单元包括输入端[din_3、din_4]、输出端[smin_1_2、min_1_2],输入端[din_3、din_4]对应输入数据中的最小值由min_1_2输出,次小值由smin_1_2输出;依此类推,第2

n-1

个第一级比较单元包括输入端[din_2

n-1、din_2n]、输出端[smin_1_2

n-1

、min_1_2

n-1

],输入端[din_2

n-1、din_2n]对应输入数据中的最小值由min_1_2

n-1

输出,次小值由smin_1_2

n-1

输出;

[0072]

第二级比较电路包括2

n-2

个结构相同的第二级比较单元,其中,第1个第二级比较单元包括的输入端与第一级比较电路的输出端[smin_1_1、smin_1_2、min_1_1、min_1_2]相对应,以及包括输出端[smin_2_1_1、smin_2_1_2、min_2_1];第2个第二级比较单元包括的输入端与第一级比较电路的输出端[smin_1_3、smin_1_4、min_1_3、min_1_4]相对应,以及包括输出端[smin_2_2_1、smin_2_2_2、min_2_2];依此类推,第2

n-2

个第二级比较单元与第一级比较电路的输出端[smin_1_(2

n-1-1)、smin_1_2

n-1

、min_1_(2

n-1-1)、min_1_2

n-1

]相对应,以及包括输出端[smin_2_2

n-2

_1、smin_2_2

n-2

_2、min_2_2

n-2

];

[0073]

第三级比较电路包括2

n-3

个结构相同的第三级比较单元,其中,第1个第三级比较单元包括的输入端与第二级比较电路的输出端[smin_2_1_1、smin_2_2_1、smin_2_1_2、smin_2_2_2、min_2_1、min_2_2]相对应,以及包括输出端[smin_3_1_1、smin_3_1_2、smin_3_1_3、min_3_1];第2个第三级比较单元包括的输入端与第二级比较电路的输出端[smin_2_3_1、smin_2_4_1、smin_2_3_2、smin_2_4_2、min_2_3、min_2_4]相对应,以及包括输出端[smin_3_2_1、smin_3_2_2、smin_3_2_3、min_3_2];依此类推,第2

n-3

个第三级比较单元与第二级比较电路的输出端[smin_2_(2

n-2-1)_1、smin_2_2

n-2

_1、smin_2_(2

n-2-1)_2、smin_2_2

n-2

_2、min_2_(2

n-2-1)、min_2_2

n-2

]相对应,以及包括输出端[smin_3_2

n-3

_1、smin_3_2

n-3

_2、smin_3_2

n-3

_3、min_3_2

n-3

];

[0074]

以此类推,第n级比较电路包括输入端与第n-1级比较电路的输出端[smin_(n-1)_1_1、smin_(n-1)_2_1、smin_(n-1)_1_2、smin_(n-1)_2_2、

……

、smin_(n-1)_1_(n-1)、smin_(n-1)_2_(n-1)、min_(n-1)_1、min_(n-1)_2]相对应,以及包括输出端[smin_n_1、smin_n_2、

……

、smin_n_n、min_n];其中输出端min_n产生输出2n个输入数据中的最小值min。

[0075]

综上,本发明提供的最小值和次最小值检索电路在对输入的2n个数值进行多级两两比较的基础上,在每一级获得最小值的同时,保留该级最小值对应的伴随次小值,该伴随次小值是与本级中最小值比较过,但大于最小值的那些值,最终将最后一级的伴随次小值再进行两两比较,就能获得紧邻最小值的次小值结果。

[0076]

通过本发明的检索电路,相比于现有技术,由于保留了与最小值比较过的伴随次小值,从而可以获得更为精确的次小值结果,同时本发明电路简单,便于电路实现。

[0077]

进一步地,参考图10,第n级比较电路的输出端[smin_n_1、smin_n_2、

……

、smin_n_n]输入到次小值比较电路,产生输出的最小值,即是2n个输入数据中的次小值smin。

[0078]

通过本发明的次小值比较电路,可以获得更临近最小值的次小值结果,也就是获得更为精确的次小值结。

[0079]

进一步地,图5是本发明检索电路一实施例第一级比较单元结构示意图,如图中所示,第一级比较单元包括一个b1和两个选择器,b1包括两个输入端,用于输入两个输入数据,b1的输出端分别电连接两个选择器的选择控制端。

[0080]

其中,选择器包括第一选择器s11和第二选择器s12。第一选择器s11的第一输入端电连接b1的第一输入端,第一选择器s11的第二输入端电连接b1的第二输入端;第二选择器s12的第一输入端电连接b1的第二输入端,第二选择器s12的第二输入端电连接b1的第一输入端;第一选择器s11的输出端用于输出两个输入数据中的第一级最小值,第二选择器s12的输出端用于输出两个输入数据中的第一级伴随次小值,该第一级伴随次小值为第一级最小值的伴随次小值,第一级比较单元输出的每个第一级最小值都对应有1个第一级伴随次小值。

[0081]

进一步地,图6是本发明检索电路一实施例第二级比较单元结构示意图,如图中所示,第二级比较单元包括一个比较器b2和三个选择器,其中,比较器b2包括两个输入端,用于输入第一级比较电路输出的两个第一级最小值,比较器b2的输出端分别电连接三个选择器的选择控制端。

[0082]

其中,选择器包括第一选择器s21、第二选择器s22和第三选择器s23。第一选择器s21的第一输入端电连接比较器b2的第一输入端,第一选择器s21的第二输入端电连接比较器b2的第二输入端;第二选择器s22的第一输入端电连接比较器b2的第二输入端,第二选择器s22的第二输入端电连接比较器b2的第一输入端;第三选择器s23的第一输入端和第二输入端分别用于对应输入第一级比较电路输出的两个第一级伴随次小值。

[0083]

其中,第三选择器s23输入的第一级伴随次小值是与比较器b2输入端输入的第一级最小值一一对应的。例如,参考图6所示,若比较器b2的第一输入端输入的是min_1_1,则第三选择器s23的第一输入端对应输入的是第一级最小值min_1_1的第一级伴随次小值smin_1_1。同样地,若比较器b2的第二输入端输入的是min_1_2,则第三选择器s23的第二输入端对应输入的是第一级最小值min_1_2的第一级伴随次小值smin_1_2。这样设置的目的是,每个选择器都是在两个属于不同最小值的次小值中进行选择。

[0084]

第一选择器s21的输出端用于输出两个第一级最小值中的最小值作为第二级最小值,第二选择器s22的输出端用于输出两个第一级最小值中的次小值,作为第二级最小值对应的1个第二级伴随次小值,第三选择器s23的输出端用于输出与两个第二级最小值中的最小值对应的第二级伴随次小值,作为第二级最小值对应的另1个第二级伴随次小值,从而,第二级比较单元输出的第二级最小值对应有2个第二级伴随次小值。

[0085]

例如,参考图6所示,若本级(第二级)比较得出最小值min_2_1=min_1_1,则第三选择器s23输出的第二级伴随次小值smin_2_1_1=smin_1_1。这是因为,参考图5输出端所示,smin_1_1为对应的第一级最小值min_1_1的第一级伴随次小值。

[0086]

相反,若本级(第二级)比较得出最小值min_2_1=min_1_2,则第三选择器s23输出的第二级伴随次小值smin_2_1_1=smin_1_2。

[0087]

综上,每个选择器都是在两个属于不同最小值的次小值中进行选择,并且最终选择留下来的伴随次小值一定是与选择留下来的最小值相对应的,也就是与该最小值比较过

的值。

[0088]

进一步地,图7是本发明检索电路一实施例第三级比较单元结构示意图,如图中所示,第三级比较单元包括一个比较器b3和四个选择器,其中,比较器b3包括两个输入端,用于输入第二级比较电路输出的两个第二级最小值,比较器b3的输出端分别电连接四个选择器的选择控制端。

[0089]

其中,选择器包括第一选择器s31、第二选择器s32、第三选择器s33和第四选择器s34。第一选择器s31的第一输入端电连接比较器b3的第一输入端,第一选择器s31的第二输入端电连接比较器b3的第二输入端;第二选择器s32的第一输入端电连接比较器b3的第二输入端,第二选择器s32的第二输入端电连接比较器b3的第一输入端;第三、第四选择器s34的第一输入端和第二输入端分别用于对应输入第二级比较电路输出的两个第二级伴随次小值。

[0090]

其中,第三、第四选择器s34输入的第二级伴随次小值是与比较器b3输入端输入的第二级最小值一一对应的。例如,参考图7所示,若比较器b3的第一输入端输入的是第二级最小值min_2_1,则第三选择器s33的第一输入端对应输入的是第二级最小值min_2_1的第二级伴随次小值smin_2_1_1。同样地,若比较器b3的第二输入端输入的是第二级最小值min_2_2,则第三选择器s33的第二输入端对应输入的是第二级最小值min_2_2的第二级伴随次小值smin_2_2_1。以此类推,第四选择器s34的第一输入端输入的是第二级最小值min_2_1的另一个第二级伴随次小值smin_2_1_2,而第四选择器s34的第二输入端输入的是第二级最小值min_2_2的另一个第二级伴随次小值smin_2_2_2。从而使得每个选择器都是在两个属于不同最小值的次小值中进行选择。

[0091]

第一选择器s31的输出端用于输出两个第二级最小值中的最小值作为第三级最小值,第二选择器s32的输出端用于输出两个第二级最小值中的次小值,作为第三级最小值对应的1个第三级伴随次小值,第三、第四选择器s34的输出端用于输出与两个第二级最小值中的最小值对应的第二级伴随次小值,作为第三级最小值对应的另2个第三级伴随次小值;第三级比较单元输出的第三级最小值都对应有3个第三级伴随次小值。

[0092]

例如,参考图7所示,若本级(第三级)比较得出最小值min_3_1=min_2_1,则第三选择器s33输出的第三级伴随次小值smin_3_1_1=smin_2_1_1。这是因为,参考图6输出端所示,smin_2_1_1为对应的第二级最小值min_2_1的第一级伴随次小值。

[0093]

相反,若本级(第三级)比较得出最小值min_3_1=min_2_2,则第三选择器s33输出的第三级伴随次小值smin_3_1_1=smin_2_2_1。

[0094]

综上,每个选择器都是在两个属于不同最小值的次小值中进行选择,并且最终选择留下来的伴随次小值一定是与选择留下来的最小值相对应的,也就是与该最小值比较过的值。

[0095]

进一步地,以此类推,图8是本发明检索电路一实施例第n级比较电路结构示意图。如图中所示,第n级比较电路包括一个比较器bn和n 1个选择器,其中,比较器bn包括两个输入端,用于输入第n-1级比较电路输出的两个第n-1级最小值,比较器bn的输出端分别电连接n 1个选择器的选择控制端。

[0096]

其中,选择器包括第一选择器sn1、第二选择器sn2

…

直至第n 1选择器sn(n 1)。第一选择器sn1的第一输入端电连接比较器bn的第一输入端,第一选择器sn1的第二输入端电

连接比较器bn的第二输入端;第二选择器sn2的第一输入端电连接比较器bn的第二输入端,第二选择器sn2的第二输入端电连接比较器bn的第一输入端;第三选择器sn3至第n 1选择器sn(n 1)各自的第一输入端和第二输入端分别用于对应输入第n-1级比较电路输出的两个第n-1级伴随次小值。其中,第三选择器sn3至第n 1选择器sn(n 1)输入的n-1级伴随次小值是与比较器bn输入端输入的第n-1级最小值一一对应的。

[0097]

第一选择器sn1的输出端用于输出两个第n-1级最小值中的最小值,作为第n级最小值,第二选择器sn2的输出端用于输出两个第n-1级最小值中的次小值,作为第n级最小值对应的1个第n级伴随次小值。第三选择器sn3至第n 1选择器sn(n 1)的输出端,分别用于输出与两个第n-1级最小值中的最小值对应的第n-1级伴随次小值,该n-1个输出值分别作为第n级最小值对应的另外n-1个第n级伴随次小值,第n级最小值对应有n个第n级伴随次小值。

[0098]

进一步地,图10是本发明检索电路一实施例次小值比较电路结构示意图。如图所示,将第n级比较电路的输出端[smin_n_1、smin_n_2、

……

、smin_n_n]输入到次小值比较电路,产生输出的最小值,即是2n个输入数据中的次小值smin。

[0099]

其中,次小值比较电路包含m级树形比较电路,每一级为两两比较,也就是说,每一级由一个或多个二输入比较器组成,每个比较器将输入的两个数值进行比较,输出较小的那一个,然后再输入到下一级树形比较电路进行比较,直至最后一级树形比较电路输出最小值。一共经过m级,m与输入的次小值个数相关。

[0100]

具体地,参考图11,当输入的次小值个数为5,则m=3,将经过三级树形比较电路完成这5个次小值的比较,最终得到这5个次小值中的最小值,作为2n个输入数据中的次小值smin。第一级树形比较电路包括两个比较器,第二级树形比较电路包括1个比较器,第三级树形比较电路(第m级树形比较电路)包括1个比较器。

[0101]

优选地,对于第i级树形比较电路(i为正整数,且0《i《m 1),有以下实现方式:

[0102]

当输入数值个数为偶数a时(a为大于零的偶数),第i级树形比较电路比较电路包括a/2个比较器,用于对输入的a个数值进行两两比较,将比较获得的a/2个较小值值输入至下一级树形比较电路(第i 1级树形比较电路)。

[0103]

其中,每一个比较器包括两个输入端和一个输出端。比较器的输入端用于输入待比较的两个次小值,输出端用于输出两个次小值中的较小值,作为第i级次小值,将第i级次小值输入至下一级树形比较电路。

[0104]

当输入数值个数为奇数b(b为大于1的奇数)时,第i级树形比较电路包括(b-1)/2个比较器,用于对输入的第1至第b-1个数进行两两比较,获得(b-1)/2个较小值,并将输入的第b个数和所述(b-1)/2个较小值输入到下一级树形比较电路(第i 1级树形比较电路)。

[0105]

每一个比较器包括两个输入端和一个输出端,比较器的输入端用于输入待比较的两个次小值,输出端用于输出两个次小值中的较小值,作为第i级次小值,将第i级次小值输入至下一级树形比较电路。

[0106]

以此类推,第m级树形比较电路(最后一级树形比较电路)包含1个比较器,比较器包括两个输入端和一个输出端。比较器的输入端用于输入待比较的两个第m-1级次小值,输出端用于输出两个第m-1级次小值中的较小值,作为第m级次小值,第m级次小值就是最终获得的次小值。

[0107]

图11为本发明一个3级树形比较电路的具体实施示例,下面详细描述:

[0108]

参考图11,在第一级树形比电路中,输入的数值个数为奇数5,则b=5,i=1,因此,第一级树形比较电路包括(5-1)/2=2个比较器。第一级树形比较电路产生2个第一级次小值,将输入到第二级树形比较电路中。另外,由于只比较了前四个原始输入的数值,因此第五个原始输入的数值smin_5_5还未比较,也将作为第一级次小值,继续输入到第二级树形比较电路中。

[0109]

参考图11,在第二级树形比较电路中,输入的数值个数为奇数3。则又有b=3,i=2。因此,第二级树形比较电路包括(3-1)/2=1个比较器。第二级树形比较电路产生1个第二级次小值,将输入到第三级树形比较电路中。另外,由于只比较了前2个第一级次小值,因此未比较的数值smin_5_5在第二级树形比较电路中还未比较,也将作为第二级次小值,继续输入到第三级树形比较电路中。

[0110]

参考图11,在第三级树形比较电路中,输入的数值个数为偶数2。则又有a=2,i=3,m=3。因此,第三级树形比较电路包括2/2=1个比较器。第三级树形比较电路产生1个第三级次小值,该第三级次小值就是最终获得的次小值。

[0111]

以上只是一种实施例,其他实施例的原理也是类似,都是通过两两比较的树形结构,最终获得输入的一组数据的最小值,在此不再赘述。

[0112]

具体地,参考图5、6、7、9、11,展示了一个具体的检索电路的1-8级示意图。为了与图1中进行对比,输入也选为32个数,因此,比较电路包含5级,经过比较电路获取的次小值为5个,因此次小值比较电路分为3级,以上可知该32个数据的检索电路一共分为8级。

[0113]

参考图5,在第1级,32个输入数据两两之间进行比较,其中较小值作为第1级的局部最小值输出,记作min_1_i,i=1.2....,16,较大值作为此局部最小值的伴随次小值输出,记作smin_1_i,i=1,2,

…

,16。

[0114]

参考图6,在第2级,min_1_i,i=1,2,

…

,16两两之间进行比较,其中较小值作为第2级的局部最小值输出,记作min_2_i,i=1,2,

…

,8,较小值的伴随次小值被继承至第2级作为此局部最小值的第一伴随次小值输出,记作smin_2_i_1,i=1,2,

…

,8,较大值作为此局部最小值的第二伴随次小值输出,记作smin_2_i_2,i=1,2,

…

,8。

[0115]

第3级、第4级同理,不再赘述。

[0116]

参考图9,在第5级得出最小值的同时还得出此最小值的5个伴随次小值。

[0117]

参考图11,真正的次小值就在图8中得出的5个伴随次小值之中,因此5个伴随次小值再经过3级树型比较后,便可以得出真正的次小值。

[0118]

与只得出最小值的图1所示的电路相比,本发明的检索电路只额外消耗了3个二输入比较器和3级树形比较过程,却可以获得更精确的最小值和相应的次小值。

[0119]

进一步地,本发明为加快其工作速率,在最小值和次最小值检索电路中插入多级流水线。

[0120]

流水线的原理就是将逻辑电路系统地分割,并在各个分割逻辑电路之间插入寄存器,并暂存中间数据的方法。目的是将一个大型的逻辑运算分解成若干小逻辑运算,每一级逻辑运算占用时间较小,并且可以并行,从而提高频率,最终提高处理速度。

[0121]

例如在最小值和次最小值检索电路中的每两级比较电路通过寄存器缓存输出,使得寄存器前后的比较电路可以并行执行逻辑运算,从而在较短时钟周期内便可以找出一组

数据中的最小值和相应的次小值。

[0122]

具体地,针对图5、6、7、9、11中一个具体的8级检索电路,可以在第1级、第3级、第5级比较电路以及图11中的第二级树形比较电路中插入寄存器,从而实现在8级的检索电路中插入四级流水线,提升了计算的并行度。流水线的级数以及插入的位置可以根据具体需要进行修改,本发明不做限定。

[0123]

实施例三

[0124]

针对实施例二中的检索电路,本发明还提供另一种实施方案。

[0125]

如图12所示,本发明提供一种最小值和次最小值检索电路,对并行输入2n个互不相同的输入数据检索出其中的最小值和次最小值,n大于等于1,包括n级比较电路;

[0126]

第一级比较电路包括2

n-1

个结构相同的第一级比较单元,其中,第1个第一级比较单元包括输入端[din_1、din_2]、输出端[smin_1_1、min_1_1],输入端[din_1、din_2]对应输入数据中的最小值由min_1_1输出,次小值由smin_1_1输出;第2个第一级比较单元包括输入端[din_3、din_4]、输出端[smin_1_2、min_1_2],输入端[din_3、din_4]对应输入数据中的最小值由min_1_2输出,次小值由smin_1_2输出;依此类推,第2

n-1

个第一级比较单元包括输入端[din_2

n-1、din_2n]、输出端[smin_1_2

n-1

、min_1_2

n-1

],输入端[din_2

n-1、din_2n]对应输入数据中的最小值由min_1_2

n-1

输出,次小值由smin_1_2

n-1

输出;

[0127]

第二级比较电路包括2

n-2

个结构相同的第二级比较单元,其中,第1个第二级比较单元包括的输入端与第一级比较电路的输出端[smin_1_1、smin_1_2、min_1_1、min_1_2]相对应,以及包括输出端[smin_2_1、min_2_1];第2个第二级比较单元包括的输入端与第一级比较电路的输出端[smin_1_3、smin_1_4、min_1_3、min_1_4]相对应,以及包括输出端[smin_2_2、min_2_2];依此类推,第2

n-2

个第二级比较单元与第一级比较电路的输出端[smin_1_(2

n-1-1)、smin_1_2

n-1

、min_1_(2

n-1-1)、min_1_2

n-1

]相对应,以及包括输出端[smin_2_2

n-2

、min_2_2

n-2

];

[0128]

第三级比较电路包括2

n-3

个结构相同的第三级比较单元,其中,第1个第三级比较单元包括的输入端与第二级比较电路的输出端[smin_2_1、smin_2_2、min_2_1、min_2_2]相对应,以及包括输出端[smin_3_1、min_3_1];第2个第三级比较单元包括的输入端与第二级比较电路的输出端[smin_2_3、smin_2_4、min_2_3、min_2_4]相对应,以及包括输出端[smin_3_2、min_3_2];依此类推,第2

n-3

个第三级比较单元与第二级比较电路的输出端[smin_2_(2

n-2-1)、smin_2_2

n-2

、min_2_(2

n-2-1)、min_2_2

n-2

]相对应,以及包括输出端[smin_3_2

n-3

、min_3_2

n-3

];

[0129]

以此类推,第n级比较电路包括输入端与第n-1级比较电路的输出端[smin_(n-1)_1、smin_(n-1)_2、min_(n-1)_1、min_(n-1)_2]相对应,以及包括输出端[smin、min];其中输出端min产生输出2n个输入数据中的最小值min,输出端smin产生2n个输入数据中的次小值smin。

[0130]

与实施例二不同点在于,从第二级比较单元开始,在输出端增加次小值比较器,将两个伴随次小值再比较一次,从而使得每一级比较单元输出的伴随次小值个数为1个,而不是n个。相应地,每一级比较单元只有3个选择器,用于输出一个最小值和两个伴随次小值。

[0131]

具体地,以下参考图图5、13、14、15,对本实施例的比较单元进行描述。

[0132]

图5是本实施例的第一级比较单元结构示意图,与实施例二中的第一级比较单元

一致,在此不再赘述。

[0133]

图13是本实施例的第二级比较单元结构示意图,如图13中所示,

[0134]

第二级比较单元包括两个比较器和三个选择器,其中,第一比较器b21包括两个输入端,用于输入第一级比较电路输出的两个第一级最小值,第一比较器b21的输出端分别电连接三个选择器的选择控制端;其中,第一选择器s21的第一输入端电连接第一比较器b21的第一输入端,第一选择器s21的第二输入端电连接第一比较器b21的第二输入端;第二选择器s22的第一输入端电连接第一比较器b21的第二输入端,第二选择器s22的第二输入端电连接第一比较器b21的第一输入端;第三选择器s23的第一输入端和第二输入端分别用于对应输入第一级比较电路输出的两个相邻的第一级伴随次小值。

[0135]

第一选择器s21的输出端用于输出两个第一级最小值中的最小值,第二选择器s22的输出端用于输出两个第一级最小值中的次小值,第三选择器s23的输出端用于输出最小值对应的上一级伴随次小值。

[0136]

第二比较器b22包括两个输入端,第一选择器s21的输出端电连接第二比较器b22的第一输入端,第二选择器s22的输出端电连接第二比较器b22的第二输入端,其中,第二比较器b22的两个输入端用于输入第一选择器s21和第二选择器s22输出的两个伴随次小值,第二比较器b22的输出端用于输出两个伴随次小值中的较小值,该较小值作为本级比较单元输出的最小值的伴随次小值。

[0137]

例如,若本级(第二级)比较得出最小值min_2_1=min_1_1,则第三选择器s23输出的次小值smin_2_1_1=smin_1_1。这是因为,参考图5输出端所示,smin_1_1为对应的上一级(第一级)最小值min_1_1的次小值,也即min_1_1的伴随次小值。

[0138]

继而,将第三选择器s23输出的伴随次小值与第二选择器s22输出的次小值输入第二比较器b22,经过比较输出较小那个做为本级的最小值的伴随次小值smin_2_1,例如,若smin_2_1_1《smin_2_1_2,smin_2_1=smin_2_1_1。

[0139]

图14是本实施例的第三级比较单元结构示意图,如图14中所示,结构同图13所示的第二级比较单元结构相同,在此不再赘述。

[0140]

图15是本实施例的第n级比较电路结构示意图,如图15中所示,结构同图13所示的第二级比较单元结构相同,区别在于在第n级比较电路的输出端,得到的最小值min和次最小值smin就是最终需要获得的最小值和次最小值,不再进入下一级电路。

[0141]

因此,本方案与实施例二的不同点还在于,不需要次小值比较电路,只需要n级比较电路就可以直接得出最小值和次最小值。

[0142]

相较于实施例二的方案,本实施例的方案额外消耗了n-1个二输入比较器,但省去了m级树形比较的次小值比较电路,依然可以获得真正的最小值和相应的次小值。

[0143]

进一步地,与实施例二类似,为加快其工作速率,在检索电路中插入多级流水线,例如每两级比较电路通过寄存器缓存输出,使得寄存器前后的比较电路可以并行执行逻辑运算,从而在较短时钟周期内便可以找出一组数据中的最小值和相应的次小值。

[0144]

以上仅为本发明的实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构变换,或直接或间接运用在其他相关的技术领域,均包括在本发明的专利保护范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。