1.本公开涉及半导体集成电路技术领域,更具体而言,涉及一种合封芯片、使用方法、设备和介质。

背景技术:

2.随着科技的发展,越来越多的产品都朝着智能化的方向发展,促进了芯片市场的发展。早期受制于技术的限制,成品芯片通常是由一个芯片封装而成的,而现在出现了可将多个芯片封装在一起的多芯片合封技术。一个由多芯片合封技术制造的芯片简称为合封芯片,引出到合封芯片外部的引脚称为合封引脚。合封芯片将多个芯片合封在一起作为一颗专用的芯片来使用,通常根据通信接口协议将相关的引脚引出到合封芯片外部作为合封引脚。这样,合封芯片在封装后就只能作为一颗专用的芯片来使用,当合封芯片中部分功能损坏时或者因为供需关系原应用场景已经不再需要时,合封芯片只能被废弃使用,这造成了一定的资源浪费,降低了合封芯片的资源利用率。

技术实现要素:

3.为了克服相关技术中存在的问题,本公开实施例提供了一种合封芯片、使用方法、设备和介质,扩展了合封芯片的应用场景,减少了合封芯片的资源浪费,提高了合封芯片的资源利用率。

4.根据本公开实施例的第一方面,提供一种合封芯片,包括:

5.存储器控制器,包括第一引脚,所述第一引脚用于接收外部设备的读/写操作请求;

6.至少一个存储器,所述存储器控制器和所述至少一个存储器相连,所述存储器控制器根据所述读/写操作请求对所述至少一个存储器进行读/写操作,所述至少一个存储器共享第二引脚,所述第二引脚用于从所述至少一个存储器读取数据和/或将数据写入所述至少一个存储器;

7.合封引脚,与所述外部设备相连接,在所述第一引脚与所述合封引脚连接时,实现所述合封芯片的功能,在所述第二引脚与所述合封引脚连接时,实现所述至少一个存储器的功能。

8.可选地,所述合封芯片还包括多路选择器,

9.所述多路选择器包括输入端、输出端和控制端,所述输入端与所述第一引脚和所述第二引脚相连,所述输出端与所述合封引脚相连,所述控制端用于接收控制信号,根据所述控制信号,将所述输出端经所述输入端与所述第一引脚或所述第二引脚相连,

10.当所述输出端与所述第一引脚相连时,实现所述合封芯片的功能;

11.当所述输出端与所述第二引脚相连时,实现所述至少一个存储器的功能。

12.可选地,所述至少一个存储器中每个存储器包括第三引脚,所述第三引脚用于从所述存储器读取数据和/或将数据写入所述存储器,所述合封芯片还包括多路选择器,

13.所述多路选择器包括输入端、输出端和控制端,所述输入端与所述第一引脚和所述至少一个存储器中每个存储器的第三引脚相连,所述输出端与所述合封引脚相连,所述控制端用于接收控制信号,根据所述控制信号,将所述输出端经所述输入端与所述第一引脚或所述第三引脚相连,

14.当所述输出端与所述第一引脚相连时,实现所述合封芯片的功能;

15.当所述输出端与所述第三引脚相连时,实现对应的所述存储器的功能。

16.可选地,所述合封引脚包括第一合封引脚和第二合封引脚,所述第一引脚与所述第一合封引脚相连,所述第二引脚与所述第二合封引脚相连,

17.在所述第一合封引脚与所述外部设备连接,所述第二合封引脚被悬空时,实现所述合封芯片的功能,

18.在所述第二合封引脚与所述外部设备连接,所述第一合封引脚被悬空时,实现所述至少一个存储器的功能。

19.可选地,所述至少一个存储器中每个存储器包括第三引脚,所述第三引脚用于从所述存储器读取数据和/或将数据写入所述存储器,所述合封引脚包括第一合封引脚和至少一个第三合封引脚,所述第一引脚与所述第一合封引脚相连,所述至少一个存储器中每个存储器的第三引脚分别与所述第三合封引脚相连,

20.在所述第一合封引脚与所述外部设备连接,其他合封引脚被悬空时,实现所述合封芯片的功能,

21.在所述第三合封引脚与所述外部设备连接,其他合封引脚被悬空时,实现对应的所述存储器的功能。

22.根据本公开实施例的第二方面,提供一种合封芯片的使用方法,所述合封芯片包括存储器控制器、至少一个存储器和合封引脚,所述存储器控制器包括第一引脚,所述第一引脚用于接收外部设备的读/写操作请求,所述存储器控制器和所述至少一个存储器相连,所述存储器控制器根据所述读/写操作请求对所述至少一个存储器进行读/写操作,所述至少一个存储器共享第二引脚,所述第二引脚用于从所述至少一个存储器读取数据和/或将数据写入所述至少一个存储器,所述合封引脚与所述外部设备相连接,所述使用方法包括:

23.将所述第一引脚与所述合封引脚连接,以实现所述合封芯片的功能;

24.将所述第二引脚与所述合封引脚连接,以实现所述至少一个存储器的功能。

25.可选地,所述合封芯片还包括多路选择器,所述多路选择器包括输入端、输出端和控制端,所述输入端与所述第一引脚和所述第二引脚相连,所述输出端与所述合封引脚相连,所述控制端用于接收控制信号,根据所述控制信号,将所述输出端经所述输入端与所述第一引脚或所述第二引脚相连,所述使用方法包括:

26.将所述输出端与所述第一引脚相连,以实现所述合封芯片的功能;

27.将所述输出端与所述第二引脚相连,以实现所述至少一个存储器的功能。

28.可选地,所述至少一个存储器中每个存储器包括第三引脚,所述第三引脚用于从所述存储器读取数据和/或将数据写入所述存储器,所述合封芯片还包括多路选择器,所述多路选择器包括输入端、输出端和控制端,所述输入端与所述第一引脚和所述至少一个存储器中每个存储器的第三引脚相连,所述输出端与所述合封引脚相连,所述控制端用于接收控制信号,根据所述控制信号,将所述输出端经所述输入端与所述第一引脚或所述第三

引脚相连,所述使用方法包括:

29.将所述输出端与所述第一引脚相连,以实现所述合封芯片的功能;

30.将所述输出端与所述第三引脚相连相连,以实现对应的所述存储器的功能。

31.可选地,所述合封引脚包括第一合封引脚和第二合封引脚,所述第一引脚与所述第一合封引脚相连,所述第二引脚与所述第二合封引脚相连,所述使用方法包括:

32.将所述第一合封引脚与所述外部设备连接,将所述第二合封引脚悬空,以实现所述合封芯片的功能,

33.将所述第二合封引脚与所述外部设备连接,将所述第一合封引脚悬空,以实现所述至少一个存储器的功能。

34.可选地,所述至少一个存储器中每个存储器包括第三引脚,所述第三引脚用于从所述存储器读取数据和/或将数据写入所述存储器,所述合封引脚包括第一合封引脚和至少一个第三合封引脚,所述第一引脚与所述第一合封引脚相连,所述至少一个存储器中每个存储器的第三引脚分别与所述第三合封引脚相连,所述使用方法包括:

35.将所述第一合封引脚与所述外部设备连接,将其他合封引脚悬空,以实现所述合封芯片的功能,

36.将所述第三合封引脚与所述外部设备连接,将其他合封引脚悬空,以实现对应的所述存储器的功能。

37.根据本公开实施例的第三方面,提供一种电子设备,包括:

38.根据上述任一项所述的合封芯片。

39.根据本公开实施例的第四方面,提供一种计算机设备,包括:

40.存储器,用于存储计算机可执行代码;

41.处理器,用于执行所述计算机可执行代码,以实现上述的方法。

42.根据本公开实施例的第五方面,提供一种计算机可读介质,包括计算机可执行代码,所述计算机可执行代码被处理器执行时实现上述的方法。

43.本公开实施例提供的合封芯片、使用方法、设备和介质,合封芯片包括存储器控制器、至少一个存储器和合封引脚,存储器控制器包括用于接收外部设备的读/写操作请求的第一引脚,存储器控制器和至少一个存储器相连,存储器控制器根据读/写操作请求对至少一个存储器进行读/写操作,至少一个存储器共享第二引脚,第二引脚用于从至少一个存储器读取数据和/或将数据写入至少一个存储器,合封引脚与外部设备相连接,在第一引脚与合封引脚连接时,实现合封芯片的功能,在第二引脚与合封引脚连接时,实现所述至少一个存储器作为整体的功能,这样,合封芯片可以实现合封芯片的功能以及至少一个存储器作为整体的功能,应用于多种应用场景,当合封芯片中部分功能损坏时或者因为供需关系原应用场景已经不再需要时,合封芯片可以作为存储器使用,实现存储器的功能,这降低了合封芯片的资源浪费,提高了合封芯片的资源利用率。

附图说明

44.通过参考以下附图对本公开实施例的描述,本公开的上述以及其它目的、特征和优点将更为清楚,在附图中:

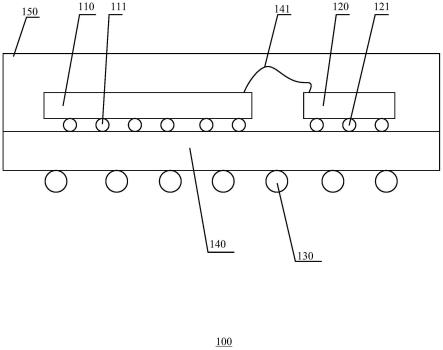

45.图1示出了根据本公开一个实施例的合封芯片的结构示意图;

46.图2示出了根据本公开一个实施例的合封芯片的内部结构示意图;

47.图3示出了根据本公开一个实施例的合封芯片的内部结构示意图;

48.图4示出了根据本公开一个实施例的合封芯片的内部结构示意图;

49.图5示出了根据本公开一个实施例的合封芯片的内部结构示意图;

50.图6示出了根据本公开一个实施例的合封芯片的使用方法的流程示意图;

51.图7示出了根据本公开一个实施例的电子设备的结构示意图;

52.图8示出了根据本公开一个实施例的计算机设备的结构示意图。

具体实施方式

53.以下基于实施例对本公开进行描述,但是本公开并不仅仅限于这些实施例。在下文对本公开的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本公开。为了避免混淆本公开的实质,公知的方法、过程、流程没有详细叙述。另外附图不一定是按比例绘制的,在附图中相同的数字表示相同或相似的元件。

54.图1示出了根据本公开一个实施例的合封芯片的结构示意图。如图1所示,合封芯片100包括:存储器控制器110、至少一个存储器120、合封引脚130、基板140和外壳150,n是正整数,且大于1。需要说明的是,为了方便描述,图1中仅示出一个存储器120。合封芯片100是采用多芯片合封技术将存储器控制器110和至少一个存储器120进行系统级封装形成的一颗专用芯片。在一些实施例中,存储器控制器110例如是微处理器、fpga(field-programmable gate array,现场可编程门阵列)等。存储器120例如是闪存等。合封芯片100可以实现为专用的嵌入式多媒体卡(embedded multi media card,emmc)合封芯片、通用闪存存储(universal flash storage,ufs)合封芯片等。

55.在一些实施例中,如图1所示,存储器控制器110、至少一个存储器120和外壳150设置于基板140的第一表面。存储器控制器110和至少一个芯片120位于外壳150的腔体内,外壳150将存储器控制器110和至少一个存储器120与外界隔绝开来。存储器控制器110包括第一引脚111,第一引脚111接收外部设备的读/写操作请求,存储器控制器110的内部功能电路与第一引脚111相连。存储器控制器110和至少一个存储器120之间通过数据传输线141连接。存储器控制器110根据读/写操作请求对至少一个存储器120进行读/写操作。至少一个存储器120共享第二引脚(图中未示出),第二引脚用于将所述至少一个存储器120作为整体,从所述至少一个存储器120读取数据和/或将数据写入所述至少一个存储器120。在一些实施例中,每个存储器120包括第三引脚121,每个存储器120的内部功能电路与第三引脚121相连。

56.在一些实施例中,如图1所示,合封引脚130设置于基板140的第二表面,合封引脚130与外部设备相连接。在一些实施例中,在存储器控制器110的第一引脚111与合封引脚130连接时,存储器控制器110的第一引脚111与外部设备连接,从而实现合封芯片100的功能。在一些实施例中,在所述至少一个存储器120的第二引脚(图中未示出)与合封引脚130连接时,所述至少一个存储器120的第二引脚与外部设备连接,所述至少一个存储器120作为整体,实现所述至少一个存储器120的功能。在一些实施例中,在存储器120的第三引脚121与合封引脚130连接时,该存储器120的第三引脚121与外部设备连接,从而实现对应的

该存储器120的功能。也即是说,本公开实施例的合封芯片100是一种可以应用于多种应用场景的多功能芯片,当合封芯片100中部分功能损坏时或者因为供需关系原应用场景已经不再需要时,还可以将该合封芯片100应用到将至少一个存储器120作为整体使用的应用场景,以及使用单个存储器120的其它应用场景。

57.ufs存储芯片颗粒是广泛使用到手机产品的芯片;它是将nand flash控制器芯片和nand flash存储芯片封装到一起的。在合封后的ufs存储芯片颗粒上,只留出了ufs协议相关管脚。nand flash控制器芯片和nand flash存储芯片间的通信管脚都没有在封装上留出来。当ufs存储芯片颗粒中的nand flash控制器芯片损坏但nand flash存储芯片正常时,nand flash存储颗粒本身的成本较高,整个芯片颗粒丢弃,资源浪费,也降低了ufs存储芯片的资源利用率。

58.在一些实施例中,合封芯片100为ufs或emmc存储芯片,相应地,存储器控制器110是ufs或者emmc控制器芯片。存储器120可以是nand flash存储芯片。在ufs存储芯片中的ufs控制器芯片或emmc存储芯片中的emmc控制器芯片损坏,而ufs或emmc存储芯片中的nand flash存储芯片正常时,将ufs或emmc存储芯片直接当成nand flash存储颗粒使用,用于开发其他低等级要求的存储产品,例如u盘。可以较大提高一批ufs或emmc存储芯片的利用率,同时可以降低开发u盘额外购买nand flash存储颗粒的成本。

59.图2示出了根据本公开一个实施例的合封芯片的内部结构示意图。如图2所示,合封芯片200包括:存储器控制器210、第1存储器220至第n存储器220、合封引脚230和多路选择器260,n是正整数,且大于1。

60.在一些实施例中,如图2所示,存储器控制器210和第1存储器220至第n存储器220通过数据连接线241相连,存储器控制器210接收外部设备的读/写操作请求且根据读/写操作请求对第1存储器220至第n存储器220进行读/写操作。存储器控制器210包括第一引脚211,每个存储器220包括第三引脚221,第三引脚221用于从存储器220读取数据和/或将数据写入存储器220。合封引脚230与外部设备相连。

61.在一些实施例中,多路选择器260包括输入端261、输出端262和控制端263。输入端261与存储器控制器210的第一引脚211和第1存储器220至第n存储器220中每个存储器220的第三引脚221相连,输出端262与合封引脚230相连。控制端263用于接收控制信号,根据控制信号将输出端262经输入端261与存储器控制器210的第一引脚211或存储器220的第三引脚221相连。当输出端262与第一引脚211相连时,实现合封芯片200的功能,当输出端262与第三引脚221相连时,实现对应的存储器220的功能。

62.在一些实施例中,当控制信号为第一电平时,多路选择器260将输出端262经输入端261与存储器控制器210的第一引脚211相连,从而存储器控制器210的第一引脚211与合封引脚230相连,合封芯片200作为一个专用的合封芯片使用,实现合封芯片200的功能。当控制信号为第二电平时,多路选择器260将输出端262经输入端261与第1存储器220的第三引脚221相连,从而第1存储器220的第三引脚221与合封引脚230相连,合封芯片200作为第1存储器220使用,实现第1存储器220的功能。当控制信号为第三电平时,多路选择器260将输出端262经输入端261与第2存储器220的第三引脚221相连,从而第2存储器220的第三引脚221与合封引脚230相连,合封芯片200作为第2存储器220使用,实现第2存储器220的功能。以此类推,当控制信号为第n 1电平时,多路选择器260将输出端262经输入端261与第n存储

器220的第三引脚221相连,从而第n存储器220的第三引脚221与合封引脚230相连,合封芯片200作为第n存储器220使用,实现第n存储器220的功能。

63.本公开实施例的合封芯片200可以应用于多种应用场景,实现合封芯片200的功能以及第1存储器220至第n存储器220中每个存储器的功能。需要说明的是,图中的第一引脚211、第三引脚221和合封引脚230仅仅是示例性的,第一引脚211、第三引脚221和合封引脚230的数量以及在各自芯片的位置可以根据实际工程需要进行不同的设置。

64.图3示出了根据本公开一个实施例的合封芯片的内部结构示意图。如图3所示,合封芯片300包括:存储器控制器310、第1存储器320至第n存储器320和合封引脚330,n是正整数,且大于1。

65.在一些实施例中,如图3所示,存储器控制器310和第1存储器320至第n存储器320通过数据连接线341相连,存储器控制器310接收外部设备的读/写操作请求且根据读/写操作请求对第1存储器320至第n存储器320进行读/写操作。存储器控制器310包括第一引脚311,每个存储器320包括第三引脚321,第三引脚321用于从存储器320读取数据和/或将数据写入存储器320。合封引脚330与外部设备相连。

66.在一些实施例中,合封引脚330包括第一合封引脚331和至少一个第三合封引脚332(图中示出第三合封引脚332-1至第三合封引脚332-n)。存储器控制器310的第一引脚311与第一合封引脚331相连,第1存储器320至第n存储器320中每个存储器320的第三引脚321分别与第三合封引脚332-1至第三合封引脚332-n相连。在一些实施例中,在第一合封引脚331与外部设备连接,第三合封引脚332被悬空时,实现合封芯片300的功能。

67.在一些实施例中,在与第1存储器320至第n存储器320中一个存储器320的第三引脚321相连的第三合封引脚332与外部设备连接,其他合封引脚被悬空时,实现对应的该存储器320的功能。例如,在与第i存储器320的第三引脚321相连的第三合封引脚332-i与外部设备连接,其他合封引脚被悬空时,实现该第i存储器320的功能,i为整数,i大于等于1且小于等于n。

68.本公开实施例的合封芯片300可以应用于多种应用场景,实现合封芯片300的功能以及第1存储器320至第n存储器320中的每个存储器的功能。需要说明的是,图中的第一引脚311、第三引脚321、第一合封引脚331和第三合封引脚332仅仅是示例性的,第一引脚311、第三引脚321、第一合封引脚331和第三合封引脚332的数量以及在各自芯片的位置可以根据实际工程需要进行不同的设置。

69.图4示出了根据本公开一个实施例的合封芯片的内部结构示意图。如图4所示,合封芯片400包括:存储器控制器410、第1存储器420至第n存储器420、合封引脚430和多路选择器460,n是正整数,且大于1。

70.在一些实施例中,如图4所示,存储器控制器410和第1存储器420至第n存储器420通过数据连接线441相连,存储器控制器410接收外部设备的读/写操作请求且根据读/写操作请求对第1存储器420至第n存储器420进行读/写操作。存储器控制器410包括第一引脚411,第1存储器420至第n存储器420共享第二引脚422。在一个示例中,第1存储器420至第n存储器420与存储器控制器410之间的数据连接线441上设置有第二引脚422,第二引脚422用于将第1存储器420至第n存储器420作为一个整体,从第1存储器420至第n存储器420读取数据和/或将数据写入第1存储器420至第n存储器420。合封引脚430与外部设备相连。

71.在一些实施例中,多路选择器460包括输入端461、输出端462和控制端463。输入端461与存储器控制器410的第一引脚411和第1存储器420至第n存储器420共享的第二引脚422相连,输出端462与合封引脚430相连。控制端463用于接收控制信号,根据控制信号将输出端462经输入端461与第一引脚411或第二引脚422相连。当输出端462经输入端461与第一引脚411相连时,实现合封芯片400的功能,当输出端462经输入端461与第二引脚422相连时,实现第1存储器420至第n存储器420的作为整体的功能。在一些实施例中,当控制信号为第一电平时,多路选择器460将输出端462经输入端461与第一引脚411相连,从而第一引脚411与合封引脚430相连,实现合封芯片400的功能。当控制信号为第二电平时,多路选择器460将输出端262经输入端461与第二引脚422相连,从而第二引脚422与合封引脚430相连,实现第1存储器420至第n存储器420的整体的功能。本公开实施例的合封芯片400可以应用于多种应用场景,实现合封芯片400的功能以及第1存储器420至第n存储器420的整体的功能。需要说明的是,图中的第一引脚411、第二引脚422和合封引脚430仅仅是示例性的,第一引脚411、第二引脚422和合封引脚430的数量以及在各自芯片的位置可以根据实际工程需要进行不同的设置。

72.在一些实施例中,合封芯片400为ufs或emmc存储芯片,相应地,存储器控制器410是ufs或者emmc控制器芯片。存储器420可以是nand flash存储芯片。当通过多路选择器460将合封引脚430连接第一引脚411,可以实现ufs或者emmc接口的存储芯片功能。当通过多路选择器460将合封引脚430连接第二引脚422,可以实现nand flash存储芯片功能。

73.图5示出了根据本公开一个实施例的合封芯片的内部结构示意图。如图5所示,合封芯片500包括:存储器控制器510、第1存储器520至第n存储器520和合封引脚530,n是正整数,且大于1。

74.在一些实施例中,如图5所示,存储器控制器510和第1存储器520至第n存储器520通过数据连接线541相连,存储器控制器510接收外部设备的读/写操作请求且根据读/写操作请求对第1存储器520至第n存储器520进行读/写操作。存储器控制器510包括第一引脚511,第1存储器520至第n存储器520共享第二引脚522。在一个示例中,第1存储器520至第n存储器520与存储器控制器510之间的数据连接线541上设置有第二引脚522,第二引脚522用于将第1存储器520至第n存储器520作为一个整体,从第1存储器520至第n存储器520读取数据和/或将数据写入第1存储器520至第n存储器520。合封引脚530与外部设备相连。

75.在一些实施例中,合封引脚530包括第一合封引脚531和第二合封引脚533。第一引脚511与第一合封引脚531相连,第二引脚522与第二合封引脚533相连。在一些实施例中,在第一合封引脚531与外部设备连接,第二合封引脚533被悬空时,实现合封芯片500的功能。在一些实施例中,在第二合封引脚533与外部设备连接,其他合封引脚被悬空时,实现第1存储器520至第n存储器520作为一个整体的功能。本公开实施例的合封芯片500可以应用于多种应用场景,实现合封芯片500的功能以及第1存储器520至第n存储器520作为一个整体的功能。需要说明的是,图中的第一引脚511、第二引脚522、第一合封引脚531和第二合封引脚533仅仅是示例性的,第一引脚511、第二引脚522、第一合封引脚531和第二合封引脚533的数量以及在各自芯片的位置可以根据实际工程需要进行不同的设置。

76.在一些实施例中,合封芯片500为ufs或emmc存储芯片,相应地,存储器控制器510是ufs或者emmc控制器芯片。存储器520可以是nand flash存储芯片。原来封装好的ufs或

emmc存储芯片颗粒上,只留有ufs/emmc协议相关引脚531,没有留出其他引脚,在ufs或者emmc控制器芯片损坏时,整颗芯片作废,造成开发生产一批ufs或者emmc控制器芯片的成本较高。而nand flash存储芯片本身成本较高,通过额外设计增加第二合封引脚533,本实施例中,第二合封引脚533为nand接口控制引脚,外部设备连接新增的nand接口控制引脚533,悬空ufs/emmc协议相关引脚531,将ufs或emmc存储芯片实现为nand flash存储芯片,可以降低一批合封芯片的整体开发生产成本,提高ufs或emmc存储芯片的利用率。同时,在ufs或者emmc控制器芯片正常时,外部设备连接ufs/emmc协议相关引脚531,悬空新增的nand接口控制引脚533,就可以不影响ufs或emmc存储芯片原有功能。

77.图6示出了根据本公开一个实施例的合封芯片的使用方法的流程示意图。本公开实施例的合封芯片的使用方法应用于上述实施例中的合封芯片。如图6所示,根据本公开一个实施例的合封芯片的使用方法包括:

78.在步骤s610中,将所述第一引脚与所述合封引脚连接,以实现所述合封芯片的功能。

79.在步骤s620中,将所述第二引脚与所述合封引脚连接,以实现所述至少一个存储器的功能。

80.在一些实施例中,所述合封芯片还包括多路选择器,所述多路选择器包括输入端、输出端和控制端,所述输入端与所述第一引脚和所述第二引脚相连,所述输出端与所述合封引脚相连,所述控制端用于接收控制信号,根据所述控制信号,将所述输出端经所述输入端与所述第一引脚或所述第二引脚相连,所述使用方法包括:

81.将所述输出端与所述第一引脚相连,以实现所述合封芯片的功能;

82.将所述输出端与所述第二引脚相连,以实现所述至少一个存储器的功能。

83.在一些实施例中,所述至少一个存储器中每个存储器包括第三引脚,所述第三引脚用于从所述存储器读取数据和/或将数据写入所述存储器,所述合封芯片还包括多路选择器,所述多路选择器包括输入端、输出端和控制端,所述输入端与所述第一引脚和所述至少一个存储器中每个存储器的第三引脚相连,所述输出端与所述合封引脚相连,所述控制端用于接收控制信号,根据所述控制信号,将所述输出端将所述输入端与所述第一引脚或所述第三引脚相连,所述使用方法包括:

84.将所述输出端与所述第一引脚相连,以实现所述合封芯片的功能;

85.将所述输出端与所述第三引脚相连相连,以实现对应的所述存储器的功能。

86.在一些实施例中,所述合封引脚包括第一合封引脚和第二合封引脚,所述第一引脚与所述第一合封引脚相连,所述第二引脚与所述第二合封引脚相连,所述使用方法包括:

87.将所述第一合封引脚与所述外部设备连接,将所述第二合封引脚悬空,以实现所述合封芯片的功能,

88.将所述第二合封引脚与所述外部设备连接,将所述第一合封引脚悬空,以实现所述至少一个存储器的功能。

89.在一些实施例中,所述至少一个存储器中每个存储器包括第三引脚,所述第三引脚用于从所述存储器读取数据和/或将数据写入所述存储器,所述合封引脚包括第一合封引脚和至少一个第三合封引脚,所述第一引脚与所述第一合封引脚相连,所述至少一个存储器中每个存储器的第三引脚分别与所述第三合封引脚相连,所述使用方法包括:

90.将所述第一合封引脚与所述外部设备连接,将其他合封引脚悬空,以实现所述合封芯片的功能,

91.将所述第三合封引脚与所述外部设备连接,将其他合封引脚悬空,以实现对应的所述存储器的功能。

92.上述使用方法的实现细节已经在上文的合封芯片实施例的详细介绍中描述,为节约篇幅,故不赘述。

93.图7示出根据本公开一个实施例的电子设备的结构示意图。如图7所示,电子设备700包括主机710和合封芯片720,主机710和合封芯片720相连。如上文的合封芯片实施例所述的那样,合封芯片720可以包括存储器控制器和至少一个存储器。在一些实施例中,电子设备700中使用合封芯片720的功能,主机710用于从外部接收读/写命令,从合封芯片720中读取数据或将数据写入合封芯片720。在一些实施例中,当合封芯片720中部分功能损坏(例如,合封芯片720中的存储器控制器损坏)时或者因为供需关系原应用场景已经不再需要时,可以将合封芯片720作为其中的至少一个存储器来使用,在电子设备700中使用合封芯片720中至少一个存储器的功能。主机710用于从外部接收读/写命令,从合封芯片720中的至少一个存储器读取数据或将数据写入合封芯片720中的至少一个存储器。

94.图8示出根据本公开一个实施例的计算机设备的结构示意图。图8示出的设备仅仅是一个示例,不应对本公开实施例的功能和使用范围构成任何限制。

95.参考图8,该计算机设备包括通过总线连接的处理器810、存储器820和输入输出设备830。存储器820包括只读存储器(rom)和随机访问存储器(ram),存储器820内存储有执行系统功能所需的各种计算机指令和数据,处理器810从存储器820中读取各种计算机指令以执行各种适当的动作和处理。输入输出设备830包括键盘、鼠标等的输入部分;包括诸如阴极射线管(crt)、液晶显示器(lcd)等以及扬声器等的输出部分;包括硬盘等的存储部分;以及包括诸如lan卡、调制解调器等的网络接口卡的通信部分。存储器820还存储有计算机指令以完成本公开实施例的方法规定的操作。

96.相应地,本公开实施例提供一种计算机可读介质,包括计算机可执行代码,所述计算机可执行代码被处理器执行时实现上述的方法。

97.根据本公开实施例提供的合封芯片、使用方法、设备和介质,合封芯片包括存储器控制器、至少一个存储器和合封引脚,存储器控制器包括用于接收外部设备的读/写操作请求的第一引脚,存储器控制器和至少一个存储器相连,存储器控制器根据读/写操作请求对至少一个存储器进行读/写操作,至少一个存储器共享第二引脚,第二引脚用于从至少一个存储器读取数据和/或将数据写入至少一个存储器,合封引脚与外部设备相连接,在第一引脚与合封引脚连接时,实现合封芯片的功能,在第二引脚与合封引脚连接时,实现所述至少一个存储器作为整体的功能,这样,合封芯片可以实现合封芯片的功能以及至少一个存储器作为整体的功能,应用于多种应用场景,当合封芯片中部分功能损坏时或者因为供需关系原应用场景已经不再需要时,合封芯片可以作为存储器使用,实现存储器的功能,这降低了合封芯片的资源浪费,提高了合封芯片的资源利用率。

98.附图中的流程图、框图图示了本公开实施例的系统、方法、装置的可能的体系框架、功能和操作,流程图和框图上的方框可以代表一个模块、程序段或仅仅是一段代码,所述模块、程序段和代码都是用来实现规定逻辑功能的可执行指令。也应当注意,所述实现规

定逻辑功能的可执行指令可以重新组合,从而生成新的模块和程序段。因此附图的方框以及方框顺序只是用来更好的图示实施例的过程和步骤,而不应以此作为对发明本身的限制。

99.以上所述仅为本公开的一些实施例,并不用于限制本公开,对于本领域技术人员而言,本公开可以有各种改动和变化。凡在本公开的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。