技术特征:

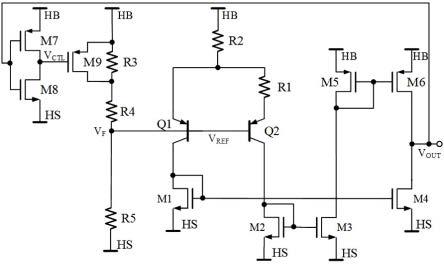

1.一种负压检测电路,其特征在于,该电路包括第一bjt晶体管q1、第二bjt晶体管q2,nmos晶体管m1、nmos晶体管m2、电阻r1和电阻r2,所述第二bjt晶体管q2的发射极与电阻r1的一端相连,电阻r1的另一端同时与第一bjt晶体管q1的发射极和电阻r2的一端相连,电阻r2的另一端与高侧电压hb相连,第一bjt晶体管q1的集电极与nmos晶体管m1的漏极相连,nmos晶体管m1的漏极与栅极相连,构成有源电阻,nmos晶体管m1的源极与高侧电压hs相连,第二bjt晶体管q2的集电极与nmos晶体管m2的漏极相连,第二晶体管m2的漏极与栅极相连,构成有源电阻,第二晶体管m2的源极与高侧电压hs相连,第一bjt晶体管q1的基极与第二bjt晶体管q2的基极相连,使得第一bjt晶体管q1和第二bjt晶体管q2的两条集电极支路电流保持一致,该基极电压为基准电压v

ref

;所述nmos晶体管m1的栅极与nmos晶体管m4的栅极相连,nmos晶体管m4的源极与高侧电压hs相连,构成电流镜电路,所述nmos晶体管m2的栅极与nmos晶体管m3的栅极相连,nmos晶体管m3的源极与高侧电压hs相连,构成电流镜电路;所述nmos晶体管m3的漏极与pmos晶体管m5的漏极相连,pmos晶体管m5的漏极与栅极相连,构成有源电阻,pmos晶体管m5的源极与高侧电压hb相连,pmos晶体管m5的栅极与pmos晶体管m6的栅极相连,pmos晶体管m6的源极与高侧电压hb相连,构成电流镜电路,pmos晶体管m6的漏极与nmos晶体管m4的漏极相连,作为输出端v

out

。2.根据权利要求1所述的负压检测电路,其特征在于,所述输出端v

out

与pmos晶体管m7和nmos晶体管m8的栅极相连,pmos晶体管m7的源极与高侧电压hb相连,nmos晶体管m8的源极与高侧电压hs相连,pmos晶体管m7和nmos晶体管m8的漏极相连,作为反相器的输出端v

ctl

,并且pmos晶体管m7的漏极与pmos晶体管m9的栅极相连,以输出端v

ctl

控制pmos晶体管m9的导通,pmos晶体管m9的源极与高侧电压hb及电阻r3的一端相连,电阻r3的另一端与pmos晶体管m9的漏极及电阻r4的一端相连,电阻r4的另一端通过电阻r5连接高侧电压hs,使得电阻r3、电阻r4和电阻r5形成串联分压。3.根据权利要求2所述的负压检测电路,其特征在于,所述电阻r4与电阻r5相连的公共端作为反馈电压端v

f

连接第一bjt晶体管q1和第二bjt晶体管q2的基极,以反馈电压端v

f

的电压值发生改变,实现带隙基准比较输出。4.根据权利要求3所述的负压检测电路,其特征在于,所述基准电压v

ref

采用与温度无关的带隙基准,带隙基准由正温度系数电压和负温度系数电压相叠加。5.根据权利要求4所述的负压检测电路,其特征在于,所述第一bjt晶体管q1的be结电压表现为负温度系数电压,第一bjt晶体管q1与第二bjt晶体管q2的be结电压差表现为正温度系数电压。

技术总结

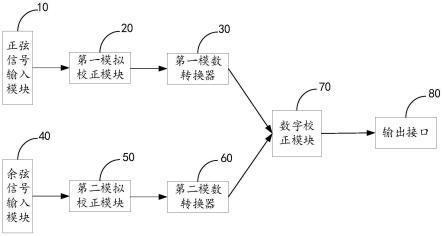

本发明是一种负压检测电路,采用带隙基准电压比较器结构,应用于GaN半桥驱动电路中,为了解决驱动电路负压的影响,抗负压电路采用降压电平移位电路实时监测高侧电压浮动状态并反馈回自举充电回路,使充电时间避开负压时间,高侧负压检测电路采用带隙基准比较器,将带隙基准和电压比较器结合在一起,受温度的影响小,由于使用电流比较,速度快,可以有效避免高侧浮动电源轨的影响。高侧浮动电源轨的影响。高侧浮动电源轨的影响。

技术研发人员:李亮 周德金 侯晓钧 濮旦晨

受保护的技术使用者:清华大学无锡应用技术研究院

技术研发日:2022.08.12

技术公布日:2022/11/25

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。