包括具有在阻焊层之上的互连路由线路的基板的封装件

1.相关申请的交叉引用

2.本专利申请要求于2020年4月6日提交的发明名称为“package comprising a substrate with interconnect routing over solder resist layer”的美国非临时申请no.16/840,752的优先权,该申请已经转让给其受让人并且在此通过引用明确并入本文。

技术领域

3.各种特征涉及包括集成器件的封装件,但更具体地涉及包括集成器件、基板以及位于阻焊层之上的互连件的封装件。

背景技术:

4.图1示出了封装件100,封装件100包括基板102、集成器件104和包封层108。基板102包括至少一个电介质层120、多个互连件122和多个焊料互连件124。多个焊料互连件144耦合到基板102和集成器件104。包封层108包封集成器件104和多个焊料互连件144。制造包括具有高密度互连件的基板的小型封装件可能是有挑战性的。一直存在提供可以容纳高密度互连件和/或高引脚数的更紧凑的封装件的需求。

技术实现要素:

5.各种特征涉及包括集成器件的封装件,但更具体地涉及包括集成器件、基板和位于阻焊层之上的互连件的封装件。

6.一个示例提供了一种封装件,该封装件包括基板和耦合到基板的集成器件。基板包括:(i)至少一个内部电介质层;(ii)位于至少一个内部电介质层中的多个互连件,其中多个互连件包括位于基板的底部金属层上的焊盘;(iii)位于至少一个内部电介质层之上的外部电介质层;(iv)耦合到多个互连件的至少一个路由互连件(routing connect),其中至少一个路由互连件位于外部电介质层之上,其中至少一个路由互连件位于基板的底部金属层之上;以及(v)位于外部电介质层和至少一个路由互连件之上的覆盖电介质层。该封装件包括耦合到位于基板的底部金属层上的焊盘的焊料互连件。

7.另一个示例提供了一种封装件,该封装件包括基板和耦合到基板的集成器件。基板包括:(i)至少一个内部电介质层;(ii)位于至少一个内部电介质层中的多个互连件,其中多个互连件包括位于基板的底部金属层上的焊盘;(iii)位于至少一个内部电介质层之上的外部电介质层;(iv)用于耦合到多个互连件的路由互连件的部件,其中用于路由互连件的部件位于外部电介质层之上,其中用于路由互连件的部件位于基板的底部金属层之上;以及(v)位于外部电介质层和用于路由互连件的部件之上的覆盖电介质层。该封装件包括耦合到位于基板的底部金属层上的焊盘的焊料互连件。

8.又一个示例提供了一种用于制造封装件的方法。该方法提供基板。基板包括:(i)至少一个内部电介质层;(ii)位于至少一个内部电介质层中的多个互连件,其中多个互连件包括位于基板的底部金属层上的焊盘;(iii)位于至少一个内部电介质层之上的外部电

介质层;(iv)耦合到多个互连件的至少一个路由互连件,其中至少一个路由互连件位于外部电介质层之上,其中至少一个路由互连件位于基板的底部金属层之上;以及(v)位于外部电介质层和至少一个路由互连件之上的覆盖电介质层。该方法将集成器件耦合到基板。该方法将焊料互连件耦合到位于基板的底部金属层上的焊盘。

9.再一个示例提供了一种封装件,该封装件包括基板和耦合到基板的集成器件。基板包括:(i)至少一个内部电介质层;(ii)位于至少一个内部电介质层中的多个互连件,其中多个互连件包括位于基板的底部金属层上的焊盘;(iii)位于至少一个内部电介质层之上的外部电介质层;(iv)位于至少一个内部电介质层之上的覆盖电介质层;(v)耦合到多个互连件的至少一个路由互连件,其中至少一个路由互连件位于覆盖电介质层之上,其中至少一个路由互连件位于基板的底部金属层之上;以及(vi)位于覆盖电介质层和至少一个路由互连件之上的第二外部电介质层。该封装件包括耦合到位于基板的底部金属层上的焊盘的焊料互连件。

附图说明

10.当结合附图考虑时,从以下阐述的详细描述,各种特征、性质和优点将变得很清楚,在附图中自始至终以相同的附图标记对应地进行标识。

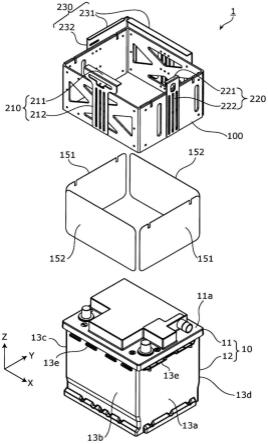

11.图1示出了包括集成器件和基板的封装件的剖面图。

12.图2示出了包括具有位于阻焊层之上的互连件的基板的封装件的剖面图。

13.图3示出了包括具有位于阻焊层之上的互连件的基板的封装件的底部平面图。

14.图4示出了包括具有位于外部电介质层之上的互连件的基板的封装件的剖面图。

15.图5(包括图5a-图5f)示出了用于制造包括位于阻焊层之上的互连件的基板的示例性序列。

16.图6(包括图6a-图6b)示出了用于制造包括位于外部电介质层之上的互连件的基板的示例性序列。

17.图7示出了用于制造包括位于阻焊层之上的互连件的基板的方法的示例性流程图。

18.图8(包括图8a-图8b)示出了用于制造包括具有位于阻焊层之上的互连件的基板的封装件的示例性序列。

19.图9示出了用于制造包括具有位于阻焊层之上的互连件的基板封装件的方法的示例性流程图。

20.图10示出了包括封装件的层叠封装件(pop),该封装件包括具有位于阻焊层之上的互连件的基板。

21.图11(包括图11a-图11c)示出了用于制造包括封装件的层叠封装件(pop)的示例性序列,该封装件包括具有位于阻焊层之上的互连件的基板。

22.图12示出了可以集成本文中描述的管芯、集成器件、集成无源器件(ipd)、无源组件、封装件和/或器件封装件的各种电子设备。

具体实施方式

23.在以下描述中,给出了具体细节以提供对本公开的各个方面的透彻理解。然而,本

领域普通技术人员将理解,可以在没有这些具体细节的情况下实践这些方面。例如,电路可以以框图示出,以避免由于不必要的细节而使各方面难以理解。在其他情况下,可能未详细示出众所周知的电路、结构和技术,以免使本公开的各方面难以理解。

24.本公开描述了一种封装件,该封装件包括基板和耦合到基板的集成器件。基板包括:(i)至少一个内部电介质层;(ii)至少位于至少一个内部电介质层中的多个互连件,其中多个互连件包括位于基板的底部金属层上的焊盘;(iii)位于至少一个内部电介质层之上的外部电介质层;(iv)耦合到多个互连件的至少一个路由互连件,其中至少一个路由互连件位于外部电介质层之上,其中至少一个路由互连件位于基板的底部金属层之上;以及(v)位于外部电介质层和至少一个路由互连件之上的覆盖电介质层,覆盖电介质层可以耦合到外部电介质层。该封装件包括耦合到位于基板的底部金属层上的焊盘的焊料互连件。外部电介质层可以包括阻焊层或光可成像电介质(pid)。覆盖电介质层可以包括阻焊层或光可成像电介质(pid)。至少一个路由互连件可以位于(例如,横向地位于)多个焊料互连件之间。集成器件和基板以这样的方式耦合在一起:使得去往和/或来自集成器件的第一电信号可以被配置为行进通过多个互连件和位于外部电介质层基板之上的至少一个路由互连件。至少一个路由互连件位于外部电介质层之上且位于焊料互连件之间的这种配置,可以允许基板的焊料互连件之间的空间(例如,横向空间)用于路由线路(routing),以提供更多路由线路占用空间而不增加基板和/或封装件的整体尺寸和形式。

25.包括具有位于外部电介质层之上的互连件的基板的示例性封装件

26.图2示出了包括位于外部电介质层之上的互连件的封装件200的剖面图。封装件200通过多个焊料互连件280耦合到板290(例如,印刷电路板(pcb))。封装件200提供具有紧凑的小因子同时还具有改进的路由互连件设计的封装件。

27.如图2所示,封装件200包括基板202、第一集成器件205、第二集成器件206、包封层208和多个焊料互连件280。

28.基板202包括第一表面(例如,顶面)和第二表面(例如,底面)。基板202包括至少一个内部电介质层220、多个互连件222、阻焊层224、外部电介质层230、覆盖电介质层240、和至少一个路由互连件242。多个互连件222至少位于至少一个内部电介质层220中和之上。多个互连件222包括位于基板202的底部金属层上的至少一个焊盘222a。焊盘222a被配置为耦合到多个焊料互连件280中的焊料互连件。外部电介质层230位于至少一个电介质层220之上。至少一个路由互连件242耦合到多个互连件222。至少一个路由互连件242位于外部电介质层230之上。至少一个路由互连件242位于基板202的底部金属层之上(或之下,具体取决于顶部和底部是如何任意定义的)。至少一个路由互连件242可以位于板290与基板202的底部金属层之间。覆盖电介质层240位于外部电介质层230和至少一个路由互连件242之上。至少一个路由互连件242可以是用于路由互连件的部件。覆盖电介质层240可以耦合到外部电介质层230。

29.如本公开中使用的,当特定电介质层位于另一电介质层“之上”时,具体取决于底部(例如,底层)或顶部(例如,顶层)是如何任意定义的,该特定电介质层可以位于另一电介质层上方或下方。位于另一电介质层“之上”(无论是上方还是下方)的特定电介质层可以表示该特定电介质层耦合到另一电介质层的表面。例如,特定电介质层的表面可以与另一电介质层的另一表面接触(例如,触及)。

30.外部电介质层230可以耦合并且位于至少一个内部电介质层220的底面之上(例如,下方)。至少一个路由互连件242和覆盖电介质层240可以耦合并且位于外部电介质层230的底面之上(例如,下方)。至少一个路由互连件242可以横向地位于多个焊料互连件280之间。至少一个路由互连件242可以不与多个焊料互连件280直接接触。至少一个路由互连件242可以耦合到多个互连件222。外部电介质层230、覆盖电介质层240和至少一个路由互连件242可以是基板202的一部分。

31.基板202的底部金属层可以是基板202的金属层,该金属层包括被配置为耦合到焊料互连件的互连件(诸如焊盘)。基板202的底部金属层不一定是基板202的最低金属层或基板202的最靠近板的金属层(当基板202耦合到板时)。在图2的示例中,基板202的底部金属层可以是包括耦合(例如,直接耦合)到多个焊料互连件280的互连件(诸如焊盘222a)的金属层。多个焊料互连件280还耦合到板290(例如,印刷电路板)。基板202的底部金属层可以是最靠近(例如,竖直地最靠近)多个焊料互连件280而不沿着与多个焊料互连件280相同的平面横向地定位(例如,沿着x轴和/或y轴)的金属层。为了本公开的目的,基板的底部金属层可以被定义为不包括位于多个焊料互连件280侧面的(一个或多个)金属层。

32.如图2所示,多个焊料互连件280耦合到基板202(例如,耦合到基板202的底部金属层),使得至少一个路由互连件242位于多个焊料互连件280的侧面和/或位于多个焊料互连件280之间。

33.至少一个路由互连件242的使用有助于节省空间并且有助于减少封装件200的总高度和占用面积,从而利用在其他情况下不会使用的空间。此外,至少一个路由互连件242的使用可以帮助减少基板202中的路由线路拥塞(例如,局部路由路线拥塞)。其中至少一个路由互连件242位于焊料互连件280之间(但可能不与焊料互连件直接接触)的这种配置使用在其他情况下不会使用的空间。特别地,这种配置可以允许基板202的焊料互连件280之间的空间(例如,横向空间)用于路由线路,以提供更多路由线路空间而不增加基板和/或封装件的整体尺寸和形式。

34.注意,至少一个路由互连件242也可以形成在基板202的另一表面(例如,顶面)之上。在这种情况下,另一覆盖电介质层和/或外部电介质可以形成在基板202的第二表面之上。因此,在一些实施方式中,可以在基板202的底面和/或顶面之上形成至少一个路由互连件、覆盖电介质层和/或外部电介质层。

35.外部电介质层230可以包括与至少一个内部电介质层220不同的材料。覆盖电介质层240可以包括与至少一个内部电介质层220不同的材料。覆盖电介质层240可以包括与至少一个内部电介质层220和外部电介质层230不同的材料。覆盖电介质层240和外部电介质层230可以各自包括与至少一个内部电介质层220不同的材料。覆盖电介质层层240和外部电介质层230可以包括相同的材料。

36.至少一个内部电介质层220可以包括覆铜层压板(copper clad laminate,ccl)芯、预浸料(prepreg)、味之素堆积膜(ajinomoto build up film,abf)和/或树脂涂覆铜(resin coated copper,rcc)。外部电介质层230可以包括阻焊层和/或光可成像电介质(pid)。覆盖电介质层240可以包括阻焊层和/或光可成像电介质(pid)。

37.第一集成器件205通过多个互连件250耦合到基板202的第一表面(例如,顶面)。多个互连件250可以包括铜柱和/或焊料互连件。第二集成器件206通过多个互连件260耦合到

基板202的第一表面。多个互连件260可以包括铜柱和/或焊料互连件。包封层208位于基板202的第一表面之上并且耦合到基板202的第一表面,并且可以包封第一集成器件205和第二集成器件206。包封层208可以包括模具材料(mold)、树脂、环氧树脂和/或聚合物。包封层208可以是用于包封的部件。

38.集成器件(例如,205、206)可以包括管芯(例如,半导体裸管芯)。集成器件可以包括射频(rf)器件、无源器件、滤波器、电容器、电感器、天线、发射器、接收器、基于gaas的集成器件、表面声波(saw)滤波器、体声波(baw)滤波器、发光二极管(led)集成器件、基于碳化硅(sic)的集成器件、存储器和/或其组合。

39.不同的实施方式可以将不同的组件耦合到基板202。可以耦合到基板202的其他组件(例如,表面安装的组件)包括无源器件(例如,电容器)。

40.去往和来自集成器件(例如,205、206)的一些电信号(例如,第一电信号、第二电信号)可以行进通过多个互连件222和至少一个路由互连件242。例如,去往和/或来自集成器件的一些信号可以行进通过多个互连件222中的第一多个互连件、至少一个路由互连件242、和多个互连件222中的第二多个互连件。至少一个路由互连件242可以允许封装件200提供更高的i/o引脚计数,而不必增加封装件200的尺寸。例如,使用至少一个路由互连件242可以允许基板202具有更少数目的金属层,这可以帮助降低封装件200的整体高度。至少一个路由互连件242可以帮助减少基板202的某些区域(例如,靠近集成器件的区域)中由于引脚计数和/或网表(netlist)数目较多而引起的拥塞和/或缠结。网表是电路的组件的布置以及组件如何电耦合在一起。

41.不同的实施方式可以包括具有不同数目的金属层的基板。此外,不同的实施方式可以包括具有不同形状和/或尺寸的基板。基板202可以包括核心层。基板202可以是无芯基板。基板202可以使用不同的制造工艺来制造,包括半加法工艺(semi-additive process,sap)和修改的半加法工艺(msap)。多个互连件222和至少一个路由互连件242可以具有不同的形状和/或尺寸。在一些实施方式中,多个互连件222可以包括再分布互连件。在一些实施方式中,至少一个路由互连件242可以包括至少一个路由再分布互连件。再分布互连件可以使用再分布层(rdl)制造工艺来制造。用于制造基板的方法的示例在下面在图5a-图5f和图6a-图6b中示出和描述。

42.图3示出了封装件200的示例性底部平面图。如图3所示,多个焊料互连件280耦合到基板202。基板202包括外部电介质层230、至少一个路由互连件242和覆盖电介质层240。至少一个路由互连件242位于外部电介质层230之上。覆盖电介质层240位于至少一个路由互连件242和外部电介质层230之上。至少一个路由互连件242位于(例如,横向地位于)多个焊料互连件280之间。至少一个路由互连件242(可以包括至少一个路由焊盘、至少一个路由迹线和/或至少一个路由过孔)可以在外部电介质层230的表面中和/或沿着外部电介质层230的表面行进。至少一个路由互连件242可以位于(例如,横向地位于)多个焊料互连件280之间。

43.图4示出了包括基板402的封装件400。封装件400类似于封装件200,并且因此包括与封装件200类似的组件。基板402类似于基板202,并且因此包括与基板202类似的组件。基板402包括第一表面(例如,顶面)和第二表面(例如,底面)。基板402包括至少一个内部电介质层220、多个互连件222、阻焊层224、外部电介质层230、外部电介质层430、覆盖电介质层

240、和至少一个路由互连件242。多个互连件222至少位于至少一个内部电介质层220中和之上。多个互连件222包括位于基板402的底部金属层上的至少一个焊盘222a。焊盘222a被配置为耦合到多个焊料互连件280中的焊料互连件。至少一个路由互连件242耦合到多个互连件222。至少一个路由互连件242位于覆盖电介质层240之上。至少一个路由互连件242位于基板402的底部金属层之上(或之下,具体取决于顶部和底部是如何任意定义的)。外部电介质层230可以位于至少一个内部电介质层220之上。外部电介质层230可以位于覆盖电介质层240的横向上。外部电介质层430位于覆盖电介质层240和至少一个路由互连件242之上。外部电介质层430可以是第二外部电介质层。外部电介质层430可以被认为是外部电介质层230的一部分,反之亦然。因此,在一些实施方式中,外部电介质层(其可以包括外部电介质层230和外部电介质层430)可以位于至少一个内部电介质层220、覆盖电介质层240和至少一个路由互连件242之上(例如,下方)。覆盖电介质激光器240可以位于至少一个内部电介质层220与外部电介质层430之间。覆盖电介质激光器240可以耦合到至少一个内部电介质层220和外部电介质层430。

44.如本公开中使用的,当特定电介质层位于另一电介质层“之上”时,具体取决于底部(例如,底层)或顶部(例如,顶层)是如何任意定义的,该特定电介质层可以位于另一电介质层上方或下方。位于另一电介质层“之上”(无论是上方还是下方)的特定电介质层可以表示该特定电介质层耦合到另一电介质层的表面。例如,特定电介质层的表面可以与另一电介质层的另一表面接触(例如,触及)。

45.外部电介质层230可以耦合并且位于至少一个内部电介质层220的底面之上(例如,下方)。覆盖电介质层240可以耦合并且位于至少一个内部电介质层220的底面之上(例如,下方)。覆盖电介质层240可以与外部电介质层230共面。至少一个路由互连件242可以耦合并且位于覆盖电介质层240的底面之上(例如,下方)。外部电介质层430可以位于覆盖电介质层240的底面和至少一个路由互连件242之上(例如,下方)。至少一个路由互连件242可以横向地位于多个焊料互连件280之间。至少一个路由互连件242可以不与多个焊料互连件280直接接触。至少一个路由互连件242可以耦合到多个互连件222。外部电介质层230、外部电介质层430、覆盖电介质层240、和至少一个路由互连件242可以是基板402的一部分。

46.注意,至少一个路由互连件242也可以形成在基板402的第一表面(例如,顶面)之上。在这种情况下,可以在基板402的第一表面之上形成另一覆盖电介质层和/或外部电介质。因此,在一些实施方式中,可以在基板402的底面和/或顶面之上形成至少一个路由互连件、覆盖电介质层和/或外部电介质层。

47.外部电介质层(例如,230、430)可以包括与至少一个内部电介质层220不同的材料。覆盖电介质层240可以包括与至少一个内部电介质层220不同的材料。覆盖电介质层240可以包括与至少一个内部电介质层220和外部电介质层(例如,230、430)不同的材料。覆盖电介质层240和外部电介质层(例如,230、430)可以各自包括与至少一个内部电介质层220不同的材料。覆盖电介质层240和外部电介质层(例如,230、430)可以包括相同的材料。

48.已经描述了具有路由互连件的各种封装件,现在将在下面描述用于制造具有路由互连件的基板的过程。

49.用于制造包括路由互连件的基板的示例性序列

50.在一些实施方式中,制造基板包括若干过程。图5(包括图5a-图5f)示出了用于提

供或制造基板的示例性序列。在一些实施方式中,图5a-图5f的序列可以用于提供或制造图2的基板202。然而,图5a-图5f的过程可以用于制造本公开中描述的任何基板。

51.应当注意,图5a-图5f的序列可以组合一个或多个阶段以简化和/或阐明用于提供或制造基板的序列。在一些实施方式中,可以改变或修改过程的顺序。在一些实施方式中,可以替换或替代一个或多个过程而不背离本公开的精神。

52.如图5a所示,阶段1示出了在提供载体500并且在载体500之上形成金属层之后的状态。金属层可以被图案化以形成互连件502。镀覆工艺和蚀刻工艺可以用于形成金属层和互连件。

53.阶段2示出了在载体500和互连件502之上形成电介质层520之后的状态。电介质层520可以包括聚酰亚胺。然而,不同的实施方式可以将不同的材料用于电介质层。电介质层520可以是内部电介质层。

54.阶段3示出了在电介质层520中形成至少一个腔体510之后的状态。至少一个腔体510可以使用蚀刻工艺(例如,光刻工艺)或激光工艺来形成。

55.阶段4示出了在电介质层520中和之上形成互连件512之后的状态。例如,可以形成过孔、焊盘和/或迹线。镀覆工艺可以用于形成互连件。互连件512可以是多个互连件222的一部分。

56.阶段5示出了在电介质层520之上形成另一电介质层522之后的状态。电介质层522可以是与电介质层520相同的材料。然而,不同的实施方式可以将不同的材料用于电介质层。电介质层522可以是内部电介质层。

57.如图5b所示,阶段6示出了在电介质层522中形成至少一个腔体530之后的状态。蚀刻工艺或激光工艺可以用于形成至少一个腔体530。

58.阶段7示出了在电介质层522中和之上形成互连件514之后的状态。例如,可以形成过孔、焊盘和/或迹线。镀覆工艺可以用于形成互连件。互连件514可以是多个互连件222的一部分。

59.阶段8示出了在电介质层522之上形成另一电介质层524之后的状态。电介质层524可以是与电介质层520相同的材料。然而,不同的实施方式可以使用不同的材料用于电介质层。电介质层524可以是内部电介质层。

60.阶段9示出了在电介质层524中形成至少一个腔体540之后的状态。蚀刻工艺或激光工艺可以用于形成至少一个腔体540。

61.如图5c所示,阶段10示出了在电介质层524中和之上形成互连件516之后的状态。例如,可以形成过孔、焊盘和/或迹线。镀覆工艺可以用于形成互连件。

62.互连件502、512、514和/或516中的一些或全部可以限定基板202的多个互连件222。电介质层520、522、524可以由至少一个内部电介质层220表示。

63.阶段11示出了在载体500从至少一个内部电介质层220解耦(例如,去除、磨光)以留下基板202之后的状态。

64.阶段12示出了在基板202之上形成阻焊层224和外部电介质层230之后的状态。沉积工艺可以用于将阻焊层224和外部电介质层230设置在基板202之上。例如,阻焊层224可以设置在至少一个内部电介质层220的第一表面(例如,顶面)之上(例如,上方),并且外部电介质层230可以设置在至少一个内部电介质层220的第二表面(例如,底面)之上(例如,下

方)。顶面和底面可以任意定义。不同的实施方式可以不同地定义顶部或底部。

65.如图5d所示,阶段13示出了在外部电介质层230中形成腔体560之后的状态。激光工艺和/或蚀刻工艺可以用于形成腔体560。

66.阶段14示出了在外部电介质层230之上形成掩模570之后的状态。

67.阶段15示出了在掩模570的部分被打开以暴露外部电介质层230的部分和多个互连件222中的一些互连件之后的状态。蚀刻工艺可以用于打开掩模570的部分。

68.如图5e所示,阶段16示出了在外部电介质层230中和之上形成至少一个路由互连件242之后的状态。例如,可以形成路由过孔、路由焊盘和/或路由迹线。镀覆工艺可以用于形成路由互连件。

69.阶段17示出了在至少一个路由互连件242和外部电介质层230之上形成覆盖电介质层240之后的状态。沉积工艺可以用于将覆盖电介质层240设置在至少一个路由互连件242和外部电介质层230之上。

70.如图5f所示,阶段18示出了在去除掩膜570之后的状态。蚀刻工艺可以用于去除或耦合掩模570。

71.阶段19示出了在焊料互连件(多个焊料互连件280中的焊料互连件)耦合到多个互连件222之后的状态。焊料互连件280可以耦合到焊盘222a(其是多个互连件222的一部分)。焊盘222a可以位于基板202的底部金属层上。阶段19可以示出基板202,基板202包括位于焊料互连件280之间的至少一个路由互连件242,如图2中所述。

72.不同的实施方式可以使用不同的工艺来形成(一个或多个)金属层。在一些实施方式中,化学气相沉积(cvd)工艺和/或物理气相沉积(pvd)工艺可以用于形成(一个或多个)金属层。例如,溅射工艺、喷涂工艺和/或镀覆工艺可以用于形成(一个或多个)金属层。

73.用于制造包括路由互连件的基板的示例性序列

74.在一些实施方式中,制造基板包括若干过程。图6(包括图6a-图6b)示出了用于提供或制造基板的示例性序列。在一些实施方式中,图6a-图6b的序列可以用于提供或制造图4的基板402。然而,图6a-图6b的过程可以用于制造本公开中描述的任何基板。

75.应当注意,图6a-图6b的序列可以组合一个或多个阶段以简化和/或阐明用于提供或制造基板的序列。在一些实施方式中,可以改变或修改过程的顺序。在一些实施方式中,可以替换或替代一个或多个过程而不背离本公开的精神。

76.如图6a所示,阶段1示出了在提供包括至少一个内部电介质层220和多个互连件222的基板402之后的状态。图6a的阶段1的基板402可以类似于图5c的阶段11的基板202。在一些实施方式中,图6a的阶段1的基板402可以如图5a-图5c的阶段1-11中示出和描述的那样制造。

77.阶段2示出了在基板402之上形成阻焊层224和覆盖电介质层240之后的状态。沉积工艺可以用于将阻焊层224和覆盖电介质层240设置在基板402之上。

78.阶段3示出了在覆盖电介质层240的部分被去除并且在覆盖电介质层240中形成腔体640之后的状态。激光工艺和/或蚀刻工艺可以用于形成腔体640和/或去除覆盖电介质层240的部分。

79.如图6b所示,阶段4示出了在覆盖电介质层240中和之上形成至少一个路由互连件242之后的状态。例如,可以形成路由过孔、路由焊盘和/或路由迹线。镀覆工艺可以用于形

成路由互连件。

80.阶段5示出了在至少一个路由互连件242和覆盖电介质层240之上形成外部电介质层230之后的状态。沉积工艺可以用于将外部电介质层230设置在至少一个路由互连件242和覆盖电介质层240之上。激光工艺和/或蚀刻工艺可以用于在外部电介质层230中形成腔体630。

81.阶段6示出了在焊料互连件(多个焊料互连件280中的焊料互连件)耦合到多个互连件222之后的状态。焊料互连件280可以耦合到焊盘222a(其是多个互连件222的一部分)。焊盘222a可以位于基板402的底部金属层上。阶段6可以示出基板402,基板402包括位于焊料互连件280之间的至少一个路由互连件242,如图4中所述。

82.不同的实施方式可以使用不同的工艺来形成(一个或多个)金属层。在一些实施方式中,化学气相沉积(cvd)工艺和/或物理气相沉积(pvd)工艺可以用于形成(一个或多个)金属层。例如,溅射工艺、喷涂工艺和/或镀覆工艺可以用于形成(一个或多个)金属层。

83.用于制造基板的方法的示例性流程图

84.在一些实施方式中,制造基板包括若干过程。图7示出了用于提供或制造基板的方法700的示例性流程图。在一些实施方式中,图7的方法700可以用于提供或制造图2的基板。例如,图7的方法可以用于制造基板202和/或基板402。

85.应当注意,图7的方法可以组合一个或多个过程以简化和/或阐明用于提供或制造基板的方法。在一些实施方式中,可以改变或修改过程的顺序。

86.该方法(在705处)提供载体500。不同的实施方式可以将不同的材料用于载体。载体可以包括基板、玻璃、石英和/或载带(carrier tape)。图5a的阶段1示出了在提供载体之后的状态。

87.该方法(在710处)在载体500之上形成金属层。金属层可以被图案化以形成互连件。镀覆工艺可以用于形成金属层和互连件。图5a的阶段1示出了在形成金属层和互连件502之后的状态。

88.该方法(在715处)在载体500和互连件502之上形成至少一个内部电介质层(例如,电介质层520)。电介质层520可以包括聚酰亚胺。形成电介质层还可以包括在电介质层520中形成多个腔体(例如,510)。沉积工艺可以用于形成至少一个内部电介质层。多个腔体可以使用蚀刻工艺(例如,光刻)或激光工艺来形成。图5a的阶段2-3示出了形成电介质层和电介质层中的腔体。

89.该方法(在720处)在内部电介质层中和之上形成互连件。例如,互连件512可以形成在电介质层520中和之上。镀覆工艺可以用于形成互连件。形成互连件可以包括在电介质层之上和/或中提供图案化的金属层。图5a的阶段4示出了在电介质层中和之上形成互连件的示例。

90.在一些实施方式中,可以形成若干内部电介质层(例如,522、524),并且在内部电介质层中和之上形成若干互连件。图5a-图5c的阶段2-10示出了形成至少一个内部电介质层和在(一个或多个)内部电介质层中和之上形成多个互连件的示例。

91.该方法(在725处)在至少一个内部电介质层220和多个互连件222之上形成外部电介质层230。外部电介质层230可以包括阻焊层或光可成像电介质(pid)。沉积工艺可以用于形成外部电介质层230。形成外部电介质层还可以包括在外部电介质层230中形成多个腔体

(例如,530)。多个腔体可以使用蚀刻工艺或激光工艺来形成。图5c-图15d的阶段12-13示出了形成外部电介质层和在外部电介质层中形成腔体。

92.该方法(在730处)在外部电介质层中和/或之上形成路由互连件。例如,可以形成至少一个路由互连件242。镀覆工艺可以用于形成路由互连件。形成路由互连件可以包括在外部电介质层230之上提供图案化的金属层。图5d-图5e的阶段14-16可以示出在外部电介质层中和之上形成互连件的示例。

93.该方法(在735处)在外部电介质层230和至少一个路由互连件242之上形成覆盖电介质层(例如,240)。覆盖电介质层240可以包括阻焊层或光可成像电介质(pid)。沉积工艺可以用于形成覆盖电介质层240。图5e-图5f的阶段17-19可以示出形成覆盖电介质层的示例。

94.如上所述,该方法可以以不同顺序形成电介质层。例如,在一些实施方式中,可以在形成至少一个外部电介质层之前形成至少一个覆盖电介质层。这样的示例至少在上面的6a-图6b中描述。不同的实施方式可以使用不同工艺来形成(一个或多个)金属层。在一些实施方式中,化学气相沉积(cvd)工艺和/或物理气相沉积(pvd)工艺可以用于形成(一个或多个)金属层。例如,溅射工艺、喷涂工艺和/或镀覆工艺可以用于形成(一个或多个)金属层。

95.用于制造包括基板的封装件的示例性序列,该基板具有位于外部电介质层之上的互连件

96.图8(包括图8a-图8b)示出了用于提供或制造包括基板的封装件的示例性序列。在一些实施方式中,图8a-图8b的序列可以用于提供或制造包括图2的基板202的封装件200或本公开中描述的任何封装件。

97.应当注意,图8a-图8b的序列可以组合一个或多个阶段以简化和/或阐明用于提供或制造封装件的序列。在一些实施方式中,可以改变或修改过程的顺序。在一些实施方式中,可以替换或替代一个或多个过程而不背离本公开的精神。图8a-图8b的序列可以用于一次制造一个或多个封装件(作为晶圆的一部分)。

98.如图8a所示,阶段1示出了在提供基板202之后的状态。基板202可以由供应商提供或制造。与图5a-图5f所示的过程类似的过程可以用于制造基板202。然而,不同的实施方式可以使用不同的工艺来制造基板202。可以用于制造基板202的工艺示例包括半加法工艺(sap)和修改的半加法工艺(msap)。

99.基板202包括第一表面(例如,顶面)和第二表面(例如,底面)。基板202包括至少一个内部电介质层220、多个互连件222、阻焊层224、外部电介质层230、覆盖电介质层240、和至少一个路由互连件242。多个互连件222至少位于至少一个内部电介质层220中和之上。多个互连件222包括位于基板202的底部金属层上的至少一个焊盘222a。焊盘222a被配置为耦合到多个焊料互连件280中的焊料互连件。外部电介质层230位于至少一个内部电介质层220之上。至少一个路由互连件242耦合到多个互连件222。至少一个路由互连件242位于外部电介质层230之上。至少一个路由互连件242位于基板202的底部金属层之上(或下方,具体取决于顶部和底部是如何任意定义的)。覆盖电介质层240位于外部电介质层230和至少一个路由互连件242之上。

100.阶段2示出了在多个焊料互连件280耦合到基板202之后的状态。焊料互连件280可以耦合到基板202的底部金属层。例如,焊料互连件280可以耦合到基板202的焊盘222a(其

位于底部金属层上)。回流工艺可以用于将焊料互连件280耦合到基板202。

101.如图8b所示,阶段3示出了在第一集成器件205通过多个互连件250耦合到基板202的第一表面(例如,顶面)之后的状态。多个互连件250可以耦合到基板202的多个互连件222中的互连件。阶段3还示出了在第二集成器件206通过多个互连件260耦合到基板202的第一表面(例如,顶面)之后的状态。多个互连件260可以耦合到基板202的多个互连件222中的互连件。回流工艺可以用于将第一集成器件205和/或第二集成器件206耦合到基板202。

102.阶段4示出了在基板202的第一表面之上形成包封层208以使得包封层208包封第一集成器件205和第二集成器件206之后的状态。形成和/或设置包封层208的工艺可以包括使用压缩和传递模塑工艺(compression and transfer molding process)、片材模塑工艺(sheet molding process)或液体模塑工艺(liquid molding process)。阶段4可以示出包括基板202、第一集成器件205、第二集成器件206和包封层208的封装件200。

103.本公开中描述的封装件(例如,200、400)可以一次一个地被制造,或者可以一起被制造为一个或多个晶圆的一部分,并且然后单个化(singulate)成个体封装件。

104.用于制造包括具有位于外部电介质层之上的互连件的基板的封装件的方法的示例性流程图

105.在一些实施方式中,制造包括基板的封装件包括若干过程。图9示出了用于提供或制造包括基板的封装件的方法900的示例性流程图。在一些实施方式中,图9的方法900可以用于提供或制造在本公开中描述的图2的封装件200。然而,方法900可以用于提供或制造本公开中描述的任何封装件。

106.应当注意,图9的方法可以组合一个或多个过程以简化和/或阐明用于提供或制造基板的封装件的方法。在一些实施方式中,可以改变或修改过程的顺序。

107.该方法(在905处)提供基板(例如,202、402)。基板202可以由供应商提供或制造。基板202包括第一表面(例如,顶面)和第二表面(例如,底面)。基板202可以包括至少一个内部电介质层220、多个互连件222、阻焊层224、外部电介质层230、覆盖电介质层240、和至少一个路由互连件242。多个互连件222至少位于至少一个内部电介质层220中和之上。多个互连件222包括位于基板202的底部金属层上的至少一个焊盘222a。焊盘222a被配置为耦合到多个焊料互连件280中的焊料互连件。外部电介质层230位于至少一个内部电介质层220之上。至少一个路由互连件242耦合到多个互连件222。至少一个路由互连件242位于外部电介质层230之上。至少一个路由互连件242位于基板202的底部金属层下方。覆盖电介质层240位于外部电介质层230和至少一个路由互连件242之上。

108.不同的实施方式可以提供不同的基板。与图5a-图5f所示的过程类似的过程可以用于制造基板202。然而,不同的实施方式可以使用不同工艺来制造基板202。图8a的阶段1示出并且描述了提供基板的示例。

109.该方法(在910处)将多个焊料互连件(例如,280)耦合到基板(例如,202)。焊料互连件280可以耦合到基板202的底部金属层。例如,焊料互连件280可以耦合到基板202的焊盘222a(其位于底部金属层上)。回流工艺可以用于将焊料互连件280耦合到基板202。图8a的阶段2示出和描述了将焊料互连件耦合到基板的示例。

110.该方法(在915处)将组件耦合到基板(例如,202)。例如,该方法可以通过多个互连件250将第一集成器件205耦合到基板202的第一表面(例如,顶面)。多个互连件250可以耦

合到多个互连件222中的互连件。该方法可以通过多个互连件260将第二集成器件206耦合到基板202的第一表面(例如,顶面)。多个互连件260可以耦合到基板202的多个互连件222中的互连件。回流工艺可以用于将第一集成器件205和/或第二集成器件206耦合到基板202。图8b的阶段3示出并且描述了将组件耦合到基板的示例。

111.该方法(在925处)在基板(例如,202)的第一表面之上形成包封层(例如,208)。包封层可以形成在基板的第一表面之上,使得包封层208包封第一集成器件205和第二集成器件206(它们是组件的示例)。形成和/或设置包封层208的工艺可以包括使用压缩和传递模塑工艺、片材模塑工艺或液体模塑工艺。图8b的阶段4示出并且描述了位于基板之上并且包封集成器件的包封层的示例。

112.包括封装件的示例性层叠封装件(pop),该封装件包括具有位于外部电介质层之上的互连件的基板

113.图10示出了层叠封装件(pop)1000的剖面图,pop 1000包括封装件1001和封装件1003,封装件1001和封装件1003包括位于外部电介质层之上的互连件。封装件1001通过多个焊料互连件1080耦合到封装件1003。封装件1001位于封装件1003之上。pop 1000通过封装件1003的多个焊料互连件280耦合到板290(例如,印刷电路板(pcb))。封装件1003提供具有紧凑的小因子同时还具有改进的路由互连件设计的封装件。

114.图10的封装件1003类似于图2的封装件200,并且因此包括与封装件200类似的组件。封装件1003包括行进通过包封层208的多个过孔1088。多个过孔1088可以包括穿模过孔(through mold via,tmv)。多个过孔1088耦合到多个互连件222。封装件1003包括位于包封层208之上的多个上部路由互连件1042。多个上部路由互连件1042可以耦合到多个过孔1088。上部覆盖电介质层1040位于多个上部路由互连件1042和包封层208之上。多个上部路由互连件1042位于(例如,横向地位于)在多个焊料互连件1080之间。多个路由互连件1042可以是用于上部路由互连件的部件。包封层1070可以位于封装件1001与封装件1003之间。

115.封装件1001包括基板1002、集成器件1006和包封层1008。基板1002包括至少一个电介质层1020和多个互连件1022。集成器件1006耦合到基板1002。包封层1008耦合到基板1002并且包封集成器件1006。

116.在一些实施方式中,封装件1001可以类似于封装件200,并且因此封装件1001可以包括外部电介质层(例如,230)和/或覆盖电介质层(例如,240)。

117.如本公开中使用的,当特定电介质层位于另一电介质层“之上”时,具体取决于底部(例如,底层)或顶部(例如,顶层)是如何任意定义的,该特定电介质层可以位于另一电介质层上方或下方。位于另一电介质层“之上”(无论是上方还是下方)的特定电介质层可以表示该特定电介质层耦合到另一电介质层的表面。例如,特定电介质层的表面可以与另一电介质层的另一表面接触(例如,触及)。

118.用于制造包括封装件的示例性层叠封装件(pop)的示例性序列,该封装件包括具有位于外部电介质层之上的互连件的基板

119.图11(包括图11a-图11c)示出了用于提供或制造层叠封装件(pop)的示例性序列。在一些实施方式中,图11a-图11c的序列可以用于提供或制造图10的pop 1000或本公开中描述的任何pop。

120.应当注意,图11a-图11c的序列可以组合一个或多个阶段以简化和/或阐明用于提

供或制造pop的序列。在一些实施方式中,可以改变或修改过程的顺序。在一些实施方式中,可以替换或替代一个或多个过程而不背离本公开的精神。图11a-图11c的序列可以用于一次制造一个pop或若干pop(作为晶圆的一部分)。

121.如图11a所示,阶段1示出了在提供或制造封装件200之后的状态。图8a-图8b示出了提供封装件的示例。封装件200可以包括基板,该基板包括至少一个路由互连件、外部电介质层和覆盖电介质层,如图2中所述。

122.阶段2示出了在封装件200的包封层208中形成腔体1110之后的状态。激光工艺和/或蚀刻工艺可以用于在包封层208中形成腔体1110。

123.阶段3示出了在包封层208的腔体1110中形成过孔1088之后的状态。粘贴工艺(pasting process)和/或镀覆工艺可以用于形成过孔1088。过孔1088可以耦合到基板202的多个互连件222。

124.如图11b所示,阶段4示出了在包封层208之上形成多个上部路由互连件1042之后的状态。多个上部路由互连件1042可以耦合到过孔1088。镀覆工艺可以用于形成多个上部路由互连件1042。

125.阶段5示出了在多个上部路由互连件1042和包封层208之上形成上部覆盖电介质层1040之后的状态。沉积工艺可以用于将上部覆盖电介质层1040设置在多个上部路由互连件1042和包封层208之上。上部覆盖电介质层1040可以包括阻焊层或光可成像电介质(pid)。封装件1003可以由封装件200制造而成。

126.如图11c所示,阶段6示出了在通过多个焊料互连件1080将封装件1001耦合到封装件1003之后的状态。回流工艺可以用于将封装件1001耦合到封装件1003。封装件1001包括基板1002、集成器件1006和包封层1008。基板1002包括至少一个电介质层1020和多个互连件1022。集成器件1006耦合到基板1002。包封层1008耦合到基板1002并且包封集成器件1006。封装件1001可以使用与用于制造封装件1003的工艺类似的工艺来制造。

127.阶段7示出了在封装件1001与封装件1003之间形成包封层1070之后的状态。形成和/或设置包封层10070的工艺可以包括使用压缩和传递模塑工艺、片材模塑工艺或液体模塑工艺以在包封层208与基板1002之间形成包封层1070。阶段7示出了包括封装件1001和封装件1003的pop 1000。

128.示例性电子设备

129.图12示出了可以与上述器件、集成器件、集成电路(ic)封装件、集成电路(ic)器件、半导体器件、集成电路、管芯、内插件、封装件、层叠封装件(pop)、系统级封装件(sip)或片上系统(soc)中的任何一者集成的各种电子设备。例如,移动电话设备1202、膝上型计算机设备1204、固定位置终端设备1206、可穿戴设备1208或机动车辆1210可以包括如本文所述的器件1200。例如,器件1200可以是本文中描述的任何器件和/或集成电路(ic)封装件。图12所示的器件1202、1204、1206和1208以及车辆1210仅是示例性的。其他电子设备也可以以器件1200为特征,包括但不限于包括以下各项的一组设备(例如,电子设备):移动设备、手持个人通信系统(pcs)单元、诸如个人数字助理的便携式数据单元、支持全球定位系统(gps)的设备、导航设备、机顶盒、音乐播放器、视频播放器、娱乐单元、诸如抄表设备的固定位置数据单元、通信设备、智能手机、平板电脑、计算机、可穿戴设备(例如,手表、眼镜)、物联网(iot)设备、服务器、路由器、在机动车辆(例如,自动驾驶汽车)中实现的电子设备、或

者存储或检索数据或计算机指令的任何其他设备、或其任何组合。

130.图2-图4、图5a-图5f、图6a-图6b、图7、图8a-图8b、图9-图10、图11a-图11c和/或图12所示的组件、过程、特征和/或功能中的一个或多个可以被重新布置和/或组合成单个组件、过程、特征或功能,或者被体现在若干组件、过程或功能中。在不背离本公开的情况下,还可以添加附加的元件、组件、过程和/或功能。还应当注意,图2-图4、图5a-图5f、图6a-图6b、图7、图8a-图8b、图9-图10、图11a-图11c和/或图12及其在本公开中的对应描述不限于管芯和/或ic。在一些实施方式中,图2-图4、图5a-图5f、图6a-图6b、图7、图8a-图8b、图9-图10、图11a-图11c和/或图12及其对应描述可以用于制造、创建、提供、和/或生产器件和/或集成器件。在一些实施方式中,器件可以包括管芯、集成器件、集成无源器件(ipd)、管芯封装件、集成电路(ic)器件、器件封装件、集成电路(ic)封装件、晶圆、半导体器件、层叠封装件(pop)器件、散热器件和/或内插件。

131.注意,本公开中的附图可以表示各种零件、组件、对象、器件、封装件、集成器件、集成电路和/或晶体管的实际表示和/或概念表示。在某些情况下,这些附图可能不是按比例绘制的。在某些情况下,为了清楚起见,可能未示出所有组件和/或部分。在一些情况下,图中的各个零件和/或组件的定位、位置、尺寸和/或形状可以是示例性的。在一些实施方式中,图中的各种组件和/或零件可以是可选的。

132.本文中使用词语“示例性”来表示“用作示例、实例或说明”。本文中描述为“示例性”的任何实施方式或方面不必被解释为比本公开的其他方面更优选或有利。同样,术语“方面”并不要求本公开的所有方面都包括所讨论的特征、优点或操作模式。本文中使用的术语“耦合”是指两个对象之间的直接或间接耦合。例如,如果对象a与对象b物理接触,而对象b与对象c接触,则对象a和c仍可以被视为彼此耦合-即使它们没有直接物理接触。术语“电耦合”可以表示两个物体直接或间接耦合在一起,使得电流(例如,信号、电源、接地)可以在两个物体之间行进。电耦合的两个物体可以具有或不具有在两个物体之间流动的电流。术语“第一”、“第二”、“第三”和“第四”(和/或高于第四的任何内容)的使用是任意的。所描述的任何组件可以是第一组件、第二组件、第三组件或第四组件。例如,被称为第二组件的组件可以是第一组件、第二组件、第三组件或第四组件。术语“包封”是指对象可以部分包封或完全包封另一对象。术语“顶部”和“底部”是任意的。位于顶部的组件的位置可以在位于底部的组件之上。顶部组件可以被认为是底部组件,反之亦然。如本公开中所述,位于第二组件“之上”的第一组件可以表示第一组件位于第二组件上方或下方,具体取决于底部或顶部是如何任意定义的。在另一示例中,第一组件可以位于第二组件的第一表面之上(例如,上方),并且第三组件可以位于第二组件的第二表面之上(例如,下方),其中第二表面与第一表面相对。还应注意,如在本技术中在一个组件位于另一组件之上的上下文中使用的术语“之上”可以用于表示在另一组件上和/或在另一组件中(例如,在组件的表面上或嵌入在组件中)的组件。因此,例如,在第二组件之上的第一组件可以表示:(1)第一组件在第二组件之上,但不直接触及第二组件;(2)第一组件在第二组件上(例如,在第二组件的表面上);和/或(3)第一组件在(例如,嵌入在)第二组件中。本公开中使用的术语“约

‘

x值

’”

或“大约x值”是指在“x值”的10%以内。例如,约1或大约1的值将表示在0.9-1.1范围内的值。

133.在一些实施方式中,互连件是允许或促进两个点、元件和/或组件之间的电连接的器件或封装件的元件或组件。在一些实施方式中,互连件可以包括迹线、过孔、焊盘、柱、再

分布金属层和/或凸块下金属化(under bump metallization,ubm)层。互连件可以包括一个或多个金属组件(例如,种子层 金属层)。在一些实施方式中,互连件是可以被配置为为电流(例如,数据信号、接地或电源)提供电路径的导电材料。互连件可以是电路的一部分。互连件可以包括一个以上的元件或组件。互连件可以由一个或多个互连件定义。不同的实施方式可以使用类似或不同的工艺来形成互连件。在一些实施方式中,化学气相沉积(cvd)工艺和/或物理气相沉积(pvd)工艺可以用于形成互连件。例如,溅射工艺、喷涂和/或镀覆工艺可以用于形成互连件。

134.此外,应当注意,本文中包含的各种公开内容可以被描述为被描绘为流程图、流程图表、结构图或框图的过程。尽管流程图可以将操作描述为顺序过程,但很多操作可以并行或同时执行。此外,可以重新布置操作的顺序。一个过程在其操作完成时终止。

135.在部背离本公开的情况下,本文中描述的本公开的各种特征可以在不同的系统中实现。应当注意,本公开的上述方面仅仅是示例并且不应当被解释为限制本公开。本公开的各方面的描述旨在说明性的,而不是限制权利要求的范围。因此,本教导可以容易地应用于其他类型的装置,并且很多替代、修改和变化对于本领域技术人员来说将是很清楚的。

136.在下文中,描述了另外的示例以促进对本发明的理解。

137.在一个另外的示例中,描述了一种封装件,该封装件包括:基板,该基板包括:(i)至少一个内部电介质层,(ii)位于至少一个内部电介质层中的多个互连件,其中多个互连件包括位于基板的底部金属层上的焊盘,(iii)位于至少一个内部电介质层之上(例如,位于至少一个内部电介质层的表面之上)的外部电介质层,(iv)耦合到多个互连件的至少一个路由互连件,其中至少一个路由互连件位于外部电介质层之上(例如,位于外部电介质层的表面之上),其中至少一个路由互连件位于基板的底部金属层之上,以及(v)位于外部电介质层和至少一个路由互连件之上的覆盖电介质层;耦合到基板的集成器件;以及耦合到位于基板的底部金属层上的焊盘的焊料互连件。外部电介质层可以包括与至少一个内部电介质层不同的材料。覆盖电介质层可以包括与至少一个内部电介质层不同的材料。覆盖电介质层可以包括与至少一个内部电介质层和外部电介质层不同的材料。此外,覆盖电介质层和外部电介质层各自可以包括与至少一个内部电介质层不同的材料。此外,覆盖电介质层和外部电介质层各自可以包括相同的材料。至少一个内部电介质层可以包括覆铜层压板(ccl)芯、预浸料、味之素堆积膜(abf)和/或树脂涂覆铜(rcc)。此外,外部电介质层和覆盖电介质层各自可以包括阻焊层和/或光可成像电介质(pid)。此外,去往和/或来自集成器件的第一电信号可以被配置为行进通过至少一个路由互连件。此外,封装件可以包括位于基板之上的包封层;位于包封层中的至少一个过孔;耦合到至少一个过孔的至少一个上部路由互连件,其中至少一个上部路由互连件位于包封层之上;以及位于至少一个上部路由互连件和包封层之上的上部覆盖电介质层。去往和/或来自集成器件的第一电信号可以被配置为行进通过至少一个上部路由互连件。此外,该封装件可以是层叠封装件(pop)的一部分。基板的底部金属层可以是竖直地最靠近焊料互连件而不横向地定位在焊料互连件旁边的金属层。该封装件可以被并入到设备中,该设备选自包括以下各项的组:音乐播放器、视频播放器、娱乐单元、导航设备、通信设备、移动设备、移动电话、智能手机、个人数字助理、固定位置终端、平板电脑、计算机、可穿戴设备、笔记本电脑、服务器、物联网(iot)设备和机动车辆中的设备。

138.在又一个另外的示例中,描述了一种装置,该装置包括:基板,该基板包括:(i)至少一个内部电介质层,(ii)位于至少一个内部电介质层中的多个互连件,其中多个互连件包括位于基板的底部金属层上的焊盘,(iii)位于至少一个内部电介质层之上的外部电介质层,(iv)用于耦合到多个互连件的路由互连件的部件,其中用于路由互连件的部件位于外部电介质层之上,其中用于路由互连件的部件位于基板的底部金属层之上,以及(v)位于外部电介质层和用于路由互连件的部件之上的覆盖电介质层;耦合到基板的集成器件;以及耦合到位于基板的底部金属层上的焊盘的焊料互连件。外部电介质层可以包括与至少一个内部电介质层不同的材料。覆盖电介质层可以包括与至少一个内部电介质层不同的材料。覆盖电介质层可以包括与至少一个内部电介质层和外部电介质层不同的材料。覆盖电介质层和外部电介质层各自可以包括与至少一个内部电介质层不同的材料。覆盖电介质层和外部电介质层各自可以包括相同的材料。去往和/或来自集成器件的第一电信号可以被配置为行进通过用于路由互连件的部件。此外,该装置可以包括:位于基板之上的用于包封的部件;位于用于包封的部件中的至少一个过孔;耦合到至少一个过孔的用于上部路由互连件的部件,其中用于上部路由互连件的部件位于用于包封的部件之上;以及位于用于上部路由互连件的部件和用于包封的部件之上的上部覆盖电介质层。此外,去往和/或来自集成器件的第一电信号可以被配置为行进通过用于上部路由互连件的部件。

139.在再一个另外的示例中,可以描述一种用于制造封装件的方法,该方法包括:提供基板,该基板包括:(i)至少一个内部电介质层,(ii)位于至少一个内部电介质层中的多个互连件,其中多个互连件包括位于基板的底部金属层上的焊盘,(iii)位于至少一个内部电介质层之上的外部电介质层,(iv)耦合到多个互连件的至少一个路由互连件,其中至少一个路由互连件位于外部电介质层之上,其中至少一个路由互连件位于基板的底部金属层之上,以及(v)位于外部电介质层和至少一个路由互连件之上的覆盖电介质层;将集成器件耦合到基板;以及将焊料互连件耦合到位于基板的底部金属层上的焊盘。该方法还可以包括:在基板之上形成包封层;在包封层中形成至少一个过孔;在包封层之上形成至少一个上部路由互连件,其中至少一个上部路由互连件耦合到至少一个过孔;以及在至少一个上部路由互连件和包封层之上形成上部覆盖电介质层。

140.在另一示例中,描述了一种封装件,该封装件包括:基板,该基板包括:(i)至少一个内部电介质层,(ii)位于至少一个内部电介质层中的多个互连件,其中多个互连件包括位于基板的底部金属层上的焊盘,(iii)位于至少一个内部电介质层之上(例如,位于至少一个内部电介质层的表面之上)的外部电介质层,(iv)位于至少一个内部电介质层之上(例如,位于至少一个内部电介质层的表面之上)的覆盖电介质层,(v)耦合到多个互连件的至少一个路由互连件,其中至少一个路由互连件位于覆盖电介质层之上(例如,位于覆盖电介质层的表面之上),其中至少一个路由互连件位于基板的底部金属层之上,以及(v)位于覆盖电介质层和至少一个路由互连件之上的第二外部电介质层;耦合到基板的集成器件;以及耦合到位于基板的底部金属层上的焊盘的焊料互连件。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。