1.本实用新型属于电阻抗成像领域,具体地说,是一种模块化高速电阻抗成像装置的独立电极模块。

背景技术:

2.电阻抗成像装置是一种多电极控制系统,低速电阻抗成像装置基本上由4个多路切换开关组成。高速电阻抗成像装置由于需要同时采集,因此需要每一路电极都需要电极放大、数模转换检测处理,使得系统比低速装置复杂了很多。这就带来了应用于不同目的不同的电极数量需要进行不同的系统设计的问题。

3.中国专利cn2010800394959电阻抗成像公开了一种用于电阻抗成像的设备,包括布置在电极载体上的包括重复单元的布置中的电极,重复单元在电极载体上重复并且具有小于90

°

的旋转对称角。

4.中国专利cn112617794a电用于电阻抗成像的测量装置及其测量方法公开了一种用于电阻抗成像的测量装置,用于对待成像对象施加激励信号并同时测量响应信号的采集模块、以及与采集模块连接且用于对响应信号进行处理的处理模块,处理模块包括与测量单元连接并接收响应信号的第一处理单元、以及与第一处理单元连接的第二处理单元,第一处理单元接收响应信号并进行处理以获得目标响应信号,第二处理单元接收目标响应信号并进行处理以获得目标信息。

5.中国专利cn202110341670x公开了一种基于fft和cordic算法的高速高精度阻抗数据采集系统,公开了一种基于fft和cordic算法的高速高精度阻抗数据采集系统,包括:fpga控制dac产生正弦激励信号经恒流源后输入到模拟开关阵列中,受fpga控制激励电流注入eit传感器,经模拟开关阵列送入仪用放大器,带通滤波器和固定增益放大器后得到模拟信号,同时送入预采样adc和四个高精度adc;经过预采样adc后的信号反馈控制仪用放大器,进行增益调整完成动态增益跟踪。然后,fpga产生四种控制时钟信号驱动高精度adc进行并行采集;最后利用宽带模式校正算法或窄带模式校正算法,对四组并行采样的数据中增益失配误差和时间相位失配误差分别进行校正,完成幅度解调进行反演成像。

6.中国专利cn2010101335019公开了一种生物电阻抗成像硬件系统,保护一种生物电阻抗成像硬件系统,涉及一种医疗设备,包括上位机,usb接口芯片,d/a转换,滤波和压流转换电路,多路开关,被测对象,放大,滤波和a/d转换电路7和fpga中央处理器,核心部件为fpga中央处理器,其包括恒流源控制模块,多路开关选择控制模块,a/d转换采样控制模块,数字相敏解调模块,usb传输控制模块和总控制模块。该系统使用fpga技术实现上述功能模块,提高了电路的集成度、可扩展性和升级性,从而大大减少成像硬件系统的体积和功耗,降低成本,提高了抗干扰性。

7.目前的现有技术专利均是一种多路切换的电阻抗成像方法,均存在如下技术缺陷:

8.1、电极通过多路开关与a/d相连,不利于不同电极数量系统的设计转移;

9.2、连接的结构复杂,造成控制设计复杂,成本增加;

10.3、电极数量的切换开关整体影响系统性能;

11.4、系统自检的设计降低系统性能。

技术实现要素:

12.为了解决现有技术中存在的技术问题,本实用新型提供了一种模块化高速电阻抗成像装置的独立电极模块,通过系统总线的方式,将不同电极数量的系统按照统一的设计方案实现,技术方案中,把激励、检测的切换开关设计在电极模块中,从而降低激励负载电容,提高激励的恒流性能,每一个电极一个独立模块,这个模块包括功能切换、系统自检、模数转换,模块通过spi总线与系统中央处理器连接。

13.本实用新型是通过以下技术方案来实现的:

14.本实用新型公开了一种模块化高速电阻抗成像装置的独立电极模块,所述的独立电极模块的一端连接电极、另一端连接中央处理器,所述的独立电极模块包括功能切换模块、激励模块、系统自检模块和模数转换模块,所述的功能切换模块分别与激励模块、系统自检模块、模数转换模块相连,所述的独立电极模块的下端设有若干输入端口,上端设有与输入端口对应的输出端口。

15.作为进一步地改进,本实用新型所述的功能切换模块包括以菊花链连接模式连接、并由spi总线控制的开关组、与开关组相连的输入端口sw_clk、sw_sdi和分别对应的输出端口sw_clk、sw_sdo。

16.作为进一步地改进,本实用新型所述的功能切换模块还包括输入端口vl、输出端口vl和电阻a,所述的电阻一端连接sw_sdi,另一端连接至vl。

17.作为进一步地改进,本实用新型所述的开关组包括开关a,开关b、开关c和开关d,所述的开关a连接至激励模块的激励正端t ,所述的开关b连接至激励模块的激励负端t-,所述的开关c连接系统自检模块,所述的开关d连接模数转换模块,所述的激励正端t 和激励负端t-位于独立电极模块的下端。

18.作为进一步地改进,本实用新型所述的系统自检模块包括电阻b和电阻c,输入端口ri_i、r0和分别对应的输出端口ri_o、r0,所述的电阻b和电阻c并联,连接至模块输出端口ri_o,所述的电阻c同时与输入端口r0和输出端口r0相连,所述的输入端口ri_i连接至电阻b。

19.作为进一步地改进,本实用新型所述的模数转换模块包括与开关d连接的差分放大器、与差分放大器连接的模数转换器、输入端口a-、d_sdi、d_clk和分别对应的输出端口a 、d_sdo、d_clk,所述的a 连接到差分放大器的正端,a-连接到差分放大器107的负端。

20.作为进一步地改进,本实用新型所述的模数转换器以菊花链连接模式连接并由spi总线控制,所述的输入端口d_sdi连至模数转换器的输入端,模数转换器的输出端连至输出端口d_sdo,所述的d_clk连接至模数转换器。

21.作为进一步地改进,本实用新型所述的模数转换模块还包括连接模数转换器的con和分别对应的输出端口con。

22.作为进一步地改进,本实用新型所述的开关d与差分放大器之间连接有阻抗变换器,所述的开关d连接至阻抗变换器的正端,阻抗变换器的负端输出连接至差分放大器的a

。

23.本实用新型的有益效果如下:

24.1)本实用新型采用独立电极模块,电极功能切换和模数转换双菊花链连接模式,最大简化中央处理器与各个电极之间的控制连接,第一个菊花链连接模式控制各个电极开关的功能,设定电极用于激励还是检测;第二个菊花链连接用于读取各个电极的模数转换(adc)数据,通过第一个菊花链连接的不同设置,完成对电极作用的定义,从而完成整个电阻抗成像数据的全部采集,当各独立电极驱动模块首尾相连并闭合开关c后形成自检电阻网络连接,系统处于自检状态,用以验证系统的工作状态。

25.2)每一个独立电极模块,包括功能切换、系统自检、模数转换(adc)等功能,模块内实现基准测试、低噪放大a1、仪表放大a2、模数转换adc,模块通过spi总线与中央处理器连接,在spi总线地址和数据速度之内,可以允许任意设计系统电极的数量。

26.3)针对高速电阻抗成像系统的模块化设计,每一个电极都有一个模拟数字转换器,而不是数个电极通过多路开关,连接到一个模拟数字转换器(adc),会具有更高速度的检测能力;同时,每一个电极独立实现激励检测的切换和数据转换的功能,通过不同数量的模块连接,快速实现不同电极数目的系统,系统复杂性不增加。

27.4)通过仔细设计模块的输入输出,用个位数的与mcu的连线实现不同数量电极的系统,连线结构简单;简化控制逻辑,进而降低功耗,提高软、硬件系统性能,软件切换实现系统校准功能,独立电极模块spi实现开关切换和数据读取,不同电极数量,只有最多5条并联的信号线;

28.5)通过设置vl端口将功能切换模块设置成菊花链串联模式,电阻a把sw_sdi连接至vl表示四开关模块工作在输入输出逐级串联的移位寄存器模式,通过移位寄存器的电极功能设置,可以一次移位完成一次激励检测的点击切换;

29.6)通过设置阻抗变换器,实现对电极形成高阻抗输入缓冲级,端口中sw_clk为开关控制时钟,sw_sdi是开关设置数据输入,sw_sdo是开关设置数据输出端口。

30.7)本实用新型将通过系统总线的方式,将不同电极数量的系统按照统一的设计方案实现。这种模块化设计方法,使得系统可以应用在通常的8、16、32系统中,不需要更改系统结构,甚至可以直接用于更多的电极系统,实现三维多断层的应用。

31.8)模块化设计可以根据系统需要堆叠电极驱动模块,按照电极实现模块化连接,统一不同电极数量系统的设计复用问题。

附图说明

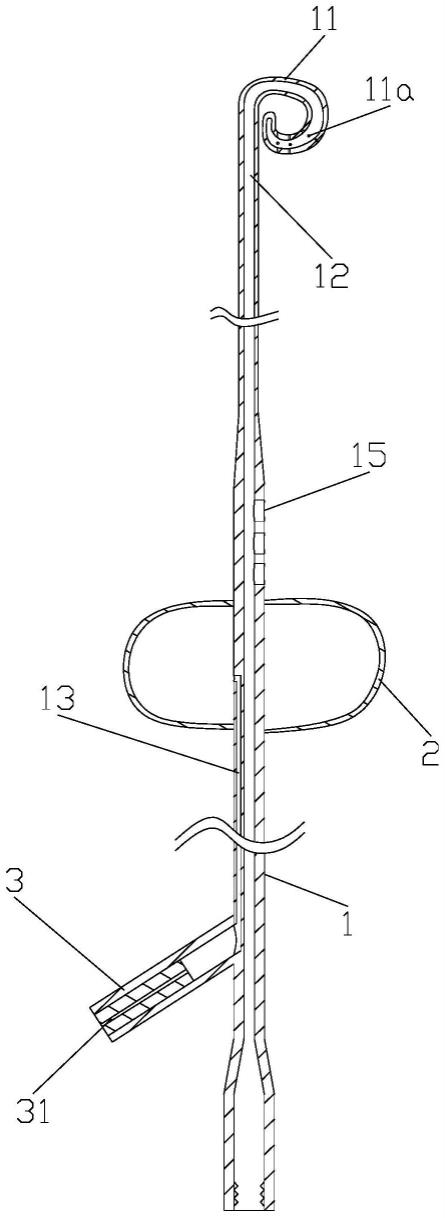

32.图1是实施例1的独立电极模块的结构示意图;

33.图2是实施例2的独立电极模块的结构示意图;

34.图3是实施例1模块化高速电阻抗成像装置的连接结构示意图;

35.图4是实施例3模块化高速电阻抗成像装置连接方式2的示意图;

36.图5是所有独立电极模块的开关c关闭后所形成的自检电阻网络图;

37.图中,1-8是独立电极模块,101是电极,102是开关组,102_1是开关a,102_2是开关b,102_3是开关c,102_4是开关d,103是电阻b,104是电阻c,105是差分放大器,106是模数转换器,107是电阻a,108是阻抗变换器。

具体实施方式

38.本实用新型公开了一种模块化高速电阻抗成像装置的独立电极模块,图1是实施例1的独立电极模块的结构示意图;独立电极模块包括功能切换模块、激励模块、系统自检模块和模数转换模块,功能切换模块分别与激励模块、系统自检模块、模数转换模块相连,独立电极模块的下端设有若干输入端口,上端设有与输入端口对应的输出端口;功能切换模块包括以菊花链连接模式连接、并由spi总线控制的开关组102、与开关组102相连的输入端口sw_clk、sw_sdi和分别对应的输出端口sw_clk、sw_sdo,开关组102包括开关a102_1,开关b102_2、开关c102_3和开关d102_4,开关a102_1连接至激励模块的激励正端t ,开关b102_2连接至激励模块的激励负端t-,开关c102_3连接系统自检模块,开关d102_4连接模数转换模块;系统自检模块包括电阻b103和电阻c104,输入端口ri_i、r0和分别对应的输出端口ri_o、r0,电阻b103和电阻c104并联,连接至模块输出端口ri_o,电阻c104同时与输入端口r0和输出端口r0相连,输入端口ri_i连接至电阻b103,各独立电极模块首尾相连并闭合开关c102_3后形成自检电阻网络,图5是所有独立电极模块的开关c102_3关闭后所形成的自检电阻网络图;模数转换模块包括与开关d102_4连接的差分放大器105、与差分放大器105连接的模数转换器106、输入端口a-、d_sdi、d_clk和分别对应的输出端口a 、d_sdo、d_clk,模数转换器106以菊花链连接模式连接并由spi总线控制,输入端口d_sdi连至模数转换器106的输入端,模数转换器106的输出端连至输出端口d_sdo,d_clk连接至模数转换器106。

39.采用独立电极模块、电极101功能切换和模数转换双菊花链连接模式,最大简化中央处理器与各个电极101之间的控制连接。第一个菊花链sw连接模式控制各个电极101开关的功能,设定电极101用于激励还是检测。第二个菊花链连接用于读取各个电极101的模数转换(adc)数据。通过第一个菊花链连接的不同设置,完成对电极101作用的定义,从而完成整个电阻抗成像数据的全部采集。当所有电极101开关的自己开关闭合的时候,系统处于自检状态,用以验证系统的工作状态。

40.具体地:独立电极模块的下方连线为模块的输入端口,模块的上端为输出端口,独立电极模块包括一个连接电极101,电极101连接一个具有菊花链连接功能的spi总线控制的四个开关开关a102_1、开关b102_2、开关c102_3和开关d102_4,其中开关a102_1连接激励正端t ,开关b102_2连接激励负端t-;开关c102_3连接电阻b103和电阻c104,电阻b103和电阻c104连接到模块输出ri_o,与下一个独立电极模块的ri_i相连,电阻c104同时连接模块的输入和输出r0,a 连接本级的差分放大器105的正端,同时连接到下一级的a-;而本级的a-则作为模块输入连接前一级的a 。差分放大器105将本级输入和前一级输入差分放大,送给模数转换器106。模数转换器106也是一个具有菊花链连接功能的模拟数字转换器,模数转换器106的输入端连接模块数据输入d_sdi;模数转换器106的输出端连接模块数据输出端口d_sdo。

41.在模块运行过程中,开关组102在同一时刻,t 、t-只能连接一个;

42.开关c102_3和开关d102_4只能同时连接一个;

43.当连接开关c 102_3的时候是自检;连接开关d102_4的时候是检测。当t 或t-连接的时候,检测一定不连接;即在同一时刻,开关a102_1、开关b102_2、开关c102_3只能有一个连接。但是在自检的时候,开关c102_3可以与开关a102_1或开关b102_2其中一个同时连接。

如下表所示,其中的*代表开关闭合;

[0044][0045]

图2是实施例2的独立电极模块的结构示意图;功能切换模块还包括输入端口vl、输出端口vl和电阻a107,所述的电阻一端连接sw_sdi,另一端连接至vl,vl是将功能切换模块设置成菊花链串联模式,电阻把sw_sdi连接至vl表示四开关模块工作在输入输出逐级串联的移位寄存器模式,所述的模数转换模块还包括连接模数转换器106的con和分别对应的输出端口con,以及位于开关d102_4与差分放大器105之间连接的阻抗变换器108,开关d102_4连接至阻抗变换器108的正端,阻抗变换器108的负端输出连接至差分放大器105的a ;con是读写控制,阻抗变换器108是对电极101形成高阻抗输入缓冲级。

[0046]

图3是实施例1模块化高速电阻抗成像装置的连接结构示意图;装置包括n个独立电极模块、与独立电极模块相连的mcu、与mcu相连的正向激励和负向激励,n个独立电极模块包括独立电极模块1、独立电极模块2直至独立电极模块n,独立电极模块均包括输入端口与输出端口,各独立电极模块之间通过输入端口与输出端口相连,mcu与独立电极模块的输入端口相连,独立电极模块1的输出端口连至mcu,正向激励与负向激励均与独立电极模块n相连,每个独立电极模块均连有一个电极101。

[0047]

多个独立电极模块连接的时候,只需要将串联的模块接口首尾相连,将第一个模块的输入和最后一个模块的输出连接到,形成系统连接结构。不同的电极101数量8、12、16、24、32....,只需要选择不同的电极101模块数量即可。图1是模块化高速电阻抗成像装置的连接结构示意图;装置至少包含4条串联线路和5条并联线路;4条串联线路为:sw_sdi切换设置输入端口、sw_sdo切换设置输出端口的线路;ri_i电极101串联电阻、ri_o端口的线路;a 差分放大器105正端输入端口、a-差分放大器105负端输入端口的线路;d_sdi数据设置端口、d_sdo数据输出端口的线路;5条并联线路为:sw_clk切换时钟端口的线路;r0电极101并联电阻端口的线路;d_clk数据传输时钟端口的线路;正向激励t 的线路;负向激励t-的线路,线路连接关系分别如下:

[0048]

sw_sdi切换设置输入端口、sw_sdo切换设置输出端口的线路:mcu的输出端口sw_sdi与独立电极模块n的输入端口sw_sdi连接,独立电极模块n的输出端口sw_sdo与独立电极模块n-1的输入端口sw_sdi连接,直到独立电极模块2的输出端口sw_sdo与独立电极模块1的输入端口sw_sdi连接,独立电极模块1的输出端口sw_sdo不需要连接;

[0049]

sw_clk切换时钟端口的线路:mcu的输出端口sw_clk独立电极模块n的输出端口sw_clk与独立电极模块n-1的输入端口sw_clk连接,直到独立电极模块2的输出端口sw_clk与独立电极模块1的输入端口sw_clk连接,独立电极模块1的输出端口sw_clk不需要连接;

[0050]

ri_i电极101串联电阻、ri_o端口的线路:独立电极模块n的输出端口ri_i与独立

电极模块n-1的输入端口ri_o连接,直到独立电极模块1的输出端口ri_i与独立电极模块n的输入端口ri_o连接;

[0051]

r0电极101并联电阻端口的线路:独立电极模块n的输出端口r0与独立电极模块n-1的输入端口r0连接,直到独立电极模块2的输出端口r0与独立电极模块1的输入端口r0连接,独立电极模块1的输出端口r0不需要连接;

[0052]

a 差分放大器105正端输入端口、a-差分放大器105负端输入端口的线路:独立电极模块n的输出端口a 与独立电极模块n-1的输入端口a-连接,直到独立电极模块1的输出端口a 与独立电极模块n的输入端口a-连接;

[0053]

d_sdi数据设置端口、d_sdo数据输出端口的线路:mcu的输出端口d_sdi与独立电极模块n的输入端口d_sdi连接,独立电极模块n的输出端口d_sdo与独立电极模块n-1的输入端口d_sdi连接,直到独立电极模块2的输出端口d_sdo与mcu的输入端口d_sdo连接;

[0054]

d_clk数据传输时钟端口的线路:mcu的输出端口d_clk与独立电极模块n的输入端口d_clk连接,独立电极模块n的输出端口d_clk与独立电极模块n-1的输入端口d_clk连接,直到独立电极模块2的输出端口d_clk与独立电极模块1的输入端口d_clk连接,独立电极模块1的输出端口d_clk不需要连接;

[0055]

正向激励t 的线路:正向激励输出t 与独立电极模块n的输入端口t 连接,独立电极模块n的输出端口t 与独立电极模块n-1的输入端口t 连接,直到独立电极模块2的输出端口t 与独立电极模块1的输入端口t 连接,独立电极模块1的输出端口t 不需要连接;

[0056]

负向激励t-的线路:负向激励输出t-与独立电极模块n的输入端口t-连接,独立电极模块n的输出端口t-与独立电极模块n-1的输入端口t-连接,直到独立电极模块2的输出端口t-与独立电极模块1的输入端口t-连接,独立电极模块1的输出端口t-不需要连接。

[0057]

装置中,当某一个电极101作为激励正端,将该电极101的独立电极模块中的开关a102_1闭合,其他开关打开;当其作为激励负端,将该电极101的独立电极模块中的开关b102_2闭合,其他开关打开;当某一个电极101作为检测电极101的时候,将该电极101的独立电极模块中的开关d102_4闭合,其他开关打开;当进行系统基准测量的时候,将所有独立电极模块中的开关c102_3闭合,其他开关打开,形成电阻自检网络;从而实现了对该电极101所有功能的切换。

[0058]

图4是实施例3模块化高速电阻抗成像装置连接方式2的示意图;n个独立电极模块的输出端口d_sdo均分别与mcu的输入端口d_sdo_1、输入端口d_sdo_2直至输入端口d_sdo_n相连,用此连接方式,采样速度可以提高n个电极101的倍数的速度,同时这种连接方式需要更快速度的mcu,以及要求mcu有更多的n-1个数据读取接口。

[0059]

实施例2的独立电极模块中,所增加的端口的连接方式如下:

[0060]

关于vl端口的线路:mcu的输出端口vl与独立电极模块n的输入端口vl连接,独立电极模块n的输出端口vl与独立电极模块n-1的输入端口vl连接,直到独立电极模块2的输出端口vl与独立电极模块1的输入端口vl连接,独立电极模块1的输出端口vl不需要连接;

[0061]

关于con的这条线:mcu的输出端口con与独立电极模块n的输入端口con连接,独立电极模块n的输出端口con与独立电极模块n-1的输入端口con连接,直到独立电极模块2的输出端口con与独立电极模块1的输入端口con连接,独立电极模块1的输出端口con不需要连接。

[0062]

以上仅是本实用新型的优选实施方式,本实用新型并不限于以上实施例,本领域技术人员在不脱离本实用新型的精神和构思的前提下直接导出或联想到的其他改进和变化,均应认为包含在本实用新型的保护范围内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。