1.本技术涉及显示技术领域,尤其涉及一种阵列基板、阵列基板的制作方法及显示面板。

背景技术:

2.在现有薄膜晶体管的结构中,其通常设置有多层绝缘材料以使不同层的金属材料绝缘设置。由于不同金属层之间存在换线的情况,因此需要对多层绝缘材料进行蚀刻以形成换线孔。由于不同区域的换线孔存在深孔和浅孔,以及为了减少蚀刻工艺,通常对深孔和浅孔同时蚀刻,而由于不同的绝缘材料的蚀刻速率不同,因此导致换线孔或电连接的过孔出现底切结构或换线孔过蚀刻的技术问题。

技术实现要素:

3.本技术提供一种阵列基板、阵列基板的制作方法及显示面板,以解决当前阵列基板中换线孔或电连接的过孔出现底切结构或换线孔过蚀刻的技术问题。

4.为解决上述方案,本技术提供的技术方案如下:本技术提出了一种阵列基板,其包括:衬底;第一绝缘层,设置于所述衬底上;第二绝缘层,设置于所述第一绝缘层上,所述第一绝缘层的水平蚀刻速率大于所述第二绝缘层的水平蚀刻速率;第三绝缘层,设置于所述第二绝缘层上,所述第三绝缘层的水平蚀刻速率大于所述第二绝缘层的水平蚀刻速率;其中,所述阵列基板设有第一区域和第二区域,且所述阵列基板包括第一类过孔和第二类过孔,所述第一类过孔设置在所述第一区域,所述第二类过孔设置在所述第二区域,所述第一类过孔贯穿所述第一绝缘层、所述第二绝缘层以及所述第三绝缘层,所述第二类过孔贯穿所述第三绝缘层,所述第一类过孔的孔深大于所述第二类过孔的孔深,所述第一类过孔的孔径大于所述第二类过孔的孔径。

5.在本技术的阵列基板中,所述第一类过孔包括第一过孔,所述第一过孔贯穿所述第一绝缘层、所述第二绝缘层以及第三绝缘层;所述第二类过孔包括第二过孔和第三过孔,所述第三过孔贯穿所述第三绝缘层,所述第二过孔贯穿所述第二绝缘层和所述第三绝缘层;其中,所述第一过孔的孔深大于所述第二过孔的孔深,所述第二过孔的孔深大于所述第三过孔的孔深,所述第一过孔的孔径大于所述第三过孔的孔径,所述第三过孔的孔径大于所述第二过孔的孔径。

6.在本技术的阵列基板中,所述第二过孔包括在所述第三绝缘层上的第一孔壁和在所述第二绝缘层上的第二孔壁,所述第一孔壁和所述第二孔壁连续设置;或者,

所述第二过孔在所述第三绝缘层上的孔壁以及在所述第二绝缘层上的孔壁非连续设置,所述第二过孔在所述第三绝缘层上的孔径大于在所述第二绝缘层上的孔径。

7.在本技术的阵列基板中,所述第一过孔在所述第三绝缘层上的孔壁、在所述第二绝缘层上的孔壁以及在所述第一绝缘层上的孔壁连续设置;其中,所述第一过孔中孔壁的倾斜角度小于所述第二过孔中孔壁的倾斜角度。

8.在本技术的阵列基板中,所述第一过孔在所述第二绝缘层上的孔壁以及在所述第一绝缘层上的孔壁连续设置,所述第一过孔在所述第三绝缘层上的孔壁以及在所述第二绝缘层上的孔壁非连续设置;其中,所述第一过孔在所述第三绝缘层上的孔径大于在所述第二绝缘层和所述第一绝缘层上的孔径。

9.在本技术的阵列基板中,所述阵列基板包括设置于所述衬底上的栅极层、设置于所述栅极层上的栅绝缘层、设置于所述栅绝缘层上的源漏极层、设置于所述源漏极层上的第一钝化层、设置于所述第一钝化层上的公共电极层、设置于所述公共电极层上的第二钝化层、以及设置于所述第二钝化层上的像素电极层;其中,所述第一过孔贯穿所述第二钝化层、所述第一钝化层以及所述栅绝缘层,用于将所述公共电极层和所述栅极层电连接,所述第二过孔贯穿所述第二钝化层和所述第一钝化层,用于将所述源漏极层和所述像素电极层电连接,所述第三过孔贯穿所述第二钝化层,用于将部分所述公共电极层和部分所述像素电极层电连接。

10.本技术还提出了一种阵列基板的制作方法,其包括:在衬底上依次形成第一绝缘层、第二绝缘层、第三绝缘层以及光阻层,且其中,所述第一绝缘层的水平蚀刻速率大于所述第二绝缘层的水平蚀刻速率,所述第三绝缘层的水平蚀刻速率大于所述第二绝缘层的水平蚀刻速率;对所述光阻层进行第一次图案化处理形成第一光阻图案,并通过所述第一光阻图案对所述阵列基板中第一区域的所述第一绝缘层、所述第二绝缘层以及所述第三绝缘层进行第一次蚀刻处理;对所述第一光阻图案进行第二次图案化处理形成第二光阻图案,并通过所述第二光阻图案对所述阵列基板中所述第一区域的所述第一绝缘层、所述第二绝缘层以及所述第三绝缘层进行第二次蚀刻处理,以形成第一类过孔,以及对所述阵列基板中第二区域的所述第三绝缘层和/或所述第二绝缘层进行第一次蚀刻处理,以形成第二类过孔;其中,所述第一类过孔的孔深大于所述第二类过孔的孔深,所述第一类过孔的孔径大于所述第二类过孔的孔径。

11.在本技术的阵列基板的制作方法中,所述对所述光阻层进行第一次图案化处理形成第一光阻图案,并通过所述第一光阻图案对所述阵列基板中第一区域的所述第一绝缘层、所述第二绝缘层以及所述第三绝缘层进行第一次蚀刻处理的步骤包括:对所述光阻层进行第一次图案化处理形成第一光阻图案,所述第一光阻图案包括第一光阻部、第二光阻部、第三光阻部以及第四光阻部,所述第一光阻部的厚度、所述第二光阻部以及第三光阻部的厚度相同,所述第一光阻部、第二光阻部以及所述第三光阻部的厚度小于所述第四光阻部的厚度,所述第一光阻部包括第一通孔,所述第一通孔位于所述第一区域;

对经所述第一通孔暴露的所述第一绝缘层、所述第二绝缘层以及所述第三绝缘层进行第一次蚀刻处理。

12.在本技术的阵列基板的制作方法中,所述对所述第一光阻图案层进行第二次图案化处理形成第二光阻图案,并通过所述第二光阻图案对所述阵列基板中所述第一区域的所述第一绝缘层、所述第二绝缘层以及所述第三绝缘层进行第二次蚀刻处理,以及对所述阵列基板中第二区域的所述第三绝缘层进行第一次蚀刻处理的步骤包括:利用灰化工艺对所述第一光阻图案进行处理,以去除所述第一光阻部、所述第二光阻部以及所述第三光阻部;对与所述第一光阻部对应的所述第一绝缘层、所述第二绝缘层以及所述第三绝缘层进行第二次蚀刻处理以形成第一过孔,以及对与所述第二光阻部对应的所述第二绝缘层和所述第三绝缘层进行第一次蚀刻处理以形成第二过孔,以及对与所述第三光阻部对应的所述第三绝缘层进行第一次蚀刻处理,以形成第三过孔;其中,所述第一过孔的孔深大于所述第二过孔的孔深,所述第二过孔的孔深大于所述第三过孔的孔深,所述第一过孔的孔径大于所述第三过孔的孔径,所述第三过孔的孔径大于所述第二过孔的孔径。

13.本技术还提出了一种显示面板,所述显示面板包括上述阵列基板。

14.有益效果:本技术通过在第一次蚀刻工艺中对第一类过孔进行初蚀刻,以及在第二次蚀刻工艺同时对第一类过孔和第二类过孔进行蚀刻,消除了蚀刻速率低的第二绝缘层在第一类过孔内形成底切结构,同时第二类过孔仅经过一次蚀刻,避免了第二类过孔的过蚀刻的技术问题。

附图说明

15.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其它有益效果显而易见。

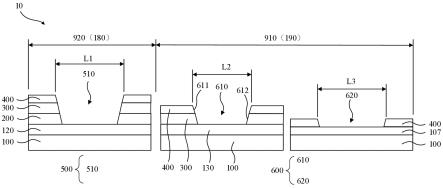

16.图1为本技术阵列基板的第一种结构图;图2为本技术阵列基板中薄膜晶体管区域的结构简图;图3为本技术显示面板的结构简图;图4为本技术阵列基板的第二种结构图;图5为本技术阵列基板的中间步骤结构图;图6为本技术阵列基板的第三种结构图;图7为本技术阵列基板的制作方法工艺流程图;图8a至图8e为本技术阵列基板的制作方法工艺步骤图。

具体实施方式

17.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

18.请参阅图1至图6,本技术提出了一种阵列基板10,其包括衬底100、设置于所述衬

底100上的第一绝缘层200、设置于所述第一绝缘层200上的第二绝缘层300、以及设置于所述第二绝缘层300上的第三绝缘层400。

19.在本实施例中,所述第一绝缘层200的水平蚀刻速率大于所述第二绝缘层300的水平蚀刻速率,所述第三绝缘层400的水平蚀刻速率大于所述第二绝缘层300的水平蚀刻速率。

20.在本实施例中,所述阵列基板10设有第一区域180和第二区域190,且所述阵列基板10包括第一类过孔500和第二类过孔600,所述第一类过孔500设置在所述第一区域180,所述第二类过孔600设置在所述第二区域190,所述第一类过孔500贯穿所述第一绝缘层200、所述第二绝缘层300以及所述第三绝缘层400,所述第二类过孔600贯穿所述第三绝缘层400,所述第一类过孔500的孔深大于所述第二类过孔600的孔深,所述第一类过孔500的孔径大于所述第二类过孔600的孔径。

21.本技术通过在第一次蚀刻工艺中对第一类过孔500进行初蚀刻,以及在第二次蚀刻工艺同时对第一类过孔500和第二类过孔600进行蚀刻,消除了水平蚀刻速率低的第二绝缘层300在第一类过孔500内形成底切结构,同时第二类过孔600仅经过一次蚀刻,避免了第二类过孔600的过蚀刻的技术问题。同时,由于所述第一类过孔500贯穿三层绝缘层,因此电连接的过孔的深度较大时,若开口的孔径较小,易导致上层金属和所述第一金属层120接触阻抗的增加,且易出现接触不良的技术问题;而本技术将第一类过孔500的孔径增加,增加了上层金属和第一金属层120的接触面积,减小了二者的接触阻抗,同时降低了上层金属和所述第一金属层120接触不良的技术问题。

22.现结合具体实施例对本技术的技术方案进行描述。

23.请参阅图1至图2,所述阵列基板10可以包括衬底100和设置于所述衬底100上的薄膜晶体管层,所述薄膜晶体管层可以包括多层金属层和多层绝缘层。

24.在本实施例中,所述衬底100的材料可以为玻璃、石英或聚酰亚胺等材料,或者由聚酰亚胺等柔性材料构成,或者由柔性材料和无机材料的层叠膜层构成。

25.在本实施例中,请参阅图2,所述薄膜晶体管层可以包括多个薄膜晶体管,所述薄膜晶体管可以为蚀刻阻挡型、背沟道蚀刻型,或者根据栅极与有源层103的位置划分为底栅薄膜晶体管、顶栅薄膜晶体管等结构,具体没有限制。例如,图2中所示的薄膜晶体管为底栅型薄膜晶体管,该薄膜晶体管可以包括设置于所述衬底100上的栅极层101、设置于所述栅极层101上的栅绝缘层102、设置于所述栅绝缘层102上的有源层103、设置于所述有源层103上的间绝缘层104、设置于所述间绝缘层104上的源漏极层105、设置于所述源漏极层105上第一钝化层106以及设置于所述第一钝化层106上的公共电极层107、设置于所述公共电极层107上的第二钝化层108、以及设置于所述第二钝化层108上的像素电极层109,所述公共电极层107层连接恒压源,所述像素电极层109与源/漏极电连接,所述公共电极层107和所述像素电极层109产生的电场驱动液晶偏转。

26.在本实施例中,所述栅极层101可以本技术阵列基板10的为第一金属层120,所述源漏极层105可以为本技术阵列基板10的第二金属层130。本实施例中的底栅型薄膜晶体管包括间绝缘层104,在其他的实施例中,也可以不设置间绝缘层104,而是将源漏极层105和有源层103直接接触连接。

27.在本实施例中,所述第一绝缘层200可以包括所述栅绝缘层102,所述第二绝缘层

300可以包括所述第一钝化层106,所述第三绝缘层400可以包括所述第二钝化层108。

28.在本实施例中,由于现有阵列基板10中通常会出现不同金属层的换线或不同金属层之间电连接的情况,因此需要对中间的绝缘层进行蚀刻,以使不同金属层之间电连接。

29.在本技术的阵列基板10中,请参阅图1,所述第一类过孔500可以包括第一过孔510,所述第一过孔510贯穿所述第一绝缘层200、所述第二绝缘层300以及第三绝缘层400,所述第二类过孔600可以包括第二过孔610和第三过孔620,所述第三过孔620贯穿所述第三绝缘层400,所述第二过孔610贯穿所述第二绝缘层300和所述第三绝缘层400。

30.在本实施例中,所述第一过孔510的孔深大于所述第二过孔610的孔深,所述第二过孔610的孔深大于所述第三过孔620的孔深,所述第一过孔510的孔径l1大于所述第三过孔620的孔径l3,所述第三过孔620的孔径l3大于所述第二过孔610的孔径l2。

31.在本实施例中,所述第一金属层120可以和所述第一绝缘层200接触,所述第一过孔510可以与所述第一金属层120对应,所述第一过孔510使部分所述第一金属层120裸露,以使上层金属层能通过所述第一过孔510和所述第一金属层120电连接;所述第二金属层130可以和所述第二绝缘层300接触,所述第二过孔610与所述第二金属层130对应,所述第二过孔610使部分所述第二金属层130裸露,以使上层金属层能通过所述第二过孔610和所述第二金属层130电连接;所述公共电极层107可以和所述第三绝缘层400接触,所述第三过孔620与所述公共电极层107对应,所述第三过孔620使部分所述公共电极层107裸露,以使上层金属层能通过所述第三过孔620和所述公共电极层107电连接。

32.在本实施例中,请参阅图3,图3为本技术的显示面板900的结构简图。所述显示面板900包括显示区910和非显示区920,所述第一区域180可以在所述非显示区920内,所述第二区域190可以在所述显示区910内;或者,所述第一区域180和所述第二区域190可以同时位于所述显示区910或所述非显示区920内。在本技术的下面实施例中,以所述第一区域180可以在所述非显示区920,所述第二区域190可以在所述显示区910为例进行说明。

33.请参阅图3,所述第一过孔510可以设置于所述非显示区920内,所述第二过孔610和所述第三过孔620可以设置于所述显示区910内。例如所述第一过孔510可以为所述显示面板900中阵列基板10上的外围换线孔,将与栅极层101同层设置的金属线换线至第二钝化层108上,由于所述第一过孔510位于非显示区920,且间绝缘层104可以仅在显示区910内成膜,因此外围的栅极层101和公共电极层107之间只有三层绝缘膜层;所述第二过孔610可以为显示区910内的连接孔,例如源/漏极通过第二过孔610和上层的像素电极层109电连接。

34.在本实施例中,所述第三过孔620可以为显示区910内的连接孔,且所述公共电极层107与恒压源连接,且恒压源的信号线通常与栅极层101或源漏极层105同层设置,因此若需要将恒压源的信号导入至所述公共电极层107,需要增加一道光罩工艺,以在第一钝化层106上形成过孔,以使得源漏极层105和公共电极层107电连接。请参阅图2,本技术可以在第二钝化层108上形成第一转接垫640,所述第一转接垫640和所述像素电极层109可以在一道光罩工艺中形成,所述公共电极层107通过第三过孔620和所述第一转接垫640电连接,且所述第一转接垫640通过转接孔630和第二转接垫650电连接,所述第二转接垫650和源/漏极可以在一道光罩工艺中形成,由于所述转接孔630和所述第二过孔610均贯穿所述第一钝化层106和所述第二钝化层108,因此所述转接孔630可以和所述第二过孔610在同一道蚀刻工艺中形成,无需增加额外的光罩工艺,即可将恒压源通过第二转接垫650、转接孔630、第一

转接垫640以及第三过孔620传输至所述公共电极层107。

35.在本实施例中,请参阅图1,由于在所述第二过孔610和所述第三过孔620开始蚀刻之前,需要对所述第一过孔510进行初蚀刻,其次所述第一过孔510与所述第二过孔610和所述第三过孔620进行第二次蚀刻工艺,所述第一过孔510经两次蚀刻工艺,使得所述第一过孔510的孔径l1较所述第二过孔610和所述第三过孔620的孔径更大;另外,所述第二过孔610和所述第三过孔620仅需一次蚀刻工艺,且由于第二过孔610需蚀刻两层绝缘层,而所述第三过孔620仅需蚀刻一层绝缘层,因此在相同蚀刻时间的条件下,所述第三过孔620的孔径l3较所述第二过孔610的孔径l2大。

36.在本实施例中,由于所述第一过孔510贯穿三层绝缘层,因此电连接的过孔的深度较大时,若开口的孔径较小,易导致上层金属和所述第一金属层120接触阻抗的增加,且易出现接触不良的技术问题;而本技术将第一过孔510的孔径l1增加,增加了上层金属和第一金属层120的接触面积,减小了二者的接触阻抗,同时降低了上层金属和所述第一金属层120接触不良的技术问题。

37.在本技术的阵列基板10中,请参阅图1,所述第二过孔610包括位于所述第三绝缘层400上的第一孔壁611和位于所述第二绝缘层300上的第二孔壁612,所述第一孔壁611和所述第二孔壁612连续设置。

38.在本实施例中,由于所述第二过孔610贯穿所述第三绝缘层400和所述第二绝缘层300,且所述第二绝缘层300的水平蚀刻速率小于所述第三绝缘层400的水平蚀刻速率,因此在对所述第二过孔610蚀刻时,所述第三绝缘层400和所述第二绝缘层300之间将出现台阶,导致所述第二过孔610对应的所述第二金属层130所裸露的面积减小,减少上层金属和所述第二金属层130的接触面积,增加上层金属和所述第二金属层130的接触阻抗,因此本技术通过增加蚀刻时间,去除所述第二过孔610内过多的所述第二绝缘层300的材料,使得所述第二过孔610在所述第三绝缘层400上的孔壁和在所述第二绝缘层300上的孔壁连续设置。

39.在本技术的阵列基板10中,请参阅图1,所述第一过孔510在所述第三绝缘层400上的孔壁、在所述第二绝缘层300上的孔壁以及在所述第一绝缘层200上的孔壁连续设置,所述第一过孔510中孔壁的倾斜角度可以小于所述第二过孔610中孔壁的倾斜角度。

40.在本实施例中,所述第一过孔510和所述第二过孔610中的孔壁均连续设置,但是由于第一过孔510的深度大于所述第二过孔610的深度,深度较大的过孔的接触阻抗较大,且在孔壁上易出现断线的技术问题;本技术通过增加所述第一过孔510的倾斜角度,使得所述第一过孔510的孔壁更缓,增加了上层金属层在所述第一过孔510的孔壁上的沉积面积,减小了上层金属层在所述第一过孔510的孔壁上的断线的风险,同时也减小了上层金属和所述第一金属层120的接触阻抗。

41.在本技术的阵列基板10中,请参阅图4,所述第二过孔610在所述第三绝缘层400上的孔壁以及在所述第二绝缘层300上的孔壁非连续设置,所述第二过孔610在所述第三绝缘层400上的孔径大于在所述第二绝缘层300上的孔径。

42.在本实施例中,由于所述第三绝缘层400的水平蚀刻速率大于所述第二绝缘层300的水平蚀刻速率,因此在对所述第二过孔610蚀刻时,所述第三绝缘层400和所述第二绝缘层300之间将出现台阶,若将该台阶去除,则需要更长的蚀刻时间,且可能导致第三过孔620的过蚀刻,因此可以根据第一过孔510中是否存在底切结构,以停止对所述第二过孔610的

蚀刻;例如,当所述第一过孔510中的底切结构消除时,则可以停止所述第二过孔610的蚀刻,即避免了第一过孔510中底切结构的消除,以及最大化的消除了所述第二过孔610中所述第二绝缘层300的台阶结构;另外,由于所述第二过孔610可能出现孔壁的倾角较大的情况,而所述第二过孔610内台阶结构的出现,可以降低上层金属在所述第二过孔610内出现断线的风险。

43.在本技术的阵列基板10中,请参阅图6,所述第一过孔510在所述第二绝缘层300上的孔壁以及在所述第一绝缘层200上的孔壁连续设置,所述第一过孔510在所述第三绝缘层400上的孔壁以及在所述第二绝缘层300上的孔壁非连续设置。

44.在本实施例中,所述第一过孔510在所述第三绝缘层400上的孔径大于在所述第二绝缘层300和所述第一绝缘层200上的孔径。

45.在本实施例中,由于所述第一过孔510贯穿所述第三绝缘层400、所述第二绝缘层300以及所述第一绝缘层200,且所述第二绝缘层300的水平蚀刻速率小于所述第三绝缘层400和所述第一绝缘层200的水平蚀刻速率,因此在对所述第一过孔510进行第一次蚀刻时,所述第三绝缘层400和所述第二绝缘层300之间将出现台阶,具体请参阅图5中的结构,所述第一绝缘层200和所述第二绝缘层300之间形成底切结构,而由于干法蚀刻在垂直方向的蚀刻速率大于水平方向的蚀刻速率,因此可以增加所述第一过孔510的蚀刻时间,即对所述第一过孔510进行第二次蚀刻时,可以消除图5中的底切结构,使得所述第一过孔510的结构形成如图6所示的结构。

46.在本实施例中,由于所述第一过孔510的深度较大,因此上层金属在所述第一过孔510内沉积时,易出现断线的风险,而本技术通过在所述第一过孔510内形成台阶结构,增加了上层金属在所述第一过孔510的孔壁上的沉积面积,降低了上层金属在所述第一过孔510内出现断线的风险。

47.在本技术的阵列基板10中,所述第一绝缘层200和所述第三绝缘层400的材料相同,所述第一绝缘层200和所述第三绝缘层400的材料可以包括氧化硅,所述第二绝缘层300的材料可以包括氮化硅。

48.在本实施例中,所述公共电极层107和所述像素电极层109的材料可以包括氧化铟锡等透明导电材料。

49.请参阅图7,本技术提出了一种阵列基板10的制作方法,其包括:s10,在所衬底100上依次形成第一绝缘层200、第二绝缘层300、第三绝缘层400以及光阻层700,且其中,所述第一绝缘层200的水平蚀刻速率大于所述第二绝缘层300的水平蚀刻速率,所述第三绝缘层400的水平蚀刻速率大于所述第二绝缘层300的水平蚀刻速率。

50.在本步骤中,所述衬底100的材料可以为玻璃、石英或聚酰亚胺等材料,或者由聚酰亚胺等柔性材料构成,或者由柔性材料和无机材料的层叠膜层构成。

51.请参阅图8a,所述第一绝缘层200和所述第三绝缘层400的材料相同,所述第一绝缘层200和所述第三绝缘层400的材料可以包括氧化硅,所述第二绝缘层300的材料可以包括氮化硅。

52.s20,对所述光阻层700进行第一次图案化处理形成第一光阻图案,并通过所述第一光阻图案对所述阵列基板10中第一区域180的所述第一绝缘层200、所述第二绝缘层300以及所述第三绝缘层400进行第一次蚀刻处理。

53.在本实施例中,步骤s20可以包括:s201,对所述光阻层700进行第一次图案化处理形成第一光阻图案,所述第一光阻图案包括第一光阻部710、第二光阻部720、第三光阻部730以及第四光阻部740,所述第一光阻部710的厚度、所述第二光阻部720以及第三光阻部730的厚度相同,所述第一光阻部710、所述第二光阻部720以及第三光阻部730的厚度小于所述第四光阻部740的厚度,所述第一光阻部710包括第一通孔711,所述第一通孔711位于所述第一区域180内;s202,对经所述第一通孔711暴露的所述第一绝缘层200、所述第二绝缘层300以及所述第三绝缘层400进行第一次蚀刻处理。

54.在本实施例中,请参阅图8b,所述第一光阻部710位于所述阵列基板10的第一区域180内,所述第一区域180可以为阵列基板10的外围换线区域,与显示面板900的非显示区920对应;所述第二光阻部720和所述第三光阻部730可以位于所述阵列基板10的第二区域190内,所述第二区域190为阵列基板10的面内区域,所述第二区域190与显示面板900的显示区910对应。

55.在步骤s201中,请参阅图8b,利用多段式掩膜板800对所述光阻层700图案化处理,以形成不同厚度的第一光阻部710、第二光阻部720、第三光阻部730以及第四光阻部740。所述多段式掩膜板800可以包括第一透光区810、第二透光区820和第三透光区830,所述第一透光区810和所述第四光阻部740对应,所述第三透光区830和所述第一通孔711对应,所述第二透光区820和剩余区域对应。

56.在本实施例中,所述光阻层700的材料以正性光阻为例,所述第一透光区810的光透过率可以为0%,所述第二透光区820的光透过率可以为50%,所述第三透光区830的光透过率可以为100%。

57.在步骤s202中,请参阅图8c,本技术可以利用干法蚀刻工艺对三层绝缘层进行第一次蚀刻处理,而由于所述第二绝缘层300的水平蚀刻速率小于所述第三绝缘层400和所述第一绝缘层200的水平蚀刻速率,在进行第一次蚀刻处理时,所述第三绝缘层400和所述第二绝缘层300之间将出现台阶,所述第一绝缘层200和所述第二绝缘层300之间形成底切结构。

58.s30,对所述光阻层700进行第二次图案化处理形成第二光阻图案,以及通过所述第二光阻图案对所述阵列基板10中第一区域180的所述第一绝缘层200、所述第二绝缘层300以及所述第三绝缘层400进行第二次蚀刻处理,以形成第一类过孔500,以及对所述阵列基板10中第二区域190的所述第三绝缘层400或/和所述第二绝缘层300进行第一次蚀刻处理,以形成第二类过孔600,所述第一类过孔500的孔深大于所述第二类过孔600的孔深,所述第一类过孔500的孔径大于所述第二类过孔600的孔径。

59.在本实施例中,步骤s30可以包括:s301:利用灰化工艺对所述第一光阻部710、所述第二光阻部720以及所述第四光阻部740处理,以去除所述第一光阻部710和所述第二光阻部720以及第三光阻部730。

60.在步骤s301中,请参阅图8d,本技术可以利用等离子体对所述第一光阻部710、所述第二光阻部720以及所述第四光阻部740处理,以去除所述第一光阻部710、所述第二光阻部720和第三光阻部730,并减小所述第四光阻部740的厚度。

61.在本实施例中,所述灰化工艺中的等离子体可以为四氟化氮、六氟化硫、氧气等气

体中的至少一种。

62.在对光阻进行灰化处理后,继续执行步骤s302:对与所述第一光阻部710对应的所述第一绝缘层200、所述第二绝缘层300以及所述第三绝缘层400进行第二次蚀刻处理以形成第一过孔510,以及对与所述第二光阻部720对应的所述第三绝缘层400和所述第二绝缘层300进行第一次蚀刻处理以形成第二过孔610,以及对与所述第三光阻部730对应的所述第三绝缘层400进行第一次蚀刻处理以形成第三过孔620。

63.具体来说,在步骤s302中,请参阅图8e,在第一区域180中,等离子体接触被第一光阻部710暴露的第三绝缘层400、第二绝缘层300和第一绝缘层200。由于等离子体对绝缘层的垂直蚀刻速率大于水平蚀刻速率,此时,第一绝缘层200和第三绝缘层400仅在水平方向上与等离子体接触,第二绝缘层300同时在水平方向和垂直方向与等离子体接触,故而,等离子体对第二绝缘层300的水平蚀刻速率大于对第一绝缘层200和第三绝缘层400的水平蚀刻速率,第二绝缘层300的后退速度大于第一绝缘层200和第三绝缘层400的后退速度,进而形成了图8e中的第一过孔510。

64.在步骤s302中,请参阅图8e,在第二区域190中,等离子体还同时接触被第二光阻部720暴露的第三绝缘层400和第二绝缘层300。由于第二绝缘层300在水平方向的蚀刻速率小于第三绝缘层400在水平方向的蚀刻速率,因此在蚀刻开始阶段,第二光阻部720暴露的第三绝缘层400和第二绝缘层300形成台阶;随着蚀刻时长的增加,以及等离子体对绝缘层的垂直蚀刻速率大于水平蚀刻速率,此时第三绝缘层400仅在水平方向上与等离子体接触,第二绝缘层300同时在水平方向和垂直方向与等离子体接触,故而等离子体对第二绝缘层300的水平蚀刻速率大于对第三绝缘层400的水平蚀刻速率,第二绝缘层300的后退速度大于第三绝缘层400的后退速度,进而形成了图8e中的第二过孔610。

65.在步骤s302中,请参阅图8e,在第二区域190中,等离子体还同时接触被第三光阻部730暴露的第三绝缘层400,进而形成了图8e中的第三过孔620。

66.在本实施例中,所述阵列基板10可以包括设置于所述衬底100上的第一金属层120、第二金属层130以及公共电极层107。所述第一金属层120可以和所述第一绝缘层200接触,所述第一过孔510可以与所述第一金属层120对应,所述第一过孔510使部分所述第一金属层120裸露,以使上层金属层能通过所述第一过孔510和所述第一金属层120电连接;所述第二金属层130可以和所述第二绝缘层300接触,所述第二过孔610与所述第二金属层130对应,所述第二过孔610使部分所述第二金属层130裸露,以使上层金属层能通过所述第二过孔610和所述第二金属层130电连接;所述公共电极层107可以和所述第三绝缘层400接触,所述第三过孔620与所述公共电极层107对应,所述第三过孔620使部分所述公共电极层107裸露,以使上层金属层能通过所述第三过孔620和所述公共电极层107电连接。

67.在本实施例中,如图4和图6中的结构也可以通过本技术的制作方法获取。

68.最后,剥离所述第三绝缘层400上的光阻材料,并进行后续膜层工艺。

69.本技术还提出了一种显示面板900,所述显示面板900包括上述阵列基板10。当所述显示面板900为液晶显示面板时,所述显示面板900还包括与所述阵列基板10相对设置的对置基板、设置于所述阵列基板10和所述对置基板之间的液晶层;当所述显示面板900为有机发光显示面板时,所述显示面板900还包括设置于所述阵列基板上的有机发光功能层、设置于所述有机发光功能层上的薄膜封装层;另外,所述阵列基板10还可以作为背光模组中

的驱动层。

70.本技术还提出了一种移动终端,其包括终端主体和上述显示面板,所述终端主体和所述显示面板组合为一体。该终端主体可以为绑定于显示面板的电路板等器件以及覆盖在所述显示面板上的盖板等。所述移动终端可以包括手机、电视机、笔记本电脑等电子设备。

71.本技术公开了一种阵列基板、阵列基板的制作方法及显示面板;该阵列基板包括叠层设置的衬底、第一绝缘层、第二绝缘层以及第三绝缘层,第二绝缘层的水平蚀刻速率小于第一绝缘层和第三绝缘层的水平蚀刻速率;阵列基板包括设有第一类过孔的第一区域和设有第二类过孔的第二区域,第一类过孔贯穿第一绝缘层、第二绝缘层以及第三绝缘层,第二类过孔贯穿第三绝缘层;本技术通过在第一次蚀刻工艺中对第一类过孔进行初蚀刻,以及在第二次蚀刻工艺同时对第一类过孔和第二类过孔进行蚀刻,消除了水平蚀刻速率低的第二绝缘层在第一类过孔内形成底切结构,同时第二类过孔仅经过一次蚀刻,避免了第二类过孔的过蚀刻的技术问题。

72.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

73.以上对本技术实施例所提供的一种阵列基板、阵列基板的制作方法及显示面板进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。