1.本说明书中公开的本发明涉及一种晶体管驱动电路。

背景技术:

2.通常已知的是,在诸如mosfet(mos晶体管)的晶体管中,在晶体管的开关驱动期间,由于晶体管的输出电压(在mosfet的情况下,vds(漏极-源极电压))的高频分量,可能发生emi(电磁干扰)噪声。

3.这种晶体管的已知切换特性包括晶体管的输出电压的上升时间tr和下降时间tf。在晶体管是例如mosfet的情况下,如图10所示,上升时间tr被定义为vds从10%上升到90%所花费的时间,并且下降时间tf被定义为vds从90%下降到10%所花费的时间。

4.当上升时间tr和下降时间tf短时,emi噪声增加,并且当上升时间tr和下降时间tf长时,emi噪声减小。同时,当上升时间tr和下降时间tf减小时,切换损耗减小,当上升时间tr和下降时间tf增加时,切换损耗增加。以这种方式,emi噪声和切换损耗(功率损耗)处于折衷关系。

5.现有技术文献

6.专利文献

7.专利文献1:特开2014-165890号公报

技术实现要素:

8.发明要解决的问题

9.在本文中,专利文献1公开了一种旨在降低emi噪声和切换损耗两者的负载驱动控制装置。在上述专利文献1中,电容连接到驱动nmos晶体管的预驱动器的输入侧,并且被充电或放电以使得预驱动器的输出电压改变,并且nmos晶体管通过预驱动器的输出电压导通/关断以便获得nmos晶体管的vds的线性上升和下降梯度。因此,可以将nmos晶体管导通/关断时的功率损耗降低到emi噪声的高频区域特性所需的最小损耗量,并且从而降低切换损耗以及emi噪声。

10.然而,上述专利文献1的缺点在于,晶体管的上升时间tr和下降时间tf均以时间上均匀的方式发生,使得所获得的降低emi噪声和切换损耗的效果可能不足。

11.考虑到上述情况,本说明书中公开的本发明的目的是提供一种能够降低emi噪声同时抑制切换损耗的增加的晶体管驱动电路。

12.解决问题的方案

13.本说明书中公开的本发明的一个方面是一种晶体管驱动电路,所述晶体管驱动电路驱动要被驱动的晶体管,并且包括控制器,所述控制器执行控制以使得在时间上改变有助于所述要被驱动的晶体管的上升时间或下降时间的电路参数(第一配置)。

14.此外,在上述第一配置中,所述电路参数可以是被供应给所述被驱动的晶体管的控制端子的电流(第二配置)。

15.此外,在上述第二配置中,还可以提供预驱动器,所述预驱动器包括所述电流流过的第一晶体管部分,并且所述控制器可以使得在时间上改变所述第一晶体管部分的导通电阻(第三配置)。

16.此外,在上述第三配置中,所述第一晶体管部分可以包括并联连接在电源电压的应用端子与所述控制端子之间的多个第一晶体管,并且所述控制器可以使得在时间上改变所述多个第一晶体管中处于启用状态并且能够导通/关断的并联连接的第一晶体管的数量(第四配置)。

17.此外,在上述第四配置中,所述多个第一晶体管中的每个第一晶体管可以是pmos晶体管,并且所述预驱动器可以包括第一开关和第二开关,所述第一开关被设置在栅极信号的应用端子与所述多个第一晶体管中的所述每个第一晶体管的栅极之间,所述第二开关被设置在所述多个第一晶体管中的所述每个第一晶体管的所述栅极与源极之间(第五配置)。

18.此外,在上述第一配置中,所述电路参数可以是从所述要被驱动的晶体管的控制端子汲取的电流(第六配置)。

19.此外,在上述第六配置中,还可以提供预驱动器,所述预驱动器包括所述电流流过的第二晶体管部分,并且所述控制器可以使得在时间上改变所述第二晶体管部分的导通电阻(第七配置)。

20.此外,在上述第七配置中,所述第二晶体管部可以包括并联连接在所述控制端子与参考电位的应用端子之间的多个第二晶体管,并且所述控制器可以使得在时间上改变所述多个第二晶体管中处于启用状态并且能够导通/关断的并联连接的第二晶体管的数量(第八配置)。

21.此外,在上述第八配置中,所述多个第二晶体管中的每个第二晶体管可以是nmos晶体管,并且

22.所述预驱动器可以包括第三开关和第四开关,所述第三开关被设置在栅极信号的应用端子与所述多个第二晶体管中的所述每个第二晶体管的栅极之间,所述第四开关被设置在所述多个第二晶体管中的所述每个第二晶体管的所述栅极与源极之间(第九配置)。

23.此外,在上述第一配置中,所述电路参数可以是所述要被驱动的晶体管的反馈电容(第十配置)。

24.此外,在上述第十配置中,所述控制器可以使得在时间上改变并联连接的反馈电容的数量,所述并联连接的反馈电容包括作为所述要被驱动的晶体管的寄生电容的第一反馈电容和除了第一反馈电容之外的至少一个第二反馈电容中的被启用的第二反馈电容(第十一配置)。

25.此外,在上述第十一配置中,所述控制器可以控制第五开关以便在所述至少一个第二反馈电容的启用和禁用状态之间切换(第十二配置)。

26.此外,在上述第三配置中,所述第一晶体管部分可以包括pmos晶体管,并且所述控制器可以使得在时间上改变所述预驱动器的电源电压(第十三配置)。

27.此外,在上述第十三配置中,所述电源电压可以是由自举生成的启动电压(第十四配置)。

28.此外,在上述第十四配置中,所述控制器可以使得在时间上改变施加到包括在自

举中的二极管的阳极的电压(第十五配置)。

29.此外,本说明书中公开的本发明的另一方面是一种切换电路,包括任何上述配置的晶体管驱动电路和所述要被驱动的晶体管(第十六配置)。

30.此外,在上述第十六配置中,所述要被驱动的晶体管可以是nmos晶体管(第十七配置)。

31.此外,上述第十七配置还可以包括在低电位侧上的nmos晶体管,所述nmos晶体管与在高电位侧上的所述要被驱动的晶体管串联连接(第十八配置)。

32.此外,本说明书中公开的本发明的又一方面是一种开关电源电路,包括任何上述配置的切换电路。

33.发明的效果

34.根据本说明书中公开的晶体管驱动电路,可以降低emi噪声同时抑制切换损耗的增加。

附图说明

35.图1是示出根据本发明的图示性实施例的dc/dc转换器的配置的示意图。

36.图2是示出根据本发明第一实施例的晶体管驱动电路的部分配置的示意图。

37.图3是示出根据本发明第二实施例的晶体管驱动电路的部分配置的示意图。

38.图4是示出根据本发明第三实施例的晶体管驱动电路的部分配置的示意图。

39.图5是示出根据本发明第四实施例的晶体管驱动电路的部分配置的示意图。

40.图6是示出根据本发明第五实施例的dc/dc转换器的配置的示意图。

41.图7是示出根据本发明第六实施例的dc/dc转换器的配置的示意图。

42.图8示出了根据本发明第七实施例的dc/dc转换器的结构。

43.图9图示了示出对输入电压的纹波波形执行的fft分析的结果的示例的曲线图。

44.图10是用于解释mosfet的上升时间和下降时间的示意图。

具体实施方式

45.参考附图,下面描述本发明的图示性实施例。

46.《dc/dc转换器的配置》

47.图1是示出根据本发明的图示性实施例的dc/dc转换器10的配置的示意图。dc/dc转换器10是将输入电压vin降压以产生输出电压vout的降压转换器。

48.如图1所示,dc/dc转换器10包括切换电路5、电感器l1、输出电容器c1、启动电容器cb和二极管d1。

49.切换电路5包括晶体管驱动电路1、nmos晶体管m1和nmos晶体管m2。nmos晶体管m1和nmos晶体管m2将由晶体管驱动电路1开关驱动。

50.nmos晶体管m1和nmos晶体管m2串联连接在输入电压vin的应用端子和接地电位的应用端子之间以形成桥。具体地,nmos晶体管m1的漏极连接到输入电压vin的应用端子。nmos晶体管m1的源极在节点nsw处连接到nmos晶体管m2的漏极。nmos晶体管m2的源极连接到接地电位的应用端子。即,nmos晶体管m1是在高电位侧上的高侧晶体管,并且nmos晶体管m2是在低电位侧上的低侧晶体管。

51.电感器l1的一端连接到节点nsw。电感器l1的另一端连接到输出电容器c1的一端。输出电容器c1的另一端连接到接地电位的应用端子。在输出电容器c1的一端处生成输出电压vout。

52.互补地开关驱动nmos晶体管m1和nmos晶体管m2,使得当它们中的一个处于导通状态时,另一个处于关断状态。这种互补开关驱动还包括提供空载时间的情况,在该空载时间期间,为了例如防止出现通过电流的目的,它们都被置于关断状态。

53.启动电容器cb的一端连接到节点nsw。启动电容器cb的另一端连接到二极管d1的阴极。电源电压vcc施加到二极管d1的阳极。启动电容器cb和二极管d1构成自举6。在节点nb处生成启动电压vboot,二极管d1在节点nb处连接到启动电容器cb。

54.晶体管驱动电路1包括控制器2、预驱动器3和预驱动器4。预驱动器3使得启动电压vboot施加到nmos晶体管m1的栅极,以便使nmos晶体管m1进入导通状态,并且使在节点nsw处生成的开关电压vsw施加到上述栅极,以便使nmos晶体管m1进入关断状态。

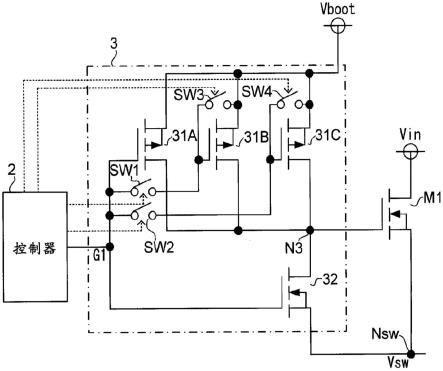

55.预驱动器4使得电源电压vreg施加到nmos晶体管m2的栅极,从而使nmos晶体管m2进入导通状态,并且使得接地电位施加到上述栅极,从而使nmos晶体管m2进入关断状态。

56.在nmos晶体管m1处于关断状态而nmos晶体管m2处于导通状态的情况下,经由二极管d1利用电源电压vcc给启动电容器cb充电,并且建立启动电压vboot=vcc-vf(vf:二极管d1的正向电压)。此后,当nmos晶体管m1处于导通状态而nmos晶体管m2处于关断状态时,建立启动电压vboot=vin vcc-vf,并且预驱动器3使得启动电压vboot被施加到nmos晶体管m1的栅极,以便使nmos晶体管m1进入导通状态。

57.控制器2控制预驱动器3和预驱动器4的驱动。

58.《第一实施例》

59.在本文中,给出了根据第一实施例的晶体管驱动电路1的描述。图2是示出了根据第一实施例的晶体管驱动电路1中的预驱动器3的内部配置的示意图。这里,nmos晶体管m1被指定为要被驱动的晶体管。

60.图2所示的预驱动器3包括pmos晶体管31a、31b和31c、nmos晶体管32以及开关sw1至sw4。关于所使用的pmos晶体管的数量,对三个pmos晶体管31a、31b和31c没有限制,并且数量可以是例如四个或更多个。

61.pmos晶体管31a、31b和31c并联连接在启动电压vboot的应用端子和节点n3之间。具体地,pmos晶体管31a、31b和31c的相应源极连接到启动电压vboot的应用端子。pmos晶体管31a、31b和31c的相应漏极连接到节点n3。

62.节点n3连接到nmos晶体管m1的栅极(控制端子)和nmos晶体管32的漏极。nmos晶体管32的源极连接到节点nsw。

63.用于输出栅极信号g1的控制器2的输出端子直接连接到pmos晶体管31a和nmos晶体管32的相应栅极中的每一个。此外,开关sw1设置在控制器2的上述输出端子与pmos晶体管31b的栅极之间。开关sw2设置在控制器2的上述输出端子与pmos晶体管31c的栅极之间。

64.开关sw3设置在pmos晶体管31b的栅极和源极之间。开关sw4设置在pmos晶体管31c的栅极和源极之间。

65.控制器2执行开关sw1至sw4的导通/关断控制。

66.控制器2使得处于高电平的栅极信号g1被施加到pmos晶体管31a和nmos晶体管32

11至sw 14。关于所使用的nmos晶体管的数量,对三个nmos晶体管32a、32b和32c没有限制,并且数量可以是例如四个或更多个。

78.pmos晶体管31连接在启动电压vboot的应用端子和节点n3之间。具体地,pmos晶体管31的源极连接到启动电压vboot的应用端子。pmos晶体管31的漏极连接到节点n3。节点n3连接到nmos晶体管m1的栅极。

79.nmos晶体管32a、32b和32c并联连接在节点n3和节点nsw之间。具体地,nmos晶体管32a、32b和32c的相应漏极连接到节点n3。nmos晶体管32a、32b和32c的相应源极连接到节点nsw。节点nsw是作为参考电位的开关电压vsw的应用端子。

80.用于输出栅极信号g1的控制器2的输出端子直接连接到pmos晶体管31和nmos晶体管32a的相应栅极中的每一个。此外,开关sw 11设置在控制器2的上述输出端子与nmos晶体管32b的栅极之间。开关sw 12设置在控制器2的上述输出端子与nmos晶体管32c的栅极之间。

81.开关sw 13设置在nmos晶体管32b的栅极和源极之间。开关sw 14设置在nmos晶体管32c的栅极和源极之间。

82.控制器2执行开关sw 11至sw 14的导通/关断控制。

83.控制器2使得处于高电平的栅极信号g1被施加到pmos晶体管31和nmos晶体管32a的栅极中的每一个,以便使pmos晶体管31进入关断状态并且使nmos晶体管32a进入导通状态。另一方面,控制器2使得处于低电平的栅极信号g1被施加到pmos晶体管31和nmos晶体管32a的栅极中的每一个,以便使pmos晶体管31进入导通状态并且使nmos晶体管32a进入关断状态。

84.此外,在启用nmos晶体管32b时,控制器2使开关sw 11进入导通状态并且使开关sw 13进入关断状态。因此,基于栅极信号g1的电平执行nmos晶体管32b的导通/关断驱动。另一方面,在禁用nmos晶体管32b时,控制器2使开关sw 11进入关断状态并且使开关sw 13进入导通状态。因此,nmos晶体管32b具有0v的vgs,从而进入关断状态。

85.此外,在启用nmos晶体管32c时,控制器2使开关sw 12进入导通状态并且使开关sw 14进入关断状态。因此,基于栅极信号g1的电平执行nmos晶体管32c的导通/关断驱动。另一方面,在禁用nmos晶体管32c时,控制器2使开关sw 12进入关断状态并且使开关sw 14进入导通状态。因此,nmos晶体管32c具有0v的vgs,从而进入关断状态。

86.nmos晶体管32a以及nmos晶体管32b和32c中的被启用nmos晶体管与pmos晶体管31处于当它们中的任一个处于导通状态时另一个进入关断状态的这种关系。

87.经由处于导通状态的pmos晶体管31从启动电压vboot的应用端子向nmos晶体管m1的栅极供应电流,并且因此nmos晶体管m1导通。此外,经由处于导通状态的nmos晶体管32a以及nmos晶体管32b和32c中的处于导通状态的被启用nmos晶体管从nmos晶体管m1的栅极汲取电流,并且因此nmos晶体管m1关断。

88.控制器2使得在时间上改变nmos晶体管32a、32b和32c中被启用并且能够导通/关断的并联连接的晶体管的数量。

89.更具体地,例如,当nmos晶体管m1的一个导通/关断操作被定义为一个切换操作时,在第一预定次数的切换操作期间,nmos晶体管32b和32c被禁用,在随后的第二预定次数的切换操作期间,nmos晶体管32b被启用而nmos晶体管32c被禁用,在随后的第三预定次数

的切换操作期间,nmos晶体管32b和32c被启用,在随后的另一第二预定次数的切换操作期间,nmos晶体管32b被禁用而nmos晶体管32c被禁用,并且在随后的另一第一预定次数的切换操作期间,nmos晶体管32b和32c被禁用。在这种情况下,被启用的并联连接的晶体管的数量从1变为2,2变为3,3变为2,2变为1。

90.因此,使得节点n3和节点nsw之间的导通电阻ron在时间上改变,并且因此可以使得从nmos晶体管m1的栅极汲取的电流在时间上改变。因此,nmos晶体管m1的下降时间tf(vds的下降时间tf)在时间上分布,并且因此可以降低emi噪声,同时抑制切换损耗的增加。上述电流对应于有助于nmos晶体管m1的下降时间tf的电路参数。

91.《第三实施例》

92.接下来,给出了根据第三实施例的晶体管驱动电路1的描述。图4是示出根据第三实施例的晶体管驱动电路1中的预驱动器4的内部配置的示意图。这里,nmos晶体管m2被指定为要被驱动的晶体管。

93.图4所示的预驱动器4包括pmos晶体管41a、41b和41c、nmos晶体管m42以及开关sw 21至sw 24。关于所使用的pmos晶体管的数量,对三个pmos晶体管41a、41b和41c没有限制,并且数量可以是例如四个或更多个。

94.根据该实施例的预驱动器4具有与根据第一实施例的预驱动器3的先前描述的配置(图2)类似的配置,其中该实施例的pmos晶体管41a、41b和41c分别对应于第一实施例的pmos晶体管31a、31b和31c,该实施例的nmos晶体管42对应于第一实施例的nmos晶体管32,并且该实施例的开关sw 21至sw 24分别对应于第一实施例的开关sw1至sw4。

95.该实施例在以下方面不同于第一实施例。即,pmos晶体管41a、41b和41c的相应漏极连接到电源电压vreg的应用端子。pmos晶体管41a、41b和41c的相应漏极连接到nmos晶体管42的漏极的节点n4连接到nmos晶体管m2的栅极。nmos晶体管42的源极连接到接地电位的应用端子。

96.以与第一实施例中的方式类似的方式,控制器2执行开关sw 21至sw 24的导通/关断控制,以便在pmos晶体管41b和41c的启用和禁用状态之间切换。基于从控制器2的输出端子输出的栅极信号g2的电平,执行pmos晶体管41a以及pmos晶体管41b和41c中的被启用pmos晶体管的导通/关断驱动。还执行nmos晶体管42的导通/关断驱动。pmos晶体管41a以及pmos晶体管41b和41c中的被启用pmos晶体管与nmos晶体管42处于当它们中的任一个处于导通状态时另一个进入关断状态的这种关系。

97.此外,以与第一实施例中的方式类似的方式,控制器2使得在时间上改变pmos晶体管41a、41b和41c中被启用并且能够导通/关断的并联连接的晶体管的数量。

98.因此,使得电源电压vreg的应用端子和节点n4之间的导通电阻ron在时间上改变,并且从而可以使得被供应给nmos晶体管m2的栅极的电流在时间上改变。因此,nmos晶体管m2的上升时间tr(vds的上升时间tr)在时间上分布,并且从而可以降低emi噪声,同时抑制切换损耗的增加。

99.《第四实施例》

100.接下来,给出了根据第四实施例的晶体管驱动电路1的描述。图5是示出根据第四实施例的晶体管驱动电路1中的预驱动器4的内部配置的示意图。这里,nmos晶体管m2被指定为要被驱动的晶体管。

101.图5所示的预驱动器4包括pmos晶体管41、nmos晶体管42a、42b和42c以及开关sw 31至sw 34。关于所使用的nmos晶体管的数量,对三个nmos晶体管42a、42b和42c没有限制,并且数量可以是例如四个或更多个。

102.根据该实施例的预驱动器4具有与根据第二实施例的预驱动器4的先前描述的配置(图3)类似的配置,其中该实施例的pmos晶体管41对应于第二实施例的pmos晶体管31,该实施例的nmos晶体管42a、42b和42c分别对应于第二实施例的nmos晶体管32a、32b和32c,并且该实施例的开关sw 31至sw 34分别对应于第二实施例的开关sw 11至sw 14。

103.该实施例在以下方面不同于第二实施例。即,pmos晶体管41的漏极连接到电源电压vreg的应用端子。pmos晶体管41的漏极连接到nmos晶体管42a、42b和42c的漏极的节点n4连接到nmos晶体管m2的栅极。nmos晶体管42a、42b和42c的相应源极连接到接地电位(参考电位)的应用端子。

104.以与第二实施例中的方式类似的方式,控制器2执行开关sw 31至sw 34的导通/关断控制,以便在nmos晶体管42b和42c的启用和禁用状态之间切换。基于从控制器2的输出端子输出的栅极信号g2的电平,执行nmos晶体管42a以及nmos晶体管42b和42c中的被启用nmos晶体管的导通/关断驱动。基于栅极信号g2的电平,还执行pmos晶体管41的导通/关断驱动。nmos晶体管42a以及nmos晶体管42b和42c中的被启用nmos晶体管与pmos晶体管41处于当它们中的任一个处于导通状态时另一个进入关状态的这种关系。

105.此外,以与第二实施例中的方式类似的方式,控制器2使得在时间上改变nmos晶体管42a、42b和42c中被启用且能够导通/关断的并联连接的晶体管的数量。

106.因此,使节点n4与接接地电位的应用端子之间的导通电阻ron在时间上改变,并且因此可使从nmos晶体管m2的栅极汲取的电流在时间上改变。因此,nmos晶体管m2的下降时间tf(vds的下降时间tf)在时间上分布,并且因此可以降低emi噪声,同时抑制切换损耗的增加。

107.《第五实施例》

108.接下来,给出了第五实施例的描述。图6是示出包括根据第五实施例的切换电路5的配置的dc/dc转换器10的示意图。这里,nmos晶体管m1被指定为要被驱动的晶体管。

109.如图6所示,根据该实施例的切换电路5包括作为nmos晶体管m1的栅极和漏极之间的寄生电容的反馈电容cgd1、以及连接在nmos晶体管m1的栅极和漏极之间的反馈电容cgd2和cgd3。关于除了连接在nmos晶体管m1的栅极和漏极之间的寄生电容之外的反馈电容的数量,对两个反馈电容cgd2和cgd3没有限制,并且数量可以是例如三个或更多个。

110.反馈电容cgd2和cgd3中的每一个的一端直接连接到nmos晶体管m1的栅极。反馈电容cgd2和cgd3中的每一个的另一端经由开关s1和s2中的对应开关连接到nmos晶体管m1的漏极。

111.控制器2执行开关s1和s2的导通/关断控制。当开关s1和s2处于导通状态时,启用反馈电容cgd2和cgd3,而当开关s1和s2处于关断状态时,禁用反馈电容cgd2和cgd3。

112.在该实施例中,控制器2使得在时间上改变在反馈电容cgd1、cgd2和cgd3中在nmos晶体管m1的栅极和漏极之间并联连接且启用的反馈电容的数量。

113.更具体地,例如,当nmos晶体管m1的一个导通/关断操作被定义为一个切换操作时,在第一预定次数的切换操作期间,反馈电容cgd2和cgd3被禁用,在随后的第二预定次数

的切换操作期间,反馈电容cgd2被启用而反馈电容cgd3被禁用,在随后的第三预定次数的切换操作期间,反馈电容cgd2和cgd3被启用,在随后的另一第二预定次数的切换操作期间,反馈电容cgd2被启用而反馈电容cgd3被禁用,并且在随后的另一第一预定次数的切换操作期间,反馈电容cgd2和cgd3被禁用。在这种情况下,并联连接且启用的反馈电容的数量从1变为2,2变为3,3变为2,2变为1。

114.因此,使得nmos晶体管m1的栅极和漏极之间的反馈电容在时间上改变,使得nmos晶体管m1的上升时间tr和下降时间tf在时间上分布,并且因此可以降低emi噪声,同时抑制切换损耗的增加。上述反馈电容对应于有助于nmos晶体管m1的上升时间tr和下降时间tf的电路参数。

115.《第六实施例》

116.接下来,给出了第六实施例的描述。图7是示出包括根据第六实施例的切换电路5的配置的dc/dc转换器10的示意图。这里,nmos晶体管m2被指定为要被驱动的晶体管。

117.如图7所示,根据该实施例的切换电路5包括为nmos晶体管m2的栅极和漏极之间的寄生电容的反馈电容cgd11、以及连接在nmos晶体管m2的栅极和漏极之间的反馈电容cgd12和cgd13。关于除了连接在nmos晶体管m2的栅极和漏极之间的寄生电容之外的反馈电容的数量,对两个反馈电容cgd12和cgd13没有限制,并且数量可以是例如三个或更多。

118.反馈电容cgd12和cgd13中的每一个的一端直接连接到nmos晶体管m2的栅极。反馈电容cgd12和cgd13中的每一个的另一端经由开关s11和s12中的对应开关连接到nmos晶体管m2的漏极。

119.控制器2执行开关s11和s12的导通/关断控制。当开关s11和s12处于导通状态时,启用反馈电容cgd12和cgd13,而当开关s11和s12处于关断状态时,禁用反馈电容cgd12和cgd13。

120.在该实施例中,控制器2使得在时间上改变在反馈电容cgd11、cgd12和cgd13中在nmos晶体管m2的栅极和漏极之间并联连接且启用的反馈电容的数量。

121.更具体地,例如,当nmos晶体管m2的一个导通/关断操作被定义为一个切换操作时,在第一预定次数的切换操作期间,反馈电容cgd12和cgd13被禁用,在随后的第二预定次数的切换操作期间,反馈电容cgd12被启用而反馈电容cgd13被禁用,在随后的第三预定次数的切换操作期间,反馈电容cgd12和cgd13被启用,在随后的另一第二预定次数的切换操作期间,反馈电容cgd12被启用而反馈电容cgd13被禁用,并且在随后的另一第一预定次数的切换操作期间,反馈电容cgd12和cgd13被禁用。在这种情况下,并联连接且启用的反馈电容的数量从1变为2,2变为3,3变为2,2变为1。

122.因此,使得nmos晶体管m2的栅极和漏极之间的反馈电容在时间上改变,使得nmos晶体管m2的上升时间tr和下降时间tf在时间上分布,并且因此可以降低emi噪声,同时抑制切换损耗的增加。

123.《第七实施例》

124.图8是示出根据第七实施例的dc/dc转换器10的配置的示意图。这里,nmos晶体管m1被指定为要被驱动的晶体管,在图8所示的dc/dc转换器10中,在自举6中提供了开关sw1至sw3。

125.开关sw1设置在预定电源电压vcc1的应用端子和二极管d1的阳极之间。开关sw2设

71.6db。

138.如图9的左侧附图所示,500khz波形具有200mv的幅度,并且因此其rms值由200mv/(2

×

√2)=70.7mv表示,使得获得由20

×

log(70.7mv)=-23db表示的频谱值,这与图9的右侧附图所示的结果基本上一致。然而,130mhz波形具有120mv的幅度,并且因此其rms值由120mv/(2

×

√2)=42.4mv表示,使得获得由20

×

log(42.4mv)=-27db表示的频谱值,这与图9的右侧附图中所示的结果不一致。

139.在本文中,如图9的左侧附图所示,在高达10秒的fft范围内,130mhz处的噪声ns1在由1/130mhz

×

5=38ns表示的时间段内出现五次。因此,其出现概率由38ns/10s=0.0038=-48.4db表示。因此,考虑到出现概率的频谱值由-27db (-48db)=-75db表示,这与图9的右侧附图所示的结果基本上一致。

140.因此,如在前述实施例中,上升时间tr和下降时间tf在时间上分布,并且因此在相同频率处出现噪声的概率减小,使得可以减小噪声的频谱值。

141.《其他》

142.虽然前面已经描述了本发明的实施例,但是在不脱离本发明的精神的情况下,可以对实施例进行各种修改。

143.例如,只要不存在不一致性,前述实施例就可以以其任何组合来实施。

144.此外,在前述实施例中的每一个中的切换电路5中,可以使用pmos晶体管来代替高侧上的nmos晶体管m1。在这种情况下,使用低于输入电压vin的电压作为预驱动器3的电源电压就足够了,并且因此不需要通过自举等生成预驱动器3的电源电压。

145.此外,根据本发明的晶体管驱动电路不限于降压型dc/dc转换器,并且还可应用于包括各种类型的dc/dc转换器(例如升压型、升压和降压型、非隔离和隔离dc/dc转换器以及dc/ac转换器(逆变器))的切换电源电路,并且还可应用于除了电源电路之外的其他类型的电路。

146.此外,由根据本发明的晶体管驱动电路驱动的晶体管不限于mosfet,并且例如可以是igbt。

147.工业上的可利用性

148.本说明书中公开的本发明可用于驱动各种类型的晶体管。

149.符号的说明

150.1晶体管驱动电路

151.2控制器

152.3预驱动器

153.4预驱动器

154.5切换电路

155.6自举

156.10dc/dc转换器

157.m1、m2nmos晶体管

158.l1电感器

159.c1输出电容器

160.cb启动电容器

161.d1二极管

162.31a至31cpmos晶体管

163.32nmos晶体管

164.sw1至sw4开关

165.31pmos晶体管

166.32a至32cnmos晶体管

167.sw11至sw14开关

168.41a至41cpmos晶体管

169.42nmos晶体管

170.sw21至sw24开关

171.41pmos晶体管

172.42a至42cnmos晶体管

173.sw31至sw34开关

174.cgd1至cgd3反馈电容

175.s1、s2开关

176.cgd11至cgd13反馈电容

177.s11、s12开关

178.sw1至sw3开关

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。