1.本发明属于模拟集成电路的设计技术领域,具体涉及一种共享比较器的张弛振荡器。

背景技术:

2.时钟是绝大多数集成电路里都需要的。芯片上时钟的来源,除了从片外输入外,则必须靠集成的振荡器模块产生。图1是使用两个电容交替充放电的张弛振荡器的电路图。传统的电路中使用两个比较器,来分别控制两个电容充电结束时到达的最高电压幅度。电容c1和c2交替充放电。如果忽略两个比较器的各自输入失调电压(input offset voltage)和输出翻转的延时(output toggling delay),每次充电时电流将电容c1(或)c2上的电压v1(或)v2,从零充至,而另一个电容c2(或)c1则保持放电状态,其电压v2(或)v1停在零电位。

3.如前所述,比较器有两个主要的非理想因素,即输入失调电压和输出翻转延时。在实际的芯片设计中,这两个比较器的非理想因素对振荡器性能产生不利影响,比如增加频率的温度漂移。因此,为了减小不利影响,需要降低比较器的输入失调电压和输出翻转延时。提高比较器的这两项性能,则需要显著增加比较器的功耗和面积。

4.另外,两个比较器的输入失调电压和输出翻转延时,各自都存在失配(mismatch)的问题。当振荡器的频率越高且需要精确的占空比(duty-cycle)时,为了减小失配引起的性能损失,也需要进一步增加比较器的功耗和面积。

技术实现要素:

5.本发明的目的在于提供一种共享比较器的张弛振荡器,以解决上述张弛振荡器使用两个比较器带来的双倍功耗和芯片面积较大的问题。

6.为实现上述目的,本发明提供如下技术方案:一种共享比较器的张弛振荡器,该张弛振荡器包括:

7.振荡器核心模块,包括电流源i

osc

、电容c1以及电容c2,操作于输入两相不交叠时钟ph1和ph2,并在处理后输出为两个电容的上的电压v1和v2;

8.二选一mux模块,操作于输入电压v1和v2,并在处理后输出电压v12;

9.比较器,操作于输入二选一mux模块输出的电压v12,并在电压v12达到其负端的参考直流电压vref时,比较器的输出将由低到高发生翻转;

10.上升沿转脉冲模块,操作于获取由低到高发生翻转的信号,并同时产生一个脉冲输出信号rs;

11.一分二demux模块,操作于接受脉冲输出信号rs,并依次交替地将rs脉冲信号分解为r

reset

和s

set

信号;

12.rs锁存器,操作于输入r和s信号,并对其处理后输出两相交叠时钟ph1和ph2,及其反相时钟ph1b和ph2b。

13.优选地,所述张弛振荡器还包括:

14.延时模块,操作于输入两相不交叠时钟ph1和ph2,并在处理后向一分二demux模块输入两相不交叠时钟ph1d和ph2d。

15.优选地,所述张弛振荡器的工作时序分为未使能状态和使能状态。

16.优选地,当张弛振荡器处于未使能工作状态时,使能信号en为低电位,而其反相信号enb为高电位,并且时钟ph1d和ph2d均为低电位。

17.优选地,所述张弛振荡器处于使能状态时,其工作的一个振荡周期由前半个振荡周期和后半个振荡周期组成。

18.与现有技术相比,本发明的有益效果是:

19.1)本发明张弛振荡器,共享比较器,节省芯片的面积和功耗。

20.2)本发明张弛振荡器,避免了两个比较器之间的失配,如输入失调电压和输出翻转延时,带来的时钟占空比误差。

21.3)本发明张弛振荡器,电路实现简洁、可靠,只增加了少量的开关数字逻辑,其功耗和面积都可以忽略。

22.4)本发明张弛振荡器,将比较器输出的上升沿转换为窄脉冲,并通过延时的开关完成demux功能,巧妙地解决本发明中的技术难题。

23.5)本发明,类似上述的设计技术,也可以用于其他不同的芯片中。

附图说明

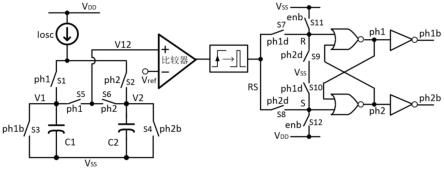

24.图1是传统的使用两个比较器的张弛振荡器;

25.图2是本发明的共享一个比较器的张弛振荡器;

26.图3是本发明的张弛振荡器的功能模块解析图;

27.图4是本发明的张弛振荡器的内部信号时序图;

28.图5是本发明的张弛振荡器的脉冲产生和时钟延时电路图。

具体实施方式

29.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

30.本发明实施例一种共享比较器的张弛振荡器,图2所示为本发明共享比较器的张弛振荡器线路图,而图3是本发明的张弛振荡器的功能原理和信号的控制与发生图。

31.原理图3中的振荡器核心模块,即由线路图2中的电流源i

osc

、电容c1和c2、以及开关s1~s4组成。如图4所示,该模块的输入为两相不交叠时钟ph1和ph2,而输出为两个电容的上的电压v1和v2。图3中的二选一mux模块由图2中的开关s5和s6构成;该模块的输入为电压v1和v2,而输出为图4中所示的电压v12。

32.每当比较器的正端输入电压v12达到其负端的参考直流电压vref时,比较器的输出由低到高翻转。此时,比较器之后的上升沿转脉冲模块将产生一个很窄(比如1纳秒左右)的脉冲输出信号rs。

33.脉冲产生模块之后的一分二demux模块负责依次交替地将rs脉冲信号分解为r

reset

和s

set

信号,作为之后rs锁存器的输入。图3中的demux模块,由图2中的开关s7~s

10

组成。r和

s信号的初始状态(即当使能信号en为低电位,而其反相信号enb为高电位时),经由开关s

11

和s

12

分别设置为低电位和高电位。

34.最后rs锁存器的输出即为两相交叠时钟ph1和ph2,及其反相时钟ph1b和ph2b。具体的信号时序和控制关系如图4所示。

35.本发明的张弛振荡器的工作时序如图3所示,描述如下:

36.当振荡器处于未使能状态时,节点r和s分别通过开关s

11

和s

12

设置为低电位和高电位。因此在初始状态时,时钟ph1、ph1d、ph2b均为高电位,而ph2、ph2d、ph1b均为低电位。

37.当开始使能振荡器时,开关s1和s4合上,s2和s3断开。电流源i

osc

开始对电容c1充电,其上电压v1开始上升,而电容c2处于已经放电状态,其上电压v1保持为零。

38.此时开关ss合上,s6断开,故二选一mux输出电压v12=v1。当电容c1持续充电至电压v12=v

ref

时,比较器的输出由低至高翻转,继而上升沿至脉冲转换模块输出脉冲的上升沿。此时时钟ph1d控制的开关依旧合上,故信号r产生上升沿,进一步触发了rs锁存器的输出翻转,即时钟ph1变低,而ph2变高。前半个振荡周期结束。

39.时钟ph2变高,ph1变低后,电容c1被迅速放电,而电容c2充电,开始了后半个振荡周期。后半个振荡周期,与前述的前半个周期类似。当后半个振荡周期结束时,又开始了下一个振荡周期。

40.需要注意的是,为了让窄脉冲rs通过开关s7或s6,控制开关s7~s

10

的时钟ph1d和ph2d相对于时钟ph1和ph2的延时(delay),必须大于脉冲rs的宽度。图5是窄脉冲rs以及延时的时钟ph1d和ph2d产生电路的一个实现例子。在图5中,时钟延时是窄脉冲宽度的大约两倍。比如窄脉冲rs的宽度为1ns,而ph1d和ph2d相对于时钟ph1和ph2的延时为2ns。另外,当本发明的振荡器未使能时,即en为低电位而enb为高电位时,时钟ph1d和ph2d均为低电位使开关s7~s

10

全部断开。如前所述,此时节点r和s分别通过开关s

11

和s

12

设置为低电位和高电位。

41.尽管已描述了本发明的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本发明范围的所有变更和修改。

42.显然,本领域的技术人员可以对本发明进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。