一种sip塑料封装件及其生产方法

技术领域

1.本发明属于微电子组装与封装技术领域,具体涉及一种sip塑料封装件及其生产方法。

背景技术:

2.集成电路器件的封装从单个组件的开发,进入到多个组件的集成后,半导体封装逐步向高密度、高集成度、高频高速、小面积、低成本、多芯片组合,以及与具有不同功能的有源电子元件,可选无源器件组配的趋势发展、整合。从封装发展的角度来看,电子产品在体积、处理速度或电性特性等各方面的需求考量下,sip级封装选取多种隔离芯片进行排列组装,采用平面式2d封装结构,搭配多功能性变压器等整合组件的方式,形成完整的系统功能,从而实现产品的性能需求。通过对sip级隔离封装产品长期应用效果跟进,设计结构上存在支撑杆或连接杆结构的产品,长期使用会对产品的性能产生影响,降低产品的应用,最终造成产品的失效,从而影响产品的正常运行,对于产品的使用是致命的,严重影响产品安全。

技术实现要素:

3.本发明的目的在于克服上述现有技术的缺点,提供一种sip塑料封装件及其生产方法,以解决现有技术中sip塑料封装件在使用过程中,因支撑杆或连接杆的使用而影响产品性能,造成产品失效的问题。

4.为达到上述目的,本发明采用以下技术方案予以实现:

5.一种sip塑料封装件,包括基岛隔离框架,所述基岛隔离框架上分别沿长度方向和宽度方向阵列有基岛隔离单元;每一个基岛隔离单元两个相对的侧边上均设置有引脚;

6.每一个基岛隔离单元上设置有第一载体、第二载体、第三载体、第四载体、第五载体和第六载体;每一个基岛隔离单元中至少有两个载体相对排列,相对排列的载体之间有间距;每一个载体至少连接有一个引脚;

7.载体上安装有芯片和变压器,变压器上安装有的焊盘,所述焊盘通过焊线至少连接有一个引脚,所述焊盘通过焊线至少连接有一个芯片,所述芯片通过焊线至少连接有一个引脚;

8.所述基岛隔离单元被塑封体本体塑封。

9.本发明的进一步改进在于:

10.优选的,相对排列的载体之间距离≥0.5mm。

11.优选的,所述塑封体本体沿其周向安装有塑封体光亮带;所述塑封体本体上开设有标记孔。

12.优选的,所述第二载体和第五载体相对设置,所述第一载体和第六载体相对设置,所述第三载体和第四载体相对设置;所述第一载体和第三载体之间通过第一载体连接部位连接,所述第五载体和第四载体之间通过第六载体连接部位连接;所述第一载体连接部位

的一端和第一载体连接,所述第六载体连接部位的一端和第六载体连接;

13.所述第二载体上安装有第一芯片和第二芯片,所述第五载体上安装有第三芯片,所述第四载体上安装有第四芯片,所述第三载体上安装有第五芯片;变压器的底部同时和第一载体和第六载体连接;

14.所述第一芯片和第二芯片通过焊线连接,第二芯片和第三芯片通过八组焊线连接,变压器上的焊盘通过焊线分别和第四芯片及第五芯片连接,第四芯片和第五芯片通过焊线连接。

15.优选的,所述第二载体上开设有第一锁定孔和第二锁定孔,所述第五载体上开设有工艺通孔。

16.优选的,所述第六载体连接有第五载体,第一载体和第五载体相对设置;第六载体通过第六载体连接部位和第四载体连接,第一载体通过第一载体连接部位和第二载体连接,第二载体和第三载体连接;

17.所述变压器共同安装在第一载体和第五载体上,所述第四载体上安装有第三芯片和第五芯片,所述第二载体上安装有第一芯片、第二芯片和第四芯片;变压器上的焊盘通过焊线分别和第四芯片、第五芯片和第一芯片连接,第四芯片和第五芯片通过焊线连接,第二芯片和第三芯片通过八组焊线连接,第二芯片和第一芯片通过焊线连接。

18.优选的,所述第二载体和第五载体相对设置,所述第一载体和第六载体相对设置,所述第三载体和第四载体相对设置;所述第二载体和第三载体通过第一载体连接部位连接,所述第四载体和第五载体通过第六载体连接部位连接;所述第一载体连接部位的另一端和第一载体连接,所述第六载体连接部位的另一端和第六载体连接;

19.所述第二载体上设置有第一芯片和第二芯片,所述第五载体上设置有第三芯片,所述第四载体上设置有第四芯片,所述第三载体上设置有第五芯片;所述变压器共同设置在第一载体和第六载体上;所述第一芯片和第二芯片通过焊线接,所述第二芯片和第三芯片通过八组焊线连接,所述第四芯片和第五芯片通过焊线连接,所述变压器上的焊盘通过焊线分别和第四芯片与第五芯片连接。

20.优选的,所述第一载体和第五载体相对设置,所述第一载体通过第一载体连接部位和第二载体连接,所述第五载体和第六载体连接,第六载体通过第六载体连接部位和第四载体连接,所述第二载体和第三载体连接,所述第二载体和第四载体相对设置;

21.所述变压器共同设置在第一载体和第五载体上,所述第二载体上设置有第四芯片,所述第四载体上设置有第五芯片,所述第四芯片和第五芯片通过焊线连接,所述变压器上的焊盘通过焊线分别与第四芯片和第五芯片连接。

22.一种上述的sip塑料封装件的生产方法,包括以下步骤:

23.步骤1,将晶圆减薄后划片,形成芯片;

24.步骤2,通过上芯粘片喷胶技术将芯片粘贴在基岛隔离单元的载体上,将变压器粘结在基岛隔离单元上;将粘结有芯片和变压器的基岛隔离单元烘烤,使得芯片在基岛隔离单元上固化;

25.步骤3,通过键合低弧度控制技术键合焊线;

26.步骤4,对基岛隔离单元进行塑封;

27.步骤5,采用自动电镀线对封装件的引线框架进行镀锡,进行焊接。

28.优选的,步骤2中,烘烤过程采用七个不同含氧区固化基岛隔离框架。

29.与现有技术相比,本发明具有以下有益效果:

30.本发明提供了一种sip塑料封装件,该塑料封装件设置有各个基岛隔离单元,基岛个单元上设置有多个载体,载体上设置有芯片和变压器,芯片和变压器通过焊线对应连接。该本发明新型封装材料、特殊封装工艺、精细化封装流程实现了一整套sip封装技术工艺标准和规范,解决高压与低压电路间传输数据和电能问题,满足市场对高电性能、高可靠性、高散热电源管理、高耐压、高安全产品的需求,替代传统光耦器件的趋势,促进电感隔离ic封装技术水平提高。封装件所用高密度引线框架特殊结构设计,能够极大限度地提高材料利用率、生产效率,保障塑封件达到msl3以上的高可靠性,降低生产成本和包装运输成本。

31.本发明提供了一种sip塑料封装件的生产方法,是提供一种通过引线框架和固定bom生产高可靠性变压器隔离功能的sip塑料封装件的方法,以解决现有的因为支撑杆或连接杆结构引起的产品失效与产品安全的问题。提供的高效率的生产方法可生产出具有可靠性达到msl3及上的电感隔离功能的ic封装件。本发明电磁式隔离芯片的sip封装件采用新颖的封装结构和适配性强的bom组合生产方法:其结构合理,工艺路线简单,bom易于实现,相比传统光耦隔离产品可以实现成本更低、尺寸更小、高隔离耐压、宽温度范围、高集成度性能、低的功耗和更加高可靠隔离电路,并且拥有高通信速率长寿命。因此,为了获得更好的隔离耐压效果,通过优化设计框架结构及改进封装制程工艺,从而解决产品的物理隔离,使高压区和低压区满足爬电的要求,同时提升产品的生产效率,实现多排多基岛高密度隔离框架的制作。为此而制作的高压隔离式dc-dc转换器,在消费、工业、汽车、通讯等领域具有广泛应用。

附图说明

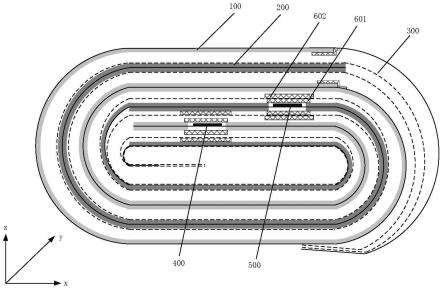

32.图1是本发明隔离框架示意图;

33.图2是本发明引线框架排样结构示意图;

34.图3是本发明sop、sow互封装件外形示意图;

35.图4是本发明引线框架结构1示意图;

36.其中,(a)图是载体示意图;(b)图是安装有芯片的示意图;

37.图5是本发明引线框架结构2示意图;

38.其中,(a)图是载体示意图;(b)图是安装有芯片的示意图;

39.图6是本发明引线框架结构3示意图;

40.其中,(a)图是载体示意图;(b)图是安装有芯片的示意图;

41.图7是本发明引线框架结构4示意图;

42.其中,(a)图是载体示意图;(b)图是安装有芯片的示意图;

43.图8是本发明产品剖面结构示意图。

44.其中,图中:1.第一载体,2.第一载体连接部位,3.外引脚,4.内引脚,5.第二载体,6.第三载体,7.第四载体,8.第六载体连接部位,9.第五载体,10.第六载体,11.变压器,12.焊盘,13.第一芯片,14.第二芯片,15.第三芯片,16.第四芯片,17.第五芯片,18.焊线,19.内管脚,20.第一锁定孔,21.第二锁定孔,22.工艺通孔,23.变压器,24.胶水,25.塑封体本体,26.塑封体光亮带,27.标记孔,28.引脚,29.外观脚镀银,30.基岛隔离框架,31.框架边

框,32.基岛隔离单元。

具体实施方式

45.下面结合附图对本发明做进一步详细描述:

46.在本发明的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制;术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性;此外,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

47.本发明公开了一种sip塑料封装件,该sip塑料件封装件包括基岛隔离框架30、第一载体5、第二载体9、第三载体7、第四载体6、第五载体10和第六载体1。

48.实施例1

49.参见图1和图2,本实施例公开了一种电磁式隔离框架与变压器芯片合封的sip塑料封装件,其包括基岛隔离框架30,参见图2,基岛隔离框架30的边部设置有框架边框31,基岛隔离框架30的内部由若干个基岛隔离单元32阵列组成,从图1和图2中可以看出基岛隔离框架30上的基岛隔离单元32呈阵列式高密度排列,有多排多列,每一个框架内部单元32由变压器封装。

50.优选的,基岛隔离框架30每条7排16列,共有112个单元框架,基岛隔离框架30的尺寸长

×

宽

×

厚:269.6

×

83

×

mm。

51.优选的,相邻列的基岛隔离单元32之间的距离:16.875mm,两塑封体边缘距离:8.450mm。

52.相对排列的载体之间距离大于或等于0.5mm,沿载体的相对两边设有复数个放射状的引脚28分列基岛隔离单元32的两长边,第二载体5中心部位设有n个隔离锁定孔21;第五载体9中心部位设有n个工艺通孔22,每个引脚28上均设有t型锁定台阶;每一个载体至少有一端与至少一引脚28相连接。

53.实施例2

54.参见图3,本实施例中公开了一种塑封后的基岛隔离单元32,基岛隔离单元32为矩形,其相对的两个长边上分别阵列有成型外脚28,所述成型外脚28上设置有焊接区29,基岛隔离单元32的内部安装有各个器件,上部被塑封体本体25塑封,塑封体本体25沿其周边设置有塑封体光亮带26,塑封体本体25上开设有标记孔27,优选的,标记孔27开设在塑封体本体25的一个角落处,防止对基岛隔离单元32中的器件有影响。

55.基岛隔离框架30的定位孔到基岛隔离框架片角剪口距离,始端8.890mm,末端9.860mm。

56.载体隔离框架第一载体5、第四载体6和第六载体1分别与第二载体9、第三载体7及第五载体10形成一定的隔离距离。

57.载体隔离框架载体上粘有芯片,变压器,外层包覆塑封体的外形特征,

58.实施例3

59.参见图4中的(a)图,本实施例中公开了一种引线框架结构,具体的包括基岛隔离单元32,基岛隔离单元32上设置有多个载体,具体的包括第一载体1、第二载体5、第三载体6、第四载体7、第五载体9和第六载体10。基岛隔离单元32的两个长边分别阵列有若干个引脚28,每一个引脚28包括一体连接的外引脚3和内引脚4,每一个引脚28均垂直于长边,相邻的引脚28之间等间距设置。所述第一载体1通过第一载体连接部位2和第三载体6连接,第一载体连接部位2的连接有两个引脚28,靠近第一载体1的引脚28用于传输第一载体1的相关信息,靠近第三载体6的引脚28用于传输第三载体6的相关信息。所述第二载体5上开设有第一锁定孔20和第二锁定孔21,以进行隔离和锁定;所述第五载体9通过第六载体连接部位8和第四载体7连接,第六载体连接部位8上设置有第六载体10,第五载体9上开设有工艺通孔22。所述锁定孔的形状能够为圆形锁定孔或椭圆形锁定孔,锁定孔数量可以有多个锁定孔,载体设计为平面结构。

60.参见图4中的(b)图,所述第二载体5上的芯片安装区安装有第一芯片13和第二芯片14,每一个芯片均通过焊线18和内引脚4连接,第一芯片13和第二芯片14通过八组焊线18连接。第五载体9上安装有第三芯片15,第三芯片15通过多个引线和第二芯片14连接,第三芯片15通过多个引线和内引脚4连接,所述第一载体连接部位2和第六载体连接部位8上共同安装有变压器11,利用胶膜或胶粘接;变压器11表面的焊盘12通过焊线分别于基岛隔离框架单元32左右区域内引脚28上的电镀银层相连,焊盘12,焊盘12的面积大小不超过两个载体连接部位的边线,即不超过载体间距11。所述第四载体7上安装有第四芯片16,第三载体6上安装有第五芯片17,第四芯片16通过多个焊线18分别和内引脚4、焊盘12和第五芯片17连接,第五芯片17通过多个焊线18分别和内引脚4、焊盘12和第四芯片16连接。

61.基岛隔离框架单元32与第一芯片13、第二芯片14第三芯片15、第四芯片16、第五芯片17及变压器11表面外部包覆塑封体,形成合封的封装件。

62.实施例4

63.参见图5中的(a)图,本实施例中公开了一种引线框架结构,具体的包括基岛隔离单元32,基岛隔离单元32中设置有多个载体,具体的包括第一载体1、第二载体5、第四载体7和第五载体9,第一载体1通过第一载体连接部位2和第二载体5连接,第五载体9通过第六载体连接部位8连接,第五载体9中设置有第六载体10。第一载体1和第五载体9在基岛隔离单元32的一侧,第四载体7和第二载体5在基岛隔离单元32的另一侧,第一载体1和第五载体9之间设置有间隙,为载体间距11。

64.参见图5中的(b)图,第一载体1和第五载体9上共同设置有变压器11,变压器11的上表面安装有焊盘12,焊盘12通过不同的焊线18和多个引脚28连接;第四载体7上设置有第三芯片15和第五芯片17,两个芯片在第四载体7上分开设置有,第五芯片17更靠近;第二载体5上设置有第一芯片13、第二芯片14和第四芯片16,三个芯片在第二载体5上分开设置;第四芯片16通过焊线18分别与焊盘12、第二芯片14以及第五芯片17连接;第一芯片13通过焊线18分别与引脚28、焊盘12、第二芯片14连接;第二芯片14通过焊线18分别与第一芯片13、第四芯片16以及第三芯片15连接;第三芯片15通过焊线18分别与第二芯片14、引脚28以及第五芯片17连接;第五芯片17通过焊线18分别与第三芯片15、第四芯片16、焊盘12以及引脚28连接。

65.基岛隔离单元32、变压器11、第三芯片15、第五芯片17、第一芯片13、第二芯片14和第四芯片16表面外部包覆塑封体,形成合封的封装件。

66.实施例5

67.参见图6中的(a)图,本实施例中公开了一种引线框架结构,具体的包括基岛隔离单元32,基岛隔离单元32中设置有多个载体,具体的包括第一载体1、第二载体5、第三载体6、第四载体7、第五载体9和第六载体10;沿基岛隔离单元32的长度方向,每一个基岛隔离单元32的两侧分别设置有一排等间距设置的引脚28;沿基岛隔离单元32的长度方向,第二载体5和第五载体9在基岛隔离单元32的一侧,第一载体1和第六载体10设置在中间位置,另一侧设置有第三载体6和第四载体7,第二载体5和第五载体9之间有间距,第一载体1和第六载体10之间有间距,第三载体6和第四载体7之间有间距;第五载体9和第四载体7分别和第六载体连接部位8的两端分别连接,第六载体连接部位8的另一端和第六载体10连接;第二载体5和第三载体6分别和第一载体连接部位2的两端分别连接,第一载连接部位2的另一端和第一载体2连接。

68.参见图6中的(b)图,第二载体5上设置有第一芯片13和第二芯片14,第五载体9上设置有第三芯片15,第一芯片13通过焊线18分别和引脚28以及第二芯片14连接,第二芯片14通过焊线18分别与第三芯片15、引脚28以及第一芯片13连接。第三芯片15通过焊线18分别与第二芯片14以及引脚28连接。第一载体1和第六载体10上共同设置有焊盘12,焊盘12通过焊线18和引脚28连接。第四载体7上设置有第四芯片16,第三载体6上设置有第五芯片17,第四芯片16通过焊线18分别连接有引脚28、焊盘12和第五芯片17,第五芯片17通过焊线18分别连接有第四芯片16、焊盘12和引脚28。

69.基岛隔离单元32、变压器11、第三芯片15、第五芯片17、第一芯片13、第四芯片16第二芯片14表面外部包覆塑封体,形成合封的封装件。

70.实施例6

71.参见图7中(a)图,本实施例中公开了一种引线框架结构,具体的包括基岛隔离单元32,基岛隔离单元32中设置有多个载体,具体的包括第一载体1、第五载体9、第四载体7和第二载体5。第一载体1通过第一载体连接部位2和引脚28连接,第一载体1通过第一载体连接部位2同时和第二载体5连接,第二载体5连接有第三载体6。第五载体9连接有第六载体10,第六载体10通过第六载体连接部位8和第四载体7连接,第六载体连接部位8和引脚28连接。沿基岛隔离单元32的长度方向,基岛隔离单元32的两侧分别设置有一排引脚28,第一载体1和第五载体9靠近基岛隔离单元32的上端,第一载体1和第五载体9之间有间隙,为载体间距11,第四载体7和第二载体5靠近基岛隔离单元32的下端,第四载体7和第二载体5之间有间距,第一载体1和第二载体5在基岛隔离单元32的右侧,第五载体9和第四载体7在基岛隔离单元32的左侧。

72.参见图7中(b)图,焊盘12共同设置在第一载体1和第五载体9上,焊盘12通过焊线18分别和引脚28连接。第四载体7上设置有第五芯片17,第二载体5上设置有的第四芯片16,第五芯片17通过焊线18分别和焊盘12、引脚28、第四载体7和第四芯片16连接。第四芯片16通过焊线18分别和焊盘12、引脚28、第五芯片17和第三载体6连接。

73.基岛隔离单元32、变压器11、第三芯片15、第五芯片17、第一芯片13、第二芯片14和第四芯片16表面外部包覆塑封体,形成合封的封装件。

74.优选的,上述实施例中所有的芯片和载体通过粘结的方式连接。

75.实施例7

76.参见图8,本发明的实施例之一为公开了一种基岛隔离框架与变压器芯片合封的sip塑料封装件的制备方法,包括以下步骤:

77.a.减薄,用减薄机减薄,将晶圆减薄到最终厚度100μm~280μm,粗磨速度控制在≤35μm/min;精度速度控制在≤10μm/min;

78.b.划片,利用划片机划片,采用双划片刀划片,避免芯片崩缺发生,且划片进刀速度控制在≤10mm/s,并及时清洗烘干;

79.c.上芯,采用本发明设计开发的多排矩阵式多载体双连筋的带椭圆形纵向锁胶孔的铜合金电镀引线框架30,采用多功能粘接头的上芯粘片一体机,使用上芯粘片喷胶技术,上芯多芯片一次粘接技术,上芯机将芯片粘在基岛隔离框架32的基岛隔离单元32上,粘接材料为环保型导电胶(绝缘胶)或daf膜(cdaf膜),采用防分层分段烘烤工艺,变压器11利用专用上芯及粘接在固定的基岛隔离单元32上,再次进行烘烤,形成芯片在基岛隔离单元32上的固化。

80.d.压焊,将金丝或钯铜线作为焊线18,压焊实施键合低弧度控制技术,采用平弧与正反打相结合,以及尖锐拐角的高级线弧形状和平拐角的高级线弧形状,控制弧高≤180μm;

81.e.塑封,选用具有高可靠性且耐高温高压的cel-1702hf9ts-g1系列环保型塑封料通过全自动塑封机将变压器、隔离芯片、焊线及基岛隔离结构框架,包覆在sop300mil 16l和20l形状,胶体尺寸长*宽*厚:10.30mmx7.50mmx2.30mm和12.80mmx7.50mmx2.30mm的塑封体封装件中,完成产品塑封包封;工艺采用薄型防翘曲和减小、消除离层的工艺,以降低冲丝率<8%,减少反包或回包,固化时间比正常减少10s~30s;后固化时ic封装件框架半成品料条在175℃烘箱老化7.5小时。

82.f.电镀,采用自动电镀线对封装件的多排矩阵式铜合金电镀sow16l或sop20l引线框架品进行镀锡的过程,使其外管脚表面镀上11.43

±

3.81μm焊锡,便于smt(surface mounting technology)焊接。

83.g.打印,采用夹具式固定、双激光头、连续送料定位打印方式,在塑封体表面进行商标打印。

84.h.切筋、成形分离,采用专用的切筋系统和模具,对框架上连接的中筋连杆进行切除,切筋刀具与塑封体之间的间隙大于0.075mm,以保证塑封体不被冲切到,同时清理模具表面塑封残渣,减少胶体被垫伤。

85.采用冲切式分离方法,将冲切刀片到塑封体25距离控制在0.075mm,塑封体上下固定压实,冲切分离,及时清理模具内的残胶碎片,形成一定形状的封装件。

86.i.测试、包装,采用专用的测试机和分选机,对电磁式封装件进行外观及功能参数的测试,保证提供客户的产品即可上机使用,满足封装件的使用要求。

87.接收产品

→

编带产品按包装数量编带

→

按规范要求加泡棉条及保护带

→

作业员核对入库单、标签

→

核对追溯小标签并贴卷盘标签

→

真空包装参数设定

→

装入包装盒

→

按规范要求贴标签、清单数量

→

检查相关附件是否齐全

→

包装入库。

88.实施例8

89.本发明所采用的另一个技术方案是:一种采用上述隔离引线框架生产sow、sop封装件的方法:

90.a.按现有sop封装生产工艺进行晶圆减薄和划片,形成各个芯片;

91.b.将切割好的芯片粘贴到基岛隔离框架的各个载体上;

92.c.烘烤,烘烤时采用七个不同含氧区快速固化防框架氧化烘烤工艺,该快速固化防防氧化烘烤工艺的详细流程是:该七个氧含量区域上下排布,框架经上芯后传递到第一氧化区,经过第一氧化区的初步固化,传递到第二氧化区依次类推,直至出箱产品粘接材料已得到充分的交联反应,各固化区域的氧含量采用渐变式量差,从第一氧含量区域到第七氧含量区域的氧含量分别为20000ppm、18000ppm、15000ppm、12000ppm、6000ppm、3000ppm、1500ppm;

93.d.烘烤后等离子清洗;

94.e.压焊,芯片间互连采用直角弧形多层焊线,其详细流程是:先在第二焊点植球,再从第一焊点焊丝,然后直角拉起线弧,接着沿第二焊点方向水平拉弧,最后垂直向下与第二焊点的焊球键合;其它连线按现有sop封装生产工艺进行压焊;压焊后进行塑封前等离子清洗,改善银面沾污;

95.f.采用高精度的自动包封系统和进行塑封,塑封时优先选用:注塑压力800~1200psi、注塑时间10~14s、模具温度170~180℃、合模压力125~135ton、固化时间120s;

96.g.塑封完成进行后固化,塑封后在175℃的温度下后固化8.5小时;

97.h.接着用热煮软化去溢料,再锡化;

98.i.采用整条框架测试、打印;

99.j.一次成型切筋,制得一种数字隔离芯塑料sow封装件。

100.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。