技术特征:

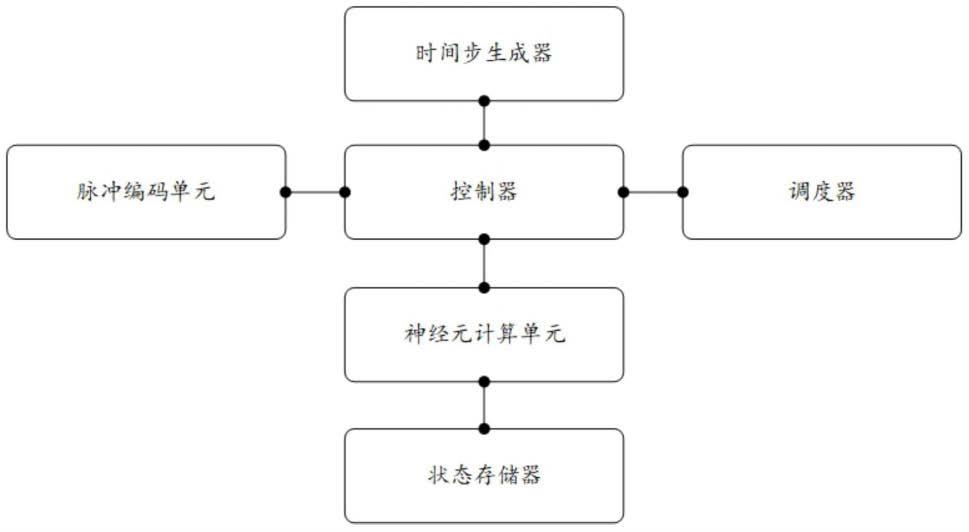

1.一种脉冲神经网络加速器,其特征在于,包括:脉冲编码单元、控制器、时间步生成器、调度器、状态存储器和神经元计算单元;所述控制器,用于在接收到输入数据后驱动所述时间步生成器生成时间步t,并将时间步t和输入数据发送给所述脉冲编码器单元;所述脉冲编码单元,用于基于时间步t将输入数据编码为下一个时间步t 1的脉冲数据,并将所述脉冲数据发送给所述控制器,由所述控制器将所述脉冲数据发送给所述调度器;所述调度器,用于对所述脉冲数据进行解码得到脉冲源地址和时间步t 1,并将脉冲源地址和时间步t 1存储到fifo阵列中;所述控制器还用于基于当前的时间步从所述fifo阵列中读取脉冲源地址,并将该脉冲源地址发送给所述神经元计算单元;所述神经元计算单元,用于根据脉冲源地址从所述状态存储器中读取对应的神经元状态数据,根据所述神经元状态数据对对应层的神经元进行状态更新,将更新后的状态数据写回所述状态存储器中,并将输出的脉冲数据发送给所述调度器进行存储,以便下一层神经元进行状态更新。2.根据权利要求1所述的脉冲神经网络加速器,其特征在于,所述脉冲编码单元包括:伪随机数生成器和泊松编码器;所述伪随机数生成器,用于在接收到时间步t后,随机生成0到1之间的随机数;所述泊松编码器,用于基于所述随机数对输入数据进行泊松编码,生成下一个时间步t 1的脉冲数据。3.根据权利要求1所述的脉冲神经网络加速器,其特征在于,所述脉冲编码单元,还用于在编码完下一个时间步t 1的输入数据后,触发所述时间步生成器生成下一个时间步t 1。4.根据权利要求1所述的脉冲神经网络加速器,其特征在于,还包括:延迟存储单元和突触延迟计算单元;所述延迟存储单元,用于存储目标神经元的突触延迟时间;所述突触延迟计算单元,用于根据所述目标神经元的突触延迟和当前时间步计算目标时间步,将所述目标神经元的目标时间步发送给所述调度器,由所述调度器根据所述目标神经元的脉冲源地址和所述目标时间步进行存储。5.根据权利要求1所述的脉冲神经网络加速器,其特征在于,所述神经元计算单元,具体用于:当神经元为if或lif神经元时,基于四级流水线根据脉冲源地址从所述状态存储器中读取对应的神经元状态数据,根据所述神经元状态数据计算脉冲神经网络参数,基于脉冲神经网络参数更新神经元状态,以及将更新后的神经元状态写回到所述状态存储器中;当神经元为izhikevich神经元时,基于六级流水线根据脉冲源地址从所述状态存储器中读取对应的神经元状态数据,根据所述神经元状态数据计算脉冲神经网络参数,基于脉冲神经网络参数更新神经元状态,以及将更新后的神经元状态写回到所述状态存储器中。6.根据权利要求5所述的脉冲神经网络加速器,其特征在于,当神经元为lif神经元时,所述脉冲神经网络参数包括基于一阶欧拉方法计算的lif神经元的膜电位电压,计算公式

为:为:为:β1=α

·

v[n],式中,v[n]为当前时刻的膜状态,v[n 1]为所求的膜电位大小,为采用一阶欧拉方法求得的膜电位电压,t

n

为计算时的第n个离散时间步,v

n

为输入膜电位大小,α为神经元膜电阻产生的电压受神经元此时膜电位的影响大小,f1(t,v)为第一目标方程,f2(t,v)为第二目标方程,β1、β2为不同阶段v的大小偏置,v

reset

为神经元静息电位,h为时间步,τ

m

为时间常数。7.根据权利要求5所述的脉冲神经网络加速器,其特征在于,当神经元为izhikevich神经元时,所述脉冲神经网络参数包括基于一阶欧拉方法计算的izhikevich神经元的膜电位电压,计算公式为:v[n 1]=(0.04v2 5v 140-u i)

·

h;u[n 1]=[a(bv-u)]

·

h;式中,v为所求的膜电位电压,u为膜电位恢复变量,i为神经元的输入电流,h为时间步,a、b、c、d为神经元的模型参数,v

threhold

为膜电压阈值。8.根据权利要求1或5所述的脉冲神经网络加速器,其特征在于,所述状态存储器包括用于存储神经元的权重的权重存储器和用于存储神经元参数的神经元参数存储单元。9.根据权利要求1所述的脉冲神经网络加速器,其特征在于,所述调度器中的fifo阵列为16个并行的fifo阵列。

技术总结

本申请公开了一种脉冲神经网络加速器,控制器在接收到输入数据后驱动时间步生成器生成时间步t;脉冲编码单元基于时间步t将输入数据编码为下一个时间步t 1的脉冲数据;调度器对脉冲数据进行解码后存储到FIFO阵列中;控制器基于当前时间步从FIFO阵列中读取脉冲源地址发送给神经元计算单元;神经元计算单元根据脉冲源地址从状态存储器中读取对应的神经元状态数据,以对对应层的神经元进行状态更新,将更新后的状态数据写回状态存储器中,并将输出的脉冲数据发送给调度器进行存储,以便下一层神经元进行状态更新,改善了现有的加速器在硬件实现上无法确定当前时间下是否剩余未处理的事件,导致加速器的性能较低的技术问题。导致加速器的性能较低的技术问题。导致加速器的性能较低的技术问题。

技术研发人员:刘怡俊 陈岳海 叶武剑

受保护的技术使用者:广东工业大学

技术研发日:2022.08.17

技术公布日:2022/11/11

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。