1.本发明属于新型纳米半导体信息器件技术领域,具体为实现一种利用栅极源重叠(即将栅极向源极延伸)、硅-锗异质结和负电容效应三者相结合来提高环栅隧穿场效应晶体管(gaa-tfet)的驱动电流的器件结构。

背景技术:

2.随着纳米尺度cmos芯片的集成度越来越高,芯片的功耗成为一个亟待解决的问题,降低功耗的主要方法是使cmos器件具有更好的开关特性,而开关特性主要取决于亚阈值摆幅(ss)的大小。由于cmos晶体管在室温下无法突破玻尔兹曼限制,即其ss不能降到60mv/decade以下,因此传统cmos器件功耗难以继续降低。

3.负电容晶体管(ncfet)通过铁电材料的负电容效应降低ss,可以作为其中一个方法来解决此问题。另一种很具有前途的器件是隧穿场效应晶体管(tfet),该器件使载流子通过带带隧穿从源极隧穿到沟道来产生电流。由于器件导电机理不同,tfet可以较容易地突破波尔茨曼限制使ss降到60mv/decade以下。但是,tfet的特点是其同时具有低的关态电流和开态电流,导致它的驱动能力很弱,限制了其未来应用。并且,在cmos技术进入5nm节点后,晶体管的尺寸也逐渐逼近其物理极限。

4.环栅场效应晶体管(gaa-fet)因其具有更强的栅极控制能力,将会代替鳍式场效应晶体管(finfet)而成为主流的cmos器件。因此,环栅隧穿场效应晶体管(gaa-tfet)是面向亚5nm节点的超低功耗cmos器件的有力竞争者。但是,目前已有的器件结构和机理仍不能有效地解决gaa-tfet驱动能力弱的问题。因此,通过结合负电容效应、硅-锗异质结、栅极源重叠和环栅结构,用以提高隧穿场效应晶体管的驱动电流。在保证隧穿场效应晶体管其他电学性能的前提下,通过器件结构部分改变提高gaa-tfet器件的驱动能力。

技术实现要素:

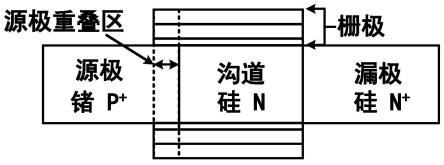

5.本发明针对gaa-tfet的驱动能力提出一种新型cmos器件结构,即:源极使用锗材料,沟道和漏极使用硅材料,在沟道和源极的接触面构成硅-锗异质结,在栅极氧化层介质和栅极金属层之间加入铁电介质层产生负电容效应提升器件沟道表面电势,并且将栅极向源极延伸形成源极重叠区(sol)结构的多重效应共同作用来提升器件的驱动能力。

6.本发明包括源极、沟道、漏极和栅极,其特征在于:源极使用锗材料,沟道和漏极使用硅材料;在所述沟道和源极的接触面构成硅-锗异质结,用于增加隧穿面积和隧穿几率;在栅极的氧化层介质和栅极的金属层之间加入铁电介质层,用于产生负电容效应提升沟道表面电势;所述栅极向源极延伸形成有源极重叠区;也用于增加隧穿面积和隧穿几率。

7.优先的,所述源极重叠区长度不超过栅极长度的33%;所述铁电介质层的厚度为源极重叠区长度的130%。

8.优先的,所述源极为在锗材料中进行p型重掺杂形成;所述沟道为在硅材料中进行n型轻掺杂形成;所述漏极为在硅材料中进行n型重掺杂形成。

9.优先的,所述栅极的氧化层介质为具有高介电常数的hfo2;其介电常数为20~24;所述栅极的金属层为tin;所述栅极的铁电介质层为基于hfo2基掺杂形成。

10.本发明的有益效果:本发明结合了负电容效应和硅-锗异质结的基础上,通过源极重叠继续提高器件的带带隧穿率和隧穿面积,进而提升器件的驱动能力。ncgaa-sol-tfet中源极重叠部分使得源极和沟道异质结宽度增加,异质结处能带弯曲更强,使得带带隧穿率和隧穿面积增加,进而提高器件的导通电流。

附图说明

11.图1为sige异质结ncgaa-tfet示意图;

12.图2为sige异质结ncgaa-sol-tfet示意图;

13.图3为sige异质结ncgaa-sol-tfet工艺流程图。

具体实施方式

14.下面将结合实施例对本发明的实施方案和工艺步骤进行详细的描述,本领域的技术人员将会理解,但是下面实施例仅用于说明本发明,而不应该视为对本发明的限制。

15.本发明主要是为了提高gaa-tfet器件的电流驱动能力,gaa-tfet作为未来很有前途的替代传统mosfet的器件,能够容易使亚阈值摆幅降到60mv/decade以下。但是它的缺点也很明显,就是导通电流很低,导致驱动能力不足。

16.本发明在gaa-tfet中,通过栅极和源极重叠区的铁电介质层产生负电容效应,使得沟道表面的电势放大,提高带带隧穿的几率。

17.再使用硅-锗异质结用以提升沟道导通电流,锗材料具有窄的禁带宽度和高的载流子迁移率,锗和硅形成的异质结能够使得带带隧穿率和隧穿面积大大增加。而且硅锗异质结相比于其他化合物异质结更加兼容目前的cmos工艺。

18.最后通过将栅极向源极延伸,使得异质结整体向源极移动,异质结耗尽区宽度增加,异质结处能带弯曲更强,在此处发生带带隧穿的概率和隧穿面积也大大增加,进而提高了导通电流。

19.对于图1所示的sige异质结ncgaa-tfet,为了提高隧穿电流,其主要的方法主要是提升隧穿结的面积和带-带间隧穿的几率,考虑通过在靠近沟道的源极也施加电压,即将栅极向源极延伸构成源极重叠区,这样可以调节源极重叠区对应器件中的电场,调控源极价带和沟道导带的位置。这使得不仅仅异质结处的能带更弯曲并发生带-带隧穿,同时也使得源极中靠近异质结处的能带也弯曲,即其等效于将异质结耗尽区变宽,其效果是能将带-带隧穿的面积和隧穿的几率同时增大,从而提升隧穿电流。

20.本实例的具体技术方案图可见图2,其结构包括:由氧化层、铁电介质层和金属电极构成的栅极,结构和材料均与栅极相同的源极重叠区,锗材料掺杂构成的源极,硅材料掺杂构成的沟道区和漏极。其中铁电介质层产生负电容效应、源区和沟道构成的硅-锗异质结增加隧穿面积和隧穿几率、栅极向源区延伸构成的源极重叠区的多重效应共同作用来提升器件的驱动电流。

21.本发明将此新结构的cmos器件命名为负电容环栅源极重叠隧穿场效应晶体管(ncgaa-sol-tfet),ncgaa-sol-tfet可以在保证其他电学性能稳定的情况下使其驱动能力

达到传统标准环栅cmos器件的水平。

22.本发明在较为先进的gaa-tfet工艺上,通过将栅极向源极延伸一定长度,即在靠近栅极的源极构成一个源极重叠区,给出了ncgaa-sol-tfet结构,具体包括:

23.源极为在锗材料中进行p型重掺杂形成;

24.沟道为在硅材料中进行n型轻掺杂形成;

25.漏极为在硅材料中进行n型重掺杂形成;

26.栅极氧化层介质为具有高介电常数(20~24)的hfo2;

27.栅极金属层为tin;

28.栅极铁电介质层为基于hfo2基掺杂形成;

29.源极重叠区即为将栅极向源极延伸的部分,结构和材料均与栅极相同。

30.本发明器件的制备工艺如图3所示:

31.(1)制备好硅衬底;

32.(2)在硅衬底上通过反应离子刻蚀出纳米线形状硅,作为漏极和沟道区;

33.(3)在沟道上通过外延生长出锗半导体作为源极;

34.(4)通过离子注入对由硅半导体构成的漏极、沟道区进行n型掺杂,掺杂浓度分别为2

×

10

19

/cm3、10

15

/cm3;

35.(5)通过离子注入对由锗半导体构成的源极进行p型掺杂,掺杂浓度为10

20

/cm3;

36.(6)在沟道上通过原子层沉积工艺,淀积一层hfo2薄膜,即为栅极氧化层介质;

37.(7)在栅极氧化层介质上,通过原子层沉积工艺,淀积一层基于hfo2基掺杂的铁电介质层,铁电介质层厚度为栅极重叠区长度的130%时,器件的综合性能最佳;

38.(8)在氮气环境中,700℃下进行5s的快速热退火,使铁电介质层表现出较好的铁电性;

39.(9)源极重叠区长度可调,但不超过栅极长度的33%,在源极重叠区重复栅极氧化层和栅极铁电介质层的工艺步骤;

40.(10)在栅极铁电介质层和源极重叠区铁电介质层,通过物理气相淀积工艺,淀积出金属栅极。在源极和漏极同样通过化学气相淀积,做出源电极和漏电极。

41.综上,本发明提供一种源极重叠区长度和铁电介质层厚度可调的硅基异质结负电容环栅源极重叠隧穿场效应晶体管的结构,通过调节不同的源极重叠区长度和铁电层厚度进行优化,最终可以得到具有优良性能的gaa-tfet器件。其在源极重叠长度不超过栅极的33%,铁电介质层厚度为源极重叠长度的130%时,器件的综合电学性能最佳。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。