1.本发明涉及半导体制造技术领域,尤其涉及一种半导体结构的形成方法。

背景技术:

2.随着半导体技术的不断发展,存储器呈现出高集成度、快速、低功耗的 发展趋势。

3.从功能上将存储器分为随机存储器(ram,random access memory)和只 读存储器(rom,read only memory)。随机存储器工作时,可以随时从任何 一个指定的地址读出数据,也可以随时将数据写入任何一个指定的存储单元。 随机存储器的读写操作方便,使用灵活。

4.随机存储器可以分为静态随机存储器(sram)和动态随机存储器 (dram)。其中,静态随机存储器利用带有正反馈的触发器来实现存储数据, 主要依靠持续的供电来保持数据的完整性。静态随机存储器在使用过程中不 需要刷新。静态随机存储器已被广泛应用在计算机的高速缓存和频繁的数据 处理中。

5.然而,现有技术中静态随机存储器的性能较差。

技术实现要素:

6.本发明解决的技术问题是提供一种半导体结构的形成方法,能够有效的 提升最终形成的半导体结构的性能。

7.为解决上述问题,本发明提供一种半导体结构的形成方法,包括:提供 衬底,所述衬底包括第一区和第二区;在所述第一区内形成第一隔离结构; 在所述第二区内形成第二隔离结构,所述第一隔离结构的顶部表面高于所述 第二隔离结构的顶部表面;在所述第二区上形成若干浮栅结构,所述第二隔 离结构位于相邻的所述浮栅结构之间;在形成所述浮栅结构之后,对所述第 一区的顶部表面、以及所述第一隔离结构的顶部表面进行清洗处理。

8.可选的,所述浮栅结构包括浮栅介质层以及位于所述浮栅介质层上的浮 栅层。

9.可选的,所述浮栅结构的形成方法包括:在所述衬底上形成浮栅介质膜, 所述浮栅介质膜分别覆盖所述第一区、第二区、第一隔离结构以及第二隔离 结构的顶部表面;在所述浮栅介质膜上形成浮栅膜;在所述浮栅膜上形成第 一图形化层,所述第一图形化层暴露出部分所述浮栅膜的顶部表面;以所述 第一图形化层为掩膜刻蚀所述浮栅膜和所述浮栅介质膜,在所述第一区和所 述第二区上分别形成初始浮栅结构;去除位于所述第一区上的初始浮栅结构, 在所述第二区上形成所述浮栅结构。

10.可选的,在形成所述浮栅结构之后,在高于所述第一区顶部表面的所述 第一隔离结构的侧壁上具有残留物,所述清洗处理去除所述残留物。

11.可选的,所述浮栅介质层的材料包括氧化硅。

12.可选的,所述浮栅层的材料包括多晶硅。

13.可选的,在形成所述浮栅结构之后,还包括:在所述第一区内形成相邻 的第一阱

区和第二阱区,所述第一隔离结构位于所述第一阱区和所述第二阱 区之间。

14.可选的,所述第一阱区在所述形成所述第二阱区之前形成。

15.可选的,所述清洗处理包括:在形成所述第一阱区之后进行第一清洗处 理;在形成所述第二阱区之后进行第二清洗处理。

16.可选的,形成所述第一阱区和进行所述第一清洗处理的方法包括:在所 述衬底上形成第二图形化层,所述第二图形化层暴露出部分所述第一区的顶 部表面、以及部分所述第一隔离结构的顶部表面;以所述第二图形化层为掩 膜对所述第一区进行第一离子的注入处理,形成所述第一阱区;在形成所述 第一阱区之后,以所述第二图形化层为掩膜对暴露出的所述第一区的顶部表 面、以及所述第一隔离结构的顶部表面进行所述第一清洗处理;在所述第一 清洗处理之后,去除所述第二图形化层。

17.可选的,形成所述第二阱区和进行所述第二清洗处理的方法包括:在所 述衬底上形成第三图形化层,所述第三图形化层暴露出部分所述第一区的顶 部表面、以及部分第一隔离结构的顶部表面;以所述第三图形化层为掩膜对 所述第一区进行第二离子的注入处理,形成所述第二阱区;在形成所述第二 阱区之后,以所述第三图形化层为掩膜对暴露出的所述第一区的顶部表面、 以及所述第一隔离结构的顶部表面进行所述第二清洗处理;在所述第二清洗 处理之后,去除所述第三图形化层。

18.可选的,所述第一离子与所述第二离子的电学类型不同。

19.可选的,所述第一离子包括n型离子或p型离子;所述第二离子包括n 型离子和p型离子。

20.可选的,所述第一清洗处理的工艺参数包括:清洗溶液包括氢氟酸,其 中氢氟酸的溶液体积比为1:50~1:100;清洗温度为24.5摄氏度~25.5摄氏度; 清洗时间为1分钟~2分钟。

21.可选的,所述第二清洗处理的工艺参数包括:清洗溶液包括氢氟酸,其 中氢氟酸的溶液体积比为1:50~1:100;清洗温度为24.5摄氏度~25.5摄氏度; 清洗时间为1分钟~2分钟。

22.可选的,在所述清洗处理之后,还包括:在所述浮栅结构上形成控制栅 结构。

23.可选的,所述控制栅结构包括:控制栅介质层以及位于所述控制栅介质 层上的控制栅层。

24.可选的,所述控制栅介质层为单层结构或多层结构。

25.可选的,当所述控制栅介质层为多层结构时,所述控制栅介质层包括: 第一氧化硅层、位于所述第一氧化硅层上的氮化硅层、以及位于所述氮化硅 层上的第二氧化硅层。

26.可选的,所述控制栅层的材料包括多晶硅。

27.与现有技术相比,本发明的技术方案具有以下优点:

28.本发明的技术方案的形成方法中,通过在形成所述浮栅结构之后,对所 述第一区的顶部表面、以及所述第一隔离结构的顶部表面进行清洗处理。利 用所述清洗处理去除在前序工艺过程中所形成的残留物,进而提升最终形成 的半导体结构的性能。

29.进一步,所述第一清洗处理在形成第一阱区之后进行。利用在形成第一 阱区时所形成的第二图形化层进行所述第一清洗处理,能够有效减少制程步 骤,同时节省了制作成本。

30.进一步,所述第二清洗处理在形成第二阱区之后进行。利用在形成第二 阱区时所形成的第三图形化层进行所述第二清洗处理,能够有效减少制程步 骤,同时节省了制作成本。

附图说明

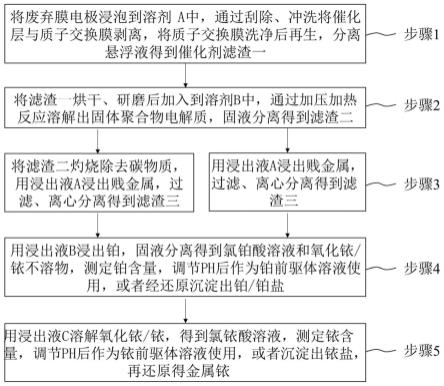

31.图1至图2是一种半导体结构的结构示意图;

32.图3至图12是本发明半导体结构形成方法实施例各步骤结构示意图。

具体实施方式

33.正如背景技术所述,现有技术中静态随机存储器的性能较差。以下将结 合附图进行具体说明。

34.请参考图1,提供衬底100,所述衬底100包括第一区i和第二区ii;在 所述第一区i内形成第一隔离结构101;在所述第二区ii内形成第二隔离结构 102,所述第一隔离结构101的顶部表面高于所述第二隔离结构102的顶部表 面。

35.请参考图2,在所述第二区ii上形成若干浮栅结构103,所述第二隔离结 构102位于相邻的所述浮栅结构103之间;在形成所述浮栅结构103之后, 在所述第一区i内形成相邻的第一阱区104和第二阱区105,所述第一隔离结 构101位于所述第一阱区101和所述第二阱区105之间。

36.在本实施例中,所述第一区i用于形成静态随机存取存储器(staticrandom-access memory,sram),所述第二区ii用于形成flash存储器,通 过将sram存储器和flash存储器进行集成,能够实现存储功能的特殊存储 器,因其具有低功耗,低成本,高密度,高可靠性等优点,而被广泛应用。

37.在本实施例中,由于在后续的制程中会有较多的刻蚀工艺,这些刻蚀工 艺会不断的损耗所述第一隔离结构101和所述第二隔离结构102,为了保证最 终所述第一隔离结构101和所述第二隔离结构102的隔离效果,因此,在最 初形成所述第一隔离结构101和所述第二隔离结构102时,所述第一隔离结 构101和所述第二隔离结构102的顶部表面是高于所述第一区i和第二区ii 的顶部表面的。

38.在本实施例中,在形成所述浮栅结构103的形成过程为:先在所述第一 区i和所述第二区ii上分别形成初始浮栅结构(未图示),然后再除去位于所 述第一区i上的初始伪栅结构,进而在所述第二区ii上形成所述浮栅结构103。 然而在去除所述第一区i上的初始伪栅结构的过程中,由于所述第一隔离结构 101的顶部表面高于所述第一区i的顶部表面,所述第一隔离结构101与所述 第一区i的界面处的所述初始浮栅结构会去除不完全,进而形成所述浮栅结构 的残留物(如图2中a部分所示),所述残留物会影响后续形成的半导体结构 的性能。

39.在此基础上,本发明提供一种半导体结构的形成方法,通过在形成所述 浮栅结构之后,对所述第一区的顶部表面、以及所述第一隔离结构的顶部表 面进行清洗处理。利用所述清洗处理去除在前序工艺过程中所形成的残留物, 进而提升最终形成的半导体结构的性能。

40.为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图 对本发明

的具体实施例做详细地说明。

41.图3至图12是本发明实施例的一种半导体结构的形成过程的结构示意 图。

42.请参考图3,提供衬底200,所述衬底200包括第一区i和第二区ii。

43.在本实施例中,所述衬底200的材料为硅;在其他实施例中,所述衬底 的材料还可以为锗、锗化硅、碳化硅、砷化镓或镓化铟。

44.在本实施例中,所述第一区i用于形成静态随机存取存储器(static random-access memory,sram),所述第二区ii用于形成闪存存储器(flash), 通过将sram存储器和flash存储器进行集成,能够实现存储功能的特殊存 储器,因其具有低功耗,低成本,高密度,高可靠性等优点,而被广泛应用。

45.请参考图4,在所述第一区i内形成第一隔离结构201。

46.在本实施例中,所述第一隔离结构201的形成方法包括:在所述第一区i 内形成第一隔离沟槽(未标示);在所述第一隔离沟槽内形成所述第一隔离结 构201。

47.由于在后续的制程工艺中会在所述第一区i上使用到较多次数的刻蚀工 艺,在进行刻蚀工艺的过程中会不断的损伤消耗所述第一隔离结构201,因此 为了保证最终的所述第一隔离结构201具有较好的隔离效果,所述第一隔离 结构201的顶部表面高于所述第一区i的顶部表面。

48.在本实施例中,所述第一隔离结构201的材料采用氧化硅。

49.请继续参考图4,在形成所述第一隔离结构201的过程中,在所述第二区 ii内形成第二隔离结构202,所述第一隔离结构201的顶部表面高于所述第二 隔离结构202的顶部表面。

50.在本实施例中,所述第二隔离结构202的形成方法包括:在所述第二区 ii内形成第二隔离沟槽(未标示);在所述第二隔离沟槽内形成所述第二隔离 结构202。

51.由于在后续的制程工艺中会在所述第二区ii上使用到较多次数的刻蚀工 艺,在进行刻蚀工艺的过程中会不断的损伤消耗所述第二隔离结构202,因此 为了保证最终的所述第二隔离结构202具有较好的隔离效果,所述第二隔离 结构202的顶部表面高于所述第二区ii的顶部表面。

52.在本实施例中,所述第二隔离结构202的材料采用氧化硅。

53.由于所述第二区ii用于形成所述闪存存储器(flash),为了更好的区分高 电平1和低电平0,需要在所述第二区ii上清洗出浮栅结构尖角(floating gatetip)。此时需要通过掩膜将所述第一区i进行覆盖,进而对所述第二区ii进行 一次清洗处理,在这个过程中,会损耗一定高度的所述第二隔离结构202,进 而使得所述第一隔离结构201的顶部表面高于所述第二隔离结构202的顶部 表面。

54.由于所述第一隔离结构201的顶部表面高于所述第二隔离结构202的顶 部表面,因此在后续的制程中,容易在高于所述第一区i顶部表面的所述第一 隔离结构201的侧壁形成残留物。

55.请参考图5,在所述第二区ii上形成若干浮栅结构203,所述第二隔离结 构202位于相邻的所述浮栅结构203之间。

56.在本实施例中,所述浮栅结构203包括浮栅介质层以及位于所述浮栅介 质层上的浮栅层(未标示)。

57.在本实施例中,所述浮栅介质层的材料包括氧化硅。

58.在本实施例中,所述浮栅层的材料包括多晶硅。

59.在本实施例中,所述浮栅结构203的形成方法包括:在所述衬底200上 形成浮栅介质膜(未图示),所述浮栅介质膜分别覆盖所述第一区i、第二区 ii、第一隔离结构201以及第二隔离结构202的顶部表面;在所述浮栅介质膜 上形成浮栅膜(未图示);在所述浮栅膜上形成第一图形化层(未图示),所 述第一图形化层暴露出部分所述浮栅膜的顶部表面;以所述第一图形化层为 掩膜刻蚀所述浮栅膜和所述浮栅介质膜,在所述第一区i和所述第二区ii上 分别形成初始浮栅结构(未图示);去除位于所述第一区i上的初始浮栅结构, 在所述第二区ii上形成所述浮栅结构203。

60.在本实施例中,在形成所述浮栅结构203之后,在高于所述第一区i顶部 表面的所述第一隔离结构201的侧壁上具有残留物,所述清洗处理去除所述 残留物。

61.在本实施例中,所述残留物为在去除位于所述第一区i上的所述初始浮栅 结构时,附着在所述第一隔离结构201侧壁的所述浮栅介质层的材料,因此, 所述残留物的材料包括氧化硅。

62.在形成所述浮栅结构203之后,还包括:在所述第一区i内形成相邻的第 一阱区和第二阱区,所述第一隔离结构201位于所述第一阱区和所述第二阱 区之间;对所述第一区i的顶部表面、以及所述第一隔离结构201的顶部表面 进行清洗处理,所述清洗处理包括:在形成所述第一阱区之后进行第一清洗 处理;在形成所述第二阱区之后进行第二清洗处理。具体过程请参考图6至 图10。

63.请参考图6,在所述衬底200上形成第二图形化层204,所述第二图形化 层204暴露出部分所述第一区i的顶部表面、以及部分所述第一隔离结构201 的顶部表面;以所述第二图形化层204为掩膜对所述第一区i进行第一离子的 注入处理,形成所述第一阱区205。

64.在本实施例中,所述第二图形化层的材料包括光刻胶,所述第二图形化 层的形成工艺包括光刻图形化工艺。

65.在本实施例中,所述第一阱区205在所述形成所述第二阱区之前形成。

66.在本实施例中,所述第一离子采用p型离子;在其他实施例中,所述第 一离子还可以采用n型离子。

67.请参考图7,在形成所述第一阱区205之后,以所述第二图形化层204为 掩膜对暴露出的所述第一区i的顶部表面、以及所述第一隔离结构201的顶部 表面进行所述第一清洗处理。

68.在本实施例中,在所述第一清洗处理的过程中,由于所述第一隔离结构 的材料与所述残留物的材料相同,虽然所述第一清洗处理能够去除所述残留 物,但是对所述第一隔离结构也会造成一定的损失,因此在所述第一清洗处 理之后,暴露出的所述第一隔离结构的顶部表面高度会降低。

69.由于所述第一清洗处理在形成第一阱区205之后进行。利用在形成第一 阱区205时所形成的第二图形化层204进行所述第一清洗处理,能够有效减 少制程步骤,同时节省了制作成本。

70.在本实施例中,所述第一清洗处理的工艺参数包括:清洗溶液包括氢氟 酸,其中氢氟酸的溶液体积比为1:50~1:100;清洗温度为24.5摄氏度~25.5 摄氏度;清洗时间为1

分钟~2分钟。

71.请参考图8,在进行所述第一清洗处理之后,去除所述第二图形化层。

72.在本实施例中,由于所述第二图形化层的材料采用光刻胶,光刻胶材料 与所述第一隔离结构采用的氧化硅材料具有较大的刻蚀选择比,因此在去除 所述第二图形化的过程中对所述第一隔离结构的损伤较小,所述第一隔离结 构的顶部表面高度不会有明显的降低。

73.去除所述第二图形化层的工艺包括湿法去胶工艺或灰化工艺。在本实施 例中,去除所述第二图形化层的工艺采用灰化工艺,所述灰化工艺的气体为 含氧气体,例如氧气或臭氧。

74.请参考图9,在所述衬底200上形成第三图形化层206,所述第三图形化 层206暴露出部分所述第一区i的顶部表面、以及部分第一隔离结构201的顶 部表面;以所述第三图形化层206为掩膜对所述第一区i进行第二离子的注入 处理,形成所述第二阱区207。

75.在本实施例中,所述第三图形化层的材料包括光刻胶,所述第三图形化 层的形成工艺包括光刻图形化工艺。

76.在本实施例中,所述第一离子与所述第二离子的电学类型不同。

77.在本实施例中,所述第二离子采用n型离子;在其他实施例中,所述第 二离子还可以采用p型离子。

78.请参考图10,在形成所述第二阱区207之后,以所述第三图形化层206 为掩膜对暴露出的所述第一区i的顶部表面、以及所述第一隔离结构201的顶 部表面进行所述第二清洗处理。

79.在本实施例中,在所述第二清洗处理也会对所述第一隔离结构也造成一 定的损失,因此在所述第二清洗处理之后,暴露出的所述第一隔离结构的顶 部表面高度会降低。

80.通过在形成所述浮栅结构203之后,对所述第一区i的顶部表面、以及所 述第一隔离结构201的顶部表面进行清洗处理。利用所述清洗处理去除在前 序工艺过程中所形成的残留物,进而提升最终形成的半导体结构的性能。

81.由于所述第二清洗处理在形成第二阱区207之后进行。利用在形成第二 阱区207时所形成的第三图形化层206进行所述第二清洗处理,能够有效减 少制程步骤,同时节省了制作成本。

82.在本实施例中,所述第二清洗处理的工艺参数包括:清洗溶液包括氢氟 酸,其中氢氟酸的溶液体积比为1:50~1:100;清洗温度为24.5摄氏度~25.5 摄氏度;清洗时间为1分钟~2分钟。

83.请参考图11,在所述第二清洗处理之后,去除所述第三图形化层。

84.在本实施例中,由于所述第三图形化层的材料采用光刻胶,光刻胶材料 与所述第一隔离结构采用的氧化硅材料具有较大的刻蚀选择比,因此在去除 所述第三图形化的过程中对所述第一隔离结构的损伤较小,所述第一隔离结 构的顶部表面高度不会有明显的降低。

85.去除所述第三图形化层的工艺包括湿法去胶工艺或灰化工艺。在本实施 例中,去除所述第三图形化层的工艺采用灰化工艺,所述灰化工艺的气体为 含氧气体,例如氧气或臭氧。

86.请参考图12,在所述清洗处理之后,在所述浮栅结构203上形成控制栅 结构208。

87.在本实施例中,所述控制栅结构208包括:控制栅介质层以及位于所述 控制栅介质层上的控制栅层(未标示)。

88.在本实施例中,所述控制栅介质层采用多层结构,所述控制栅介质层包 括:位于所述浮栅层上的第一氧化硅层、位于所述第一氧化硅层上的氮化硅 层、以及位于所述氮化硅层上的第二氧化硅层(未标示)。

89.其中所述控制栅介质层的所述第一氧化硅层与所述第二氧化硅层能够较 好与所述基晶进行结合,而所述氮化硅层居中,则可以阻挡缺陷(如pinhole) 的延展,因此通过三层结构的设计能够互补所缺。

90.在其他实施例中,所述控制栅介质层还可以采用单层结构。

91.在本实施例中,所述控制栅层的材料包括多晶硅。

92.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员, 在不脱离本发明的精神和范围内,均可作各种更动与修改,因此本发明的保 护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。