1.本发明涉及芯片零件、连接器等电子零件,尤其涉及一种在电子零件的零件主体上形成的焊接用电极端子结构。

背景技术:

2.将芯片零件、连接器等电子零件安装于电路板时,在电子零件的零件主体具有的连接端子的表面上形成包含sn(锡)或sn-pb(铅)的镀层作为外部连接层,此外部连接层使用焊料材料与设置在电路板的布线图案的焊盘接合。例如,如芯片电阻器等在零件主体的两端部形成被焊接外部连接层的表面安装零件的情况,将焊膏(焊料材料)涂布于布线图案的焊盘后,将电子零件放置在电路板上,使外部连接层与焊膏重叠,在此状态下,通过回流炉的热使外部连接层的镀层与焊膏熔融,之后,使焊膏冷却

·

固化而使连接端子与焊盘连接。另外,如连接器等从零件主体突出的针状的连接端子焊接的导线零件的情况,将连接端子插入电路板的穿通孔后,连接端子的外部连接层(镀层)与焊料材料通过烙铁等的热而熔融,之后,将焊料材料冷却

·

固化而将连接端子与焊盘连接。

3.作为将电子零件安装于电路板时使用的焊料材料,已知例如,锡(sn)和铅(pb)以约6:4(sn63%-pb37%)的比例混合的所谓的共晶焊料。这种组成的共晶焊料的熔点为183℃,但为了使焊料熔融,需要施加熔点以上的热,因此通过焊接时的热而构成连接端子的ag或cu在焊料材料侧渗出现象,即有发生所谓的「焊料腐蚀」的现象之虞。为了防止这种焊料腐蚀而设置障壁层,以往已提出通过在电子零件的连接端子与外部连接层之间设置由镍、铅构成的障壁层而防止焊料腐蚀的电极端子结构(例如,参见专利文献1)。

4.[专利文献1]日本特开2001-210545号公报

技术实现要素:

[0005]

[发明所欲解决问题]

[0006]

近年来,从世界的环境保护的观点,推荐无铅化,使用几乎不含铅的所谓的无铅焊料。此处,例如使用组成为sn 96.5%-ag 3%-cu 0.5%的无铅焊料的情况,该无铅焊料的熔点为220℃,与使用共晶焊料的情况相比,焊料安装时的加热温度变高温,因而即使障壁层由镍构成,镍也容易向焊料材料侧扩散,变成无法充分发挥作为障壁层的功能。因此需要加厚镀镍层以使焊料腐蚀延迟,但加厚镀层而形成的情况,不仅容易通过外部应力、内部应力而产生裂纹,而且电镀时间和材料成本也会增加。

[0007]

另外,在汽车业界中,自动驾驶装置、安全装置等技术近年来得到了飞速发展,随之而来电子零件的搭载数量急剧增加。此外,搭载于汽车的电子零件要求比消费类零件更高的可靠性,由于使用环境也很苛刻,因此对高耐热性的要求特别高,要求即使在200℃左右的环境下也能毫无问题地使用的高耐热性。然而,当电子零件在200℃左右的高温环境下使用时,构成障壁层的镀镍层扩散到表面,不能起到作为障壁层的功能。即,现有的电极端子结构有不仅在焊料安装时而且在使用环境下确保耐热性为困难的问题。

[0008]

本发明是鉴于这样的现有技术的实际情况而完成,其目的在于提供一种电子零件,其具备能够确保焊料安装时或使用环境下的耐热性的端子电极构造。

[0009]

[解决问题的手段]

[0010]

为了达成上述目的,本发明的电子零件的特征在于,包括:零件主体、形成在前述零件主体上的连接端子、通过电解电镀形成以覆盖前述连接端子的基底层、通过电解电镀形成以覆盖前述基底层的障壁层、以及在前述障壁层的表面形成的以锡为主成分的外部连接层,前述障壁层是由在镍中添加3%~15%的磷的合金镀层制成,同时前述基底层是比前述障壁层更富有展性和延性的至少一种的金属层。

[0011]

这样制成的电子零件是被外部连接层覆盖的障壁层由以镍(ni)作为主成分而含有3%~15%磷(p)的合金(ni-p)镀层制成,由于该合金镀层比镍更慢地扩散到锡中,因此即使没有无益地加厚形成障壁层,也可确保焊料安装时和使用环境下的耐热性。而且,作为障壁层的基底层形成比障壁层更富有展性或延性的金属层,即使内部应力随着向镍中添加磷而增加,其应力也被基底层缓和,从而可以抑制裂纹的发生。

[0012]

在上述构成的电子零件中,基底层只要是比障壁层更富有展性和延性的至少一种的金属层即可,可为金、银、铂、或以它们为主成分的合金,但优选为成本上有利的铜或以铜为主成分的合金。

[0013]

另外,在上述构成的电子零件中,基底层的膜厚过薄时,不能充分发挥缓和应力的效果,与其相反,基底层的膜厚过厚时,则成本生产性下降,因而基底层的膜厚优选为3μm~25μm。

[0014]

另外,在上述构成的电子零件中,在连接端子和障壁层之间形成磁性体层时,利用磁性体层的磁特性,例如,在将制品收纳于带状包装体中的缠带工序、从包装体取出制品而安装于电路板上时,通过磁性使制品的态势稳定成为可能。

[0015]

[发明功效]

[0016]

根据本发明的电子零件,可实现在焊料安装时或使用环境下能够确保耐热性的端子电极结构的同时,可抑制裂纹的发生。

附图说明

[0017]

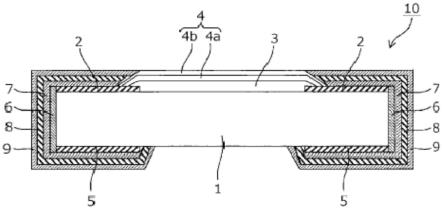

图1为本发明的第一实施方式所涉及的芯片电阻器的剖面图;

[0018]

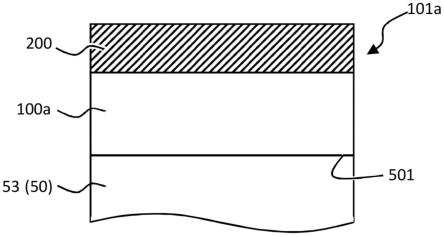

图2为表示该芯片电阻器的制造工序的剖面图;

[0019]

图3为本发明的第二实施方式所涉及的芯片电阻器的剖面图;

[0020]

图4为表示该芯片电阻器的制造工序的剖面图。

[0021]

附图标记说明:

[0022]

1 绝缘基板(零件主体)

[0023]

2 表电极(连接端子)

[0024]

3 电阻元件

[0025]

4 保护层

[0026]

4a 底涂层

[0027]

4b 外涂层

[0028]

5 背电极(连接端子)

[0029]

6 端面电极(连接端子)

[0030]

7 基底层

[0031]

8 障壁层

[0032]

9 外部连接层

[0033]

10 芯片电阻器(电子零件)

[0034]

11 磁性体层

具体实施方式

[0035]

以下,参见附图对发明的实施形态进行说明时,图1为本发明的第一实施方式所涉及的芯片电阻器的剖面图。

[0036]

如图1所示,为电子零件的一例的芯片电阻器10主要由下列构成﹕长方体形状的绝缘基板1、形成于绝缘基板1的表面的长边方向两端部上的一对表电极2、以在一对表电极2间进行桥接的方式形成的电阻元件3、被覆电阻元件3的全部和表电极2的一部分的保护层4、形成于绝缘基板1的背面的长边方向两端部上的一对背电极5、形成于绝缘基板1的长边方向两端面上的导通对应的表电极2和背电极5间的一对端面电极6、被覆这些表电极2与背电极5和端面电极6的一对基底层7、被覆各基底层7的一对障壁层8、被覆各障壁层8的一对外部连接层9。

[0037]

绝缘基板1是由陶瓷等制成的零件主体,该绝缘基板1是通过沿纵横分割槽将后述的大幅面基板分割而得到多个的绝缘基板。

[0038]

一对表电极2以规定间隔存在而形成于绝缘基板1的相对的短边侧上,这些表电极2是将ag系浆料进行丝网印刷,干燥

·

烧成而得。

[0039]

电阻元件3是将氧化钌等电阻膏进行丝网印刷,干燥

·

烧成而得,电阻元件3的两端部各自与表电极2重叠。另外,在电阻元件3形成图未示出的修边槽,通过该修边槽而调整电阻元件3的电阻值。

[0040]

保护层4是包含底涂层4a和外涂层4b的2层结构。底涂层4a是将玻璃浆料进行丝网印刷而烧成获得,该底涂层4a是在形成修边槽之前以覆盖电阻元件3的方式形成。外涂层4b是将环氧系树脂浆料进行丝网印刷而加热硬化获得,该外涂层4b是从底涂层4a的上方在电阻元件3上形成修边槽后,以包含修边槽而整体覆盖电阻元件3和底涂层4a的方式形成。

[0041]

一对背电极5有以规定的间隔形成在绝缘基板1的背面的与表电极2对应的位置,这些背电极5是将ag浆料进行丝网印刷而干燥

·

烧成而得。

[0042]

一对端面电极6是在绝缘基板1的端面上溅射ni-cr或在绝缘基板1的端面上涂布ag系浆料并加热硬化而得。端面电极6以将对应的表电极2和背电极5间进行导通的方式形成,通过这些表电极2和端面电极6和背电极5而构成截面

コ

字状的连接端子。

[0043]

一对基底层7是通过电解电镀形成覆盖连接端子的铜镀层,通过该基底层7而减轻了在后续工序中伴随进行的障壁层8的电镀形成所产生的内部应力。此处,如果基底层7的膜厚的膜厚不足,不能充分发挥应力缓和效果,与其相反,如果基材层7的膜厚过厚,则成本和生产性降低。基底层7设定在3μm~25μm的范围内。这些基底层7只要是富含比障壁层8更具展性和延性的至少一种的金属层即可,可为以金、银、铂、或它们为主成分的合金,在本实施方式中使用铜或以铜为主成分的合金,因为在成本上更比这些金属有利。

[0044]

一对障壁层8是以覆盖基底层7的方式通过电解电镀形成的以镍(ni)作为主成分而含有磷(p)的合金镀层(ni-p镀层),其厚度设定为2μm~15μm的范围。此处,构成障壁层8的合金镀层,镍中所含的磷的含量越多,越能抑制向构成外部连接层9的锡镀层的扩散,如果镍中所含的磷的含量不足,越无法充分发挥扩散防止效果。但是,如果磷的含量过高,则即使在基底层7中,内部应力也会变得过高而不能缓和,因此将障壁层8中的磷含有率相对于镍设定在3%~15%的范围内。

[0045]

一对外部连接层9以覆盖障壁层8的方式通过电解电镀形成的锡(sn)镀层,其厚度设定为2μm~15μm的范围。

[0046]

接着,对于如上述构成的芯片电阻器10的制造方法,参见图2所示的剖面图进行说明。

[0047]

首先,准备可获得多个绝缘基板1的大幅面基板。在该大幅面基板上预先设置有网格状的主分割槽和次分割槽,由两分割槽隔开的方格每一个成为1个芯片区域。虽然图2示出相当于1个的大幅面基板10a为代表,但实际上对相当于多个芯片区域的大幅面基板共同执行以下说明的各工序。

[0048]

即,如图2(a)所示,在大幅面基板10a的表面上将ag-pd浆料进行丝网印刷而干燥,在各芯片形成区域的长边方向两端部存有规定间隔而形成对向的一对表电极2。另外,与此同时或前后,在大幅面基板10a的背面将ag浆料进行丝网印刷而干燥,在各芯片形成区域的长边方向两端部存有规定间隔而形成对向的一对背电极5。

[0049]

接着,如图2(b)所示,在大幅面基板10a的表面上将含有氧化钌等的电阻膏进行丝网印刷而干燥,形成两端部重叠在表电极2的电阻元件3后,将其在约850℃的高温进行烧成。接着,覆盖电阻元件3的区域上将玻璃浆料进行丝网印刷而干燥,形成被覆电阻元件3的底涂层4a后,将其在约600℃的温度进行烧成。接着,通过从底涂层4a的上方照射激光束,在电阻元件3上形成图未示出的修边槽而调整电阻值。然后,从底涂层4a的上方将环氧系树脂浆料进行丝网印刷,将其在约200℃的温度下进行加热硬化而形成外涂层4b,形成包含底涂层4a和外涂层4b的2层结构的保护层4。

[0050]

接着,将大幅面基板10a沿着主分割槽主分割成长条状基板10b后,通过在该长条状基板10b的分割面上将ni/cr进行溅射,如图2(c)所示,形成将设置于长条状基板10b的表背两面的表电极2和背电极5间进行连接的端面电极6。另外,代替在长条状基板10b的分割面上将ni/cr进行溅射,也可通过涂布ag系浆料并使加热硬化,而形成端面电极6的方式。

[0051]

接着,将长条状基板10b沿着次分割槽次分割成多个芯片状基板10c后,通过对这些芯片状基板10c施加电解电镀,如图2(d)所示,在芯片状基板10c的两端部形成覆盖连接端子(表电极2、端面电极6和背电极5)的基底层7。该基底层7由铜镀层制成,其膜厚被设定成3μm~25μm的范围(在本实施方式中为10μm)。

[0052]

接着,通过对芯片状基板10c施加电解电镀,如图2(e)所示,形成覆盖基底层7的障壁层8。该障壁层8由以镍(ni)作为主成分而含有磷(p)的合金镀层(ni-p镀层)制成,其厚度被设定成2μm~15μm的范围(在本实施方式中为5μm)。障壁层8中磷相对于镍的含有率被设定成3%~15%(在本实施方式中为5%)的范围,即使通过向镍中添加磷而有内部应力产生,其应力也被基底层7缓和。

[0053]

接着,通过对芯片状基板10c施加电解电镀,如图2(f)所示,形成覆盖障壁层8的表

面的外部连接层9。外部连接层9为以锡(sn)作为主成分的sn镀层,其厚度被设定成2μm~15μm的范围。据此,形成包含障壁层8、外部连接层9等的耐热特性优秀的端子电极结构,并完成了图1所示的芯片电阻器10。

[0054]

如以上说明,在第一实施方式所涉及的芯片电阻器10中,以由锡镀层制成的外部连接层9覆盖的障壁层8是以镍(ni)作为主成分而含有磷(p)3%~15%的合金(ni-p)镀层制成,由于该合金镀层比镍更慢地扩散到锡中,因此即使徒劳地形成厚的障壁层8,也可确保在焊料安装时或使用环境下的耐热性。而且,由于作为障壁层8的基底层7而通过电解电镀形成铜镀层,因此即使伴随向镍中添加磷而使内部应力增大,其应力也被基底层7缓和,可抑制由于内部应力而产生的裂纹。

[0055]

另外,由于这些基底层7、障壁层8、外部连接层9通过电解电镀而形成,因此每个都由致密的膜形成,并且可以最大限度地引出各自具有的特性(应力缓和、障壁机能、焊接性),因可以进行一系列电镀,可尽可能地防止形成各层的电镀工序间的由于环境的腐蚀的同时,确保在各层的边界处的密着性和生产性。

[0056]

图3是本发明的第二实施方式所涉及的芯片电阻器20的剖面图。第二实施方式所涉及的芯片电阻器20与第一实施方式所涉及的芯片电阻器10不同的点在于连接端子(表电极2、端面电极6和背电极5)和障壁层8之间有形成磁性体层11,除此之外的构成基本上相同。

[0057]

即,如图3所示,该芯片电阻器20主要由以下构成:长方体形状的绝缘基板1、形成于绝缘基板1的表面的长边方向两端部上的一对表电极2、以在一对表电极2间进行桥接的方式形成的电阻元件3、被覆电阻元件3的全部和表电极2的一部分的保护层4、形成于绝缘基板1的背面的长边方向两端部的一对背电极5、形成于绝缘基板1的长边方向两端面而导通对应的表电极2和背电极5间的一对端面电极6、被覆这些表电极2和背电极5和端面电极6的一对磁性体层11、被覆各磁性体层11的一对基底层7、被覆各基底层7的一对障壁层8、以及被覆各障壁层8的一对外部连接层9。

[0058]

一对磁性体层11是以覆盖连接端子的方式通过电解电镀形成的镍(ni)镀层,其厚度被设定为2μm~15μm的范围。磁性体层11可通过提高在镍中添加磷而降低的障壁层8的磁性,可在基底层7和障壁层8之间形成。另外,因磁性体层11以外的构成与第一实施方式相同,所以通过附上与图1相同的符号,这里将省略重复的说明。

[0059]

接着,对于如上述构成的芯片电阻器20的制造方法,参见图4所示的剖面图进行说明。另外,在图4所示的制造工序,图4(a)对应第一实施方式中的图2(c),在此之前的工序与第一实施方式相同。

[0060]

即,在图未示出的大幅面基板上形成表电极2、电阻元件3、保护层4(底涂层4a和外涂层4b)、背电极5后,将此大幅面基板进行主分割而得到的长条状基板10b的分割面上通过将ni/cr溅射,如图4(a)所示,形成连接设置在长条状基板10b的表里两面的表电极2和背电极5间的端面电极6。

[0061]

接着,将长条状基板10b沿着次分割槽次分割成多个芯片状基板10c后,通过对这些芯片状基板10c施加电解电镀,如图4(b)所示,在芯片状基板10c的两端部形成覆盖连接端子(表电极2、端面电极6和背电极5)的磁性体层11。该磁性体层11由镍(ni)镀层制成,其厚度设定为2μm~15μm的范围(在本实施方式中为5μm)。

[0062]

接着,通过对芯片状基板10c施加电解电镀,如图4(c)所示,在芯片状基板10c的两端部形成覆盖磁性体层11的基底层7。该基底层7是由铜镀层制成,其膜厚设定为3μm~25μm的范围(在本实施方式中为10μm)。

[0063]

接着,通过对芯片状基板10c施加电解电镀,如图4(d)所示,形成覆盖基底层7的障壁层8。该障壁层8是由以镍(ni)作为主成分而含有磷(p)的合金镀层(ni-p镀层)制成,其厚度设定为2μm~15μm的范围(在本实施方式中为5μm)。另外,障壁层8中的磷对镍的含有率设定为3%~15%(在本实施方式中为5%)的范围。

[0064]

接着,通过对芯片状基板10c施加电解电镀,如图4(e)所示,形成覆盖障壁层8的表面的外部连接层9。外部连接层9是以锡(sn)作为主成分的sn镀层,其厚度设定为2μm~15μm的范围。据此,形成包含障壁层8、外部连接层9等的耐热特性优异的端子电极结构,完成了图3所示的芯片电阻器20。

[0065]

如以上说明,在第二实施方式所涉及的芯片电阻器20中,由于连接端子(表电极2、端面电极6和背电极5)与障壁层8之间形成了由镀镍层制成的磁性体层11,因而利用磁性体层11的磁特性,在例如将制品收纳于带状的包装体中的缠带工序、将制品从包装体取出而安装于电路板上时,可通过磁性而稳定制品的态势。

[0066]

另外,在第二实施方式所涉及的芯片电阻器20中,在连接端子(表电极2、端面电极6和背电极5)与基底层7之间形成磁性体层11,但磁性体层11若形成于连接端子与障壁层8之间并没有问题。即,磁性体层11可形成于基底层7和障壁层8之间,磁性体层11也可形成于连接端子与基底层7之间和基底层7与障壁层8之间的两者。

[0067]

另外,在上述各实施方式中,对于将本发明适用于表面安装零件的一例的芯片电阻器的情况进行说明,但芯片电阻器以外的电子零件,例如,对于如连接器的具有针状的连接端子的导线零件本发明亦可能适用。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。