1.本技术涉及电路技术领域,尤其涉及一种阻变存储器的数据读出电路和阻变存储电路。

背景技术:

2.近年来,阻变存储器(rram,resistive random access memory)以良好的可微缩性、低功耗和与逻辑工艺良好的兼容性成为一种较有前途的先进工艺节点下的嵌入式非易失存储器,被广泛的应用于消费电子、自动驾驶汽车、工业控制和物联网边缘设备等领域。

3.然而,伴随着阻变存储器的使用,阻变存储器的阻态逐渐退化,即高阻态的阻值大幅度减小或者低阻态幅度增大,容易导致数据读出电路难以正常区分高阻态和低阻态,导致数据读出错误。

技术实现要素:

4.本技术实施例提供了一种阻变存储器的数据读出电路和阻变存储电路,能够改善阻变存储器的高阻态退化带来数据读出错误的问题。

5.第一方面,一种阻变存储器的数据读出电路,包括:自适应灵敏电流放大器和参考电流生成器,所述自适应灵敏电流放大器用于电连接阻变存储器,所述自适应灵敏电流放大器与所述参考电流生成器电连接;

6.所述参考电流生成器用于生成基础参考电流;

7.所述自适应灵敏电流放大器用于根据所述基础参考电流和阻变存储器的位线电流得到参考电流;

8.所述自适应灵敏电流放大器用于比对所述参考电流与所述位线电流的大小,以读出存储数据。

9.在一种可行的实施方式中,所述自适应灵敏电流放大器包括:数据读出模块和参考电流模块;

10.所述数据读出模块与所述参考电流模块电连接,所述数据读出模块用于与所述阻变存储器电连接,所述参考电流模块分别与所述阻变存储器和所述参考电流生成器电连接;

11.所述参考电流模块用于根据所述基础参考电流和所述位线电流得到所述参考电流;

12.所述数据读出模块用于比对所述参考电流与所述位线电流的大小,以读出所述存储数据。

13.在一种可行的实施方式中,所述参考电流模块包括反馈单元和多个放大单元;

14.所述反馈单元分别与所述阻变存储器和所述放大单元电连接,所述放大单元分别与所述数据读出模块和所述参考电流生成器电连接;

15.所述反馈单元用于根据所述阻变存储器的所述位线电流生成激励响应,并根据所

述激励响应控制对应所述放大单元的导通;

16.所述放大单元用于将所述基础参考电流进行放大得到对应的所述参考电流。

17.在一种可行的实施方式中,多个所述放大单元并联,每个所述放大单元对应一个放大系数。

18.在一种可行的实施方式中,所述放大单元包括第一mos管,所述第一mos管的栅极与所述反馈单元电连接。

19.在一种可行的实施方式中,所述放大单元包括第二mos管,所述第二mos管与所述参考电流生成器之间设置有第三mos管;

20.所述第三mos管的沟道宽长比乘以所述放大系数等于对应所述第二mos管的沟道宽长比。

21.在一种可行的实施方式中,所述自适应灵敏电流放大器包括前置保护模块;

22.所述数据读出模块包括位线电流输入端、参考电流输入端和数据读出端;

23.所述位线电流输入端和所述参考电流输入端分别电连接所述前置保护模块。

24.在一种可行的实施方式中,所述参考电流生成器包括复制阻变存储模块和电流生成模块;

25.所述电流生成模块用于在所述复制阻变存储模块处于低阻态时生成所述基础参考电流,其中,所述复制阻变存储模块处于低阻态时的电流为低阻电流,所述低阻电流是所述基础参考电流的两倍。

26.在一种可行的实施方式中,所述复制阻变存储模块包括多个阻变存储单元。

27.第二方面,一种阻变存储电路,包括:阻变存储器和上述任一项所述的阻变存储器的数据读出电路;

28.所述阻变存储器包括阻变存储阵列和数据写入控制电路,所述阻变存储阵列与所述数据写入控制电路电连接;

29.所述阻变存储阵列与所述阻变存储器的数据读出电路电连接;

30.所述阻变存储阵列包括多个阻变存储单元。

31.本技术实施例提供的阻变存储器的数据读出电路和阻变存储电路,通过设置适应灵敏电流放大器和参考电流生成器,参考电流生成器可以生成基础参考电流,适应灵敏电流放大器可以根据位线电流的大小适应性调整对应的参考电流的大小,参考电流与基础参考电流是线性的系数关系,通过动态调整参考电流的大小,可以保证整参考电流一直处于高阻态和低阻态输出的位线电流的中间位置,使得在阻变存储器发生高阻退化的情况下仍能正确读出存储数据。能够提高对于位线电流与参考电流大小的判断精度,可以避免发生由于阻变存储器的阻态退化导致阻变存储窗口变小,从而造成数据读出错误的问题。

附图说明

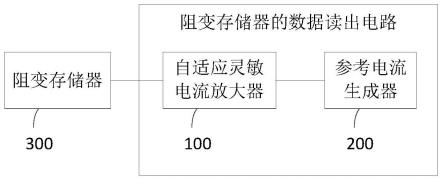

32.图1为本技术实施例提供的一种阻变存储器的数据读出电路的示意性结构框图;

33.图2为本技术实施例提供的另一种阻变存储器的数据读出电路的示意性结构框图;

34.图3为本技术实施例提供的又一种阻变存储器的数据读出电路的示意性结构框图;

35.图4为本技术实施例提供的再一种阻变存储器的数据读出电路的示意性结构图;

36.图5为本技术实施例提供的一种阻变存储器的数据读出电路的示意性结构框图;

37.图6为本技术实施例提供的另一种阻变存储器的数据读出电路的示意性结构图;

38.图7为本技术实施例提供的一种阻变存储电路的示意性结构框图。

具体实施方式

39.为了更好的理解本说明书实施例提供的技术方案,下面通过附图以及具体实施例对本说明书实施例的技术方案做详细的说明,应当理解本说明书实施例以及实施例中的具体特征是对本说明书实施例技术方案的详细的说明,而不是对本说明书技术方案的限定,在不冲突的情况下,本说明书实施例以及实施例中的技术特征可以相互组合。

40.在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。术语“两个以上”包括两个或大于两个的情况。

41.阻变存储器以良好的可微缩性、低功耗和与逻辑工艺良好的兼容性成为一种较有前途的先进工艺节点下的嵌入式非易失存储器,被广泛的应用于消费电子、自动驾驶汽车、工业控制和物联网边缘设备等领域。然而,伴随着阻变存储器的使用,阻变存储器的高阻态逐渐退化,即高阻态的阻值大幅度减小,容易导致数据读出电路难以正常区分高阻态和低阻态,导致数据读出错误。

42.有鉴于此,本技术提供一种阻变存储器的数据读出电路,能够改善阻变存储器的高阻态退化带来数据读出错误的问题。

43.在一种可行的实施方式中,图1为本技术实施例提供的一种阻变存储器的数据读出电路的示意性结构框图。示例性的,如图1所示,本技术实施例提供一种阻变存储器的数据读出电路,包括:自适应灵敏电流放大器(current sense amplifier,csa)100和参考电流生成器200,自适应灵敏电流放大器100用于电连接阻变存储器300,自适应灵敏电流放大器100与参考电流生成器200电连接。参考电流生成器200用于生成基础参考电流;自适应灵敏电流放大器100用于根据基础参考电流和阻变存储器300的位线电流得到参考电流;自适应灵敏电流放大器100用于比对参考电流与位线电流的大小,以读出存储数据。

44.示例性的,结合图1,本技术实施例提供的一种阻变存储器的数据读出电路能够读出阻变存储器300的存储数据,具体的,阻变存储器300在工作过程中会产生位线电流i

bl

,位线电流i

bl

是流经阻变存储器的电流,阻变存储器的数据读出电路可以通过判断位线电流i

bl

与自身生成的参考电流i

ref

的大小来读出阻变存储器300的存储数据。示例性的,如果i

bl

》i

ref

,则阻变存储器的数据读出电路输出为“1”,如果i

bl

《i

ref

,则阻变存储器的数据读出电路输出为“0”。示例性的,阻变存储器300处于高阻态时,位线电流i

bl

相对较小,则阻变存储器的数据读出电路输出为“0”;阻变存储器300处于低阻态时,位线电流i

bl

相对较大,则阻变

存储器的数据读出电路输出为“1”。如果高阻态出现退化现象,即高阻态的阻值大幅度减小,此时,高阻态对应的位线电流i

bl

相应变大,如果参考电流i

ref

始终不变,则在判断大小关系时容易发生i

bl

》i

ref

的情况,阻变存储器的数据读出电路输出为“1”,导致阻变存储器300处于高阻态时,阻变存储器的数据读出电路输出为“1”,此时发生数据读出错误。阻变存储器300发生高阻态退化会造成阻变存储窗口变小,阻变存储器300的阻变存储窗口变小容易导致数据读出错误率的升高。因此,本技术实施例提供的阻变存储器的数据读出电路,参考电流生成器200可以生成基础参考电流i1,自适应灵敏电流放大器100通过与阻变存储器300的电连接接收到阻变存储器300的位线电流i

bl

,自适应灵敏电流放大器100可以判断当前被读取的阻变存储器300的位线电流i

bl

是否发生偏移,例如,当阻变存储器300内高阻态发生退化情况,即高阻态的阻值大幅度减小,此时,则高阻态对应的位线电流i

bl

相应变大,适应灵敏电流放大器100可以根据当前位线电流i

bl

的大小调整对应的参考电流i

ref

,参考电流i

ref

大小的调整是以基础参考电流i1为基础,例如,参考电流i

ref

=调整系数

×

基础参考电流i1,调整系数可以根据预先设定,本技术不作具体限定。示例性的,当阻态相同时,如果位线电流i

bl

变大,则可以相应的将参考电流i

ref

调大,如果位线电流i

bl

变小,则可以相应的将参考电流i

ref

调小。通过动态调整参考电流i

ref

的大小,可以保证整参考电流i

ref

一直处于高阻态和低阻态输出的位线电流i

bl

的中间位置,使得在阻变存储器300发生高阻退化的情况下仍能正确读出存储数据。

45.本技术实施例提供的阻变存储器的数据读出电路,通过设置适应灵敏电流放大器100和参考电流生成器200,参考电流生成器200可以生成基础参考电流i1的大小,适应灵敏电流放大器100可以根据位线电流i

bl

的大小适应性调整对应的参考电流i

ref

,参考电流i

ref

与基础参考电流i1是线性的系数关系,通过动态调整参考电流i

ref

的大小,可以保证整参考电流i

ref

一直处于高阻态和低阻态输出的位线电流的中间位置,使得在阻变存储器发生高阻退化的情况下仍能正确读出存储数据。能够提高对于位线电流i

bl

与参考电流i

ref

大小的判断精度,可以避免发生由于阻变存储器300的阻态退化导致阻变存储窗口变小,从而造成数据读出错误的问题。

46.在一种可行的实施方式中,图2为本技术实施例提供的另一种阻变存储器的数据读出电路的示意性结构框图。示例性的,如图2所示,自适应灵敏电流放大器100包括:数据读出模块110和参考电流模块120;数据读出模块110与参考电流模块120电连接,数据读出模块110用于与阻变存储器300电连接,参考电流模块120分别与阻变存储器300和参考电流生成器200电连接;参考电流模块120用于根据基础参考电流和位线电流得到参考电流;数据读出模块110用于比对参考电流与位线电流的大小,以读出存储数据。

47.示例性的,参考图2,参考电流模块120可以根据位线电流i

bl

判断是否需要调整当前的参考电流i

ref

,当判断需要调整当前的参考电流i

ref

时,基于基础参考电流i1可以得到对应的参考电流i

ref

,从而实现调整当前的参考电流i

ref

。数据读出模块110可以用于比对位线电流i

bl

与调整后的参考电流i

ref

的大小,以读出存储数据。

48.本技术实施例提供的阻变存储器的数据读出电路,通过在自适应灵敏电流放大器100内设置数据读出模块110和参考电流模块120,参考电流模块120可以基于基础参考电流i1和位线电流i

bl

调整当前参考电流i

ref

,数据读出模块110可以比对参考电流i

ref

与位线电流i

bl

的大小,以读出存储数据,以实现提高对于位线电流i

bl

与参考电流i

ref

大小的判断精

度,可以避免发生由于阻变存储器300的阻态退化导致阻变存储窗口变小,从而造成数据读出错误的问题。

49.在一种可行的实施方式中,图3为本技术实施例提供的又一种阻变存储器的数据读出电路的示意性结构框图。示例性的,如图3所示,参考电流模块120包括反馈单元121和多个放大单元122;反馈单元121分别与阻变存储器300和放大单元122电连接,放大单元122分别与数据读出模块110和参考电流生成器200电连接;反馈单元121用于根据阻变存储器300的位线电流生成激励响应,并根据激励响应控制对应放大单元的导通;放大单元122用于将基础参考电流进行放大得到对应的参考电流。

50.在一种可行的实施方式中,多个放大单元122并联,每个放大单元122对应一个放大系数,放大系数可以对应上述实施例提到的调整系数。

51.示例性的,继续参考图3,图3所示放大单元122的数量为4个,分别为1号放大单元、2号放大单元、3号放大单元和4号放大单元,只是示意性的,不作为本技术的具体限定。反馈单元121可以将阻变存储器300的位线电流i

bl

生成激励响应,可以根据激励响应控制具体哪一个放大单元122将被导通。示例性的,如图3所示,如果放大单元122的数量为4个,则激励响应可以是4位代码,例如,[1000]、[0100]、[0010]和[0001],激励响应[1000]可以表示1号放大单元被导通,其他放大单元均不导通;激励响应[0100]可以表示2号放大单元被导通,其他放大单元均不导通;激励响应[0010]可以表示3号放大单元被导通,其他放大单元均不导通;激励响应[0001]可以表示4号放大单元被导通,其他放大单元均不导通。放大单元122可以将基础参考电流i1进行放大得到对应的参考电流,示例性的,每个放大单元122对应一个放大系数,放大系数可以是任意大于0的数,例如,0.5、0.8、1.2、1.5、2、3、4或5等,本技术不作具体限定。基础参考电流i1乘以任意放大单元122对应的放大系数可以得到对应的参考电流i

ref

,即每个放大单元122的导通对应不同的参考电流i

ref

。被控制导通的放大单元122会将对应的参考电流i

ref

提供给数据读出模块110。

[0052]

本技术实施例提供的阻变存储器的数据读出电路,通过设置反馈单元121,根据位线电流i

bl

生成激励响应,根据激励响应控制选择放大单元122的导通,多个放大单元122并联,每个放大单元122对应一个放大系数,通过放大单元122的导通以对基础参考电流i1的系数放大,通过反馈单元121通过激励响应控制对应放大单元的导通,可以实现对当前参考电流i

ref

的调整。实现提高对于位线电流i

bl

与参考电流i

ref

大小的判断精度,可以避免发生由于阻变存储器300的阻态退化导致阻变存储窗口变小,从而造成数据读出错误的问题。

[0053]

在一种可行的实施方式中,图4为本技术实施例提供的再一种阻变存储器的数据读出电路的示意性结构图。示例性的,如图4所示,放大单元122包括第一mos管,第一mos管的栅极与反馈单元121电连接。图4所示的放大单元122的数量为4个,4个放大单元122对应的第一mos管分别为第一mos管p0、第一mos管p1、第一mos管p2和第一mos管p3。每个第一mos管的栅极均与反馈单元121电连接,第一mos管的开启可以控制对应放大单元122的导通,第一mos管的关闭可以控制对应放大单元122的断开,反馈单元121可以根据激励响应给第一mos管的栅极通入电信号以开启第一mos管,实现控制对应放大单元122的导通。采用mos管实现开关控制较为灵敏,且可以通过脉冲信号或者其他电信号来实现,便于控制,且不会增加电路的读出延迟。

[0054]

在一种可行的实施方式中,继续参考图4,放大单元122还包括第二mos管,图4所示

的放大单元对应的第二mos管分别为第二mos管m0、第二mos管m1、第二mos管m2和第二mos管m3。第二mos管与参考电流生成器200之间设置有第三mos管m4。第三mos管m4的沟道宽长比乘以放大系数等于对应第二mos管的沟道宽长比,即第三mos管m4的沟道宽长比与第二mos管的沟道宽长比等于对应放大单元122的放大系数。第三mos管m4的源级和栅极短路连接可以使得第三mos管m4处于饱和状态,流经第三mos管m4的电流始终都为基础参考电流i1,通过将第二mos管和第三mos管m4的栅极串联,以及将mos管的沟道宽长比的不同设计来实现对于基础参考电流i1的放大。示例性的,如果第三mos管m4的沟道宽长比为1,第二mos管m0、第二mos管m1、第二mos管m2和第二mos管m3的沟道宽长比分别为3、6、9和12,则对应的流经第二mos管m0、第二mos管m1、第二mos管m2和第二mos管m3的电流分别为i3=3i1、i6=6i1、i9=9i1和i

12

=12i1,因此,可以实现对基础参考电流i1的放大,得到对应的参考电流i

ref

。通过设计第二mos管不同的沟道尺寸(宽长比)来实现电流放大比较容易实现,且精度较高。本实施例提供的mos管的沟道尺寸只是示意性的,不作为本技术的具体限定。

[0055]

继续参考图4,自适应灵敏电流放大器100包括前置保护模块130;数据读出模块110包括位线电流输入端111、参考电流输入端112和数据读出端dq;位线电流输入端111和参考电流输入端112分别电连接前置保护模块130。图4所示的数据读出模块110可以采用比较器comp,比较器comp的两个输入端分别作为位线电流输入端111、参考电流输入端112,输出端作为数据读出端dq。前置保护模块130可以起到限流保护的作用,具体的通过分别控制电压vmat和vref来实现控制流经前置保护模块130的电流不会过大,可以避免电流过大损伤比较器comp。图4中两个前置保护模块130相对于比较器comp对称设置,且两个前置保护模块130的电路结构相同,可以对比较器comp的两个输入端提供限流保护。如图4所示,vdd可以表示高电平,vss可以表示低电平;en_readn和en_read可以分别代表mos管的开启使能信号端,vclamp可以代表钳位电路的电压输入端,前置保护模块130包括nmos和pmos,图4所示前置保护模块130的电路结构只是示意性的,不作为本技术的具体限定。参考电流i

ref

通过前置保护模块130输入到参考电流输入端112,位线电流i

bl

通过前置保护模块130输入到位线电流输入端111。

[0056]

在一种可行的实施方式中,图5为本技术实施例提供的一种阻变存储器的数据读出电路的示意性结构图。示例性的,如图5所示,参考电流生成器200包括复制阻变存储模块210和电流生成模块220;电流生成模块220用于在复制阻变存储模块210处于低阻态时生成基础参考电流i1,其中,复制阻变存储模块处于低阻态时的电流为低阻电流,低阻电流是基础参考电流的两倍。

[0057]

在一种可行的实施方式中,图6为本技术实施例提供的另一种阻变存储器的数据读出电路的示意性结构图。示例性的,如图6所示,复制阻变存储模块210包括多个阻变存储单元211,多个阻变存储单元211可以呈阵列排布,本技术不作具体限定。电流生成模块220在所有阻变存储单元211处于低阻态时生成基础参考电流i1,其中,复制阻变存储模块210处于低阻态时的电流为低阻电流i0,低阻电流i0是基础参考电流i1的两倍,电流生成模块220以阻变存储单元211的低阻态为参考基准生成基础参考电流i1,即电流生成模块220将低阻电流i0做减半处理得到基础参考电流i1。通过复制阻变存储模块210得到的低阻电流i0是模拟阻变存储器的最大电流,以低阻电流i0的一半作为基础参考电流i1,后续对基础参考电流i1进行不同程度的放大调节,可以使得参考电流i

ref

始终保持在低阻态位线电流和高

阻态位线电流之间,低阻态位线电流是阻变存储器300处于低阻态时的位线电流,高阻态位线电流是阻变存储器300处于高阻态时的位线电流,如此,能够使得高阻位线电流始终小于参考电流,低阻位线电流始终大于参考电流,可以实现阻变存储器300处于高阻态时阻变存储器的数据读出电路输出为“0”,阻变存储器300处于低阻态时阻变存储器的数据读出电路输出为“1”。从而能够提高对于位线电流i

bl

与参考电流i

ref

大小的判断精度,可以避免发生由于阻变存储器300的阻态退化导致阻变存储窗口变小,从而造成数据读出错误的问题。复制阻变存储模块210可以直接由阻变存储器300中的阻变存储单元复制得到,本技术不作具体限定。

[0058]

第二方面,本技术实施例提供一种阻变存储电路,图7为本技术实施例提供的一种阻变存储电路的示意性结构框图。示例性的,如图7所示,本技术实施例提供一种阻变存储电路,包括:阻变存储器和上述任一项阻变存储器的数据读出电路csa;阻变存储器包括阻变存储阵列310和数据写入控制电路,阻变存储阵列310与数据写入控制电路电连接;阻变存储阵列310与阻变存储器的数据读出电路csa电连接;阻变存储阵列310包括多个阻变存储单元311,多个阻变存储单元311呈阵列排列。

[0059]

示例性的,如图7所示,阻变存储单元311采用1t1r的结构,即每个阻变存储单元311包括1个mos管和1个电阻,每行串联的阻变存储单元311电连接1个阻变存储器的数据读出电路csa。复制阻变存储模块210分别与数据写入控制电路和电流生成模块220电连接。数据写入控制电路包括第一数据写入控制电路321和第二数据写入控制电路322。

[0060]

阻变存储单元311通过阻变层中的氧空位进行导电,当氧空位之间的间隙变化时,阻变存储单元导电能力也发生变化,这种变化可以反映在电流或者电阻的变化中。在对阻变存储阵列310进行写操作时,需要使对应被写入的阻变存储单元311形成导电通路(这个过程可以被称为form),否则阻变存储单元311处于绝缘状态。在操作过程中,需要在阻变存储单元311的两端形成较大的电位差,此时,字线(word line,wl)施加一个合适的电压使得mos管处于饱和状态,可以起到限流,防止电流过大损伤阻变存储单元311的作用;在位线(bit line,bl)上施加较大的电压,源线(source line,sl)接地,以激活阻变层中的氧空位,在电场的作用下形成导电通道,阻变存储单元311变至低阻态(low resistance state,lrs)。将阻变存储单元311重回高阻态(hight resistance state,hrs),使阻变存储单元311的导电通路断裂的过程称为复位(rest),这个操作过程与form过程相反,需要对阻变存储单元311施加反向电压使导电细丝断裂,具体的,字线wl施加电压使mos管处于线性状态(电阻增大不需要限流),位线bl接地,源线sl施加电压,可以使得阻变存储单元311由低阻态转变为高阻态,此过程为擦除数据或者写入“0”(rest)的过程。置位操作(set)的过程与form操作过程类似,但是form过的阻变存储单元311不需要太大的位线电压就能够形成导电通道。容易理解的是,从高阻态变为低阻态是写入“1”的过程。利用阻变存储单元311在擦写过程中,导电通路会随机的形成与断裂,组成导电通路的氧空位之间存在纳米级间隙,间隙大小的不可预测以及氧空位的随机分布导致通路的形状与尺寸的变化,这就导致了阻变存储单元311之间阻值的变化,将这种变化提取出来就可以作为物理不可克隆函数(physical unclonaable function,puf)的响应,对多个阻变存储单元311进行form操作后,再通过set和rest的puf的初始化密钥生成过程,选择一个合适的参考电流,通过阻变存储器的数据读出电路csa对参考电流和位线电流的比较,可以读出存储数据(0或1),得到的

存储数据可以作为puf的密钥。

[0061]

示例性的,如图7所示,第一数据写入控制电路321用于根据时钟信号clk控制字线wl电压的施加,第二数据写入控制电路322用于控制源线sl和位线bl是接地还是接入电压。通常mos管的栅极对应字线wl,源级对应源线sl,漏极对应位线bl。示例性的,如图7所示,同列阻变存储单元311对应相同的字线wl信号,阻变存储阵列310的字线信号分别为wl《0》、wl《0》、

…

、wl《30》wl《31》(32位);同行阻变存储单元311对应相同的源线sl信号,阻变存储阵列310的源线信号分别为sl《0》、sl《0》、

…

、sl《30》、sl《31》(32位);同行阻变存储单元311对应相同的位线bl电流,阻变存储阵列310的位线电流分别为i

bl0

、i

bl1

、

…

、i

bl30

、i

bl31

(32位);对应读出的存储数据分别位dq0、dq1、

…

、dq30、dq31(32位)。复制阻变存储模块210的字线为wlr(wlr《0》、wlr《0》、

…

、wlr《30》、wlr《31》),源线为sl_r,位线为bl_r,位线电流为i

bl_r

,基础参考电流i1根据位线电流为i

bl_r

生成。图7所示,阻变存储阵列310中的32行

×

32列的阻变存储单元311只是示意性的表示,不作为本技术的具体限定,

[0062]

本技术实施例提供的阻变存储电路,针对阻变存储单元的高阻态退化导致的存储窗口减小,使得阻变存储器的读出电路无法正常识别低阻态和高阻态,从而导致存储数据的读出错误。本技术实施例提供的阻变存储电路,设置有阻变存储器的数据读出电路csa,利用复制阻变存储模块210和电流生成模块220生成基础参考电流i1,自适应灵敏电流放大器100根据位线电流i

bl

和基础参考电流i1得到适应性调整的参考电流i

ref

。当位线电流i

bl

由于高阻态的退化而发生变化时,通过对基础参考电流i1的相应放大,来达到调整参考电流i

ref

的效果,以同步适应性调整与位线电流i

bl

比对的整参考电流i

ref

方式来补偿存储窗口减小的问题,实现提高对于位线电流i

bl

与参考电流i

ref

大小的判断精度,从而避免数据读出错误问题的发生,使得在阻变存储单元发生高阻退化的情况下仍能正确读出存储数据。

[0063]

尽管已描述了本说明书的优选实施例,但本领域内的技术人员一旦得知了基本创造性概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本说明书范围的所有变更和修改。

[0064]

显然,本领域的技术人员可以对本说明书进行各种改动和变型而不脱离本说明书的精神和范围。这样,倘若本说明书的这些修改和变型属于本说明书权利要求及其等同技术的范围之内,则本说明书也意图包含这些改动和变型在内。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。