1.本发明涉及存内计算领域,特别是涉及一种存内计算单元及装置。

背景技术:

2.卷积神经网络(cnns)在大规模识别任务中的精度得到了前所未有的提高。然而,算法复杂度和内存访问限制了cnn硬件的能量效率和加速速度。因此,亟需一种存内计算单元或装置能够提高计算效率。

技术实现要素:

3.本发明的目的是提供一种存内计算单元及装置,能够提高计算效率。

4.为实现上述目的,本发明提供了如下方案:

5.一种存内计算单元,包括:译码器和sram单元;

6.所述译码器用于将输入数据进行正负区分,并将输出结果输入至字线wlr和字线wll;

7.所述sram单元的第一输入端与字线wll连接,所述sram单元的第二输入端与字线wlr连接;

8.所述sram单元的第一输出端与位线bl连接,所述sram单元的第二输出端与位线blb连接。

9.可选地,所述sram单元为6t sram。

10.一种存内计算装置,包括:多个存内计算单元阵列;每个所述存内计算单元阵列包括:多个存内计算单元;

11.所述存内计算单元阵列用于将位线bl和位线blb的放电结果进行乘累加计算。

12.可选地,还包括:adc模块;

13.所述adc模块用于将乘累加计算进行量化处理。

14.根据本发明提供的具体实施例,本发明公开了以下技术效果:

15.本发明所提供的一种存内计算单元及装置,利用所述译码器将输入数据进行正负区分,并将输出结果输入至字线wlr和字线wll,进而控制相应的字线的打开和关闭,进一步确定位线是否放电,这样不需要在存内计算单元阵列中添加额外的模拟结构为乘累加的模拟电压结果区分高低位,既节省了这一操作,提升了计算速度,同时也降低了开销。

附图说明

16.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

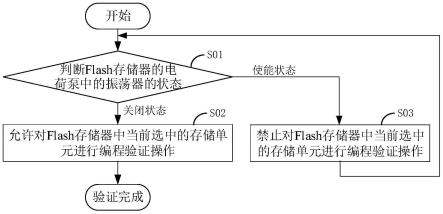

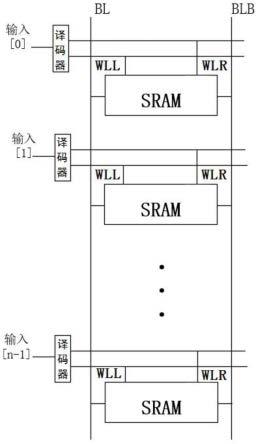

17.图1为本发明所提供的一种存内计算单元阵列结构示意图。

具体实施方式

18.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

19.本发明的目的是提供一种存内计算单元及装置,能够提高计算效率。

20.为使本发明的上述目的、特征和优点能够更加明显易懂,下面结合附图和具体实施方式对本发明作进一步详细的说明。

21.图1为本发明所提供的一种存内计算单元阵列结构示意图,如图1所示,本发明所提供的一种存内计算单元,包括:译码器和sram单元。

22.所述译码器用于将输入数据进行正负区分,并将输出结果输入至字线wlr和字线wll。

23.输出结果为正,则打开字线wlr,输出结果为负,则打开字线wlr,对应的读出sram单元左右权重存储节点其中一个的值,完成了输入数据与权重存储节点中存储的值的乘法。

24.所述sram单元的第一输入端与字线wll连接,所述sram单元的第二输入端与字线wlr连接。

25.所述sram单元的第一输出端与位线bl连接,所述sram单元的第二输出端与位线blb连接。

26.所述sram单元为6t sram。

27.一种存内计算装置,包括:多个如图1所示的存内计算单元阵列;每个所述存内计算单元阵列包括:多个存内计算单元;

28.所述存内计算单元阵列用于将位线bl和位线blb的放电结果进行乘累加计算。

29.一列存内计算单元阵列中sram单元存储了整个权重矩阵所有数。而存内计算装置包括多个存内计算单元阵列,即存储了不同的高低位。

30.通过将不同数据的相同位安排在同一阵列进行乘累加,数据高低位的组合可以在数字外围电路中统一组合,可以在阵列中实现不同精度数据的自由组合。

31.本发明所提供的一种存内计算装置,还包括:adc模块。所述adc模块用于将乘累加计算进行量化处理。

32.本发明在存内计算单元阵列的基础上增加有限的面积,实现了在存储阵列的内部进行计算,并且其计算的各阶段划分简单,不会出现额外的复杂时序控制要求。各个列之间可以独立的工作,具有很好的并发性,可以大幅提升计算效率。

33.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的系统而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

34.本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的一般技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处。综上所述,本说明书内容不

应理解为对本发明的限制。

技术特征:

1.一种存内计算单元,其特征在于,包括:译码器和sram单元;所述译码器用于将输入数据进行正负区分,并将输出结果输入至字线wlr和字线wll;所述sram单元的第一输入端与字线wll连接,所述sram单元的第二输入端与字线wlr连接;所述sram单元的第一输出端与位线bl连接,所述sram单元的第二输出端与位线blb连接。2.根据权利要求1所述的一种存内计算单元,其特征在于,所述sram单元为6t sram。3.一种存内计算装置,其特征在于,包括:多个存内计算单元阵列;每个所述存内计算单元阵列包括:多个权利要求1-2任意一项所述的存内计算单元;所述存内计算单元阵列用于将位线bl和位线blb的放电结果进行乘累加计算。4.根据权利要求1所述的一种存内计算装置,其特征在于,还包括:adc模块;所述adc模块用于将乘累加计算进行量化处理。

技术总结

本发明涉及一种存内计算单元及装置。该单元包括:译码器和SRAM单元;所述译码器用于将输入数据进行正负区分,并将输出结果输入至字线WLR和字线WLL;所述SRAM单元的第一输入端与字线WLL连接,所述SRAM单元的第二输入端与字线WLR连接;所述SRAM单元的第一输出端与位线BL连接,所述SRAM单元的第二输出端与位线BLB连接。本发明能够提高计算效率。本发明能够提高计算效率。本发明能够提高计算效率。

技术研发人员:乔树山 李润成 尚德龙 周玉梅

受保护的技术使用者:中科南京智能技术研究院

技术研发日:2022.07.27

技术公布日:2022/10/11

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。