减少延迟单元的ddr dfe接收电路结构

技术领域

1.本发明涉及ddr技术领域,尤其涉及ddr dfe接收电路结构。

背景技术:

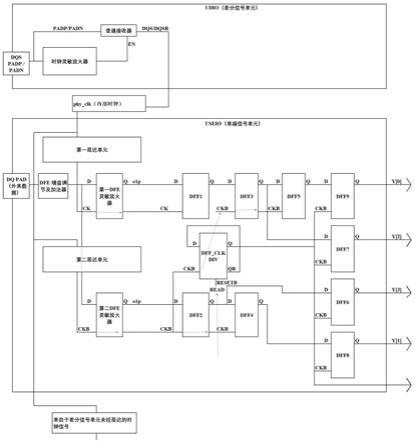

2.随着速度的越来越高,现有ddr 尤其ddr5等电路中需要增加判决反馈均衡(dfe)结构,受限于本身的工作速度,dfe通常需要把进来的数据dq分作奇偶两路【图1中dfe灵敏放大器(dfe sense latch high) 和dfe灵敏放大器(dfe sense latch low)】来分别处理。此处即需要每路各有一个延迟单元(256 step delay line )1、2来调整dqs 和dq的时序关系。另一方面,ddr本身的特点,需要差分单元(dio)过来的时钟信号dqs来对数据dq采样,产生数据e1p 和o1p,之后又需要把此时钟域的信号e1p和o1p转换为内部时钟(phy_clk)域的信号,方便中央处理器(cpu)等直接处理,此处又需要两个延迟单元3、4对e1p/o1p 采样,经进一步由时钟分频触发器(dff_clkdiv)降速后由触发器(dff)9/7/6/8 产生并行的四路数据。

3.即需要两个延迟单元来处理数据dq与dqs的时序关系,还需要两个延迟单元(delay line )把此数据处理成内部时钟(phy_clk)的信号,四个延迟单元占据了巨大面积。

技术实现要素:

4.本发明的目的在于提供减少延迟单元的ddr dfe接收电路结构,有效减少延迟单元的数量和面积,实现节省成本的目的。

5.实现上述目的的技术方案是: 一种减少延迟单元的ddr dfe接收电路结构,包括:第一dfe灵敏放大器、第二dfe灵敏放大器、第一延迟单元、第二延迟单元和触发电路,其中,所述第一dfe灵敏放大器通过所述第一延迟单元接收内部时钟;所述第二dfe灵敏放大器通过所述第二延迟单元接收内部时钟;所述第一dfe灵敏放大器和所述第二dfe灵敏放大器根据外来数据分别产生时钟域信号elp和olp,并连接所述触发电路;所述触发电路通过所述第一延迟单元和所述第二延迟单元接收内部时钟。

6.优选的,所述触发电路包括:时钟分频触发器以及第一至第九触发器,所述第一dfe灵敏放大器、第一触发器、第三触发器、第五触发器和第九触发器依次串接;所述第二dfe灵敏放大器、第二触发器、第四触发器和第八触发器依次串接;所述第七触发器连接所述第三触发器和第五触发器的相接端;所述第六触发器连接所述第二触发器和第四触发器的相接端;所述第一延迟单元连接所述第一触发器;所述第二延迟单元连接所述第二触发器、第三触发器、第四触发器、第五触发器和

时钟分频触发器;所述时钟分频触发器连接所述第六触发器、第七触发器、第八触发器和第九触发器。

7.一种减少延迟单元的ddr dfe接收电路结构,包括:第一dfe灵敏放大器、第二dfe灵敏放大器、第一延迟单元、反相器和触发电路,其中,所述第一dfe灵敏放大器通过所述第一延迟单元接收内部时钟;所述第一延迟单元通过所述反相器连接所述第二dfe灵敏放大器;所述第一dfe灵敏放大器和所述第二dfe灵敏放大器根据外来数据分别产生时钟域信号elp和olp,并连接所述触发电路;所述触发电路分别连接所述第一延迟单元和所述反相器。

8.优选的,所述触发电路包括:时钟分频触发器以及第一至第九触发器,所述第一dfe灵敏放大器、第一触发器、第三触发器、第五触发器和第九触发器依次串接;所述第二dfe灵敏放大器、第二触发器、第四触发器和第八触发器依次串接;所述第七触发器连接所述第三触发器和第五触发器的相接端;所述第六触发器连接所述第二触发器和第四触发器的相接端;所述第一延迟单元连接所述第一触发器;所述反相器连接所述第二触发器、第三触发器、第四触发器、第五触发器和时钟分频触发器;所述时钟分频触发器连接所述第六触发器、第七触发器、第八触发器和第九触发器。

9.本发明的有益效果是:本发明直接用内部时钟(phy_clk)代替数据采样时钟(dqs)来对数据采样,采用固定四相位采样,采用反相器等措施减少延迟单元数量,面积大大减小,节省成本。

附图说明

10.图1是现有技术中ddr dfe接收电路结构示意图;图2是本发明的减少延迟单元的ddr dfe接收电路结构一实施例的结构图;图3是本发明的减少延迟单元的ddr dfe接收电路结构另一实施例的结构图;图4是本发明中内部时钟与dfe_clkdiv 产生的多相位分频时钟与 dff6,7,8,9 的相位时序关系。

具体实施方式

11.下面将结合附图对本发明作进一步说明。

12.实施例一如图2所示,本发明的减少延迟单元的ddr dfe接收电路结构,包括:第一dfe灵敏放大器、第二dfe灵敏放大器、第一延迟单元、第二延迟单元和触发电路,其中,差分信号单元输出内部时钟。第一dfe灵敏放大器通过第一延迟单元接收内部时钟;第二dfe灵敏放大器通过所述第二延迟单元接收内部时钟。

13.第一dfe灵敏放大器和第二dfe灵敏放大器根据外来数据dq分别产生时钟域信号elp和olp,并连接触发电路;其中,外来数据dq经dfe增益调节及加法器模块处理后同时送至第一dfe灵敏放大器和第二dfe灵敏放大器,在dfe增益调节环节,外来数据dq电平及幅值会被调节至合适和水平,以便信号经加法器后方便的被第一、二dfe灵敏放大器接收。其中的加法器即:把外来数据与dfe中dff1,2,3,4 各级反馈信号相加的单元。

14.触发电路通过第一延迟单元和第二延迟单元接收内部时钟。

15.触发电路包括:时钟分频触发器dff_clkdiv以及第一至第九触发器dff1-dff9,第一dfe灵敏放大器、第一触发器dff1、第三触发器dff3、第五触发器dff5和第九触发器dff9依次串接。第二dfe灵敏放大器、第二触发器dff2、第四触发器dff4和第八触发器dff8依次串接。第七触发器dff7连接第三触发器dff3和第五触发器dff5的相接端。第六触发器dff6连接第二触发器dff2和第四触发器dff4的相接端。第一延迟单元连接第一触发器dff1;第二延迟单元连接第二触发器dff2、第三触发器dff3、第四触发器dff4、第五触发器dff5和时钟分频触发器dff_clkdiv。

16.时钟分频触发器dff_clkdiv连接第六触发器dff6、第七触发器dff7、第八触发器dff8和第九触发器dff9。

17.本发明在原有的基础上把第一级的采样时钟dqs换为内部时钟(phy_clk),便可省去图1中处理dqs与phy_clk 时钟域时序关系的延迟单元3,延迟单元4。同时dff1/dff2 由原来上升沿采样变为下降沿采样,给e1p/o1p 信号留出足够的稳定和建立时间,取代延迟单元3、4 的时延。

18.实施例二如图3所示,一种减少延迟单元的ddr dfe接收电路结构,包括:第一dfe灵敏放大器、第二dfe灵敏放大器、第一延迟单元、反相器inv和触发电路。

19.第一dfe灵敏放大器通过第一延迟单元接收内部时钟;第一延迟单元通过反相器inv连接第二dfe灵敏放大器。

20.第一dfe灵敏放大器和第二dfe灵敏放大器根据外来数据分别产生时钟域信号elp和olp,并连接触发电路;触发电路分别连接第一延迟单元和反相器inv。

21.触发电路包括:时钟分频触发器dff_clkdiv以及第一至第九触发器dff1-dff9。

22.第一dfe灵敏放大器、第一触发器dff1、第三触发器dff3、第五触发器dff5和第九触发器dff9依次串接。第二dfe灵敏放大器、第二触发器dff2、第四触发器dff4和第八触发器dff8依次串接。第七触发器dff7连接第三触发器dff3和第五触发器dff5的相接端。第六触发器dff6连接第二触发器dff2和第四触发器dff4的相接端。第一延迟单元连接第一触发器dff1。反相器inv连接第二触发器dff2、第三触发器dff3、第四触发器dff4、第五触发器dff5和时钟分频触发器dff_clkdiv;时钟分频触发器dff_clkdiv连接第六触发器dff6、第七触发器dff7、第八触发器dff8和第九触发器dff9。

23.进一步,将实施例一中第二延迟单元替换为反相器,如此,延迟单元减少为1个,面积大大减小。

24.如图4所示,最后串转并之后的数据(例如y0)由正反4相位内部时钟(phy_clk)采样,其中必然有至少两组数值正确,根据延迟单元1、2 的延迟数值选择采用哪一路,从而找出正确的数值。其中,dff6,dff7,dff8,dff9会同时产生几笔数据,这些数据通过内部时钟

先后采集,有先后顺序。图4中,0、1、2、3表示一组数据的先后序列;4、5、6、7表示另一组数据的先后序列。

25.以上实施例仅供说明本发明之用,而非对本发明的限制,有关技术领域的技术人员,在不脱离本发明的精神和范围的情况下,还可以作出各种变换或变型,因此所有等同的技术方案也应该属于本发明的范畴,应由各权利要求所限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。