1.本实用新型涉及自启动电路技术领域,具体涉及一种自启动电路。

背景技术:

2.随着科学技术的不断发展,各种各样的智能设备出现在我们的日常生活中,为我们的工作生活提供了极大的便利。这些智能设备设计中会使用各种处理器如cpu、mcu、dsp、fpga等。在运行上述芯片前往往是需要向芯片的启动管脚发送启动信号后,才能开始工作。过去通常采用按键的方式来实现处理器的启动功能,但是某些应用场景下,设备是不支持按键的,此时采用传统的方法已无法启动芯片。

技术实现要素:

3.因此,本实用新型要解决的技术问题在于克服现有技术中的采用按键自启动电路无法适用于不支持按键的设备的缺陷,从而提供一种自启动电路。

4.为达到上述目的,本实用新型提供如下技术方案:

5.本实用新型实施例提供一种自启动电路,包括:第一延时电路、第二延时电路、第一开关电路、第二开关电路,其中,第一延时电路的第一端与外接电源连接,第一延时电路的第二端接地,第一延时电路的第三端与第一开关电路的控制端连接,第一延时电路用于延时第一预设时间;第二延时电路的第一端与外接电源连接,第二延时电路的第二端接地,第二延时电路的第三端与第二开关电路的控制端连接,第二延时电路用于延时第二预设时间,第二预设时间大于第一预设时间;第一开关电路的第一端与外接电源连接,第一开关电路的第二端接地,第一开关电路的第三端与待启动设备连接;第二开关电路的第一端与第一开关电路的控制端连接,第二开关电路的第二端接地;外接电源接通后,在第一延时电路的延时时间达到第一预设时间,以及第二延时电路的延时时间达到第二预设时间过程中,第一开关电路与第二开关电路处于交替导通状态,第一开关电路的第三端依次输出第一电平启动信号、第二电平启动信号、第一电平启动信号,当第二电平启动信号的持续时间达到预设启动时间后,待启动设备启动。

6.在一实施例中,第一延时电路包括:第一电阻、第一电容,其中,第一电容的第一端通过第一电阻与外接电源连接,第一电容的第一端还与第一开关的控制端连接,第一电容的第二端接地。

7.在一实施例中,第二延时电路包括:第二电阻及第二电容,其中,第二电容的第一端通过第二电阻与外接电源连接,第二电容的第一端还与第二开关电路的控制端连接,第二电容的第二端接地。

8.在一实施例中,第二延时电路还包括:放电电路,放电电路与第二电容并联连接。

9.在一实施例中,放电电路包括:第三电阻及二极管,其中,二极管的阴极通过第三电阻与第二电容的第一端连接,二极管的阳极与第二电容的第二端连接。

10.在一实施例中,二极管为肖特基二极管。

11.在一实施例中,第一开关电路包括:第四电阻及第一开关,其中,第一开关的控制端与第一延时电路的第三端连接,第一开关的控制端还与第二开关电路的第一端连接,第一开关的第一端通过第四电阻与外接电源连接,第一开关的第一端还与待启动设备连接,第一开关的第二端接地。

12.在一实施例中,第二开关电路包括:第二开关,其中,第二开关的控制端与第二延时电路的第三端连接,第二开关的第一端与第一开关电路的控制端连接,第二开关的第二端接地。

13.在一实施例中,第二预设时间与第一预设时间的差值为第二电平启动信号的持续时间。

14.本实用新型技术方案,具有如下优点:

15.1.本实用新型提供的自启动电路,外接电源接通后,在第一延时电路的延时时间达到第一预设时间,以及第二延时电路的延时时间达到第二预设时间过程中,所述第一开关电路与所述第二开关电路处于交替导通状态,所述第一开关电路的第三端依次输出第一电平启动信号、第二电平启动信号、第一电平启动信号,当所述第二电平启动信号的持续时间达到预设启动时间后,所述待启动设备启动,从而通过设置两个延时时间代替持续按下按键的时间,以适用于对不支持按键的设备的启动。

16.2.本实用新型提供的自启动电路,将第二电容与放电电路并联连接,从而避免当外接电源快速通断电时,第二电容通过放电电路放电,从而避免自启动电路故障,并利用肖特基二极管的单向导通性、快关频率高、正向压降低的特点来给第二电容放电。

17.3.本实用新型提供的自启动电路,目前的市面上的自启动电路多是由逻辑门器件或者较为复杂的电路搭建而成,设计较为复杂,成本相对也较高,而采用无源器件搭建电路,设计简单,成本低。

附图说明

18.为了更清楚地说明本实用新型具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本实用新型的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

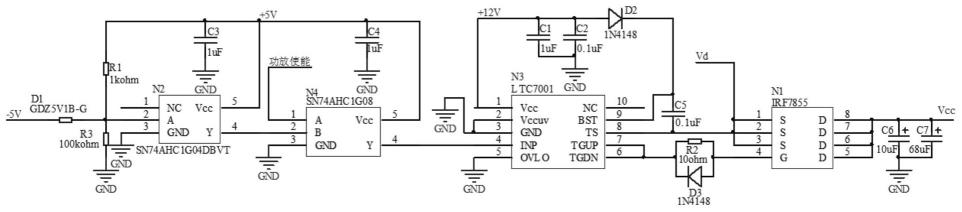

19.图1为本实用新型实施例提供的按键启动电路结构图;

20.图2为本实用新型实施例提供的自启动电路的一个具体示例的组成图;

21.图3为本实用新型实施例提供的自启动电路的电路结构图。

具体实施方式

22.下面将结合附图对本实用新型的技术方案进行清楚、完整地描述,显然,所描述的实施例是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

23.在本实用新型的描述中,需要说明的是,术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是

为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。此外,术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

24.在本实用新型的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,还可以是两个元件内部的连通,可以是无线连接,也可以是有线连接。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本实用新型中的具体含义。

25.此外,下面所描述的本实用新型不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

26.实施例

27.现有技术中的按键启动电路如图1所示,其中,电阻r10和按键开关sw1的连接点为启动信号输出端(即pwkey端),连接芯片的启动管脚,通过外力对按键开关进行控制,来启动芯片。当按键开关sw1没有按下时,芯片的启动管脚的输入信号为高电平,在按下按键开关sw1的一段时间内,芯片的启动管脚的输入信号为低电平,此时芯片会根据低电平的保持时间判断是否误为误触发信号。如不是,会启动芯片开始工作,此时可松开按键。但是某些应用场景下,设备是不支持按键的。此时采用传统的方法已无法启动芯片。需要一种自启动电路完成芯片的启动。因此本实用新型实施例提供一种自启动电路,如图2所示,包括:第一延时电路1、第二延时电路2、第一开关电路3、第二开关电路4。

28.如图2所示,第一延时电路1的第一端与外接电源连接,第一延时电路1的第二端接地,第一延时电路1的第三端与第一开关电路3的控制端连接,第一延时电路1用于延时第一预设时间。

29.如图2所示,第二延时电路2的第一端与外接电源连接,第二延时电路2的第二端接地,第二延时电路2的第三端与第二开关电路4的控制端连接,第二延时电路2用于延时第二预设时间,第二预设时间大于第一预设时间。

30.如图2所示,第一开关电路3的第一端与外接电源连接,第一开关电路3的第二端接地,第一开关电路3的第三端与待启动设备连接。

31.如图2所示,第二开关电路4的第一端与第一开关电路3的控制端连接,第二开关电路4的第二端接地。

32.本实用新型实施例中,外接电源接通后,在第一延时电路1的延时时间达到第一预设时间,以及第二延时电路2的延时时间达到第二预设时间过程中,第一开关电路3与第二开关电路4处于交替导通状态,第一开关电路3的第三端依次输出第一电平启动信号、第二电平启动信号、第一电平启动信号,当第二电平启动信号的持续时间达到预设启动时间后,待启动设备启动。

33.具体地,本实用新型实施例的第一电平启动信号可以为高电平启动信号,第二电平启动信号可以为低电平启动信号。本实用新型实施例自启动电路工作过程分为以下三个阶段:(1)当外接电源通电后,第一延时电路1及第二延时电路2同时进行延时,当第一延时电路1的延时时间未达到第一预设时间、第二延时电路2的延时时间未达到第二预设时间时,第一开关电路3及第二开关电路4均处于关断状态,第一开关电路3的第三端输出高电平

信号,此时待启动设备仍未启动;(2)当第一延时电路1的延时时间达到第一预设时间、第二延时电路2的延时时间未达到第二预设时间时,第一开关电路3导通、第二开关电路4仍处于关断状态,第一开关电路3的第三端持续输出低电平信号,当该低电平信号持续时间达到预设启动时间后,待启动设备启动(也就是说,待启动设备内的芯片判断所接受的低电平信号持续时间达到预设启动时间后,芯片启动);(3)当第一延时电路1的延时时间达到第一预设时间、第二延时电路2的延时时间达到第二预设时间时,第二开关电路4导通、第一开关电路3关断,第一开关电路3的第三端持续输出高电平,完成待启动设备启动工作。

34.在一具体实施例中,如图3所示,第一延时电路1包括:第一电阻r1、第一电容c1,其中,第一电容c1的第一端通过第一电阻r1与外接电源(vcc端)连接,第一电容c1的第一端还与第一开关的控制端(第一开关q1的控制端)连接,第一电容c1的第二端接地。

35.具体地,当外接电源通电后,第一电容c1开始充电,第一电容c1的充电时间为第一预设时间,通过调整外接电源的电压、第一电容c1的性能参数、第一电阻r1的阻值,调整第一预设时间。

36.在一具体实施例中,如图3所示,第二延时电路2包括:第二电阻r2及第二电容c2,其中,第二电容c2的第一端通过第二电阻r2与外接电源(vcc端)连接,第二电容c2的第一端还与第二开关电路4的控制端(q2的控制端)连接,第二电容c2的第二端接地。

37.具体地,当外接电源通电后,第二电容c2开始充电,第二电容c2的充电时间为第二预设时间,通过调整外接电源的电压、第二电容c2的性能参数、第二电阻r2的阻值,调整第二预设时间。

38.在一具体实施例中,如图3所示,第一开关电路3包括:第四电阻r4及第一开关q1,其中,第一开关q1的控制端与第一延时电路1的第三端连接,第一开关q1的控制端还与第二开关电路4的第一端连接,第一开关q1的第一端通过第四电阻r4与外接电源连接,第一开关q1的第一端(pwkey端)还与待启动设备连接,第一开关q1的第二端接地。

39.如图3所示,第二开关电路4包括:第二开关q2,其中,第二开关q2的控制端与第二延时电路2的第三端连接,第二开关q2的第一端与第一开关q1电路3的控制端(q1的控制端)连接,第二开关q2的第二端接地。

40.具体地,当外接电源通电后,由于第一电容c1及第二电容c2的作用,第一开关q1及第二开关q2并不会立刻导通,pwkey端持续输出高电平启动信号,此时外接电源首先为第一电容c1及第二电容c2充电,因为第一电容c1的充电时间(第一预设时间)小于第二电容c2的充电时间(第二预设时间),故第一电容c1率先完成充电,第一电容c1的电压率先达到第一开关q1的导通电压,第一开关q1导通,pwkey端持续输出低电平启动信号,之后,随着时间的推移,第二电容c2完成充电,第二电容c2的电压达到第二开关q2的导通电压,此时第二开关q2导通,第一开关q1的控制端电压被拉低,第一开关q1关断,pwkey端持续输出高电平。

41.进一步地,在第一电容c1完成充电、第二电容c2还未完成充电的时间内,即在第一开关q1导通、第二开关q2关断的时间内,pwkey端持续输出低电平启动信号,当该低电平启动信号的持续时间达到预设启动时间后,待启动设备启动,也就是说,待启动设备内部的芯片检测接收的低电平启动信号达到预设启动时间后,芯片启动。

42.需要说明的是,第二预设时间与第一预设时间的差值为第二电平启动信号的持续时间,通过调整第一预设时间、第二预设时间,调整第二电平启动信号的持续时间。

43.在一具体实施例中,第二延时电路2还包括:放电电路,该放电电路与第二电容c2并联连接。具体地,如图2所示,放电电路包括:第三电阻r3及二极管d,其中,二极管d的阴极通过第三电阻r3与第二电容c2的第一端连接,二极管d的阳极与第二电容c2的第二端连接。

44.具体地,若外接电源出现快速上电后断电,此时会由于外接电源通电时间短导致低电平启动信号的持续时间达不到预设启动时间,会导致自启动电路工作不正常,为了降低快速通断电导致自启动电路工作不正常的概率,本实用新型实施例设置放电电路,并使该放电电路与第二电容c2并联连接,从而当外接电源断电时,第二电容c2对外放电,通过二极管d的单向导通与第三电阻r3相连,形成一个环路进行快速放电。

45.进一步地,本实用新型实施例的放电电路的二极管d为肖特基二极管,利用肖特基二极管的单向导通性、快关频率高、正向压降低的特点来给第二电容c2放电。

46.显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引申出的显而易见的变化或变动仍处于本实用新型创造的保护范围之中。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。