1.本公开涉及光电传感器技术领域,尤其涉及一种硅光电倍增管及其制备方法。

背景技术:

2.硅光电倍增管(sipm)是具有光子数分辨能力的单光子探测器。与传统的光电倍增管(photomultiplier tube,pmt)相比,sipm工作于非真空环境因此不易损坏,sipm体积小、不受磁场影响、功耗低、单光子分辨能力强,这些优势使得sipm逐渐替代pmt成为具有广阔发展前景的单光子探测器,目前已广泛应用于天文物理、高能物理、激光雷达、核医学成像等方面。

3.然而,由于硅为间接带隙材料,对光的吸收较弱,特别是近红外波段效率较低,为提高sipm的光子探测效率,需要较厚的吸收层,这不可避免的提高的工作电压和使用成本。因此,如何在降低硅光电倍增管的工作电压的同时提高硅光电倍增管的光子探测效率成为人们关注的重点。

技术实现要素:

4.本公开旨在至少在一定程度上解决相关技术中的技术问题之一。

5.为此,本公开的第一个目的在于提出一种硅光电倍增管,可以在降低硅光电倍增管的工作电压的同时提高硅光电倍增管的光子探测效率。

6.本公开的第二个目的在于提出一种硅光电倍增管的制备方法。

7.为达到上述目的,本公开第一方面实施例提出的一种硅光电倍增管,包括:背电极、第一类型外延硅衬底、减反射层和电极,所述第一类型外延硅衬底包括第一类型硅衬底层、第一类型外延层和至少一个第二类型重掺杂区,其中,

8.所述第一类型硅衬底层设置于所述背电极的上表面,所述第一类型外延层设置于所述第一类型硅衬底层的上表面,所述至少一个第二类型重掺杂区设置于所述第一类型外延层的上表面,所述第一类型外延层和所述至少一个第二类型重掺杂区形成至少一个立体pn结;

9.在所述第二类型重掺杂区的上表面设置倒金字塔结构,所述第一类型外延硅衬底的上表面包括所述倒金字塔结构的上表面;

10.所述减反射层设置于所述第一类型外延硅衬底的上表面,且不完全覆盖所述第一类型外延硅衬底的上表面;

11.所述电极设置于所述减反射层不覆盖所述第一类型外延硅衬底的上表面的区域,且所述电极与所述第二类型重掺杂区连接;

12.其中,第一类型和第二类型分别为电子型和空穴型中的一种。

13.可选地,在本公开的一个实施例中,所述第二类型重掺杂区的上表面与所述第一类型外延层的上表面构成所述第一类型外延硅衬底的上表面,所述减反射层不完全覆盖所述第二类型重掺杂区的上表面,所述硅光电倍增管还包括:偏压电极和淬灭电极;其中,

14.所述淬灭电极设置于所述减反射层的上表面;

15.所述偏压电极设置于所述淬灭电极的上表面,所述偏压电极通过所述淬灭电极与所述电极连接。

16.可选地,在本公开的一个实施例中,所述倒金字塔结构的开口形状为正方形;

17.所述减反射层在所述倒金字塔结构的底部位置设置开口,所述开口的尺寸小于所述正方形的尺寸,不大于所述第二类型重掺杂区的区域尺寸。

18.可选地,在本公开的一个实施例中,所述硅光电倍增管还包括:第二类型重掺杂层;其中,

19.所述第二类型重掺杂层包括所述至少一个第二类型重掺杂区,所述第一类型外延层包括至少一个第一类型重掺杂区,所述第一类型重掺杂区设置于所述第二类型重掺杂区的下表面,所述至少一个第一类型重掺杂区和所述至少一个第二类型重掺杂区形成所述至少一个立体pn结;

20.所述第二类型重掺杂层的上表面为所述第一类型外延硅衬底的上表面,所述电极设置于所述第二类型重掺杂层中除第一类型重掺杂区之外的上表面,且所述电极通过所述第二类型重掺杂层与所述第二类型重掺杂区连接。

21.可选地,在本公开的一个实施例中,所述背电极包括第一金属层和至少一层第二金属层;其中,

22.所述第一金属层位于所述至少一层第二金属层的上表面,且与所述第一类型硅衬底层接触;

23.所述第一金属层的材料与所述第二金属层的材料不同。

24.可选地,在本公开的一个实施例中,所述电极包括第三金属层和第四金属层;其中,

25.所述第三金属层与所述第二类型重掺杂区连接,所述第四金属层通过所述第三金属层与所述第二类型重掺杂区连接;

26.所述第三金属层的材料与所述第四金属层的材料不同。

27.综上,本公开第一方面实施例提出的硅光电倍增管,包括:背电极、第一类型外延硅衬底、减反射层和电极,所述第一类型外延硅衬底包括第一类型硅衬底层、第一类型外延层和至少一个第二类型重掺杂区,其中,所述第一类型硅衬底层设置于所述背电极的上表面,所述第一类型外延层设置于所述第一类型硅衬底层的上表面,所述至少一个第二类型重掺杂区设置于所述第一类型外延层的上表面,所述第一类型外延层和所述至少一个第二类型重掺杂区形成至少一个立体pn结;在所述第二类型重掺杂区的上表面设置倒金字塔结构,所述第一类型外延硅衬底的上表面包括所述倒金字塔结构的上表面;所述减反射层设置于所述第一类型外延硅衬底的上表面,且不完全覆盖所述第一类型外延硅衬底的上表面;所述电极设置于所述减反射层不覆盖所述第一类型外延硅衬底的上表面的区域,且所述电极与所述第二类型重掺杂区连接;其中,第一类型和第二类型分别为电子型和空穴型中的一种。本公开通过引入倒金字塔结构并实现立体的第二类型重掺杂区,可以提高入射光的吸收率,可以提高硅光电倍增管的性能,从而可以提高硅光电倍增管的光电转换效率,进而可以在降低硅光电倍增管的工作电压的同时提高硅光电倍增管的光子探测效率。

28.为达到上述目的,本公开第二方面实施例提出的一种硅光电倍增管的制备方法,

包括:

29.选择第一类型外延硅衬底,并在所述第一类型外延硅衬底的上表面制备倒金字塔结构;

30.在所述第一类型外延硅衬底的上表面进行离子注入,形成第二类型重掺杂区;

31.在所述第一类型外延硅衬底的上表面制备减反射层;

32.对预设区域的减反射层进行腐蚀去除;

33.在减反射层进行腐蚀去除后形成的区域制备电极;

34.在所述第一类型外延硅衬底的下表面制备背电极。

35.可选地,在本公开的一个实施例中,所述在所述第一类型外延硅衬底的上表面制备倒金字塔结构,包括:

36.在所述第一类型外延硅衬底的上表面制备二氧化硅层;

37.在所述二氧化硅层中制作周期性正方形开口;

38.在所述第一类型外延硅衬底的下表面旋涂光刻胶,并放入硅腐蚀液中;

39.去除所述第一类型外延硅衬底下表面的光刻胶和上表面的氧化硅。

40.可选地,在本公开的一个实施例中,所述第一类型外延硅衬底的上表面进行离子注入,形成第二类型重掺杂区,包括:

41.在所述倒金字塔结构的底部进行离子注入,形成第二类型重掺杂区;

42.所述对预设区域的减反射层进行腐蚀去除;在减反射层进行腐蚀去除后形成的区域制备电极,包括:

43.在所述第一类型外延硅衬底的上表面的预设位置制备淬灭电阻;

44.对位于所述倒金字塔结构底部位置的减反射层进行腐蚀去除;

45.在减反射层进行腐蚀去除后形成的区域制备连接所述淬灭电阻和所述第二类型重掺杂区的电极,在所述淬灭电阻的上表面制备偏压电极。

46.可选地,在本公开的一个实施例中,所述在所述第一类型外延硅衬底的上表面进行离子注入,形成第二类型重掺杂区,包括:

47.在所述倒金字塔结构的下方进行离子深注入,形成第一类型重掺杂区;

48.在所述第一类型外延硅衬底的上表面进行离子浅注入,形成第二类型重掺杂层。

49.综上,本公开第二方面实施例提出的硅光电倍增管的制备方法,通过选择第一类型外延硅衬底,并在所述第一类型外延硅衬底的上表面制备倒金字塔结构;在所述第一类型外延硅衬底的上表面进行离子注入,形成第二类型重掺杂区;在所述第一类型外延硅衬底的上表面制备减反射层;对预设区域的减反射层进行腐蚀去除;在减反射层进行腐蚀去除后形成的区域制备电极;在所述第一类型外延硅衬底的下表面制备背电极。本公开通过引入倒金字塔结构并实现立体的第二类型重掺杂区,可以提高入射光的吸收率,可以提高硅光电倍增管的性能,从而可以提高硅光电倍增管的光电转换效率,进而可以在降低硅光电倍增管的工作电压的同时提高硅光电倍增管的光子探测效率。

50.本公开附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本公开的实践了解到。

附图说明

51.本公开上述的和/或附加的方面和优点从下面结合附图对实施例的描述中将变得明显和容易理解,其中:

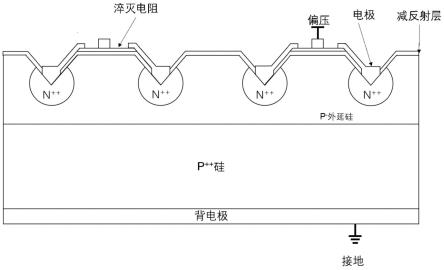

52.图1为本公开实施例所提供的第一种硅光电倍增管的截面示意图;

53.图2为本公开实施例所提供的第一种硅光电倍增管的工作原理图;

54.图3为本公开实施例所提供的立体pn结的截面示意图;

55.图4为本公开实施例所提供的第一种硅光电倍增管的俯视图;

56.图5为本公开实施例所提供的第二种硅光电倍增管的截面示意图;

57.图6为本公开实施例所提供的第二种硅光电倍增管的俯视图;

58.图7为本公开实施例提供的第一种硅光电倍增管的工艺流程示意图;

59.图8为本公开实施例提供的第二种硅光电倍增管的工艺流程示意图。

具体实施方式

60.下面详细描述本公开的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本公开,而不能理解为对本公开的限制。相反,本公开的实施例包括落入所附加权利要求书的精神和内涵范围内的所有变化、修改和等同物。

61.下面结合具体的实施例对本公开进行详细说明。

62.本公开实施例提供的一种硅光电倍增管,包括:背电极、第一类型外延硅衬底、减反射层和电极,第一类型外延硅衬底包括第一类型硅衬底层、第一类型外延层和至少一个第二类型重掺杂区,其中,

63.第一类型硅衬底层设置于背电极的上表面,第一类型外延层设置于第一类型硅衬底层的上表面,至少一个第二类型重掺杂区设置于第一类型外延层的上表面,第一类型外延层和至少一个第二类型重掺杂区形成至少一个立体pn结;

64.在第二类型重掺杂区的上表面设置倒金字塔结构,第一类型外延硅衬底的上表面包括倒金字塔结构的上表面;

65.减反射层设置于第一类型外延硅衬底的上表面,且不完全覆盖第一类型外延硅衬底的上表面;

66.电极设置于减反射层不覆盖第一类型外延硅衬底的上表面的区域,且电极与第二类型重掺杂区连接;

67.其中,第一类型和第二类型分别为电子型和空穴型中的一种。

68.根据一些实施例,当第一类型和第二类型分别为电子型和空穴型中的一种时,第一类型和第二类型可以不为相同类型,也就是说,第一类型为电子型时,第二类型为空穴型;第一类型为空穴型时,第二类型为电子型。

69.根据一些实施例,第一类型硅衬底并不特指某一固定衬底。例如,该第一类型硅衬底可以为(100)晶面的p型重掺杂p

硅。该第一类型硅衬底也可以为粗糙度《1nm的硅衬底。

70.在一些实施例中,第一类型外延层并不特指某一固定外延层。例如,该第一类型外延层可以为p型轻掺杂p-外延硅。该第一类型外延层的厚度可以为10-50微米。该第一类型

外延层的电阻率可以为10-1000ω.cm。

71.在一些实施例中,第二类型重掺杂区并不特指某一固定掺杂区。例如,该第二类型重掺杂区可以为n型重掺杂n

区。该第二类型重掺杂区的掺杂浓度可以为10

16-10

20

cm-3

。

72.在一些实施例中,减反射层并不特指某一固定减反射层。例如,该减反射层可以为氧化硅减反射层。该减反射层的厚度可以为10-500nm。

73.易于理解的是,本公开提供的硅光电倍增管,通过引入倒金字塔结构并实现立体的第二类型重掺杂区,可以提高光电转换效率,可以提高硅光电倍增管的光子探测效率,降低硅光电倍增管的工作电压,可以用于实现单光子级微弱光信号的探测,并有潜力成为激光雷达系统和近红外脑功能成像系统等需要弱光探测应用中必备的光传感器,可广泛用于激光雷达、近红外脑功能成像等需要极弱光探测的领域。

74.在本公开实施例中,第二类型重掺杂区的上表面与第一类型外延层的上表面构成第一类型外延硅衬底的上表面,减反射层不完全覆盖第二类型重掺杂区的上表面,硅光电倍增管还包括:偏压电极和淬灭电极;其中,

75.淬灭电极设置于减反射层的上表面;

76.偏压电极设置于淬灭电极的上表面,偏压电极通过淬灭电极与电极连接。

77.根据一些实施例,图1为本公开实施例所提供的第一种硅光电倍增管的截面示意图。如图1所示,第一类型为空穴型,第二类型为电子型,第一类型硅衬底层为p

硅,第一类型外延层为p-外延硅,第二类型重掺杂区为n

区,背电极接地。

78.在一些实施例中,电极和偏压电极的结构和使用的材料相同。偏压电极通过淬灭电极与电极连接时,如图1所示,部分电极与硅接触,部分电极不与硅接触。其中,和硅接触的部分电极的尺寸可以为1-5微米。和硅不接触的部分电极的宽度可以为1-3微米。

79.在一些实施例中,淬灭电阻的材料包括但不限于多晶硅、二氧化钛等。淬灭电阻的厚度可以为10-100nm。淬灭电阻的宽度可以为1-3微米。淬灭电阻的电阻大小可以为50-500kω。

80.在一些实施例中,图2为本公开实施例所提供的第一种硅光电倍增管的工作原理图。如图2所示,硅光电倍增管(sipm)由一系列工作于盖革模式的雪崩光电二极管(avalanche photodiode,apd)微单元并联而成,微单元间相互独立,每个微单元包括立体pn结和淬灭电阻,所有微单元通过公共的阳极和公共的阴极输出信号,信号大小正比于处于激发状态的微单元数目即正比于探测到的光子数。

81.在一些实施例中,图3为本公开实施例所提供的立体pn结的截面示意图。如图3所示,在返向偏压的作用下,p-外延硅的p-界面与n

区的n

界面之间会形成立体耗尽区,与传统的平面pn结结构相比,增加了耗尽区的体积,从而在不提高工作电压的条件下提高光子的探测效率。同时,设置在n

区上表面的倒金字塔结构还可以减少入射光的反射,从而进一步提高光的吸收效率。这种立体pn结结构与平面pn结结构相比,可以将光子探测效率提高2倍以上。

82.在本公开实施例中,根据一些实施例,图4为本公开实施例所提供的第一种硅光电倍增管的俯视图。如图4所示,倒金字塔结构的开口形状可以为正方形;

83.减反射层在倒金字塔结构的底部位置设置开口,开口的尺寸小于正方形的尺寸,不大于第二类型重掺杂区的区域尺寸。

84.根据一些实施例,倒金字塔结构的开口的正方形的边长可以为1-8微米。减反射层在倒金字塔结构的底部位置设置的开口的尺寸可以为0.5-5微米。第二类型重掺杂区的区域尺寸可以为1-8微米。

85.在一些实施例中,如图4所示,一个倒金字塔结构对应一个立体pn结,每个立体pn结上设置的电极可以通过其对应的淬灭电阻连接至同一个偏压电极。

86.在本公开实施例中,硅光电倍增管还包括:第二类型重掺杂层;其中,

87.第二类型重掺杂层包括至少一个第二类型重掺杂区,第一类型外延层包括至少一个第一类型重掺杂区,第一类型重掺杂区设置于第二类型重掺杂区的下表面,至少一个第一类型重掺杂区和至少一个第二类型重掺杂区形成至少一个立体pn结;

88.第二类型重掺杂层的上表面为第一类型外延硅衬底的上表面,电极设置于第二类型重掺杂层中除第一类型重掺杂区之外的上表面,且电极通过第二类型重掺杂层与第二类型重掺杂区连接。

89.根据一些实施例,图5为本公开实施例所提供的第二种硅光电倍增管的截面示意图。如图5所示,第一类型为空穴型,第二类型为电子型,第一类型硅衬底层为p

硅,第一类型外延层为p-外延硅,第二类型重掺杂层为n

层,n

层包括至少一个n

区,第二类型重掺杂区为p

区,其中,位于p

区上表面的n

层为n

区。p

区的p

界面与n

区的n

界面之间会形成立体pn结。背电极接地。

90.在一些实施例中,p

硅的掺杂浓度高于p

区的掺杂浓度。

91.在一些实施例中,图6为本公开实施例所提供的第二种硅光电倍增管的俯视图。如图6所示,倒金字塔结构的开口形状可以为圆形。电极可以环绕设置于n

层上表面的四周。

92.在本公开实施例中,背电极包括第一金属层和至少一层第二金属层;其中,

93.第一金属层位于至少一层第二金属层的上表面,且与第一类型硅衬底层接触;

94.第一金属层的材料与第二金属层的材料不同。

95.根据一些实施例,第一金属层的材料包括但不限于钛、铬等金属。第一金属层的厚度可以为1-10nm。

96.根据一些实施例,第二金属层的材料包括但不限于金、铝、铜等金属。第二金属层的厚度可以为100nm-2000nm。第二金属层的厚度也可以为50-200nm。

97.例如,背电极包括第一金属层和两层第二金属层。其中,第一层第二金属层位于第二层第二金属层的上表面。第一层第二金属层的材料包括但不限于钛、铬等金属,第一层第二金属层的厚度为100nm-2000nm。第二层第二金属层的材料为金,第二层第二金属层的厚度为50-200nm。

98.在本公开实施例中,电极包括第三金属层和第四金属层;其中,

99.第三金属层与第二类型重掺杂区连接,第四金属层通过第三金属层与第二类型重掺杂区连接;

100.第三金属层的材料与第四金属层的材料不同。

101.根据一些实施例,第三金属层的材料包括但不限于钛、铬等金属。第三金属层的厚度可以为1-10nm。该第三金属层可以直接与第二类型重掺杂区连接,如图1所示。该第三金属层也可以通过第二类型重掺杂层与第二类型重掺杂区连接,如图5所示。

102.在一些实施例中,第四金属层的材料包括但不限于金等金属。第四金属层的厚度

可以为50nm-300nm。

103.综上,本公开实施例提出的硅光电倍增管,包括:背电极、第一类型外延硅衬底、减反射层和电极,第一类型外延硅衬底包括第一类型硅衬底层、第一类型外延层和至少一个第二类型重掺杂区,其中,第一类型硅衬底层设置于背电极的上表面,第一类型外延层设置于第一类型硅衬底层的上表面,至少一个第二类型重掺杂区设置于第一类型外延层的上表面,第一类型外延层和至少一个第二类型重掺杂区形成至少一个立体pn结;在第二类型重掺杂区的上表面设置倒金字塔结构,第一类型外延硅衬底的上表面包括倒金字塔结构的上表面;减反射层设置于第一类型外延硅衬底的上表面,且不完全覆盖第一类型外延硅衬底的上表面;电极设置于减反射层不覆盖第一类型外延硅衬底的上表面的区域,且电极与第二类型重掺杂区连接;其中,第一类型和第二类型分别为电子型和空穴型中的一种。本公开通过引入倒金字塔结构并实现立体的第二类型重掺杂区,可以提高入射光的吸收率,可以提高硅光电倍增管的性能,从而可以提高硅光电倍增管的光电转换效率,进而可以在降低硅光电倍增管的工作电压的同时提高硅光电倍增管的光子探测效率。

104.为了实现上述实施例,本公开还提出一种硅光电倍增管的制备方法,包括:

105.s101,选择第一类型外延硅衬底,并在第一类型外延硅衬底的上表面制备倒金字塔结构;

106.s102,在第一类型外延硅衬底的上表面进行离子注入,形成第二类型重掺杂区;

107.s103,在第一类型外延硅衬底的上表面制备减反射层;

108.s104,对预设区域的减反射层进行腐蚀去除;

109.s105,在减反射层进行腐蚀去除后形成的区域制备电极;

110.s106,在第一类型外延硅衬底的下表面制备背电极。

111.根据一些实施例,在第一类型外延硅衬底的上表面制备倒金字塔结构之前,还需要对第一类型外延硅衬底进行清洁处理。

112.在本公开实施例中,在第一类型外延硅衬底的上表面制备倒金字塔结构,包括:

113.在第一类型外延硅衬底的上表面制备二氧化硅层;

114.在二氧化硅层中制作周期性正方形开口;

115.在第一类型外延硅衬底的下表面旋涂光刻胶,并放入硅腐蚀液中;

116.去除第一类型外延硅衬底下表面的光刻胶和上表面的氧化硅。

117.在本公开实施例中,第一类型外延硅衬底的上表面进行离子注入,形成第二类型重掺杂区,包括:

118.在倒金字塔结构的底部进行离子注入,形成第二类型重掺杂区;

119.对预设区域的减反射层进行腐蚀去除;在减反射层进行腐蚀去除后形成的区域制备电极,包括:

120.在第一类型外延硅衬底的上表面的预设位置制备淬灭电阻;

121.对位于倒金字塔结构底部位置的减反射层进行腐蚀去除;

122.在减反射层进行腐蚀去除后形成的区域制备连接淬灭电阻和第二类型重掺杂区的电极,在淬灭电阻的上表面制备偏压电极。

123.以一个场景举例,图7为本公开实施例提供的第一种硅光电倍增管的工艺流程示意图。如图7所示,该工艺流程包括以下步骤:

124.s201,选择晶体表面为(100)晶面的第一类型外延硅衬底,并对其进行清洁处理;

125.其中,该第一类型外延硅衬底中,第一类型硅衬底层为p

硅,该p

硅的电阻率为0.001ω.cm;该第一类型外延硅衬底中,第一类型外延层为p-掺杂硅,该p-掺杂硅的厚度为30微米,该p-掺杂硅的电阻率为100ω.cm。

126.s202,在第一类型外延硅衬底的上表面通过等离子体增强化学的气相沉积法制备一层二氧化硅层,该二氧化硅层的厚度为300nm;

127.根据一些实施例,等离子体增强化学的气相沉积法(plasma enhanced chemical vapor deposition,pecvd)是指借助微波或射频等使含有薄膜成分原子的气体电离,在局部形成等离子体,而等离子体化学活性很强,很容易发生反应,在基片上沉积出所期望的薄膜的方法。为了使化学反应能在较低的温度下进行,pecvd利用了等离子体的活性来促进反应,因而这种气相沉积法称为等离子体增强化学气相沉积。

128.s203,在二氧化硅层中制作周期性正方形开口,该正方形开口的边长为4微米;

129.s204,在第一类型外延硅衬底的背面旋涂光刻胶,将硅片(旋涂光刻胶后的第一类型外延硅衬底)放入硅腐蚀液中,第一类型外延硅衬底的表面硅裸露位置的硅由于各项异性腐蚀,可行成倒金字塔结构;

130.s205,去除第一类型外延硅衬底背面的光刻胶和正面的二氧化硅;

131.s206,在倒金字塔结构底部进行离子注入,形成n

掺杂区,n

掺杂区的掺杂浓度为10

19

cm-3

,n

掺杂区的区域尺寸为3微米,接着快速退火激活掺杂离子;

132.s207,在第一类型外延硅衬底的表面通过pecvd制备氧化硅减反射层,该氧化硅减反射层的厚度为150nm;

133.s208,在氧化硅减反射层上表面的特定位置制备多晶硅淬灭电阻,厚度为20nm,宽度为3微米,电阻大小为200kω。

134.根据一些实施例,在氧化硅减反射层上表面的特定位置制备多晶硅淬灭电阻时,该特定位置为立体pn结对应的电极连接偏压电极的一侧。

135.s209,将倒金字塔结构底部位置的氧化硅减反射层腐蚀去除,腐蚀去除后形成的开口尺寸为2微米;

136.s210,制作偏压电极和与n

硅接触的电极,分别于淬灭电阻的两端连接;

137.根据一些实施例,偏压电极和电极均为二层金属结构,与n

区硅接触的金属为钛金属,厚度为2nm;不与n

区硅接触的金属为金,厚度为100nm,尺寸为2微米。

138.s211,在第一类型外延硅衬底的背面制作背电极。

139.根据一些实施例,背电极为三层金属结构,与硅接触的金属为钛、铬金属,厚度为10nm;第二层金属为铝,厚度为1000nm,第三层金属为金,厚度为100nm。

140.在本公开实施例中,在第一类型外延硅衬底的上表面进行离子注入,形成第二类型重掺杂区,包括:

141.在倒金字塔结构的下方进行离子深注入,形成第一类型重掺杂区;

142.在第一类型外延硅衬底的上表面进行离子浅注入,形成第二类型重掺杂层。

143.以一个场景举例,图8为本公开实施例提供的第二种硅光电倍增管的工艺流程示意图。如图8所示,该工艺流程包括以下步骤:

144.s301,选择第一类型外延硅衬底,并对其进行清洁处理;

145.其中,该第一类型外延硅衬底中,第一类型硅衬底层为p

硅,第一类型外延层为p-掺杂硅。

146.s302,在第一类型外延硅衬底的上表面制备二氧化硅层(介质薄膜);

147.s303,在二氧化硅层中制作周期性圆形开口;

148.s304,在第一类型外延硅衬底的底面旋涂光刻胶,将硅片放入硅腐蚀液中,第一类型外延硅衬底的表面硅裸露位置的硅由于各项异性腐蚀,可行成倒金字塔结构;

149.s305,在倒金字塔结构底部进行p

离子深注入,形成p

层;

150.s306,对二氧化硅层(介质薄膜)进行腐蚀,并去除背电极的底面旋涂的光刻胶;

151.s307,在第一类型外延硅衬底的上表面进行n

离子浅注入,形成n

层;

152.s308,在n

层的上表面制备氧化硅减反射层;

153.s309,在氧化硅减反射层中进行腐蚀开窗;

154.s310,在氧化硅减反射层进行腐蚀开窗后形成的区域中制备电极;

155.s311,在第一类型外延硅衬底的背面制作背电极。

156.综上,本公开实施例提出的硅光电倍增管的制备方法,通过选择第一类型外延硅衬底,并在第一类型外延硅衬底的上表面制备倒金字塔结构;在第一类型外延硅衬底的上表面进行离子注入,形成第二类型重掺杂区;在第一类型外延硅衬底的上表面制备减反射层;对预设区域的减反射层进行腐蚀去除;在减反射层进行腐蚀去除后形成的区域制备电极;在第一类型外延硅衬底的下表面制备背电极。本公开通过引入倒金字塔结构并实现立体的第二类型重掺杂区,可以提高入射光的吸收率,可以提高硅光电倍增管的性能,从而可以提高硅光电倍增管的光电转换效率,进而可以在降低硅光电倍增管的工作电压的同时提高硅光电倍增管的光子探测效率。

157.需要说明的是,在本公开的描述中,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性。此外,在本公开的描述中,除非另有说明,“多个”的含义是两个或两个以上。

158.流程图中或在此以其他方式描述的任何过程或方法描述可以被理解为,表示包括一个或更多个用于实现特定逻辑功能或过程的步骤的可执行指令的代码的模块、片段或部分,并且本公开的优选实施方式的范围包括另外的实现,其中可以不按所示出或讨论的顺序,包括根据所涉及的功能按基本同时的方式或按相反的顺序,来执行功能,这应被本公开的实施例所属技术领域的技术人员所理解。

159.应当理解,本公开的各部分可以用硬件、软件、固件或它们的组合来实现。在上述实施方式中,多个步骤或方法可以用存储在存储器中且由合适的指令执行系统执行的软件或固件来实现。例如,如果用硬件来实现,和在另一实施方式中一样,可用本领域公知的下列技术中的任一项或他们的组合来实现:具有用于对数据信号实现逻辑功能的逻辑门电路的离散逻辑电路,具有合适的组合逻辑门电路的专用集成电路,可编程门阵列(pga),现场可编程门阵列(fpga)等。

160.本技术领域的普通技术人员可以理解实现上述实施例方法携带的全部或部分步骤是可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,该程序在执行时,包括方法实施例的步骤之一或其组合。

161.此外,在本公开各个实施例中的各功能单元可以集成在一个处理模块中,也可以

是各个单元单独物理存在,也可以两个或两个以上单元集成在一个模块中。上述集成的模块既可以采用硬件的形式实现,也可以采用软件功能模块的形式实现。所述集成的模块如果以软件功能模块的形式实现并作为独立的产品销售或使用时,也可以存储在一个计算机可读取存储介质中。

162.上述提到的存储介质可以是只读存储器,磁盘或光盘等。

163.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本公开的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

164.尽管上面已经示出和描述了本公开的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本公开的限制,本领域的普通技术人员在本公开的范围内可以对上述实施例进行变化、修改、替换和变型。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。