一种沟槽型mosfet及其制造方法

技术领域

1.本技术涉及半导体技术领域,特别涉及一种沟槽型mosfet及其制造方法。

背景技术:

2.沟槽mosfet(metal oxide semiconductor field effect transistor,金属氧化物半导体场效应晶体管)具有输入阻抗高,驱动电流小,开关速度快,高温特性好等优点被广泛应用于电力电子领域。

3.一般的沟槽型mosfet中,相互分离的栅极导体之间经由介质层隔离。介质层通常采化学气相沉积工艺以及化学机械抛光工艺形成。但是由于沟槽的关键尺寸较小,化学气相沉积工艺对填充性的要求较高,使得介质层的形成较为困难。

技术实现要素:

4.鉴于上述问题,本技术的目的在于提供一种沟槽型mosfet及其制造方法,在沟槽的中部依次形成第二介质层和层间介质层,第二介质层将层间介质层与第一介质层、第一导体以及外延层隔离,防止形成层间介质层的过程中对第一导体和外延层被氧化,从而导致第一导体和外延层的形状以及性能发生改变。

5.本技术第一方面提供一种沟槽型mosfet的制造方法,包括:形成从第一掺杂类型的外延层的上表面延伸至其内部的沟槽;形成位于沟槽下部的第一介质层以及第一导体,其中,第一介质层覆盖沟槽下部的内表面,用以将第一导体与外延层隔离;形成位于沟槽中部的第二介质层以及层间介质层,第二介质层覆盖第一介质层和第一导体的表面以及沟槽中部的内表面,第二介质层将层间介质层与第一介质层、第一导体以及外延层隔离;以及形成位于沟槽上部的第三介质层以及第二导体,第三介质层覆盖沟槽上部的内表面,第三介质层将第二导体与外延层隔离。

6.本技术第二方面提供一种沟槽型mosfet,其中,包括:第一掺杂类型的外延层;从第一掺杂类型的外延层的上表面延伸至其内部的沟槽;位于沟槽下部的第一介质层以及第一导体,第一介质层覆盖沟槽下部的内表面,用以将第一导体与外延层隔离;位于沟槽中部的第二介质层以及层间介质层,第二介质层覆盖第一介质层和第一导体的表面以及沟槽中部的内表面,第二介质层将层间介质层与第一介质层、第一导体以及外延层隔离;以及位于沟槽上部的第三介质层以及第二导体,第三介质层覆盖沟槽上部的内表面,第三介质层将第二导体与外延层隔离。

附图说明

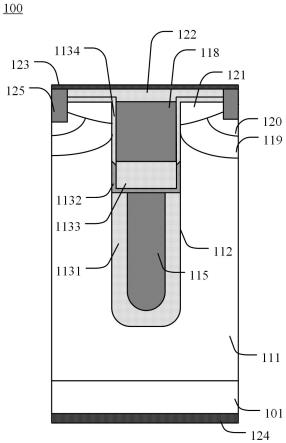

7.通过以下参照附图对本技术实施例的描述,本技术的上述以及其他目的、特征和优点将更为清楚:图1示出了根据本技术实施例的沟槽型mosfet的截面图;图2a至图2k示出了本技术实施例的沟槽型mosfet器件的制造方法的各阶段截面图。

具体实施方式

8.以下在各个附图中,相同的元件采用类似的附图标记表示。为了清楚起见,附图中的各个部分没有按比例绘制。此外,可能未示出某些公知的部分。为了简明起见,可以在一幅图中描述经过数个步骤后获得的半导体结构。

9.在描述器件的结构时,当将一层、一个区域称为位于另一层、另一个区域“上面”或“上方”时,可以指直接位于另一层、另一个区域上面,或者在其与另一层、另一个区域之间还包含其它的层或区域。并且,如果将器件翻转,该一层、一个区域将位于另一层、另一区域“下面”或“下方”。

10.如果为了描述直接位于另一层、另一区域上面的情形,本文将采用“直接在

……

上面”或“在

……

上面并与之邻接”的表述方式。

11.除非在下文中特别指出,半导体器件的各个部分可以由本领域的技术人员公知的材料构成。半导体材料例如包括iii-v族半导体,如砷化镓(gaas)、氮化镓(gan)等,iv-iv族半导体,如碳化硅(sic)等,ii-vi族化合物半导体,如硫化镉(cds)、碲化镉(cdte)等,以及iv族半导体,如硅(si)、锗(ge)等。栅极导体可以由能够导电的各种材料形成,例如金属层、掺杂多晶硅层、或包括金属层和掺杂多晶硅层的叠层栅极导体或者是其他导电材料,例如为tac、tin、tasin、hfsin、tisin、ticn、taalc、tialn、tan、ptsix、ni3si、pt、ru、w、和各种导电材料的组合。栅极电介质可以由sio2或介电常数大于sio2的材料构成,例如包括氧化物、氮化物、氮氧化物、硅酸盐、铝酸盐、钛酸盐。并且,栅极电介质不仅可以由本领域的技术人员公知的材料形成,也可以采用将来开发的用于栅极电介质的材料。

12.图1示为本技术实施例的沟槽型mosfet的截面图。本技术中,第一掺杂类型是n型和p型中的一种,第二掺杂类型是n型和p型中的另一种。在半导体层中注入n型掺杂剂,例如p、as,可以形成n型半导体层。在半导体层中掺入p型掺杂剂,例如b,可以形成p型半导体层。

13.沟槽型mosfet 100包括衬底101和位于其上的外延层111,衬底101为第一掺杂类型,于一实施例中为n型重掺杂。外延层111位于衬底101的第一表面上,外延层111相对于衬底101是轻掺杂。在衬底101的第二表面上形成漏极电极124。

14.沟槽型mosfet 100包括从外延层111的上表面延伸进入其内部的沟槽112;位于沟槽112内部的介质层和电极导体;位于外延层111并与沟槽112相邻的体区119,其中体区119为第二掺杂类型。沟槽112从外延层111的上表面延伸至其内部,终止于外延层111中。

15.沟槽112内的介质层包括第一介质层1131、第二介质层1132、层间介质层1133以及第三介质层1134。电极导体包括第一导体115和第二导体118。第一介质层1131覆盖沟槽112下部的内表面,第一导体115位于第一介质层1131围绕沟槽下部形成的空腔内。第一导体115与外延层111由第一介质层1131隔离。第二介质层1132覆盖第一导体115和第一介质层

1131的上表面以及沟槽112中部的内表面。层间介质层1133位于第二介质层1132围绕沟槽112中部的形成的空腔内。第三介质层1134覆盖沟槽上部的内表面,第二导体118位于层间介质层1133上方,且侧壁经由第三介质层1134与外延层111隔离。

16.在本实施例中,第一导体115为屏蔽导体,第二导体118为栅极导体,第三介质层1134为栅介质层,层间介质层1133将屏蔽导体和栅极导体隔离。

17.沟槽型mosfet 100包括在体区119中形成第一掺杂类型的源区121;在体区119中形成第二掺杂类型的体接触区120;在源区121和栅极导体118上方形成的第四介质层122;在紧邻源区121处形成穿透第四介质层122以及源区121到达体接触区120的导电通道125;在第四介质层122上方形成的源极电极123,源极电极123经由导电通道125连接至体接触区120。其中,第四介质层122可以是具有一定厚度的氧化物层,例如,氧化硅。

18.本实施例中,层间介质层1133通过沉积多晶硅层,并由多晶硅氧化形成,防止在层间介质层中产生空隙,改善了器件的机械强度和电学性能。相较于一般通过hpd-cvd工艺以及cmp工艺形成第三介质层,本实施例中形成第三介质层的制造工艺更为简化。

19.在将多晶硅氧化形成层间介质层1133的过程中,第二介质层1132可以将多晶硅层与外延层111以及将多晶硅层与第一导体115隔离,防止多晶硅氧化形成层间介质层1133的过程中对第一导体115以及外延体层111造成影响,于一实施例中,第二介质层1132可以为氮化硅。

20.第二介质层1132的厚度小于第一介质层1131的厚度,以在沟槽内形成较大的空腔,使得多晶硅层在氧化的过程中,氧气具有足够的空间与多晶硅层接触,使多晶硅层能够充分地氧化,防止多晶硅层的氧化不充分,造成第一导体和115第二导体118之间的绝缘隔离失效。

21.在一实施例中,第二介质层1132的厚度例如为200埃~300埃,小于第一介质层1131的厚度。

22.图2a至图2g示出了本技术实施例的沟槽型mosfet器件的制造方法的各阶段截面图。

23.如图2a所示,在衬底101上形成外延层111,并且在外延层111中形成沟槽112。

24.该步骤中,在半导体衬底101上形成外延层111,衬底101作为器件的漏区,具有第一掺杂类型。在一实施例中,衬底101的材料可以为掺杂成n型的单晶硅衬底。

25.在外延层111的上表面形成图案化的掩膜pr,并经由掩膜pr在外延层111中形成沟槽112。

26.该步骤中,例如采用沉积工艺形成掩膜pr,采用光刻形成包括沟槽112的开口的图案化掩模pr,然后对没有掩膜pr覆盖的外延层111进行刻蚀,以在外延层111中形成沟槽112。于一实施例中,刻蚀可以采用干法刻蚀,例如离子铣刻蚀、等离子刻蚀、反应离子刻蚀、激光烧蚀,或者使用湿法刻蚀。在一实施例中,掩膜pr可以为光致抗蚀剂掩膜,在形成沟槽112后,去除掩膜pr。

27.如图2b所示,在沟槽112中依次形成第一介质层1131和多晶硅层1141。

28.于一实施例中,通过热氧化或化学气相沉积的方式,在沟槽112的内部以及外延层111的上表面形成第一介质层1131,即第一介质层1131覆盖沟槽112的底部,侧壁,以及外延层111的上表面。于一实施例中,第一介质层1131可以由氧化物或者氮化物组成,例如,氧化

硅或者氮化硅。热氧化包括水热氧化hto或选择性反应氧化sro(selective reactive oxidation),化学气相沉积cvd包括低压化学气相沉积lpcvd或次大气压化学气相沉积sacvd。

29.通过低压化学气相沉积的方式,在沟槽112的内部以及外延层111的上方的第一介质层1131的表面形成多晶硅层1141。第一介质层1131将多晶硅层1141与外延层111隔离。

30.如图2c所示,对第一介质层1131和多晶硅层1141进行回蚀刻。

31.该步骤中,对多晶硅层1141进行化学机械研磨,然后回刻蚀多晶硅层1141,使得外延层111上方的第一介质层1131的表面以及沟槽112上部的多晶硅层1141去除,剩余的多晶硅层1141部分成为第一导体115。于一实施例中,回刻蚀可采用干法刻蚀。

32.采用刻蚀工艺,刻蚀第一介质层1131,去除位于外延层111上表面以及沟槽112上部的第一介质层1131,使得第一介质层1131位于沟槽112侧壁与第一导体115之间,并且第一介质层1131未覆盖第一导体115的顶部。第一介质层1131的表面低于第一导体115的表面;于一实施例中,该刻蚀工艺可以是湿法刻蚀,用以在较为平整的膜面上刻出绒面,从而增加光程,减少光的反射,湿法刻蚀可用稀释的hf或boe(buffered-oxide-etch,缓冲氧化物刻蚀液)等。

33.如图2d所示,在第一介质层1131的上表面、第一导体115的上表面、沟槽112的上部和外延层111的上表面形成第二介质层1132。

34.该步骤中,采用沉积工艺形成第二介质层1132,其中,第二介质层1132覆盖第一介质层1131的上表面、第一导体115的上表面、沟槽112的上部和外延层111的上表面,第二介质层1132围绕沟槽112的上部形成空腔。

35.本实施例中,第二介质层1132例如为氮化硅层,第二介质层1132将后续形成的多晶硅层1142与第一导体231以及多晶硅层1142与外延层111进行隔离,防止后续多晶硅层1142氧化的过程中,第一导体115和外延层111被氧化,从而导致第一导体115和外延层111的形状以及性能发生改变。

36.第二介质层1132的厚度小于第一介质层1131的厚度,以防止占用沟槽112过多的空间,使得在后续多晶硅层1142氧化的过程中,氧气具有足够的空间与多晶硅层1142接触,防止多晶硅层1142氧化不充分,而造成第一导体115和第二导体118之间的绝缘隔离失效。

37.在一实施例中,第二介质层1132的厚度例如为200埃~300埃,小于第一介质层1131的厚度。

38.如图2e所示,在第二介质层1132围绕沟槽112的上部形成的空腔内形成多晶硅层1142。

39.该步骤中,例如采用淀积工艺形成多晶硅层1142,将多晶硅层1142填充至由第二介质层1132围绕沟槽112上部所形成的空腔,以及外延层111上方的第二介质层1132的表面。对多晶硅层1142进行刻蚀,去除外延层111上方的多晶硅层1142以及部分沟槽112内部的多晶硅层1142,使得剩余的多晶硅层1142位于所沟槽112的中部。

40.如图2f所示,对剩余的多晶硅层1142进行氧化层,形成层间介质层1133。

41.该步骤中,通过对多晶硅层1142进行氧化的方式形成层间介质层1133,相较于通过高密度等离子体化学气相沉积(high density plasma chemical vapor deposition,hpd-cvd)工艺以及化学机械抛光(chemical mechanical polishing,cmp)工艺形成层间介

质层的方式,本实施例形成层间介质层的方式更加简化工艺流程。

42.如图2g所示,对第二介质层1132进行刻蚀。

43.该步骤中,对外延层111的上表面的第二介质层1132以及沟槽112上部侧壁的部分第二介质层1132进行刻蚀,保留位于沟槽112中部的内表面以及位于第一导体115和第一介质层1131上表面的第二介质层1132。借由第二介质层1132将层间介质层1133的侧壁与沟槽112的侧壁隔离。于一实施例中,第二介质层1132的上表面与层间介质层1133的表面齐平,或者第二介质层1132的上表面低于层间介质层1133的表面。

44.如图2h和图2i所示,形成第三介质层1134以及第二导体118。

45.该步骤中,例如采用热氧化技术,形成位于第二介质层1132和层间介质层1133上的沟槽侧壁以及外延层111的上表面的氧化层,该氧化层为栅极介质层1134,沟槽112侧壁被栅极介质层1134覆盖。热氧化技术一般为硅与含有氧化物质的气体,例如水汽和氧气,在高温下进行化学反应,而在硅片表面产生一层致密的二氧化硅(sio2)薄膜。

46.采用低压化学气相沉积的方式,在覆盖有栅极介质层1134的沟槽112中填充多晶硅层1143,多晶硅层1143包括位于沟槽112的第一部分1143a和位于外延层111上方的第二部分1143b。接着采用回刻蚀或化学机械平面化,去除多晶硅层1143位于外延层111上方的第二部分1143b,使得多晶硅层1143的上端终止于沟槽的开口处,并且多晶硅层1143的上表面与外延层111的上表面齐平,形成第二导体118。

47.层间介质层1133使得第一导体115以及第二导体118彼此绝缘,并且层间介质层1133具有一定的质量和厚度支持可能存在于第一导体115以及第二导体118之间的电势差。

48.如图2j所示,在外延层111邻近沟槽112的区域中形成体区119以及源区121。

49.体区119为第二掺杂类型,其中第二掺杂类型与第一掺杂类型相反。进行第一次离子注入,形成在外延层111邻近沟槽112中的体区119。进行第二次离子注入,在体区119中形成第一掺杂类型的源区121。通过控制离子注入的参数,例如注入能量和剂量,可以达到所需要的深度和获得所需的掺杂浓度,体区119的深度不超过栅极导体118在沟槽112中的延伸深度。采用光致抗蚀剂掩模,可以控制体区119和源区121的横向延伸区域。体区119和源区121分别与沟槽112相邻接,由第三介质层1134与第二导体118之间隔离。

50.如图2k所示,形成位于源区121上方的第四介质层122。

51.通过沉积工艺,形成位于源区121上方的第四介质层122,进一步进行化学机械平面化,以获得平整的表面。第四介质层122覆盖源区121和第二导体118的顶部表面,第三介质层1134位于外延层111的第一表面的部分可以在形成源区121后以刻蚀的方式去除,也可以不去除,与第四介质层122共形,位于源区121 的上方。

52.通过刻蚀工艺及离子注入工艺,在体区119中形成第二掺杂类型的体接触区120,通过刻蚀工艺,形成穿透第四介质层122以及源区121到达体接触区120的导电通道125,以及在第四介质层122上方形成源极电极123,源极电极123经由导电通道125连接至体接触区120。通过沉积工艺,在衬底101的第二表面上形成漏极电极124,得到如图1所示的沟槽型mosfet 100。

53.本技术中,源极电极123、第二导体(栅极导体)118、第一导体(屏蔽导体)114、以及漏极电极124可以分别由导电材料形成,于一实施例中,可以是铝合金或铜之类的金属材料。

54.本技术提供的沟槽型mosfet及其制造方法,层间介质层通过沉积多晶硅层,以及多晶硅氧化形成,防止在层间介质层中产生空隙,改善了器件的机械强度和电学性能;相较于一般通过复杂的hpd-cvd工艺以及cmp工艺形成第三介质层,本技术形成第三介质层的制作工艺流程更加简化。

55.依照本技术的实施例如上文所述,这些实施例并没有详尽叙述所有的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述,可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了更好地解释本技术的原理和实际应用,从而使所属技术领域技术人员能很好地利用本技术以及在本技术基础上的修改使用。本技术仅受权利要求书及其全部范围和等效物的限制。

再多了解一些

本文用于创业者技术爱好者查询,仅供学习研究,如用于商业用途,请联系技术所有人。