1.本技术对应于在2020年2月7日向日本专利局提交的日本特愿2020-020082号,该申请的全部公开通过引用并入于此。

2.本发明涉及一种半导体装置。

背景技术:

3.专利文献1公开了包含半导体芯片、第一槽构造以及第二槽构造的半导体装置。第一槽构造包含第一槽和第一绝缘膜。第一槽形成于半导体芯片的主面,将该主面划分为活性区及非活性区。第一绝缘膜形成于第一槽的壁面。第二槽构造包含第二槽、第二绝缘膜和第三绝缘膜。第二槽从第一槽起隔开间隔地形成于活性区的主面。第二绝缘膜覆盖第二槽的上壁面,且形成得比第一绝缘膜薄。第三绝缘膜覆盖第二槽的下壁面,且形成得比第二绝缘膜厚。

4.现有技术文献

5.专利文献

6.专利文献1:日本特表2013-508980号公报

技术实现要素:

7.发明要解决的课题

8.在第一槽内的构造及第二槽内的构造不同时,可能在半导体芯片中在第一槽及第二槽之间的区域产生应力而形成结晶缺陷。本发明的一实施方式提供一种能够抑制半导体芯片的结晶缺陷的半导体装置。

9.用于解决课题的手段

10.本发明的一实施方式提供一种半导体装置,包含:半导体芯片,其具有主面;第一槽,其形成于所述主面,将所述主面划分为第一区域和第二区域;第一绝缘膜,其形成于所述第一槽的壁面;第二槽,其从所述第一槽起隔开间隔地形成于所述第一区域的所述主面;第二绝缘膜,其覆盖所述第二槽的上壁面,且比所述第一绝缘膜薄;第三绝缘膜,其覆盖所述第二槽的下壁面,且比所述第二绝缘膜厚;第三槽,其从所述第一槽起隔开间隔地形成于所述第二区域的所述主面;第四绝缘膜,其覆盖所述第三槽的上壁面,且比所述第一绝缘膜薄;以及第五绝缘膜,其覆盖所述第三槽的下壁面,且比所述第四绝缘膜厚。

11.本发明的一实施方式提供一种半导体装置,包含:半导体芯片,其具有主面;场沟槽构造,其形成于所述主面,并在所述主面划分活性区和非活性区;沟槽栅极构造,其从所述场沟槽构造起隔开间隔地形成于所述活性区,并与所述场沟槽构造对置;以及伪沟槽构造,其从所述场沟槽构造起隔开间隔地形成于所述非活性区,并隔着所述场沟槽构造与所述沟槽栅极构造对置。

12.本发明中的上述或者其他目的、特征以及效果,参照附图通过下述实施方式的说明而变得明确。

附图说明

13.图1是表示本发明的第一实施方式的半导体装置的俯视图。

14.图2是表示图1所示的半导体芯片的第一主面的构造的俯视图。

15.图3是图2所示的区域iii的放大图。

16.图4是沿着图3所示的iv-iv线的剖视图。

17.图5是沿着图3所示的v-v线的剖视图。

18.图6是沿着图3所示的vi-vi线的剖视图。

19.图7是图2所示的区域vii的放大图。

20.图8a是用于对图1所示的半导体装置的制造方法的一例进行说明的剖视图。

21.图8b是表示图8a之后的工序的剖视图。

22.图8c是表示图8b之后的工序的剖视图。

23.图8d是表示图8c之后的工序的剖视图。

24.图8e是表示图8d之后的工序的剖视图。

25.图8f是表示图8e之后的工序的剖视图。

26.图8g是表示图8f之后的工序的剖视图。

27.图8h是表示图8g之后的工序的剖视图。

28.图8i是表示图8h之后的工序的剖视图。

29.图8j是表示图8i之后的工序的剖视图。

30.图8k是表示图8j之后的工序的剖视图。

31.图8l是表示图8k之后的工序的剖视图。

32.图8m是表示图8l之后的工序的剖视图。

33.图8n是表示图8m之后的工序的剖视图。

34.图8o是表示图8n之后的工序的剖视图。

35.图8p是表示图8o之后的工序的剖视图。

36.图8q是表示图8p之后的工序的剖视图。

37.图8r是表示图8q之后的工序的剖视图。

38.图8s是表示图8r之后的工序的剖视图。

39.图8t是表示图8s之后的工序的剖视图。

40.图9是图4的对应图,是用于对不存在伪沟槽栅极构造的情况下的应力进行说明的剖视图。

41.图10是图4的对应图,是用于对存在伪沟槽栅极构造的情况下的应力进行说明的剖视图。

42.图11是图2的对应图,是表示本发明的第二实施方式的半导体装置的半导体芯片的第一主面的构造的俯视图。

43.图12是图11所示的区域xii的放大图。

44.图13是沿着图12所示的xiii-xiii线的剖视图。

45.图14是沿着图12所示的xiv-xiv线的剖视图。

46.图15是沿着图12所示的xv-xv线的剖视图。

47.图16是图11所示的区域xvi的放大图。

48.图17a是用于对图11所示的半导体装置的制造方法的一例进行说明的剖视图。

49.图17b是表示图17a之后的工序的剖视图。

50.图17c是表示图17b之后的工序的剖视图。

51.图17d是表示图17c之后的工序的剖视图。

52.图17e是表示图17d之后的工序的剖视图。

53.图17f是表示图17e之后的工序的剖视图。

54.图17g是表示图17f之后的工序的剖视图。

55.图17h是表示图17g之后的工序的剖视图。

56.图17i是表示图17h之后的工序的剖视图。

57.图17j是表示图17i之后的工序的剖视图。

58.图17k是表示图17j之后的工序的剖视图。

59.图17l是表示图17k之后的工序的剖视图。

60.图17m是表示图17l之后的工序的剖视图。

61.图17n是表示图17m之后的工序的剖视图。

62.图17o是表示图17n之后的工序的剖视图。

63.图17p是表示图17o之后的工序的剖视图。

64.图17q是表示图17p之后的工序的剖视图。

65.图17r是表示图17q之后的工序的剖视图。

66.图17s是表示图17r之后的工序的剖视图。

67.图17t是表示图17s之后的工序的剖视图。

68.图18是图12的对应图,是表示本发明的第三实施方式的半导体装置的半导体芯片的第一主面的构造的放大图。

69.图19是沿着图18所示的xix-xix线的剖视图。

70.图20是沿着图18所示的xx-xx线的剖视图。

具体实施方式

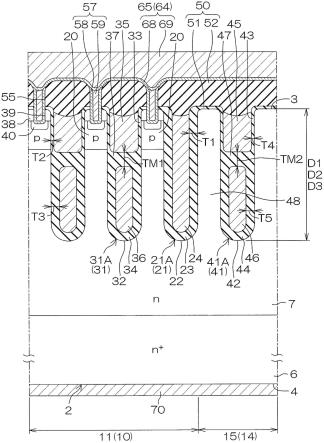

71.图1是表示本发明的第一实施方式的半导体装置1的俯视图。图2是表示图1所示的半导体芯片2的第一主面3的构造的俯视图。图3是图2所示的区域iii的放大图。图4是沿着图3所示的iv-iv线的剖视图。图5是沿着图3所示的v-v线的剖视图。图6是沿着图3所示的vi-vi线的剖视图。图7是图2所示的区域vii的放大图。

72.参照图1~图7,半导体装置1包含形成为长方体形状的硅制的半导体芯片2。半导体芯片2包含:一侧的第一主面3、另一侧的第二主面4、以及连接第一主面3和第二主面4的侧面5a、5b、5c、5d。第一主面3和第二主面4在从它们的法线方向z观察的俯视图(以下简称为“俯视图”)中形成为四边形形状(具体而言为长方形形状)。

73.侧面5a~5d包含:第一侧面5a、第二侧面5b、第三侧面5c以及第四侧面5d。第一侧面5a以及第二侧面5b在第一方向x上延伸,在与第一方向x交叉的第二方向y上对置。具体而言,第二方向y与第一方向x正交。第一侧面5a及第二侧面5b形成半导体芯片2的短边。第三侧面5c以及第四侧面5d在第二方向y上延伸,在第一方向x上对置。第三侧面5c及第四侧面5d形成半导体芯片2的长边。

74.半导体芯片2包含n

型的漏极区6以及n型的漂移区7。漏极区6形成于第二主面4的表层部。漏极区6优选形成于第二主面4的表层部的整个区域。漏极区6的n型杂质浓度可以为1

×

10

18

cm-3

以上且1

×

10

21

cm-3

以下。在本方式(this embodiment)中,漏极区6由半导体基板形成。

75.漏极区6的厚度可以为50μm以上且400μm以下。漏极区6的厚度可以为50μm以上且100μm以下、100μm以上且200μm以下、200μm以上且300μm以下、或300μm以上且400μm以下。漏极区6的厚度优选为50μm以上且150μm以下。

76.漂移区7形成于第一主面3的表层部。漂移区7优选形成于第一主面3的表层部的整个区域。漂移区7形成在第一主面3和漏极区6之间的区域,与漏极区6电连接。漂移区7具有小于漏极区6的n型杂质浓度的n型杂质浓度。漂移区7的n型杂质浓度可以为1

×

10

15

cm-3

以上且1

×

10

18

cm-3

以下。在本方式中,漂移区7由外延层形成。

77.漂移区7具有小于漏极区6的厚度的厚度。漂移区7的厚度可以为2μm以上且30μm以下。漂移区7的厚度可以为2μm以上且5μm以下、5μm以上且10μm以下、10μm以上且15μm以下、15μm以上且20μm以下、20μm以上且25μm以下、或25μm以上且30μm以下。漂移区7的厚度优选为5μm以上且15μm以下。

78.参照图2,半导体装置1包含从侧面5a~5d向内侧隔开间隔地形成于第一主面3的活性区10(第一区域)。活性区10是形成作为功能器件的misfet(metal insulator semiconductor field effect transistor,金属绝缘体半导体场效应晶体管)的区域。活性区10具体而言包含:第一活性区11、第二活性区12及第三活性区13。第一活性区11形成于第一主面3的中央部。第一活性区11在俯视图中形成为四边形形状(在第二方向y上延伸的长方形形状)。

79.第二活性区12形成于第一侧面5a与第一活性区11之间的区域。当设定了在第二方向y上横穿第一主面3的中央部的中央线时,从该中央线向第一方向x的一侧(第三侧面5c侧)隔开间隔地形成第二活性区12。第二活性区12在俯视图中形成为四边形形状(在第一方向x上延伸的长方形形状)。第二活性区12在第二方向y上与第一活性区11对置。

80.第三活性区13形成于第一侧面5a与第一活性区11之间的区域。当设定了在第二方向y上横穿第一主面3的中央部的中央线时,从该中央线向第一方向x的另一侧(第四侧面5d侧)隔开间隔地形成第三活性区13。第三活性区13在俯视图中形成为四边形形状(在第一方向x上延伸的长方形形状)。第三活性区13在第二方向y上与第一活性区11对置,在第一方向x上与第二活性区12对置。

81.半导体装置1包含形成于第一主面3的非活性区14(第二区域)。非活性区14形成在活性区10外,是不形成功能器件(misfet)的区域。具体而言,非活性区14包含外周区域15及焊盘区域16。外周区域15在俯视图中形成为包围活性区10的环状。具体而言,外周区域15在俯视图中沿着侧面5a~5d呈带状延伸,一并包围第一活性区11、第二活性区12以及第三活性区13。焊盘区域16在俯视图中在第二活性区12与第三活性区13之间的区域形成为四边形形状。

82.参照图3~图6,半导体装置1包含在活性区10中形成于第一主面3的表层部的p型的体区20。体区20均匀地形成在活性区10的整个区域。从漂移区7的底部向第一主面3侧隔开间隔地形成体区20。体区20的p型杂质浓度可以为1

×

10

16

cm-3

以上且1

×

10

18

cm-3

以下。

83.参照图2~图7,半导体装置1包含形成于第一主面3的多个(在本方式中为3个)场沟槽构造21(第一槽构造)。在本方式中,多个场沟槽构造21包含:1个第一场沟槽构造21a、1个第二场沟槽构造21b以及1个第三场沟槽构造21c。

84.第一场沟槽构造21a在第一主面3中从第二侧面5b向第一侧面5a侧隔开间隔地形成于第二侧面5b侧的区域。第一场沟槽构造21a在俯视图中形成为在第一方向x上延伸的带状。第一场沟槽构造21a在第一主面3的一侧(第一侧面5a侧)的区域划分第一活性区11,在第一主面3的另一侧(第二侧面5b侧)的区域划分非活性区14。

85.当设定了在第二方向y上横穿焊盘区域16的线时,第一场沟槽构造21a在第一方向x上横穿该线。由此,第一场沟槽构造21a隔着第一活性区11与焊盘区域16对置。

86.第一场沟槽构造21a具有包含第一沟槽22(第一槽)、第一绝缘膜23以及第一电极24的单电极构造。第一沟槽22、第一绝缘膜23以及第一电极24可以分别称为“场沟槽”、“场绝缘膜”以及“场电极”。通过将第一主面3朝向第二主面4下挖而形成第一沟槽22。第一沟槽22贯通体区20,并从漂移区7的底部向第一主面3侧隔开间隔地形成第一沟槽22。

87.第一沟槽22的侧壁在半导体芯片2内在与第一主面3之间形成的角度可以为90

°

以上且92

°

以下。第一沟槽22也可以形成为开口宽度从开口朝向底壁变窄的尖细形状。第一沟槽22的底壁优选形成为朝向第二主面4的弯曲形状。

88.第一沟槽22具有第一宽度w1。第一宽度w1是与第一沟槽22延伸的方向正交的方向(即第二方向y)的宽度。第一宽度w1可以为0.5μm以上且3μm以下。第一宽度w1可以为0.5μm以上且1μm以下、1μm以上且1.5μm以下、1.5μm以上且2μm以下、2μm以上且2.5μm以下、或2.5μm以上且3μm以下。第一宽度w1优选为0.5μm以上且2μm以下。

89.第一沟槽22具有第一深度d1。第一深度d1可以为1μm以上且10μm以下。第一深度d1可以为1μm以上且2μm以下、2μm以上且4μm以下、4μm以上且6μm以下、6μm以上且8μm以下、或8μm以上且10μm以下。第一深度d1优选为1μm以上且5μm以下。

90.第一沟槽22具有第一纵横比(aspect ratio)d1/w1。第一纵横比d1/w1是第一深度d1相对于第一宽度w1之比。第一纵横比d1/w1优选超过1且为5以下。第一纵横比d1/w1特别优选为3以上且5以下。

91.沿着第一沟槽22的壁面形成第一绝缘膜23。具体而言,第一绝缘膜23在第一沟槽22的壁面的整个区域形成为膜状,在第一沟槽22内划分u字状的凹陷空间。在本方式中,第一绝缘膜23包含氧化硅。

92.第一绝缘膜23具有第一厚度t1。第一厚度t1是沿着第一沟槽22的壁面的法线方向的第一绝缘膜23的厚度。第一厚度t1可以为0.1μm以上且1μm以下。第一厚度t1可以为0.1μm以上且0.25μm以下、0.25μm以上且0.5μm以下、0.5μm以上且0.75μm以下、或0.75μm以上且1μm以下。第一厚度t1优选为0.15μm以上且0.65μm以下。

93.第一电极24隔着第一绝缘膜23埋设于第一沟槽22。第一电极24横穿体区20的底部的深度位置,隔着第一绝缘膜23与体区20以及漂移区7对置。即,第一电极24包含相对于体区20的底部位于第一主面3侧的部分、以及相对于体区20的底部位于第一沟槽22的底壁侧的部分。在本方式中,第一电极24包含导电性多晶硅。第一电极24形成为场电极。对第一电极24施加作为基准电位的源极电位(例如接地电位)。

94.在第一方向x上从焊盘区域16向一侧(第三侧面5c侧)隔开间隔地形成第二场沟槽

构造21b。第二场沟槽构造21b在第一主面3中从第一侧面5a向第二侧面5b侧隔开间隔地形成于第一侧面5a侧的区域。第二场沟槽构造21b在俯视图中形成为在第一方向x上延伸的带状。

95.第二场沟槽构造21b在第一主面3的另一侧(第二侧面5b侧)的区域划分第二活性区12,在第一主面3的一侧(第一侧面5a侧)的区域划分非活性区14。第二场沟槽构造21b隔着第一活性区11以及第二活性区12与第一场沟槽构造21a对置。

96.第二场沟槽构造21b与第一场沟槽构造21a一样,具有包含第一沟槽22、第一绝缘膜23以及第一电极24的单电极构造。第二场沟槽构造21b除了第一沟槽22的长度不同这一点以外,具有与第一场沟槽构造21a一样的构造。省略针对第二场沟槽构造21b的具体的说明。

97.在第一方向x上从焊盘区域16向另一侧(第四侧面5d侧)隔开间隔地形成第三场沟槽构造21c。第三场沟槽构造21c在第一主面3中从第一侧面5a向第二侧面5b侧隔开间隔地形成于第一侧面5a侧的区域。第三场沟槽构造21c在俯视图中形成为在第一方向x上延伸的带状。

98.第三场沟槽构造21c在第一主面3的另一侧(第二侧面5b侧)的区域划分第三活性区13,在第一主面3的一侧(第一侧面5a侧)的区域划分非活性区14。第三场沟槽构造21c隔着第一活性区11和第三活性区13与第一场沟槽构造21a对置,隔着焊盘区域16与第二场沟槽构造21b对置。

99.第三场沟槽构造21c与第一场沟槽构造21a一样,具有包含第一沟槽22、第一绝缘膜23以及第一电极24的单电极构造。第三场沟槽构造21c除了第一沟槽22的长度不同这一点以外,具有与第一场沟槽构造21a一样的构造。省略针对第三场沟槽构造21c的具体的说明。

100.参照图2~图7,半导体装置1包含在活性区10中形成于第一主面3的多个沟槽栅极构造31(第二槽构造)。在本方式中,多个沟槽栅极构造31包含:多个第一沟槽栅极构造31a、多个第二沟槽栅极构造31b以及多个第三沟槽栅极构造31c。

101.多个第一沟槽栅极构造31a形成于第一活性区11。从焊盘区域16以及第一场沟槽构造21a起隔开间隔地形成多个第一沟槽栅极构造31a。多个第一沟槽栅极构造31a分别在俯视图中形成为在第一方向x上延伸的带状,并在第二方向y上隔开间隔地形成多个第一沟槽栅极构造31a。多个第一沟槽栅极构造31a形成为在第一方向x上延伸的条纹状。即,多个第一沟槽栅极构造31a在俯视图中相对于第一场沟槽构造21a平行地延伸。

102.隔开第一间隔p1地形成多个第一沟槽栅极构造31a。第一间隔p1可以为0.1μm以上且2μm以下。第一间隔p1可以为0.1μm以上且0.5μm以下、0.5μm以上且1μm以下、1μm以上且1.5μm以下、或1.5μm以上且2μm以下。第一间隔p1优选为0.5μm以上且1.5μm以下。

103.从第一场沟槽构造21a起隔开第二间隔p2地形成第一沟槽栅极构造31a。第二间隔p2可以为0.1μm以上且2μm以下。第二间隔p2可以为0.1μm以上且0.5μm以下、0.5μm以上且1μm以下、1μm以上且1.5μm以下、或1.5μm以上且2μm以下。第二间隔p2优选为0.5μm以上且1.5μm以下。第二间隔p2优选与第一间隔p1相等。第二间隔p2与第一间隔p1相等是指第二间隔p2的值属于以第一间隔p1的值为基准的

±

10%以内的范围。

104.多个第一沟槽栅极构造31a分别具有包含第二沟槽32(第二槽)、第二绝缘膜33、第

三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37的分离电极构造(多电极构造)。第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35以及第三电极36可以分别称为“栅极沟槽”、“上侧绝缘膜”、“下侧绝缘膜”、“上侧电极”以及“下侧电极”。通过将第一主面3朝向第二主面4下挖而形成第二沟槽32。第二沟槽32贯通体区20,并从漂移区7的底部向第一主面3侧隔开间隔地形成第二沟槽32。

105.第二沟槽32的侧壁在半导体芯片2内在与第一主面3之间形成的角度可以为90

°

以上且92

°

以下。第二沟槽32也可以形成为开口宽度从开口朝向底壁变窄的尖细形状。第二沟槽32的底壁优选形成为朝向第二主面4的弯曲形状。

106.第二沟槽32具有第二宽度w2。第二宽度w2是与第二沟槽32延伸的方向正交的方向(即第二方向y)的宽度。第二宽度w2可以为0.5μm以上且3μm以下。第二宽度w2可以为0.5μm以上且1μm以下、1μm以上且1.5μm以下、1.5μm以上且2μm以下、2μm以上且2.5μm以下、或2.5μm以上且3μm以下。第二宽度w2优选为0.5μm以上且2μm以下。

107.第二沟槽32具有第二深度d2。第二深度d2可以为1μm以上且10μm以下。第二深度d2可以为1μm以上且2μm以下、2μm以上且4μm以下、4μm以上且6μm以下、6μm以上且8μm以下、或8μm以上且10μm以下。第二深度d2优选为1μm以上且5μm以下。

108.第二宽度w2优选与第一沟槽22的第一宽度w1相等。第二宽度w2与第一宽度w1相等是指第二宽度w2的值位于以第一宽度w1的值为基准的

±

10%以内的范围。第二深度d2优选与第一沟槽22的第一深度d1相等。第二深度d2与第一深度d1相等是指第二深度d2的值属于以第一深度d1的值为基准的

±

10%以内的范围。

109.第二沟槽32具有第二纵横比d2/w2。第二纵横比d2/w2是第二深度d2相对于第二宽度w2之比。第二纵横比d2/w2优选超过1且为5以下。第二纵横比d2/w2特别优选为3以上且5以下。在本方式中,第二纵横比d2/w2与第一沟槽22的第一纵横比d1/w1相等。

110.第二绝缘膜33覆盖第二沟槽32的上壁面。具体而言,第二绝缘膜33覆盖相对于体区20的底部位于第二沟槽32的开口侧的区域的上壁面。第二绝缘膜33与体区20相接。第二绝缘膜33也可以在体区20外的区域中与漂移区7相接。第二绝缘膜33在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23对置。在本方式中,第二绝缘膜33包含氧化硅。第二绝缘膜33形成为栅极绝缘膜。

111.第二绝缘膜33具有比第一绝缘膜23的第一厚度t1薄的第二厚度t2。第二厚度t2是沿着第二沟槽32的壁面的法线方向的第二绝缘膜33的厚度。第二厚度t2可以为0.01μm以上且0.2μm以下。第二厚度t2可以为0.01μm以上且0.05μm以下、0.05μm以上且0.1μm以下、0.1μm以上且0.15μm以下、或0.15μm以上且0.2μm以下。第二厚度t2优选为0.05μm以上且0.1μm以下。

112.第三绝缘膜34覆盖第二沟槽32的下壁面。具体而言,第三绝缘膜34覆盖相对于体区20的底部位于第二沟槽32的底壁侧的区域的下壁面。第三绝缘膜34在第二沟槽32的底壁侧的区域划分u字状的凹陷空间。第三绝缘膜34与漂移区7相接。第三绝缘膜34在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23对置。在本方式中,第三绝缘膜34包含氧化硅。

113.第三绝缘膜34具有比第二绝缘膜33的第二厚度t2厚的第三厚度t3。第三厚度t3是沿着第二沟槽32的壁面的法线方向的第三绝缘膜34的厚度。第三厚度t3可以为0.1μm以上

且1μm以下。第三厚度t3可以为0.1μm以上且0.25μm以下、0.25μm以上且0.5μm以下、0.5μm以上且0.75μm以下、或0.75μm以上且1μm以下。

114.第三厚度t3优选为0.15μm以上且0.65μm以下。第三厚度t3优选与第一绝缘膜23的第一厚度t1相等。第三厚度t3与第一厚度t1相等是指第三厚度t3的值属于以第一厚度t1的值为基准的

±

10%以内的范围。

115.第二电极35隔着第二绝缘膜33埋设于第二沟槽32内的上侧(开口侧)。第二电极35隔着第二绝缘膜33与体区20对置。第二电极35的底部相对于体区20的底部的深度位置位于第二沟槽32的底壁侧。第二电极35的底部隔着第三绝缘膜34与漂移区7对置。第二电极35相对于体区20的对置面积大于第二电极35相对于漂移区7的对置面积。

116.第二电极35在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一电极24对置。在本方式中,第二电极35包含导电性多晶硅。第二电极35形成为栅极电极。对第二电极35施加作为控制电位的栅极电位。

117.第三电极36隔着第三绝缘膜34埋设于第二沟槽32内的下侧(底壁侧)。第三电极36隔着第三绝缘膜34与漂移区7对置。第三电极36在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一电极24对置。在本方式中,第三电极36包含导电性多晶硅。第三电极36形成为场电极。对第三电极36施加作为基准电位的源极电位(例如接地电位)。即,第三电极36在本方式中被固定为与第一电极24相同的电位。

118.第三电极36包含隔着第三绝缘膜34向第二沟槽32的开口侧引出的1个或多个(在本方式中为3个)引出电极36a。在本方式中,多个引出电极36a形成于第二沟槽32的一侧(第三侧面5c侧)的一端部、另一侧(第四侧面5d侧)的另一端部以及中央部。中央部的引出电极36a将第三电极36分割为第二沟槽32的一侧(第三侧面5c侧)的部分和另一侧(第四侧面5d侧)的部分。

119.在对多个第一沟槽栅极构造31a进行观察时,多个引出电极36a在俯视图中在第二方向y上排列为一列,相互对置。引出电极36a的配置以及个数是任意的,根据第二沟槽32的长度、布线布局而适当调整。

120.第一中间绝缘膜37介于第二电极35和第三电极36之间,使第二电极35和第三电极36绝缘分离。第一中间绝缘膜37与第二绝缘膜33以及第三绝缘膜34相连。第一中间绝缘膜37在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23对置。在本方式中,第一中间绝缘膜37包含氧化硅。

121.第一中间绝缘膜37具有比第二绝缘膜33的第二厚度t2厚的第一中间厚度tm1。第一中间厚度tm1是第一中间绝缘膜37中的沿着法线方向z的部分的厚度。第一中间厚度tm1可以为0.05μm以上且1μm以下。第一中间厚度tm1可以为0.05μm以上且0.1μm以下、0.1μm以上且0.25μm以下、0.25μm以上且0.5μm以下、0.5μm以上且0.75μm以下、或0.75μm以上且1μm以下。第一中间厚度tm1优选为0.2μm以上且0.5μm以下。

122.第一中间绝缘膜37中的、在俯视图中介于第二电极35和第三电极36之间的第一中间部分37a的厚度,能够根据在制造中使用的抗蚀剂掩模的布局而适当调整,其是任意的。第一中间部分37a的厚度可以为0.05μm以上且15μm以下。第一中间部分37a的厚度可以为0.05μm以上且1μm以下、1μm以上且5μm以下、5μm以上且10μm以下、或10μm以上且15μm以下。第一中间部分37a的厚度优选为3μm以上且5μm以下。

123.参照图7,多个第二沟槽栅极构造31b形成于第二活性区12。从焊盘区域16以及第二场沟槽构造21b起隔开间隔地形成多个第二沟槽栅极构造31b。多个第二沟槽栅极构造31b在俯视图中分别形成为在第一方向x上延伸的带状,并在第二方向y上隔开第一间隔p1地形成多个第二沟槽栅极构造31b。

124.多个第二沟槽栅极构造31b形成为在第一方向x上延伸的条纹状。即,多个第二沟槽栅极构造31b在俯视图中相对于第二场沟槽构造21b平行地延伸。从第二场沟槽构造21b起隔开第二间隔p2地形成多个第二沟槽栅极构造31b。

125.多个第二沟槽栅极构造31b与第一沟槽栅极构造31a一样,分别具有包含第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37的分离电极构造。第二沟槽栅极构造31b除了第二沟槽32的长度以及引出电极36a(第三电极36)的布局不同这一点之外,具有与第一沟槽栅极构造31a一样的构造。省略针对第二沟槽栅极构造31b的具体的说明。

126.参照图7,多个第三沟槽栅极构造31c形成于第三活性区13。从焊盘区域16以及第三场沟槽构造21c起隔开间隔地形成多个第三沟槽栅极构造31c。多个第三沟槽栅极构造31c在俯视图中分别形成为在第一方向x上延伸的带状,并在第二方向y上隔开第一间隔p1地形成多个第三沟槽栅极构造31c。

127.多个第三沟槽栅极构造31c形成为在第一方向x上延伸的条纹状。即,多个第三沟槽栅极构造31c在俯视图中相对于第三场沟槽构造21c平行地延伸。从第三场沟槽构造21c起隔开第二间隔p2地形成多个第三沟槽栅极构造31c。

128.多个第三沟槽栅极构造31c与第一沟槽栅极构造31a一样,分别具有包含第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37的分离电极构造。第三沟槽栅极构造31c除了第二沟槽32的长度以及引出电极36a(第三电极36)的布局不同这一点之外,具有与第一沟槽栅极构造31a一样的构造。省略针对第三沟槽栅极构造31c的具体的说明。

129.参照图3以及图4,半导体装置1包含在体区20的表层部分别形成于沿着多个第二沟槽32(沟槽栅极构造31)的区域的n

型的多个源极区38。各源极区38具有超过漂移区7的n型杂质浓度的n型杂质浓度。各源极区38的n型杂质浓度可以为1

×

10

18

cm-3

以上且1

×

10

21

cm-3

以下。

130.多个源极区38在俯视图中分别形成为沿着多个第二沟槽32延伸的带状。各源极区38覆盖从对应的第二沟槽32露出的第二绝缘膜33。即,各源极区38隔着第二绝缘膜33与第二电极35对置。各源极区38的底部从体区20的底部起隔开间隔地位于第一主面3侧的区域。各源极区38在与漂移区7之间划定misfet的沟道。

131.半导体装置1包含在活性区10分别形成于多个第二沟槽32(沟槽栅极构造31)之间的区域的多个源极接触孔39。多个源极接触孔39在俯视图中分别形成为在第一方向x上延伸的带状。多个源极接触孔39在俯视图中形成为在第一方向x上延伸的条纹状。

132.多个源极接触孔39以夹入1个第二沟槽32的形式沿着第二方向y与多个第二沟槽32交替地形成。在第一方向x上,各源极接触孔39的长度优选小于各第二沟槽32的长度。在俯视图中从第二沟槽32起隔开间隔地形成各源极接触孔39。各源极接触孔39形成为横穿源极区38的深度。各源极接触孔39的底壁位于体区20的底部和源极区38的底部之间的区域。

各源极接触孔39使源极区38从两侧露出。

133.半导体装置1包含在体区20内分别形成于沿着多个源极接触孔39的区域的p

型的多个接触区40。各接触区40具有超过体区20的p型杂质浓度的p型杂质浓度。各接触区40的p型杂质浓度可以为1

×

10

18

cm-3

以上且1

×

10

21

cm-3

以下。

134.各接触区40在体区20中形成于沿着各源极接触孔39的底壁的区域。从体区20的底部向各源极接触孔39的底壁侧隔开间隔地形成各接触区40。各接触区40覆盖各源极接触孔39的底壁的整个区域。各接触区40可以覆盖各源极接触孔39的侧壁。各接触区40与多个源极区38电连接。

135.参照图2~图7,半导体装置1包含在非活性区14中形成于第一主面3的多个伪沟槽栅极构造41(第三槽构造)。伪沟槽栅极构造41可以称为“伪沟槽构造”(dummy trench)。多个伪沟槽栅极构造41由与活性区10(misfet)电独立的附件模式(accessory pattern)构成。多个伪沟槽栅极构造41包含:1个第一伪沟槽栅极构造41a、1个第二伪沟槽栅极构造41b以及1个第三伪沟槽栅极构造41c。

136.第一伪沟槽栅极构造41a从第一场沟槽构造21a向第一活性区11的相反侧隔开间隔地形成于非活性区14,与第一场沟槽构造21a相邻。第一伪沟槽栅极构造41a在俯视图中形成为在第一方向x上延伸的带状。即,第一伪沟槽栅极构造41a在俯视图中相对于第一场沟槽构造21a平行地延伸,隔着第一场沟槽构造21a与第一沟槽栅极构造31a对置。

137.从第一场沟槽构造21a起隔开第三间隔p3地形成第一伪沟槽栅极构造41a。第三间隔p3可以为0.1μm以上且2μm以下。第三间隔p3可以为0.1μm以上且0.5μm以下、0.5μm以上且1μm以下、1μm以上且1.5μm以下、或1.5μm以上且2μm以下。第三间隔p3优选为0.5μm以上且1.5μm以下。

138.第三间隔p3优选与第二间隔p2(第一间隔p1)相等。第三间隔p3与第二间隔p2(第一间隔p1)相等是指第三间隔p3的值属于以第二间隔p2(第一间隔p1)的值为基准的

±

10%以内的范围。

139.第一伪沟槽栅极构造41a具有包含第三沟槽42(第三槽)、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47的伪分离电极构造。第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47可以分别称为“伪沟槽”、“上侧伪绝缘膜”、“下侧伪绝缘膜”、“上侧伪电极”、“下侧伪电极”以及“伪中间绝缘膜”。通过将第一主面3朝向第二主面4下挖而形成第三沟槽42。第三沟槽42在半导体芯片2的厚度方向上横穿体区20的底部的深度位置,并从漂移区7的底部向第一主面3侧隔开间隔地形成第三沟槽42。

140.第三沟槽42的侧壁在半导体芯片2内在与第一主面3之间形成的角度可以为90

°

以上且92

°

以下。第三沟槽42可以形成为开口宽度从开口朝向底壁变窄的尖细形状。第三沟槽42的底壁优选形成为朝向第二主面4的弯曲形状。

141.第三沟槽42具有第三宽度w3。第三宽度w3是与第三沟槽42延伸的方向正交的方向(即第二方向y)的宽度。第三宽度w3可以为0.5μm以上且3μm以下。第三宽度w3可以为0.5μm以上且1μm以下、1μm以上且1.5μm以下、1.5μm以上且2μm以下、2μm以上且2.5μm以下、或2.5μm以上且3μm以下。第三宽度w3优选为0.5μm以上且2μm以下。

142.第三沟槽42具有第三深度d3。第三深度d3可以为1μm以上且10μm以下。第三深度d3

可以为1μm以上且2μm以下、2μm以上且4μm以下、4μm以上且6μm以下、6μm以上且8μm以下、或8μm以上且10μm以下。第三深度d3优选为1μm以上且5μm以下。

143.第三宽度w3优选与第二沟槽32的第二宽度w2相等。第三宽度w3与第二宽度w2相等是指第三宽度w3的值属于以第二宽度w2的值为基准的

±

10%以内的范围。第三深度d3优选与第二沟槽32的第二深度d2相等。第三深度d3与第二深度d2相等是指第三深度d3的值属于以第二深度d2的值为基准的

±

10%以内的范围。

144.第三沟槽42具有第三纵横比d3/w3。第三纵横比d3/w3是第三深度d3相对于第三宽度w3之比。第三纵横比d3/w3优选超过1且为5以下。第三纵横比d3/w3特别优选为3以上且5以下。在本方式中,第三纵横比d3/w3与第二纵横比d2/w2相等。

145.第四绝缘膜43覆盖第三沟槽42的上壁面。具体而言,第四绝缘膜43覆盖相对于体区20的底部的深度位置位于第三沟槽42的开口侧的区域的上壁面。第四绝缘膜43与漂移区7相接。第四绝缘膜43在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23对置。第四绝缘膜43隔着场沟槽构造21与沟槽栅极构造31的第二绝缘膜33对置。在本方式中,第四绝缘膜43包含氧化硅。第四绝缘膜43形成为伪栅极绝缘膜。

146.第四绝缘膜43具有比第一绝缘膜23的第一厚度t1薄的第四厚度t4。第四厚度t4是沿着第三沟槽42的壁面的法线方向的第四绝缘膜43的厚度。第四厚度t4可以为0.01μm以上且0.2μm以下。第四厚度t4可以为0.01μm以上且0.05μm以下、0.05μm以上且0.1μm以下、0.1μm以上且0.15μm以下、或0.15μm以上且0.2μm以下。第四厚度t4优选为0.05μm以上且0.1μm以下。

147.第四厚度t4优选与第二绝缘膜33的第二厚度t2相等。第四厚度t4与第二厚度t2相等是指第四厚度t4的值属于以第二厚度t2的值为基准的

±

10%以内的范围。

148.第五绝缘膜44覆盖第三沟槽42的下壁面。具体而言,第五绝缘膜44覆盖相对于体区20的底部的深度位置位于第三沟槽42的底壁侧的区域的下壁面。第五绝缘膜44在第三沟槽42的底壁侧的区域划分u字状的凹陷空间。第五绝缘膜44与漂移区7相接。第五绝缘膜44在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23对置。第五绝缘膜44隔着场沟槽构造21与沟槽栅极构造31的第三绝缘膜34对置。在本方式中,第五绝缘膜44包含氧化硅。

149.第五绝缘膜44具有比第四绝缘膜43的第四厚度t4厚的第五厚度t5。第五厚度t5是沿着第三沟槽42的壁面的法线方向的第五绝缘膜44的厚度。第五厚度t5可以为0.1μm以上且1μm以下。第五厚度t5可以为0.1μm以上且0.25μm以下、0.25μm以上且0.5μm以下、0.5μm以上且0.75μm以下、或者0.75μm以上且1μm以下。

150.第五厚度t5优选为0.15μm以上且0.65μm以下。第五厚度t5优选与第三绝缘膜34的第三厚度t3相等。第五厚度t5与第三厚度t3相等是指第五厚度t5的值属于以第三厚度t3的值为基准的

±

10%以内的范围。

151.第四电极45隔着第四绝缘膜43以电悬浮状态埋设于第三沟槽42的上侧。第四电极45形成为伪栅极电极。第四电极45的底部相对于体区20的底部的深度位置位于第三沟槽42的底壁侧。第四电极45隔着第四绝缘膜43与漂移区7对置。

152.第四电极45在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一电极24对置。第四电极45隔着场沟槽构造21与沟槽栅极构造31的第二电极35对置。在本方式

中,第四电极45包含导电性多晶硅。

153.第五电极46隔着第五绝缘膜44以电悬浮状态埋设于第三沟槽42的下侧。第五电极46形成为伪场电极。第五电极46隔着第五绝缘膜44与漂移区7对置。第五电极46在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一电极24对置。第五电极46隔着场沟槽构造21与沟槽栅极构造31的第三电极36对置。在本方式中,第五电极46包含导电性多晶硅。

154.第五电极46包含隔着第五绝缘膜44向第三沟槽42的开口侧引出的1个或多个(在本方式中为3个)引出电极46a。在本方式中,多个引出电极46a形成于第三沟槽42的一侧(第三侧面5c侧)的一端部、另一侧(第四侧面5d侧)的另一端部以及中央部。中央部的引出电极46a将第四电极45分割为第三沟槽42的一侧(第三侧面5c侧)的部分和另一侧(第四侧面5d侧)的部分。

155.在设定了在第二方向y上分别横穿多个沟槽栅极构造31的多个引出电极36a的多条线时,多个引出电极46a位于该多条线上。由此,多个引出电极46a隔着场沟槽构造21以1对1对应的关系与多个引出电极36a对置。引出电极46a的配置以及个数是任意的,根据引出电极36a(第三电极36)的布局而适当调整。

156.第二中间绝缘膜47介于第四电极45和第五电极46之间,使第四电极45和第五电极46绝缘分离。第二中间绝缘膜47与第四绝缘膜43以及第五绝缘膜44相连。第二中间绝缘膜47在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23对置。第二中间绝缘膜47隔着场沟槽构造21与沟槽栅极构造31的第一中间绝缘膜37对置。在本方式中,第二中间绝缘膜47包含氧化硅。

157.第二中间绝缘膜47具有比第四绝缘膜43的第四厚度t4厚的第二中间厚度tm2。第二中间厚度tm2是第二中间绝缘膜47中的沿着法线方向z的部分的厚度。第二中间厚度tm2也可以为0.05μm以上且1μm以下。第二中间厚度tm2可以为0.05μm以上且0.1μm以下、0.1μm以上且0.25μm以下、0.25μm以上且0.5μm以下、0.5μm以上且0.75μm以下、或0.75μm以上且1μm以下。

158.第二中间厚度tm2优选为0.2μm以上且0.5μm以下。

159.第二中间厚度tm2优选与第一中间绝缘膜37的第一中间厚度tm1相等。第二中间厚度tm2与第一中间厚度tm1相等是指第二中间厚度tm2的值属于以第一中间厚度tm1的值为基准的

±

10%以内的范围。

160.第二中间绝缘膜47中的、在俯视图中介于第四电极45与第五电极46之间的第二中间部分47a的厚度能够根据在制造中使用的抗蚀剂掩模的布局而适当调整,其是任意的。第二中间部分47a的厚度可以为0.05μm以上且15μm以下。第二中间部分47a的厚度可以为0.05μm以上且1μm以下、1μm以上且5μm以下、5μm以上且10μm以下、或10μm以上且15μm以下。第二中间部分47a的厚度优选为3μm以上且5μm以下。

161.第二中间部分47a的厚度优选与第一中间部分37a的厚度相等。第二中间部分47a的厚度与第一中间部分37a的厚度相等是指第二中间部分47a的厚度的值属于以第一中间部分37a的厚度的值为基准的

±

10%以内的范围。

162.第一伪沟槽栅极构造41a在与第一场沟槽构造21a之间划分由半导体芯片2的一部分构成的台面部48。在台面部48中,在第一主面3的表层部不形成体区20。即,台面部48由漂移区7(外延层)构成,使漂移区7从第一主面3露出。

163.这样,第一伪沟槽栅极构造41a具有与第一沟槽栅极构造31a对应的构造。即,第一伪沟槽栅极构造41a的第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47分别与第一沟槽栅极构造31a的第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37对应。由此,第一伪沟槽栅极构造41a具有隔着第一场沟槽构造21a与第一沟槽栅极构造31a对称(具体而言为线对称)的构造。

164.参照图7,第二伪沟槽栅极构造41b从第二场沟槽构造21b向第二活性区12的相反侧隔开间隔地形成于非活性区14,与第二场沟槽构造21b相邻。第二伪沟槽栅极构造41b在俯视图中形成为在第一方向x上延伸的带状。即,第二伪沟槽栅极构造41b在俯视图中相对于第二场沟槽构造21b平行地延伸,隔着第二场沟槽构造21b与第二沟槽栅极构造31b对置。从第二场沟槽构造21b起隔开第三间隔p3地形成第二伪沟槽栅极构造41b,第二伪沟槽栅极构造41b在与第二场沟槽构造21b之间划分台面部48。

165.第二伪沟槽栅极构造41b与第一伪沟槽栅极构造41a一样,具有包含第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47的伪分离电极构造。第二伪沟槽栅极构造41b除了第三沟槽42的长度以及引出电极46a(第五电极46)的布局不同这一点以外,具有与第一伪沟槽栅极构造41a一样的构造。

166.第二伪沟槽栅极构造41b具有与第二沟槽栅极构造31b对应的构造。即,第二伪沟槽栅极构造41b的第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47分别与第二沟槽栅极构造31b的第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37对应。由此,第二伪沟槽栅极构造41b具有隔着第二场沟槽构造21b与第二沟槽栅极构造31b对称(具体而言为线对称)的构造。省略针对第二伪沟槽栅极构造41b的具体的说明。

167.参照图7,第三伪沟槽栅极构造41c从第三场沟槽构造21c向第三活性区13的相反侧隔开间隔地形成于非活性区14,与第三场沟槽构造21c相邻。第三伪沟槽栅极构造41c在俯视图中形成为在第一方向x上延伸的带状。即,第三伪沟槽栅极构造41c在俯视图中相对于第三场沟槽构造21c平行地延伸,隔着第三场沟槽构造21c与第三沟槽栅极构造31c对置。从第三场沟槽构造21c起隔开第三间隔p3地形成第三伪沟槽栅极构造41c,第三伪沟槽栅极构造41c在与第三场沟槽构造21c之间划分台面部48。

168.第三伪沟槽栅极构造41c与第一伪沟槽栅极构造41a一样,具有包含第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47的伪分离电极构造。第三伪沟槽栅极构造41c除了第三沟槽42的长度以及引出电极46a(第五电极46)的布局不同这一点以外,具有与第一伪沟槽栅极构造41a一样的构造。

169.第三伪沟槽栅极构造41c具有与第三沟槽栅极构造31c对应的构造。即,第三伪沟槽栅极构造41c的第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47分别与第三沟槽栅极构造31c的第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37对应。由此,第三伪沟槽栅极构造41c具有隔着第三场沟槽构造21c与第三沟槽栅极构造31c对称(具体而言为线对称)的构造。省略针对第三伪沟槽栅极构造41c的具体的说明。

170.参照图4~图6,半导体装置1包含覆盖第一主面3的主面绝缘膜50。主面绝缘膜50

覆盖多个伪沟槽栅极构造41的整个区域,使多个伪沟槽栅极构造41从外部绝缘分离。即,主面绝缘膜50在与半导体芯片2之间使多个伪沟槽栅极构造41孤立为电悬浮状态。另一方面,主面绝缘膜50选择性地覆盖多个场沟槽构造21和多个沟槽栅极构造31,允许来自外部的接触。

171.在本方式中,主面绝缘膜50具有包含从第一主面3侧起依次层叠的第一主面绝缘膜51和第二主面绝缘膜52的层叠构造。在本方式中,第一主面绝缘膜51包含氧化硅。第一主面绝缘膜51覆盖第一主面3,与第一绝缘膜23、第二绝缘膜33、第三绝缘膜34、第四绝缘膜43以及第五绝缘膜44相连。

172.在本方式中,第二主面绝缘膜52包含氧化硅。第二主面绝缘膜52选择性地覆盖多个场沟槽构造21以及多个沟槽栅极构造31,另一方面,覆盖多个伪沟槽栅极构造41的整个区域。第二主面绝缘膜52具有超过第一主面绝缘膜51的厚度的厚度。

173.主面绝缘膜50在覆盖活性区10的部分,具有多个栅极开口53、多个源极开口54以及多个源极接触开口55。多个栅极开口53分别形成于在主面绝缘膜50中覆盖多个沟槽栅极构造31的部分。多个栅极开口53使多个沟槽栅极构造31的第二电极35分别露出。多个栅极开口53也可以使多个沟槽栅极构造31的一端部和/或另一端部分别露出。多个栅极开口53优选在第二方向y上隔开间隔地排列成一列。

174.多个源极开口54分别形成于在主面绝缘膜50中覆盖多个场沟槽构造21的部分以及覆盖多个沟槽栅极构造31的部分。多个源极开口54使多个场沟槽构造21的第一电极24以及多个沟槽栅极构造31的引出电极36a(第三电极36)分别露出。

175.多个源极开口54根据引出电极36a的配置,在第二方向y上隔开间隔地排列成一列。在本方式中,多个源极开口54仅使位于中央部的多个引出电极36a露出,不使位于两端的多个引出电极36a露出。即,位于两端的多个引出电极36a由主面绝缘膜50覆盖。

176.多个源极接触开口55分别形成于在主面绝缘膜50中覆盖多个沟槽栅极构造31之间的区域的部分。多个源极接触开口55使多个源极接触孔39以1对1对应的关系分别露出。多个源极接触开口55具有与多个源极接触孔39匹配的平面形状,分别与多个源极接触孔39连通。

177.半导体装置1包含埋设于主面绝缘膜50的多个栅极插头电极56及多个源极插头电极57。多个栅极插头电极56分别埋设于多个栅极开口53。多个栅极插头电极56在对应的栅极开口53内分别与沟槽栅极构造31的第二电极35电连接。

178.多个源极插头电极57分别埋设于多个源极开口54以及多个源极接触开口55。多个源极插头电极57在对应的源极开口54内分别与场沟槽构造21的第一电极24以及沟槽栅极构造31的引出电极36a(第三电极36)电连接。另外,多个源极插头电极57从对应的源极接触开口55进入到源极接触孔39内,分别与源极区38以及接触区40电连接。

179.栅极插头电极56及源极插头电极57具有包含从主面绝缘膜50侧依次层叠的势垒电极58及主电极59的层叠构造。势垒电极58沿着主面绝缘膜50形成为膜状,划分凹陷空间。势垒电极58包含ti层及tin层中的至少1个。主电极59隔着势垒电极58埋设于主面绝缘膜50。主电极59包含钨。

180.参照图1,半导体装置1包含形成于主面绝缘膜50之上的栅极主面电极61。栅极主面电极61经由多个栅极插头电极56与多个沟槽栅极构造31的第二电极35电连接。在图1、图

2、图3以及图7中,栅极主面电极61相对于第二电极35的连接部由

×

标记表示。

181.具体而言,栅极主面电极61一体地包含栅极焊盘电极62以及栅极指状电极63。栅极焊盘电极62是与导线(例如接合线)等外部连接的外部端子部。栅极焊盘电极62形成于在主面绝缘膜50中覆盖第一主面3的焊盘区域16的部分之上。因此,栅极焊盘电极62在俯视图中形成于不与场沟槽构造21、沟槽栅极构造31以及伪沟槽栅极构造41重叠的区域。栅极焊盘电极62在俯视图中形成为四边形形状。

182.栅极指状电极63从栅极焊盘电极62线状地引出到主面绝缘膜50之上,在俯视图中从多个方向划分第一主面3的内侧区域。在本方式中,栅极指状电极63在俯视图中形成为沿着第一侧面5a、第三侧面5c以及第四侧面5d延伸的c字形状使得从3个方向划分第一主面3的内侧区域,使第二侧面5b侧的区域开放。

183.栅极指状电极63与多个栅极插头电极56电连接。栅极指状电极63经由多个栅极插头电极56与多个沟槽栅极构造31的第二电极35电连接。栅极指状电极63关于第一沟槽栅极构造31a,在俯视图中在比位于两端的多个引出电极36a靠内侧的位置与第二电极35电连接(也一并参照图3)。

184.半导体装置1包含从栅极主面电极61起隔开间隔地形成在主面绝缘膜50之上的源极主面电极64。源极主面电极64经由多个源极插头电极57与多个场沟槽构造21的第一电极24、多个沟槽栅极构造31的引出电极36a(第三电极36)、源极区38以及接触区40电连接。在图1、图2、图3以及图7中,源极焊盘电极65相对于第一电极24以及第三电极36的连接部由

×

标记表示。

185.具体而言,源极主面电极64包含源极焊盘电极65。源极焊盘电极65是与导线(例如接合线)等外部连接的外部端子部。源极焊盘电极65形成于在主面绝缘膜50中覆盖活性区10的部分之上。源极焊盘电极65在俯视图中在由栅极主面电极61的内周缘划分出的区域形成为多边形形状。

186.源极焊盘电极65与多个源极插头电极57电连接。源极焊盘电极65经由多个源极插头电极57与场沟槽构造21的第一电极24以及多个沟槽栅极构造31的引出电极36a(第三电极36)电连接。另外,源极焊盘电极65经由多个源极插头电极57与源极区38以及接触区40电连接。

187.栅极主面电极61及源极主面电极64分别包含从主面绝缘膜50侧依次层叠的势垒电极68及主电极69。势垒电极68在主面绝缘膜50之上形成为膜状。势垒电极68包含ti层及tin层中的至少1个。主电极69在势垒电极68之上形成为膜状。主电极69包含纯cu层(纯度为99%以上的cu层)、纯al层(纯度为99%以上的al层)、alsi合金层、alcu合金层以及alsicu合金层中的至少1个。

188.半导体装置1包含形成在第二主面4之上的漏极电极70。漏极电极70覆盖第二主面4的整个区域。漏极电极70在与第二主面4(漏极区6)之间形成欧姆接触。漏极电极70包含ti层、ni层、pd层、au层以及ag层中的至少1个。

189.漏极电极70可以具有将ti层、ni层、pd层、au层以及ag层中的至少2个以任意的顺序层叠而成的层叠构造。漏极电极70可以具有由ti层、ni层、pd层、au层或ag层构成的单层构造。漏极电极70优选包含作为欧姆电极的ti层。在本方式中,漏极电极70具有包含从第二主面4侧依次层叠的ti层、ni层、pd层、au层以及ag层的层叠构造。

190.图8a~图8t是用于对图1所示的半导体装置1的制造方法的一例进行说明的剖视图。图8a~图8t是与图4对应的部分的剖视图。

191.参照图8a,准备成为半导体芯片2的基体(base)的外延晶片81。外延晶片81具有一侧的第一晶片主面82和另一侧的第二晶片主面83。第一晶片主面82和第二晶片主面83分别对应于半导体芯片2的第一主面3和第二主面4。

192.外延晶片81具有包含n

型半导体晶片84和n型外延层85的层叠构造。通过使硅从半导体晶片84的主面外延生长而形成外延层85。半导体晶片84为漏极区6的基体,外延层85为漂移区7的基体。

193.接着,参照图8b,在第一晶片主面82之上形成具有规定图案的硬掩模86。硬掩模86使在第一晶片主面82中应形成多个第一沟槽22、多个第二沟槽32及多个第三沟槽42的区域露出,并覆盖它们以外的区域。硬掩模86可以通过cvd(chemical vapor deposition,化学气相沉积)法或氧化处理法(例如热氧化处理法)来形成。硬掩模86也可以通过利用抗蚀剂掩模(未图示)的蚀刻法进行图案化。

194.接着,第一晶片主面82的不需要的部分通过利用硬掩模86的蚀刻法而被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,多个第一沟槽22、多个第二沟槽32以及多个第三沟槽42形成于第一晶片主面82。然后,除去硬掩模86。

195.接下来,参照图8c,在第一晶片主面82之上形成第一基体绝缘膜87。第一基体绝缘膜87为第一绝缘膜23、第三绝缘膜34以及第五绝缘膜44的基体。第一基体绝缘膜87沿着第一晶片主面82、多个第一沟槽22的壁面、多个第二沟槽32的壁面以及多个第三沟槽42的壁面形成为膜状。第一基体绝缘膜87可以通过cvd法和/或氧化处理法(例如热氧化处理法)来形成。

196.接着,参照图8d,在第一基体绝缘膜87之上形成第一基体电极层88。第一基体电极层88包含导电性多晶硅,为第一电极24、第三电极36以及第五电极46的基体。第一基体电极层88隔着第一基体绝缘膜87填埋多个第一沟槽22、多个第二沟槽32以及多个第三沟槽42,覆盖第一晶片主面82。第一基体电极层88可以通过cvd法来形成。

197.接着,参照图8e,第一基体电极层88的不需要的部分通过蚀刻法被除去,直到第一基体绝缘膜87露出为止。蚀刻法可以是湿蚀刻法和/或干蚀刻法。

198.接着,参照图8f,在第一晶片主面82之上形成具有规定图案的抗蚀剂掩模89。抗蚀剂掩模89覆盖多个第一沟槽22,使多个第二沟槽32和多个第三沟槽42露出。接着,第一基体电极层88的不需要的部分通过利用抗蚀剂掩模89的蚀刻法被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成第一电极24、第三电极36以及第五电极46。

199.接着,参照图8g,第一基体绝缘膜87的不需要的部分通过利用抗蚀剂掩模89的蚀刻法被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成第一绝缘膜23、第三绝缘膜34以及第五绝缘膜44。之后,除去抗蚀剂掩模89。

200.接着,参照图8h,在第一晶片主面82之上形成第二基体绝缘膜90。第二基体绝缘膜90包含氧化硅,为第一中间绝缘膜37和第二中间绝缘膜47的基体。第二基体绝缘膜90填埋多个第二沟槽32和多个第三沟槽42,覆盖第一晶片主面82。第二基体绝缘膜90可以通过cvd法来形成。

201.接着,参照图8i,第二基体绝缘膜90的不需要的部分通过蚀刻法除去直到第一晶

片主面82露出为止。蚀刻法可以是湿蚀刻法和/或干蚀刻法。

202.接着,第二基体绝缘膜90的不需要的部分通过利用抗蚀剂掩模(未图示)的蚀刻法被除去,直到多个第二沟槽32的侧壁和多个第三沟槽42的侧壁露出为止。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成第一中间绝缘膜37和第二中间绝缘膜47。第一中间绝缘膜37的第一中间部分37a的厚度和第二中间绝缘膜47的第二中间部分47a的厚度根据抗蚀剂掩模(未图示)的布局而调整为任意的值。

203.接着,参照图8j,第三基体绝缘膜91沿着第一晶片主面82、多个第二沟槽32的壁面以及多个第三沟槽42的壁面形成为膜状。第三基体绝缘膜91为第二绝缘膜33、第四绝缘膜43以及第一主面绝缘膜51的基体。第三基体绝缘膜91也形成于第一电极24的外表面。第三基体绝缘膜91可以通过cvd法和/或氧化处理法(例如热氧化处理法)来形成。

204.接着,参照图8k,在第三基体绝缘膜91之上形成第二基体电极层92。第二基体电极层92包含导电性多晶硅,是第二电极35以及第四电极45的基体。第二基体电极层92隔着第三基体绝缘膜91填埋多个第二沟槽32和多个第三沟槽42,覆盖第一晶片主面82。第二基体电极层92可以通过cvd法来形成。

205.接着,参照图8l,第二基体电极层92的不需要的部分通过蚀刻法被除去,直到第一主面绝缘膜51露出为止。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成第二电极35和第四电极45。另外,形成多个场沟槽构造21、多个沟槽栅极构造31以及多个伪沟槽栅极构造41。

206.接着,参照图8m,在第一晶片主面82的表层部形成体区20。通过利用离子注入掩模(未图示)的离子注入法来向第一晶片主面82的表层部导入p型杂质,由此,形成体区20。具体而言,体区20的p型杂质从第一晶片主面82以及第二沟槽32的侧壁导入至第一晶片主面82的表层部。

207.另外,在第一晶片主面82的表层部形成源极区38。通过利用离子注入掩模(未图示)的离子注入法向第一晶片主面82的表层部来导入n型杂质,由此,形成源极区38。具体而言,源极区38的n型杂质从第一晶片主面82和第二沟槽32的侧壁导入到第一晶片主面82的表层部。源极区38可以在体区20的形成工序之后形成,也可以在体区20的形成工序之前形成。

208.接下来,参考图8n,在第一主面绝缘膜51之上形成第二主面绝缘膜52。第二主面绝缘膜52一并覆盖多个场沟槽构造21、多个沟槽栅极构造31以及多个伪沟槽栅极构造41。第二主面绝缘膜52包含氧化硅。第二主面绝缘膜52可以通过cvd法来形成。由此,形成包含第一主面绝缘膜51以及第二主面绝缘膜52的主面绝缘膜50。

209.接着,参照图8o,在主面绝缘膜50之上形成具有规定图案的抗蚀剂掩模93。抗蚀剂掩模93使在主面绝缘膜50中应形成多个栅极开口53、多个源极开口54以及多个源极接触开口55的区域露出,并覆盖它们以外的区域。

210.接着,主面绝缘膜50的不需要的部分通过利用抗蚀剂掩模93的蚀刻法被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,在主面绝缘膜50形成多个栅极开口53、多个源极开口54以及多个源极接触开口55。

211.接着,在第一晶片主面82中从多个源极接触开口55露出的部分通过利用多个源极接触开口55的蚀刻法被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,与多个源极接

触开口55连通的多个源极接触孔39形成于第一晶片主面82。抗蚀剂掩模93可以在形成源极接触孔39之后除去,也可以在形成源极接触开口55之后除去。

212.接下来,在体区20的表层部中在沿着源极接触孔39的底壁的区域形成接触区40。通过利用离子注入掩模(未图示)的离子注入法来向源极接触孔39的底壁导入p型杂质,由此,形成接触区40。

213.接着,参照图8p,在主面绝缘膜50之上形成第三基体电极层94。第三基体电极层94为多个栅极插头电极56以及多个源极插头电极57的基体。第三基体电极层94包含从主面绝缘膜50侧依次层叠的势垒电极58及主电极59。势垒电极58包含ti层及tin层中的至少1个。主电极59包含钨。势垒电极58和主电极59可以通过溅射法和/或蒸镀法来分别形成。

214.接着,参照图8q,第三基体电极层94的不需要的部分通过蚀刻法被除去,直到主面绝缘膜50露出为止。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成多个栅极插头电极56以及多个源极插头电极57。

215.接着,参照图8r,在主面绝缘膜50之上形成第四基体电极层95。第四基体电极层95为栅极主面电极61及源极主面电极64的基体。第四基体电极层95包含从主面绝缘膜50侧依次层叠的势垒电极68及主电极69。势垒电极68包含ti层及tin层中的至少1个。主电极69包含纯cu层、纯al层、alsi合金层、alcu合金层以及alsicu合金层中的至少1个。势垒电极68和主电极69可以通过溅射法和/或蒸镀法来分别形成。

216.接着,参照图8s,在第四基体电极层95之上形成具有规定图案的抗蚀剂掩模96。抗蚀剂掩模96覆盖在第四基体电极层95中应形成栅极主面电极61及源极主面电极64的区域,使它们以外的区域露出。接着,第四基体电极层95的不需要的部分通过利用抗蚀剂掩模96的蚀刻法被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成栅极主面电极61及源极主面电极64。

217.接着,参照图8t,在第二晶片主面83之上形成漏极电极70。漏极电极70包含ti层、ni层、pd层、au层以及ag层中的至少1个。漏极电极70可以通过溅射法和/或蒸镀法来形成。之后,选择性地切断外延晶片81,切出多个半导体装置1。经过包含以上的工序,制造半导体装置1。

218.图9是图4的对应图,是用于对不存在伪沟槽栅极构造41的情况下的应力进行说明的剖视图。图10是图4的对应图,是用于对存在伪沟槽栅极构造41的情况下的应力进行说明的剖视图。

219.参照图9,在不存在伪沟槽栅极构造41的情况下,相邻地形成分别具有相互不同的内部构造的场沟槽构造21以及沟槽栅极构造31。具体而言场沟槽构造21包含第一沟槽22及第一绝缘膜23。第一绝缘膜23具有比较厚的第一厚度t1,并形成于第一沟槽22的壁面。场沟槽构造21具有包含第一电极24的单电极构造。第一电极24隔着第一绝缘膜23埋设于第一沟槽22。

220.另一方面,沟槽栅极构造31包含:第二沟槽32、第二绝缘膜33以及第三绝缘膜34。第二绝缘膜33具有比第一厚度t1薄的第二厚度t2,形成于第二沟槽32的上壁面。第三绝缘膜34具有比第二厚度t2厚的第三厚度t3,形成于第二沟槽32的下壁面。

221.沟槽栅极构造31具有包含第二电极35、第三电极36以及第一中间绝缘膜37的分离电极构造。第二电极35隔着第二绝缘膜33埋设于第二沟槽32内的上侧。第三电极36隔着第

三绝缘膜34埋设于第二沟槽32内的下侧。第一中间绝缘膜37介于第二电极35和第三电极36之间,使第二电极35和第三电极36绝缘。

222.这样构造的情况下,在半导体芯片2中,在场沟槽构造21与沟槽栅极构造31之间的区域产生应力。该应力因第一沟槽22内的第一绝缘膜23以及第二沟槽32内的第二绝缘膜33(第三绝缘膜34)的厚度的差异而产生。该应力在将第一沟槽22向第二沟槽32侧拉近的方向上产生。即,该应力包含第一沟槽22侧的拉伸应力(tensile stress)以及第二沟槽32侧的压缩应力(compressive stress)。这种应力成为第一沟槽22与第二沟槽32之间的区域中的结晶缺陷的原因。

223.参照图10,在半导体装置1中,为了避免上述应力的问题,在隔着场沟槽构造21与沟槽栅极构造31对置的区域(非活性区14),形成具有与沟槽栅极构造31对应的构造的伪沟槽栅极构造41。该情况下,相邻地形成沟槽栅极构造31与场沟槽构造21,另一方面,相邻地形成伪沟槽栅极构造41与场沟槽构造21。

224.根据这样的构造,能够在半导体芯片2中在沟槽栅极构造31侧的区域产生第一应力,另一方面,能够在半导体芯片2中在伪沟槽栅极构造41侧的区域产生第二应力。第一应力在将第一沟槽22向第二沟槽32侧拉近的方向上产生,另一方面,第二应力在将第一沟槽22向第三沟槽42侧拉近的方向上产生。即,第二应力在抵消第一应力的方向上产生。由此,能够缓和第一应力和第二应力,因此,能够抑制因应力引起的结晶缺陷。

225.具体而言,伪沟槽栅极构造41包含:第三沟槽42、第四绝缘膜43以及第五绝缘膜44。第四绝缘膜43具有比第一厚度t1薄的第四厚度t4,形成于第三沟槽42的上壁面。第五绝缘膜44具有比第四厚度t4厚的第五厚度t5,形成于第三沟槽42的下壁面。

226.伪沟槽栅极构造41具有包含第四电极45、第五电极46以及第二中间绝缘膜47的伪分离电极构造。第四电极45隔着第四绝缘膜43埋设于第三沟槽42内的上侧。第五电极46隔着第五绝缘膜44埋设于第三沟槽42内的下侧。第二中间绝缘膜47介于第四电极45和第五电极46之间,使第四电极45和第五电极46绝缘。

227.伪沟槽栅极构造41的第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47分别与沟槽栅极构造31的第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37对应。

228.第四电极45以及第五电极46优选形成为电悬浮状态。该情况下,不向第四电极45以及第五电极46供给电力,因此,能够抑制因伪沟槽栅极构造41引起的不期望的电气特性的变动。作为一例,能够抑制因伪沟槽栅极构造41引起的不期望的漏电流的增加、寄生电容的增加。

229.特别是,根据将伪沟槽栅极构造41配置于非活性区14的构造,能够抑制活性区10中的结晶缺陷,同时能够适当地抑制活性区10中的电气特性的变动。场沟槽构造21与伪沟槽栅极构造41之间的台面部48优选不具有体区20。根据该构造,能够适当地抑制因台面部48的构造引起的电气特性的变动。

230.图11是图2的对应图,是表示本发明的第二实施方式的半导体装置101的半导体芯片2的第一主面3的构造的俯视图。图12是图11所示的区域xii的放大图。图13是沿着图12所示的xiii-xiii线的剖视图。图14是沿着图12所示的xiv-xiv线的剖视图。图15是沿着图12所示的xv-xv线的剖视图。图16是图11所示的区域xvi的放大图。以下,对与对半导体装置1

叙述的构造对应的构造标注相同的参照符号,省略它们的说明。

231.参照图11~图16,半导体装置101的第一场沟槽构造21a在本方式中具有包含第一沟槽22、第一绝缘膜23、第一电极24以及绝缘体102的单电极构造。绝缘体102可以称为“场绝缘体”。以与第一实施方式的情况一样的方式形成第一沟槽22。

232.第一绝缘膜23沿着第一沟槽22的下壁面形成为膜状,使第一沟槽22的上壁面露出。具体而言,第一绝缘膜23覆盖相对于体区20的底部位于第一沟槽22的底壁侧的区域的下壁面。第一绝缘膜23的一部分可以与体区20相接。第一绝缘膜23在第一沟槽22的底壁侧的区域中划分u字状的凹陷空间。第一绝缘膜23与漂移区7相接。第一绝缘膜23与第一实施方式的情况一样具有第一厚度t1。

233.第一电极24隔着第一绝缘膜23埋设于第一沟槽22内的下侧。具体而言,第一电极24相对于体区20的底部埋设于第一沟槽22的底壁侧的区域。第一电极24隔着第一绝缘膜23与漂移区7对置。第一电极24的一部分可以隔着第一绝缘膜23与体区20对置。

234.第一电极24包含隔着第一绝缘膜23向第一沟槽22的开口侧引出的1个或多个(在本方式中为3个)引出电极24a。在本方式中,多个引出电极24a在俯视图中形成于第一沟槽22的一侧(第三侧面5c侧)的一端部、另一侧(第四侧面5d侧)的另一端部以及中央部。引出电极24a的配置以及个数是任意的,根据第一沟槽22的长度、布线布局、引出电极36a(第三电极36)的布局等适当调整。

235.绝缘体102埋设于第一沟槽22内的上侧。具体而言,绝缘体102在第一沟槽22内埋设于由第一沟槽22的上壁面、第一绝缘膜23以及第一电极24划分出的凹陷空间。在本方式中,绝缘体102以横穿体区20的底部的深度位置的方式埋设于第一沟槽22。即,绝缘体102包含相对于体区20的底部位于第一主面3侧的部分以及位于第一沟槽22的底壁侧的部分。绝缘体102可以包含氧化硅。

236.第二场沟槽构造21b与第一场沟槽构造21a一样,具有包含第一沟槽22、第一绝缘膜23、第一电极24以及绝缘体102的单电极构造。第二场沟槽构造21b除了第一沟槽22的长度以及引出电极24a(第一电极24)的布局不同这一点之外,具有与第一场沟槽构造21a一样的构造。省略针对第二场沟槽构造21b的具体的说明。

237.第三场沟槽构造21c与第一场沟槽构造21a一样,具有包含第一沟槽22、第一绝缘膜23、第一电极24以及绝缘体102的单电极构造。第三场沟槽构造21c除了第一沟槽22的长度以及引出电极24a(第一电极24)的布局不同这一点以外,具有与第一场沟槽构造21a一样的构造。省略针对第三场沟槽构造21c的具体的说明。

238.多个第一沟槽栅极构造31a与第一实施方式的情况一样,分别具有包含第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37的分离电极构造。第二绝缘膜33在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的绝缘体102对置。第三绝缘膜34在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23对置。

239.第二电极35在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的绝缘体102对置。在本方式中,第二电极35在与第一主面3平行的横向(第二方向y)上不与场沟槽构造21的第一电极24对置。当然,第二电极35的一部分可以在与第一主面3平行的横向(第二方向y)上与第一电极24对置。

240.第三电极36在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一电极24对置。另外,第三电极36的引出电极36a在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的引出电极24a对置。在本方式中,第三电极36在与第一主面3平行的横向(第二方向y)上不与场沟槽构造21的绝缘体102对置。当然,第三电极36的一部分也可以在与第一主面3平行的横向(第二方向y)上与绝缘体102对置。第一中间绝缘膜37在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的绝缘体102对置。

241.多个第二沟槽栅极构造31b与多个第一沟槽栅极构造31a一样,分别具有包含第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37的分离电极构造。第二沟槽栅极构造31b除了第二沟槽32的长度以及引出电极36a(第三电极36)的布局不同这一点之外,具有与第一沟槽栅极构造31a一样的构造。省略针对第二沟槽栅极构造31b的具体的说明。

242.多个第三沟槽栅极构造31c与多个第一沟槽栅极构造31a一样,分别具有包含第二沟槽32、第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36以及第一中间绝缘膜37的分离电极构造。第三沟槽栅极构造31c除了第二沟槽32的长度以及引出电极36a(第三电极36)的布局不同这一点之外,具有与第一沟槽栅极构造31a一样的构造。省略针对第三沟槽栅极构造31c的具体的说明。

243.第一伪沟槽栅极构造41a与第一实施方式的情况一样,具有包含第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47的伪分离电极构造(伪多电极构造)。

244.第四绝缘膜43在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的绝缘体102对置。第四绝缘膜43隔着场沟槽构造21与沟槽栅极构造31的第二绝缘膜33对置。第五绝缘膜44在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23对置。第五绝缘膜44隔着场沟槽构造21与沟槽栅极构造31的第三绝缘膜34对置。

245.第四电极45在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的绝缘体102对置。第四电极45隔着场沟槽构造21与沟槽栅极构造31的第二电极35对置。在本方式中,第四电极45在与第一主面3平行的横向(第二方向y)上不与场沟槽构造21的第一电极24对置。当然,第四电极45的一部分也可以在与第一主面3平行的横向(第二方向y)上与第一电极24对置。

246.第五电极46在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一电极24对置。第五电极46隔着场沟槽构造21与沟槽栅极构造31的第三电极36对置。另外,第五电极46的引出电极46a在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的引出电极24a对置。

247.在本方式中,第五电极46在与第一主面3平行的横向(第二方向y)上不与场沟槽构造21的绝缘体102对置。当然,第五电极46也可以在与第一主面3平行的横向(第二方向y)上与绝缘体102对置。第二中间绝缘膜47在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的绝缘体102对置。

248.第二伪沟槽栅极构造41b与第一伪沟槽栅极构造41a一样,具有包含第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47的伪分离电极构造。第二伪沟槽栅极构造41b除了第三沟槽42的长度以及引出电极46a(第五电极46)的

布局不同这一点以外,具有与第一伪沟槽栅极构造41a一样的构造。省略针对第二伪沟槽栅极构造41b的具体的说明。

249.第三伪沟槽栅极构造41c与第一伪沟槽栅极构造41a一样,具有包含第三沟槽42、第四绝缘膜43、第五绝缘膜44、第四电极45、第五电极46以及第二中间绝缘膜47的伪分离电极构造。第三伪沟槽栅极构造41c除了第三沟槽42的长度以及引出电极46a(第五电极46)的布局不同这一点以外,具有与第一伪沟槽栅极构造41a一样的构造。省略针对第三伪沟槽栅极构造41c的具体的说明。

250.源极主面电极64与第一实施方式的情况一样包含源极焊盘电极65。在本方式中,源极主面电极64经由多个源极插头电极57与多个场沟槽构造21的引出电极24a(第一电极24)以及多个沟槽栅极构造31的引出电极36a(第三电极36)电连接。

251.图17a~图17t是用于对图1所示的半导体装置101的制造方法的一例进行说明的剖视图。图17a~图17t是与图13对应的部分的剖视图。

252.参照图17a,准备成为半导体芯片2的基体的外延晶片81。外延晶片81具有一侧的第一晶片主面82和另一侧的第二晶片主面83。第一晶片主面82和第二晶片主面83分别对应于半导体芯片2的第一主面3和第二主面4。

253.外延晶片81具有包含n

型的半导体晶片84和n型的外延层85的层叠构造。通过使硅从半导体晶片84的主面外延生长而形成外延层85。半导体晶片84为漏极区6的基体,外延层85为漂移区7的基体。

254.接着,参照图17b,在第一晶片主面82之上形成具有规定图案的硬掩模86。硬掩模86使在第一晶片主面82中应形成多个第一沟槽22、多个第二沟槽32及多个第三沟槽42的区域露出,并覆盖它们以外的区域。硬掩模86可以通过cvd法或氧化处理法(例如热氧化处理法)来形成。硬掩模86也可以通过利用抗蚀剂掩模(未图示)的蚀刻法进行图案化。

255.接着,第一晶片主面82的不需要的部分通过利用硬掩模86的蚀刻法被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,在第一晶片主面82形成多个第一沟槽22、多个第二沟槽32以及多个第三沟槽42。然后,除去硬掩模86。

256.接下来,参照图17c,在第一晶片主面82之上形成第一基体绝缘膜87。第一基体绝缘膜87为第一绝缘膜23、第三绝缘膜34以及第五绝缘膜44的基体。第一基体绝缘膜87沿着第一晶片主面82、多个第一沟槽22的壁面、多个第二沟槽32的壁面以及多个第三沟槽42的壁面形成为膜状。第一基体绝缘膜87可以通过cvd法和/或氧化处理法(例如热氧化处理法)来形成。

257.接着,参照图17d,在第一基体绝缘膜87之上形成第一基体电极层88。第一基体电极层88包含导电性多晶硅,为第一电极24、第三电极36以及第五电极46的基体。第一基体电极层88隔着第一基体绝缘膜87填埋多个第一沟槽22、多个第二沟槽32以及多个第三沟槽42,并覆盖第一晶片主面82。第一基体电极层88可以通过cvd法来形成。

258.接着,参照图17e,第一基体电极层88的不需要的部分通过利用抗蚀剂掩模(未图示)的蚀刻法被除去。第一基体电极层88除去直到多个第一沟槽22、多个第二沟槽32以及多个第三沟槽42的深度方向中途部。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成第一电极24(引出电极24a)、第三电极36(引出电极36a)以及第五电极46(引出电极44a)。

259.接着,参照图17f,第一基体绝缘膜87的不需要的部分通过利用抗蚀剂掩模(未图

示)的蚀刻法被除去。除去第一基体绝缘膜87直到多个第一沟槽22、多个第二沟槽32以及多个第三沟槽42的上壁面露出为止。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成第一绝缘膜23、第三绝缘膜34以及第五绝缘膜44。

260.接下来,参照图17g,在第一晶片主面82之上形成第二基体绝缘膜90。第二基体绝缘膜90包含氧化硅,为第一中间绝缘膜37、第二中间绝缘膜47以及绝缘体102的基体。第二基体绝缘膜90填埋多个第二沟槽32和多个第三沟槽42,覆盖第一晶片主面82。第二基体绝缘膜90可以通过cvd法来形成。

261.接着,参照图17h,第二基体绝缘膜90的不需要的部分通过蚀刻法被除去,直到第一晶片主面82露出为止。蚀刻法可以是湿蚀刻法和/或干蚀刻法。

262.接着,参照图17i,在第一晶片主面82之上形成具有规定图案的抗蚀剂掩模103。抗蚀剂掩模103覆盖多个第一沟槽22,使多个第二沟槽32和多个第三沟槽42选择性地露出。接着,通过利用抗蚀剂掩模103的蚀刻法来除去第二基体绝缘膜90的不需要的部分。

263.蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成第一中间绝缘膜37、第二中间绝缘膜47以及绝缘体102。第一中间绝缘膜37的第一中间部分37a的厚度和第二中间绝缘膜47的第二中间部分47a的厚度根据抗蚀剂掩模103的布局而调整为任意的值。然后,除去抗蚀剂掩模103。

264.接着,参照图17j,第三基体绝缘膜91沿着第一晶片主面82、多个第二沟槽32的壁面以及多个第三沟槽42的壁面形成为膜状。第三基体绝缘膜91为第二绝缘膜33、第四绝缘膜43以及第一主面绝缘膜51的基体。第三基体绝缘膜91也形成于第一电极24(引出电极24a)的外表面、第三电极36(引出电极36a)的外表面以及第五电极46(引出电极44a)的外表面。第三基体绝缘膜91可以通过cvd法和/或氧化处理法(例如热氧化处理法)来形成。

265.接着,参照图17k,在第三基体绝缘膜91之上形成第二基体电极层92。第二基体电极层92包含导电性多晶硅,为第二电极35以及第四电极45的基体。第二基体电极层92隔着第三基体绝缘膜91填埋多个第二沟槽32和多个第三沟槽42,覆盖第一晶片主面82。第二基体电极层92可以通过cvd法来形成。

266.接着,参照图17l,第二基体电极层92的不需要的部分通过蚀刻法被除去直到第一主面绝缘膜51露出。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成第二电极35和第四电极45。另外,形成多个场沟槽构造21、多个沟槽栅极构造31以及多个伪沟槽栅极构造41。

267.接着,参照图17m,在第一晶片主面82的表层部形成体区20。通过利用离子注入掩模(未图示)的离子注入法来向第一晶片主面82的表层部导入p型杂质,由此,形成体区20。具体而言,体区20的p型杂质从第一晶片主面82以及第二沟槽32的侧壁导入至第一晶片主面82的表层部。

268.另外,在第一晶片主面82的表层部形成源极区38。通过利用离子注入掩模(未图示)的离子注入法来向第一晶片主面82的表层部导入n型杂质,由此,形成源极区38。具体而言,源极区38的n型杂质从第一晶片主面82和第二沟槽32的侧壁导入到第一晶片主面82的表层部。源极区38可以在体区20的形成工序之后形成,也可以在体区20的形成工序之前形成。

269.接下来,参照图17n,在第一主面绝缘膜51之上形成第二主面绝缘膜52。第二主面绝缘膜52一并覆盖多个场沟槽构造21、多个沟槽栅极构造31以及多个伪沟槽栅极构造41。

第二主面绝缘膜52包含氧化硅。第二主面绝缘膜52可以通过cvd法来形成。由此,形成包含第一主面绝缘膜51以及第二主面绝缘膜52的主面绝缘膜50。

270.接着,参照图17o,在主面绝缘膜50之上形成具有规定图案的抗蚀剂掩模93。抗蚀剂掩模93使在主面绝缘膜50中应形成多个栅极开口53、多个源极开口54以及多个源极接触开口55的区域露出,并覆盖它们以外的区域。

271.接着,主面绝缘膜50的不需要的部分通过利用抗蚀剂掩模93的蚀刻法被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,在主面绝缘膜50形成多个栅极开口53、多个源极开口54以及多个源极接触开口55。

272.接着,在第一晶片主面82中从多个源极接触开口55露出的部分通过利用多个源极接触开口55的蚀刻法被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,与多个源极接触开口55连通的多个源极接触孔39形成于第一晶片主面82。抗蚀剂掩模93可以在形成源极接触孔39之后除去,也可以在形成源极接触开口55之后除去。

273.接下来,接触区40形成于在体区20的表层部中沿着源极接触孔39的底壁的区域。通过利用离子注入掩模(未图示)的离子注入法来向源极接触孔39的底壁导入p型杂质,由此,形成接触区40。

274.接着,参照图17p,在主面绝缘膜50之上形成第三基体电极层94。第三基体电极层94为多个栅极插头电极56以及多个源极插头电极57的基体。第三基体电极层94包含从主面绝缘膜50侧依次层叠的势垒电极58及主电极59。势垒电极58包含ti层及tin层中的至少1个。主电极59包含钨。势垒电极58和主电极59可以通过溅射法和/或蒸镀法来分别形成。

275.接着,参照图17q,第三基体电极层94的不需要的部分通过蚀刻法除去直到主面绝缘膜50露出为止。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成多个栅极插头电极56以及多个源极插头电极57。

276.接着,参照图17r,在主面绝缘膜50之上形成第四基体电极层95。第四基体电极层95为栅极主面电极61及源极主面电极64的基体。第四基体电极层95包含从主面绝缘膜50侧依次层叠的势垒电极68及主电极69。势垒电极68包含ti层及tin层中的至少1个。主电极69包含纯cu层、纯al层、alsi合金层、alcu合金层以及alsicu合金层中的至少1个。势垒电极68和主电极69可以通过溅射法和/或蒸镀法来分别形成。

277.接着,参照图17s,在第四基体电极层95之上形成具有规定图案的抗蚀剂掩模96。抗蚀剂掩模96覆盖在第四基体电极层95中应形成栅极主面电极61及源极主面电极64的区域,使它们以外的区域露出。接着,第四基体电极层95的不需要的部分通过利用抗蚀剂掩模96的蚀刻法被除去。蚀刻法可以是湿蚀刻法和/或干蚀刻法。由此,形成栅极主面电极61及源极主面电极64。

278.接着,参照图17t,在第二晶片主面83之上形成漏极电极70。漏极电极70包含ti层、ni层、pd层、au层以及ag层中的至少1个。漏极电极70可以通过溅射法和/或蒸镀法来形成。之后,选择性地切断外延晶片81,切出多个半导体装置101。经过包含以上内容的工序,制造半导体装置101。

279.以上,通过包含埋设于第一沟槽22内的上侧的绝缘体102的半导体装置101,也能够获得与对半导体装置1叙述的效果一样的效果。

280.图18是图12的对应图,是表示本发明的第三实施方式的半导体装置111的半导体

芯片2的第一主面3的构造的放大图。图19是沿着图18所示的xix-xix线的剖视图。图20是沿着图18所示的xx-xx线的剖视图。半导体装置111具有使第二实施方式的半导体装置101的构造变形的方式。以下,对与对半导体装置101叙述的构造对应的构造标注相同的参照符号,省略它们的说明。

281.参照图18~图20,在半导体装置111中,沟槽栅极构造31具有与场沟槽构造21不同的内部构造。另外,伪沟槽栅极构造41具有与场沟槽构造21不同的内部构造。另外,伪沟槽栅极构造41具有与沟槽栅极构造31不同的内部构造。

282.具体而言,场沟槽构造21具有包含单一电极的单电极构造。另外,沟槽栅极构造31具有包含在上下方向上分割配置的多个电极的多电极构造。另外,伪沟槽栅极构造41具有包含单一电极的伪单电极构造。分别以与第二实施方式的构造一样的方式形成场沟槽构造21以及沟槽栅极构造31。

283.第一伪沟槽栅极构造41a在本方式中,与第二实施方式的构造不同,具有包含第三沟槽42、第五绝缘膜44以及第五电极46且不包含第四绝缘膜43、第四电极45以及第二中间绝缘膜47的伪单电极构造。即,第五绝缘膜44形成覆盖第三沟槽42的壁面的单一的伪绝缘膜,第五电极46形成隔着伪绝缘膜埋设于第三沟槽42的单一的伪电极。第五电极46在第二实施方式的构造中,视为具有包含隔着第五绝缘膜44引出到第三沟槽42的开口侧的整个区域的单一的引出电极46a的构造。

284.具体而言,第五绝缘膜44覆盖第三沟槽42的上壁面以及下壁面。在本方式中,第五绝缘膜44呈膜状覆盖第三沟槽42的壁面的整个区域。第五绝缘膜44在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23、第一电极24(引出电极24a)以及绝缘体104对置。另外,第五绝缘膜44隔着场沟槽构造21与沟槽栅极构造31的第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36(引出电极36a)以及第一中间绝缘膜37对置。

285.具体而言,第五电极46隔着第五绝缘膜44埋设于第三沟槽42的开口侧(上壁面侧)以及底侧(下壁面侧)。在本方式中,第五电极46在与第一主面3平行的横向(第二方向y)上与场沟槽构造21的第一绝缘膜23、第一电极24(引出电极24a)以及绝缘体104对置。另外,第五电极46隔着场沟槽构造21与沟槽栅极构造31的第二绝缘膜33、第三绝缘膜34、第二电极35、第三电极36(引出电极36a)以及第一中间绝缘膜37对置。

286.第二伪沟槽栅极构造41b与第一伪沟槽栅极构造41a一样,具有包含第三沟槽42、第五绝缘膜44以及第五电极46的伪单电极构造。第二伪沟槽栅极构造41b除了第三沟槽42的长度不同这一点以外,具有与第一伪沟槽栅极构造41a一样的构造。省略针对第二伪沟槽栅极构造41b的具体的说明。

287.第三伪沟槽栅极构造41c与第一伪沟槽栅极构造41a一样,具有包含第三沟槽42、第五绝缘膜44以及第五电极46的伪单电极构造。第三伪沟槽栅极构造41c除了第三沟槽42的长度不同这一点以外,具有与第一伪沟槽栅极构造41a一样的构造。省略针对第三伪沟槽栅极构造41c的具体的说明。

288.在本方式中,主面绝缘膜50覆盖多个伪沟槽栅极构造41(多个第五电极46的露出部)的整个区域,使多个伪沟槽栅极构造41从外部绝缘分离。即,主面绝缘膜50使多个第五电极46与第五绝缘膜44一起孤立为电悬浮状态。

289.以上,通过半导体装置111,也获得与对半导体装置1描述的效果一样的效果。

290.本发明的实施方式还能够以其他方式实施。

291.在上述的各实施方式中,对体区20在台面部48中不形成于第一主面3的表层部的例子进行了说明。但是,体区20也可以在台面部48中形成于第一主面3的表层部。该情况下,伪沟槽栅极构造41的第四绝缘膜43也可以以与沟槽栅极构造31的第二绝缘膜33一样的方式与体区20相接。另外,伪沟槽栅极构造41的第四电极45也可以以与沟槽栅极构造31的第二电极35一样的方式,隔着第四绝缘膜43与体区20对置。

292.在所述的各实施方式中,对沟槽栅极构造31的第三电极36形成为场电极,作为基准电位的源极电位(例如接地电位)施加于第三电极36的例子进行了说明。但是,也可以将第三电极36形成为栅极电极,将作为控制电位的栅极电位施加于第三电极36。即,第三电极36也可以固定为与第二电极35相同的电位,另一方面,也可以固定为与第一电极24不同的电位。该情况下,栅极主面电极61(栅极指状电极63)经由栅极插头电极56与第三电极36的引出电极36a电连接。

293.在上述的各实施方式中,对源极主面电极64不与位于两端的多个引出电极36a以及多个引出电极46a连接的例子进行了说明。但是,源极主面电极64也可以经由多个源极插头电极57与位于两端的多个引出电极36a以及多个引出电极46a连接。该情况下,源极主面电极64可以包含以与位于两端的多个引出电极36a以及多个引出电极46a连接的方式从源极焊盘电极65呈线状引出的源极指状电极。

294.在上述的各实施方式中,对“第一导电型”为“n型”,“第二导电型”为p型的例子进行了说明,但也可以是“第一导电型”为“p型”,“第二导电型”为“n型”。该情况下的具体结构通过在上述的说明以及附图中将“n型区域”置换为“p型区域”,将“n型区域”置换为“p型区域”而得到。

295.以下,表示从本说明书以及附图提取的特征的例子。以下的[a1]~[a20]和[b1]~[b20]提供能够抑制半导体芯片的结晶缺陷的半导体装置。以下,括号内的字母数字表示所述的实施方式中的对应构成要素等,但并不是将各项的范围限定于实施方式的意思。

[0296]

[a1]一种半导体装置,包含:半导体芯片(2),其具有主面(3);第一槽(22),其形成于所述主面(3),将所述主面(3)划分为第一区域(10)和第二区域(14);第一绝缘膜(23),其形成于所述第一槽(22)的壁面;第二槽(32),其从所述第一槽(22)起隔开间隔地形成于所述第一区域(10)的所述主面(3);第二绝缘膜(33),其覆盖所述第二槽(32)的上壁面,且比所述第一绝缘膜(23)薄;第三绝缘膜(34),其覆盖所述第二槽(32)的下壁面,且比所述第二绝缘膜(33)厚;第三槽(42),其从所述第一槽(22)起隔开间隔地形成于所述第二区域(14)的所述主面(3);第四绝缘膜(43),其覆盖所述第三槽(42)的上壁面,且比所述第一绝缘膜(23)薄;以及第五绝缘膜(44),其覆盖所述第三槽(42)的下壁面,且比所述第四绝缘膜(43)厚。

[0297]

[a2]根据a1所述的半导体装置,其中,所述第一区域(10)是活性区(10),所述第二区域(14)是所述活性区(10)外的非活性区(14)。

[0298]

[a3]根据a1或a2所述的半导体装置,其中,所述半导体装置还包含:第一电极(24),其隔着所述第一绝缘膜(23)埋设于所述第一槽(22);第二电极(35),其隔着所述第二绝缘膜(33)埋设于所述第二槽(32)的上侧;第三电极(36),其隔着所述第三绝缘膜(34)埋设于所述第二槽(32)的下侧;第四电极(45),其隔着所述第四绝缘膜(43)埋设于所述第三

槽(42)的上侧;以及第五电极(46),其隔着所述第五绝缘膜(44)埋设于所述第三槽(42)的下侧。

[0299]

[a4]根据a3所述的半导体装置,其中,电悬浮状态的所述第四电极(45)埋设于所述第三槽(42)的上侧,电悬浮状态的所述第五电极(46)埋设于所述第三槽(42)的下侧。

[0300]

[a5]根据a3或a4所述的半导体装置,其中,所述半导体装置还包含:第一中间绝缘膜(37),其介于所述第二电极(35)与所述第三电极(36)之间;以及第二中间绝缘膜(47),其介于所述第四电极(45)与所述第五电极(46)之间。

[0301]

[a6]根据a5所述的半导体装置,其中,所述第一中间绝缘膜(37)比所述第二绝缘膜(33)厚,所述第二中间绝缘膜(47)比所述第四绝缘膜(43)厚。

[0302]

[a7]根据a3~a6中任一项所述的半导体装置,其中,对所述第一电极(24)施加基准电位,对所述第二电极(35)施加控制电位,对所述第三电极(36)施加所述基准电位或所述控制电位。

[0303]

[a8]根据a7所述的半导体装置,其中,对所述第三电极(36)施加所述基准电位。

[0304]

[a9]根据a3~a8中任一项所述的半导体装置,其中,所述第三电极(36)包含:1个或多个第一引出电极(36a),其隔着所述第三绝缘膜(34)向所述第二槽(32)的开口侧引出,所述第五电极(46)包含:1个或多个第二引出电极(46a),其隔着所述第五绝缘膜(44)向所述第三槽(42)的开口侧引出。

[0305]

[a10]根据a9所述的半导体装置,其中,所述第二引出电极(46a)隔着所述第一槽(22)与所述第一引出电极(36a)对置。

[0306]

[a11]根据a1~a10中任一项所述的半导体装置,其中,还包含:体区(20),其形成于所述主面(3)的表层部,所述第二槽(32)贯通所述体区(20)。

[0307]

[a12]根据a11所述的半导体装置,其中,所述第三槽(42)在与所述第一槽(22)之间划分由所述半导体芯片(2)的一部分构成的台面部(48),所述体区(20)不形成于所述台面部(48)。

[0308]

[a13]根据a11或a12所述的半导体装置,其中,所述半导体装置还包含:源极区(38),其在所述体区(20)的表层部中形成于沿着所述第二槽(32)的区域。

[0309]

[a14]根据a1~a13中任一项所述的半导体装置,其中,所述第一槽(22)在俯视图中形成为带状,所述第二槽(32)在俯视图中形成为与所述第一槽(22)平行地延伸的带状,所述第三槽(42)在俯视图中形成为与所述第一槽(22)平行地延伸的带状。

[0310]

[a15]根据a1~a14中任一项所述的半导体装置,其中,包含多个所述第二槽(32)。

[0311]

[a16]根据a15所述的半导体装置,其中,隔开0.1μm以上且2μm以下的间隔地形成多个所述第二槽(32)。

[0312]

[a17]根据a1~a16中任一项所述的半导体装置,其中,从所述第一槽(22)起隔开0.1μm以上且2μm以下的间隔(p2)地形成所述第二槽(32),从所述第一槽(22)起隔开0.1μm以上且2μm以下的间隔(p3)地形成所述第三槽(42)。

[0313]

[a18]根据a1~a17中任一项所述的半导体装置,其中,所述半导体装置还包含:主面绝缘膜(50),其形成于所述主面(3)之上,并使所述第三槽(42)与外部绝缘。

[0314]

[a19]根据a1~a18中任一项所述的半导体装置,其中,所述第一槽(22)具有0.5μm以上且3μm以下的宽度(w1),所述第二槽(32)具有0.5μm以上且3μm以下的宽度(w2),所述第

三槽(42)具有0.5μm以上且3μm以下的宽度(w3)。

[0315]

[a20]根据a1~a19中任一项所述的半导体装置,其中,所述第一槽(22)具有1μm以上且10μm以下的深度(d1),所述第二槽(32)具有1μm以上且10μm以下的深度(d2),所述第三槽(42)具有1μm以上且10μm以下的深度(d3)。

[0316]

[b1]一种半导体装置,其中,包含:半导体芯片(2),其具有主面(3);场沟槽构造(21),其形成于所述主面(3),并在所述主面(3)划分活性区(10)和非活性区(11);沟槽栅极构造(31),其从所述场沟槽构造(21)起隔开间隔地形成于所述活性区(10),并与所述场沟槽构造(21)对置;以及伪沟槽构造(41),其从所述场沟槽构造(21)起隔开间隔地形成于所述非活性区(11),并隔着所述场沟槽构造(21)与所述沟槽栅极构造(31)对置。

[0317]

[b2]根据b1所述的半导体装置,其中,所述伪沟槽构造(41)从所述沟槽栅极构造(31)电隔离。

[0318]

[b3]根据b1或b2所述的半导体装置,其中,所述伪沟槽构造(41)从所述场沟槽构造(21)电隔离。

[0319]

[b4]根据b1~b3中任一项所述的半导体装置,其中,所述伪沟槽构造(41)形成为电悬浮状态。

[0320]

[b5]根据b1~b4中任一项所述的半导体装置,其中,所述沟槽栅极构造(31)具有与所述场沟槽构造(21)不同的内部构造。

[0321]

[b6]根据b1~b5中任一项所述的半导体装置,其中,所述伪沟槽构造(41)具有与所述场沟槽构造(21)不同的内部构造。

[0322]

[b7]根据b1~b6中任一项所述的半导体装置,其中,所述伪沟槽构造(41)具有与所述沟槽栅极构造(31)不同的内部构造。

[0323]

[b8]根据b1~b7中任一项所述的半导体装置,其中,所述场沟槽构造(21)具有包含单一电极的单电极构造,所述沟槽栅极构造(31)具有包含在上下方向上分割配置的多个电极的多电极构造,所述伪沟槽构造(41)具有包含单一电极的单电极构造。

[0324]

[b9]根据b8所述的半导体装置,其中,所述场沟槽构造(21)包含:场沟槽(22),其形成于所述主面(3);场电极(24),其埋设于所述场沟槽(22)的底壁侧;以及场绝缘体(102),其埋设于所述场沟槽(22)的开口侧。

[0325]

[b10]根据b9所述的半导体装置,其中,所述沟槽栅极构造(31)包含:栅极沟槽(32),其形成于所述主面(3);上侧电极(35),其埋设于所述栅极沟槽(32)的开口侧;以及下侧电极(36),其埋设于所述栅极沟槽(32)的底壁侧,所述上侧电极(35)隔着所述半导体芯片(2)的一部分与所述场绝缘体(102)对置,所述下侧电极(36)隔着所述半导体芯片(2)的一部分与所述场电极(24)对置。

[0326]

[b11]根据b10所述的半导体装置,其中,所述场沟槽构造(21)包含:第一引出电极(24a),其从所述场电极(24)向所述场沟槽(22)的开口侧引出,所述沟槽栅极构造(31)包含:第二引出电极(36a),其从所述下侧电极(36)向所述栅极沟槽(32)的开口侧引出。

[0327]

[b12]根据b10或b11所述的半导体装置,其中,所述沟槽栅极构造(31)包含:中间绝缘膜(37),其介于所述上侧电极(35)与所述下侧电极(36)之间,所述中间绝缘膜(37)隔着所述半导体芯片(2)的一部分与所述场绝缘体(102)对置。

[0328]

[b13]根据b11或b12所述的半导体装置,其中,对所述上侧电极(35)赋予栅极电

位,对所述下侧电极(36)赋予与所述场电极(24)相同的电位。

[0329]

[b14]根据b9~b13中任一项所述的半导体装置,其中,所述伪沟槽构造(41)包含:伪沟槽(42),其形成于所述主面(3);以及伪电极(46),其埋设于所述伪沟槽(42),所述伪电极(46)隔着所述半导体芯片(2)的一部分与所述场电极(24)以及所述场绝缘体(102)对置。

[0330]

[b15]根据b1~b7中任一项所述的半导体装置,其中,所述场沟槽构造(21)包含:场沟槽(22),其形成于所述主面(3);以及场绝缘膜(23),其覆盖所述场沟槽(22)的壁面,所述沟槽栅极构造(31)包含:栅极沟槽(32),其形成于所述主面(3);上侧绝缘膜(33),其覆盖所述栅极沟槽(32)的上壁面;以及下侧绝缘膜(34),其覆盖所述栅极沟槽(32)的下壁面,所述伪沟槽构造(41)包含:伪沟槽(42),其形成于所述主面(3);以及伪绝缘膜(44),其覆盖所述伪沟槽(42)的壁面,所述上侧绝缘膜(33)比所述场绝缘膜(23)薄,所述下侧绝缘膜(34)比所述上侧绝缘膜(33)厚,所述伪绝缘膜(44)比所述上侧绝缘膜(33)厚。

[0331]

[b16]根据b1~b15中任一项所述的半导体装置,其中,所述场沟槽构造(21)在俯视图中形成为在一方向上延伸的带状,所述沟槽栅极构造(31)在俯视图中形成为相对于所述场沟槽构造(21)平行地延伸的带状,所述伪沟槽构造(41)在俯视图中形成为相对于所述场沟槽构造(21)平行地延伸的带状。

[0332]

[b17]根据b1~b16中任一项所述的半导体装置,其中,从所述场沟槽构造(21)起隔开第一间隔(p2)地形成所述沟槽栅极构造(31),从所述场沟槽构造(21)起隔开与所述第一间隔(p2)大致相等的第二间隔(p3)地形成所述伪沟槽构造(41)。

[0333]

[b18]根据b1~b17中任一项所述的半导体装置,其中,以与所述场沟槽构造(21)大致相等的深度(d1≈d2)形成所述沟槽栅极构造(31),以与所述场沟槽构造(21)大致相等的深度(d1≈d3)形成所述伪沟槽构造(41)。

[0334]

[b19]根据b1~b18中任一项所述的半导体装置,其中,多个所述沟槽栅极构造(31)从所述场沟槽构造(21)起隔开间隔地形成于所述活性区(10),单一的所述伪沟槽构造(41)从所述场沟槽构造(21)起隔开间隔地形成于所述非活性区(11)。

[0335]

[b20]根据b1~b19中任一项所述的半导体装置,其中,所述半导体装置还包含:体区(20),其形成于所述主面(3)的表层部,所述场沟槽构造(21)贯通所述体区(20),所述沟槽栅极构造(31)贯通所述体区(20),所述伪沟槽构造(41)不贯通所述体区(20)。

[0336]

对本发明的实施方式进行了详细说明,但这些只不过是为了明确本发明的技术内容而使用的具体例,本发明不应被解释为限定于这些具体例,本发明的范围由所附的权利要求书所限定。

[0337]

符号说明

[0338]

1 半导体装置

[0339]

2 半导体芯片

[0340]

3 第一主面

[0341]

10 活性区(第一区域)

[0342]

14 非活性区(第二区域)

[0343]

20 体区

[0344]

22 第一沟槽(第一槽)

[0345]

23 第一绝缘膜

[0346]

24 第一电极

[0347]

32 第二沟槽(第二槽)

[0348]

33 第二绝缘膜

[0349]

34 第三绝缘膜

[0350]

35 第二电极

[0351]

36 第三电极

[0352]

37 第一中间绝缘膜

[0353]

38 源极区

[0354]

42 第三沟槽(第三槽)

[0355]

43 第四绝缘膜

[0356]

44 第五绝缘膜

[0357]

45 第四电极

[0358]

46 第五电极

[0359]

47 第二中间绝缘膜

[0360]

48 台面部

[0361]

50 主面绝缘膜

[0362]

101 半导体装置。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。