具有电过应力完整性的高电压隔离屏障

背景技术:

1.许多电路包含多个电压域中的电路系统,例如低电压域中的低电压逻辑电路系统及第二高电压域中的通信驱动器电路。在正常操作中,高电压数字隔离器提供不同电压域之间的通信通道,同时保护低电压电路对抗因高电压域上的有害电流或电压造成装置降级。电路系统中在高电压隔离屏障组件附近的电过应力(eos)事件可能潜在地损坏高电压屏障,使其不能够将低电压电路系统与高电压域隔离。

技术实现要素:

2.在一个方面中,一种电子装置包含半导体层上方的多层级金属化结构,以及第一区域中的隔离组件,及所述金属化结构的所述第一区域与第二区域之间的导电屏蔽件。所述金属化结构包含所述半导体层上的预金属层级及所述预金属层级上方的金属化结构层级。所述隔离组件包含位于不同的金属化结构层级中的第一与第二端子。所述导电屏蔽件包含包围所述相应金属化结构层级中的所述第一区域的经互连金属线及沟槽通路。在一个实例中,所述隔离组件是电容器。在另一实例中,所述隔离组件是变压器。在一个实例中,所述隔离组件的所述第二端子位于顶部或最终金属化结构层级中且包含经暴露侧。在一个实例中,所述第一区域包含多个隔离组件。在一个实例中,所述金属化结构层级中的一者包含具有间隙的金属线,以及延伸穿过所述隔离组件且连接到所述隔离组件的所述第一端子的金属布线特征。在一个实例中,所述导电屏蔽件在侧视立面图中具有阶梯形状。

3.本公开的另一方面中提供一种封装式电子装置。所述封装式电子装置在所述装置内包含第一及第二半导体裸片。所述裸片及电连接围封于具有部分暴露的引线的封装结构中。所述第一半导体裸片包含半导体层、所述半导体层上方的具有第一及第二区域的多层级金属化结构、所述金属化结构的第一区域中的隔离组件,以及所述第一与第二区域之间的具有经互连金属线及沟槽通路的导电屏蔽件。在一个实例中,所述导电屏蔽件具有阶梯形状。在一个实例中,所述隔离组件是电容器。在另一实例中,所述隔离组件是变压器。在一个实例中,所述第二裸片还包含第二半导体层、所述第二半导体层上方的具有第一及第二区域的第二多层级金属化结构、所述第二金属化结构的第一区域中的第二隔离组件。

4.另一方面提供一种方法,其包含在半导体层上方形成多层级金属化结构,所述多层级金属化结构具有第一及第二区域以及所述第一与第二区域之间的具有经互连金属线及沟槽通路的导电屏蔽件。所述方法还包含:自晶片分离出包含所述半导体层及所述多层级金属化结构的第一半导体裸片,在隔离组件的第二端子与第二半导体裸片的导电特征之间形成电连接,及将所述第一半导体裸片、所述第二半导体裸片及所述电连接围封于封装结构中,所述封装结构具有沿着所述封装结构的一或多个侧暴露的导电引线。

附图说明

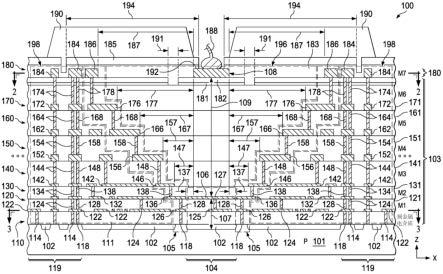

5.图1是在半导体层上面的多层级金属化结构中的由导电屏蔽件包围的第一区域中具有隔离电容器的电子装置的部分截面侧视立面图。

6.图2是沿着图1的电子装置中的线2-2截取的部分截面俯视平面图。

7.图3是沿着图1的电子装置中的线3-3截取的部分截面俯视平面图。

8.图4是包含图1到3的装置的封装式电子装置的示意图。

9.图5是制作封装式电子装置的方法的流程图。

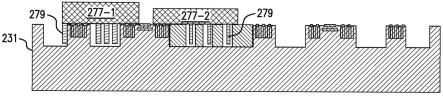

10.图6到25是经历根据图5的方法的金属化结构制作处理的图1到3的装置的部分截面侧视立面图。

11.图26是展示经历导线接合的引线框架的一部分与所附接半导体裸片的部分俯视平面图。

12.图27是封装式电子装置的透视图。

13.图28是在半导体层上面的多层级金属化结构中的由导电屏蔽件包围的第一区域中具有隔离变压器的另一电子装置的部分截面侧视立面图。

14.图29是沿着图28的电子装置中的线29-29截取的部分俯视平面图。

15.图30是沿着图28的电子装置中的线30-30截取的部分俯视平面图。

具体实施方式

16.在图式中,相似参考编号始终是指相似元件,且各种特征未必按比例绘制。并且,术语“耦合(couple)”包含间接或直接电或机械连接或者其组合。举例来说,如果第一装置耦合到第二装置或与第二装置耦合,那么所述连接可为通过直接电连接,或通过经由一或多个介入装置及连接的间接电连接。下文中在功能的上下文中描述各种电路、系统及/或组件的一或多个操作特性,在一些情形中,所述功能是由在电路系统正被供电及操作时各种结构的配置及/或互连所致。

17.最初参考图1到3,图1展示电子装置100的部分截面侧视图,且图2及3展示沿着图1中的线2-2及3-3截取的电子装置100的部分的相应俯视截面图。电子装置100包含半导体层101。在一个实例中,半导体层101是或包含在半导体层101的顶部侧上或中形成有隔离结构102(例如,浅沟槽隔离或sti结构)的p型半导体材料。在一个实例中,半导体层101是硅层、硅-锗层、绝缘体上硅(soi)结构,或具有半导体材料的另一层。电子装置100进一步包含安置于半导体层101的顶部侧上方的多层级金属化结构103。另外,电子装置100在多层级金属化结构103中包含隔离组件104及导电屏蔽件105。

18.如下文进一步论述,隔离组件104是在多层级金属化结构103的第一区域中,且导电屏蔽件105由多层级金属化结构的经互连金属线及沟槽通路形成以提供围绕隔离组件104的法拉第笼。导电屏蔽件105将所述第一区域与多层级金属化结构103的外围第二区域分隔开。在一个实施方案中,电子装置100还包含形成于半导体层101上及/或中多层级金属化结构103的外围第二区域下方的其它电路系统(例如,低电压逻辑电路,未展示)。

19.在图1的实例中,隔离组件104是包含与半导体层101间隔开距离107(例如,2.8μm)的第一(例如,下部或底部)端子106(例如,第一电容器板)的电容器。如下文进一步论述,在一个实例中,导电屏蔽件105包含组成金属层中的一者中的间隙,且导电布线特征将所述第二区域的低电压逻辑电路系统连接到隔离组件104的第一端子106。电容器104还包含第二(例如,上部或顶部)端子108(例如,第二电容器板)。在此实例中,第一端子106与第二端子108大体上彼此平行,尽管这并不是所有可能实施方案的严格要求。另外,第一端子106与第

二端子108彼此分隔开距离109(例如,12.7μm),端子106与108之间具有介电材料层以形成电容器104。在所图解说明的实例中,电容器隔离组件104的第二端子108包含经暴露顶部侧,从而允许第二端子108成为第二半导体裸片(例如,下文的图4及26)的高电压域端子(例如,接合导线)。

20.多层级金属化结构103包含预金属层级110及整数n个金属化结构层级,其中n大于3。图1到3的实例包含n=7个金属化结构层级。预金属层级110包含半导体层101上的预金属电介质(pmd)层111。在一个实例中,pmd层111是或包含具有约1.2μm的厚度的二氧化硅(sio2)。预金属层级110包含半导体层101上的圆柱形接点114及预金属沟槽接点118。接点114及118沿着图1中的垂直(例如,z)方向延伸穿过pmd层111。沟槽接点118包围预金属层级110中的pmd层111的中央第一部分,其间不具有间隙。在一个实例中,预金属层级接点114及沟槽接点118是或包含钨。在所图解说明的实例中,预金属沟槽接点118连接到半导体层101以在sti区段102之间形成接地连接(如图1中所展示)以便提供导电屏蔽件105的操作为围绕隔离组件104的接地法拉第笼的下部区段。预金属层级110还在电子装置100的所图解说明部分的外周边附近的区域119中包含沟槽接点118,例如以提供对抗装置100上的裂缝及机械应力的保护,尽管这并不是所有可能实施方案的严格要求。

21.如图1及3中所展示,多层级金属化结构103还包含预金属层级110上的第一金属化结构层级120(例如,在图1中标记为m1)。第一金属化结构层级120包含第一层级间电介质(ild)层121以及多层级金属化结构103的第二部分中的导电金属线122及圆柱形钨通路124。第一金属化结构层级120还包含多层级金属化结构103的第一部分中的金属布线特征125、第一金属线126、金属布线特征125上的布线通路127。在一个实例中,第一金属线126是或包含沿着图1中的z方向具有大约0.61μm的厚度的铝金属。另外,第一金属化结构层级120包含第一金属线126上的第一沟槽通路128。第一ild层121在pmd层111、金属布线特征125及第一金属线126上延伸。第一金属线126至少部分地在预金属沟槽接点118上延伸,且第一沟槽通路128在第一金属线126上延伸。第一沟槽通路128及第一金属线126在第一金属化结构层级120中包围多层级金属化结构103的第一区域的另一部分。在一个实例中,第一ild层121是或包含具有大约1.2μm的厚度(例如,沿着图1中的z方向)的二氧化硅(sio2)。

22.如图3中所展示,金属布线特征125从第一区域穿过第一金属线126中的间隙g延伸到第一金属化结构层级120的第二区域。第一金属化结构层级120还在电子装置100的所图解说明部分的外周边附近的区域119中包含沟槽通路128,例如以提供对装置100上的裂缝及机械应力的减小,尽管这并不是所有可能实施方案的严格要求。第一金属化结构层级120及图1到3的实例中的其它金属化结构层级包含是或包含钨的通路114及沟槽接点118,尽管这并不是所有可能实施方案的要求。另外,第一金属化结构层级120及多层级金属化结构103的其它金属化结构层级包含是或包含铝或铜的金属线,尽管这并不是所有可能实施方案的要求。

23.第二金属化结构层级130(在图1中标记为m2)在多层级金属化结构103中在第一金属化结构层级120上延伸。第二金属化结构层级130包含第二ild层131以及多层级金属化结构103的第二部分中的导电金属线132及圆柱形钨通路134。在一个实例中,第二ild层131是或包含沿着z具有大约1.2μm的厚度的二氧化硅。第二金属化结构层级130进一步包含至少部分地在第一沟槽通路128上的第二金属线136及第二金属线136上的第二沟槽通路138。在

一个实例中,第二金属线136是或包含沿着图1中的z方向具有大约0.61μm的厚度的铝金属。第二金属化结构层级130还包含隔离组件104的与第二金属线136间隔开且至少部分地在第二金属化结构层级130的中央第一部分中在金属布线特征125上的布线通路127上方延伸的第一端子106。在此实例中,第二ild层131在第一ild层121、第二金属线136及第一端子106上延伸。第二沟槽通路138在第二金属线136上延伸。第二沟槽通路138及第二金属线136包围第二金属化结构层级130的第一区域的第二部分。如图1中所展示,隔离组件104的第二端子108包含横向边缘(图1中的左侧及右侧),且相应第一金属线126及第二金属线136包含沿着第一方向(例如,图1到3中的x方向)与第二端子108的相应横向边缘间隔开相应非零间隔距离137的相对横向边缘。第二金属化结构层级130还在电子装置100的所图解说明部分的外周边附近的区域119中包含沟槽通路138,尽管这并不是所有可能实施方案的严格要求。

24.多层级金属化结构103还包含第三金属化结构层级140(在图1中标记为m3)。第三金属化结构层级140在多层级金属化结构103中在第二金属化结构层级130上延伸。第三金属化结构层级140包含第三ild层141以及多层级金属化结构103的第二部分中的导电金属线142及圆柱形钨通路144。在一个实例中,第三ild层141是或包含沿着z具有大约2.5μm的厚度的二氧化硅。第三金属化结构层级140进一步包含至少部分地在第二沟槽通路138上的第三金属线146及第三金属线146上的第三沟槽通路148。在一个实例中,第三金属线146是或包含沿着图1中的z方向具有大约0.61μm的厚度的铝金属。在此实例中,第三ild层141在第二ild层131及第三金属线146上延伸。第三沟槽通路148在第三金属线146上延伸穿过第三ild层141。第三沟槽通路148及第三金属线146包围第三金属化结构层级140的第一区域的一部分。如图1中所展示,第三金属线146包含沿着x方向与第二端子108的相应横向边缘间隔开非零间隔距离147的横向边缘。图1到3中的导电屏蔽件105包含图1中所展示的阶梯形状,其中非零间隔距离147(例如,大约30μm)大于前一(例如,下伏)第二金属化结构层级130的间隔距离137。第三金属化结构层级140还在电子装置100的所图解说明部分的外周边附近的区域119中包含沟槽通路148,尽管这并不是所有可能实施方案的严格要求。

25.第四金属化结构层级150(在图1中标记为m4)在多层级金属化结构103中在第三金属化结构层级140上延伸。第四金属化结构层级150包含第四ild层151以及多层级金属化结构103的第二部分中的导电金属线152及圆柱形钨通路154。在一个实例中,第四ild层151是或包含沿着z具有大约3.2μm的厚度的二氧化硅。第四金属化结构层级150进一步包含至少部分地在第三沟槽通路148上的第四金属线156及第四金属线156上的第四沟槽通路158。在一个实例中,第四金属线146是或包含沿着图1中的z方向具有大约1.3μm的厚度的铝金属。在此实例中,第四ild层151在第三ild层141及第四金属线156上延伸。第四沟槽通路158在第四金属线156上延伸穿过第四ild层151。第四沟槽通路158及第四金属线156包围第四金属化结构层级150的第一区域的一部分。如图1中所展示,第四金属线156包含沿着x方向与第二端子108的相应横向边缘间隔开大于前一(例如,下伏)第三金属化结构层级140的间隔距离147的非零间隔距离157(例如,大约40μm)的横向边缘。第四金属化结构层级150还在电子装置100的所图解说明部分的外周边附近的区域119中包含沟槽通路158,尽管这并不是所有可能实施方案的严格要求。

26.多层级金属化结构103还包含在多层级金属化结构103中在第四金属化结构层级150上延伸的第五金属化结构层级160(在图1中标记为m5)。第五金属化结构层级160包含第

五ild层161以及多层级金属化结构103的第二部分中的导电金属线162及圆柱形钨通路164。在一个实例中,第五ild层161是或包含沿着z具有大约3.2μm的厚度的二氧化硅。第五金属化结构层级160进一步包含至少部分地在第四沟槽通路158上的第五金属线166及第五金属线166上的第五沟槽通路168。在一个实例中,第五金属线166是或包含沿着图1中的z方向具有大约1.3μm的厚度的铝金属。在此实例中,第五ild层161在第四ild层151及第五金属线166上延伸。第五沟槽通路168在第五金属线166上延伸穿过第五ild层161。第五沟槽通路168及第五金属线166包围第五金属化结构层级160的第一区域的一部分。如图1中所展示,第五金属线166包含沿着x方向与第二端子108的相应横向边缘间隔开大于前一(例如,下伏)第四金属化结构层级150的间隔距离157的非零间隔距离167(例如,大约50μm)的横向边缘。第五金属化结构层级160还在电子装置100的所图解说明部分的外周边附近的区域119中包含沟槽通路168,尽管这并不是所有可能实施方案的严格要求。

27.第六金属化结构层级170(在图1中标记为m6)在多层级金属化结构103中在第五金属化结构层级160上延伸。第六金属化结构层级170包含第六ild层171以及多层级金属化结构103的第二部分中的导电金属线172及圆柱形钨通路174。在一个实例中,第六ild层171是或包含沿着z具有大约3.2μm的厚度的二氧化硅。第六金属化结构层级170进一步包含至少部分地在第五沟槽通路168上的第六金属线176及第六金属线176上的第六沟槽通路178。在一个实例中,第六金属线176是或包含沿着图1中的z方向具有大约1.3μm的厚度的铝金属。在此实例中,第六ild层171在第五ild层161及第六金属线176上延伸。第六沟槽通路178在第六金属线176上延伸穿过第六ild层171。第六沟槽通路178及第六金属线176包围第六金属化结构层级170的第一区域的一部分。如图1中所展示,第六金属线176包含沿着x方向与第二端子108的相应横向边缘间隔开大于前一(例如,下伏)第五金属化结构层级160的间隔距离167的非零间隔距离177(例如,大约70μm)的横向边缘。第六金属化结构层级170还在电子装置100的所图解说明部分的外周边附近的区域119中包含沟槽通路178,尽管这并不是所有可能实施方案的严格要求。

28.图1到3中的实例多层级金属化结构103具有n个金属化结构层级,其中n=7。最上部或顶部(例如,第n或第七)金属化结构层级180(在图1中标记为m7)在多层级金属化结构103中在第六金属化结构层级170上延伸。第七金属化结构层级180包含具有是或包含氮氧化硅(sion)的0.3μm厚层181及是或包含氮化硅(sin)的0.55μm层182的双层结构。第七金属化结构层级180还包含保护性外涂覆(po)层183(例如,sio2)、多层级金属化结构103的第二部分中的导电金属线184,所述导电金属线中的一些形成提供到外部组件(例如,另一裸片或者引线框架的导电特征,未展示)的导电性的导电裸片垫。氮氧化硅层185在层183的部分上延伸且在一个实例中,具有2.8μm的厚度。层183与184共同形成保护性外涂覆(po)层。

29.另外,第七(例如,第n)金属化结构层级180包含隔离组件104的第二端子108及第七(例如,第n)金属线186。第二端子108与图1及2中所展示的第n金属线186间隔开大于前一(例如,下伏)第六金属化结构层级170的间隔距离177的非零间隔距离187(例如,大约90μm)。在一个实例中,层183是或包含沿着z具有大约4.5μm的厚度的二氧化硅。第七金属线186至少部分地在第六沟槽通路178上延伸。在一个实例中,第七金属线186是或包含沿着图1中的z方向具有大约3.0μm的厚度的铝金属。在此实例中,层183在双层结构181、182上并在双层181、182的间隙中在第六ild层171上延伸。另外,层183在第二端子108的一部分上并在第

七金属线186上延伸。第七金属线186包围第七金属化结构层级180的第一区域的上部部分以完成导电屏蔽件105。

30.图1到3中的实例电子装置100包含具有在第二金属化结构层级130中的第一端子106及在第七金属化结构层级180中的第二端子108的电容器隔离组件104。在其它实施方案中,相应第一端子106与第二端子108可位于金属化结构层级120、130、140、150、160、170、180中的不同的金属化结构层级中。此外,在所图解说明的实例中,导电屏蔽件105的阶梯形状包含逐渐增加的间隔距离137、147、157、167、177及187,尽管这并不是所有可能实施方案的严格要求。另外,不同实施方案包含具有非阶梯形状的导电屏蔽件。所图解说明的阶梯形状有利地提供隔离组件104的第二端子108与屏蔽结构105之间的大体一致的间隔。导电屏蔽件105提供通过沟槽接点118连接到半导体层101以提供完全包围多层级金属化结构103的第一区域的接地屏蔽件的大体连续的导电金属(例如,铜、氮化钽、钛、氮化钛、铝、钨)法拉第笼或屏蔽结构。在一个实例中,掺杂铜的铝线由氮化钛夹持,且铜线在三侧上由氮化钽囊封。在特定实施方案中,沟槽通路是或包含用于铜镶嵌方案的钨或铜,以形成导电屏蔽结构105。

31.在一个实施方案中,隔离组件104的第二端子108电连接到来自与多层级金属化结构103的第二部分的电路系统不同的电压域中的电路(例如,及第二半导体裸片)的高电压信号。在一个实例中,电子装置100包含具有多层级金属化结构103的第二部分中的连接及布线结构的低电压逻辑电路系统(未展示),且导电屏蔽件105提供多层级金属化结构103的第二部分与第一部分之间的基本上连续的隔离屏障。在所图解说明实施方案中,导电屏蔽件105由相应金属化结构层级120、130、140、150、160、170、180中包围多层级金属化结构103的第一区域196的经互连金属线126、136、146、156、166、176、186及沟槽接点/通路118、128、138、148、158、168、178建立,其中仅具有一或多个小间隙g(例如,图3),以用于第一端子106到低电压电路系统的电连接或多层级金属化结构103的第二部分的连接。

32.在一个实例中,电子装置100包含两个或多于两个隔离组件104(例如,具有图2中所见的顶部板或第二端子108的电容器)。在一个实施方案中,一对或多对电容器隔离组件104设置于多层级金属化结构103的第一部分中,且导电屏蔽件105提供环绕所有隔离组件104的单个接地法拉第笼结构。在另一替代实施方案中,在多层级金属化结构103中建立多个导电屏蔽件105,以提供个别地环绕一或多个相关联隔离组件的多个接地法拉第笼结构。在图1到3的实例中,个别电容器隔离组件104在多层级金属化结构103的第一区域中彼此横向间隔开,且个别地包含位于金属化结构层级中的不同的金属化结构层级(例如,在所图解说明的实例中,层级130及180)中的第一端子106与第二端子108。此外,在图1到3的实例中,电容器隔离组件104中的每一者包含延伸穿过金属线126中的对应间隙g的相关联导电布线特征125。

33.如图1中所展示,实例上部电容器板或第二端子108可焊接或以其它方式电连接到(例如,高电压域)的另一电路。图1展示其中接合导线188的第一端焊接到第二端子108的经暴露顶部侧192以促进电连接到另一裸片的导电特征的一个实例(例如,如下文结合图4及26进一步图解说明及描述)。实例电子装置100还包含在保护性外涂覆层183及185的部分上方延伸的10μm厚聚酰亚胺层190。在一个实例中,聚酰亚胺层190提供应力屏障以减轻在围封于经模制封装结构中之后半导体层101及多层级金属化结构103上的机械应力,例如以减

轻在某一数目个温度循环事件之后可能潜在地分层的上覆模制化合物与185的表面之间的机械应力。

34.在此实例中,聚酰亚胺层190、保护性氧化物层185及层183包含暴露第二端子108的顶部侧192的间隙。在此实例中,层181及182包含完全环绕第二端子108的具有横向间隙距离191的间隙。另外,层183及185包含沿着x方向与接合导线开口横向间隔开距离194(例如,273μm)的凹部或间隙。在一个实例中,此凹部或间隙位于最外围导电线184之间以便终止切割诱发的裂缝以防引入到裸片。距离194在不同实施方案中取决于在隔离组件周围存在何种外部电路系统而不同,且在一个实例中,所述凹部或间隙完全环绕裸片。如图1中以虚线形式展示,导电屏蔽件105提供具有环绕电容器隔离组件104且将第一区域196(例如,与高电压域相关联)与第二区域198(例如,与较低或不同电压域相关联)分隔开的伸缩式阶梯结构的接地法拉第笼。

35.图4示意性地图解说明包含上文所描述的电子装置100的实例封装式电子装置400。在此实例中,封装式电子装置400包含表示如上文结合图1到3描绘及描述的经单片化或经分离的半导体裸片的第一裸片100。第一裸片的装置100具有多层级金属化结构103,所述多层级金属化结构具有位于经隔离第一区域196与第二区域198之间的导电屏蔽件105以及电容器隔离组件104,如先前所描述。第一半导体裸片或电子装置100与一或多个额外半导体裸片封装在一起以建立具有与第一(例如,低电压)电压域相关联的导电引线或端子401、402、403、404、405、406、408及与一或多个额外(例如,较高电压)电压域相关联的导电引线或端子409、410、411、414、415及416的封装式电子组件。

36.如图4中示意性地展示,电子装置100(例如,第一半导体裸片)包含一对电容器104,每一电容器具有连接(例如,导线接合)到对应接合导线188的第一端子106及第二端子108。在对应用户应用(例如,通信系统印刷电路板)中,端子401到406、408到411及414到416焊接到对应电路板迹线421到426、428到431及434到436以分别利用相关联信号线或信号ina、inb、vcci、gnd、dis、dt、vcci、vssb、outb、vddb、vssa、outa及vdda提供电互连及操作。在此实例中,第一裸片或电子装置100包含将低电压第一及第二通信通道信号提供到相应电容器104的第一端子106的逻辑电路440。

37.图1及4中的第一半导体裸片电子装置100的导电屏蔽件105将多层级金属化结构103的第一部分196与相关联于第二端子108的高电压隔离。图4中的电容器104提供逻辑电路440与封装式电子装置400的第一半导体裸片451及第二额外半导体裸片452的电容式耦合电路之间的隔离屏障。在一个实例中,半导体裸片451及452还包含多层级金属化结构103,所述多层级金属化结构具有位于经隔离第一区域196与第二区域198之间的导电屏蔽件105以及具有板端子106及108的电容器104,如先前所描述。如图4中所展示,相应接合导线188是导线接合到第二端子108的经暴露顶部侧192以提供逻辑电路440与半导体裸片451及452的相应驱动器453及454之间的串联连接的电容器耦合。在另一实例中,第二半导体裸片451及第三半导体裸片452不包含内部隔离电容器,且接合导线188焊接到相应半导体裸片451及452的导电特征,例如焊接到相应驱动器453及454的输入(参见下文图26中的实例)。在一个实例中,半导体裸片451及452是封装式电子装置400的接收器,其从相应驱动器453及454的输出连接到在切换节点434处控制电压vssa的外部电路系统。

38.图4中的第一接收器输出通道(例如,通道“a”)提供相对于在供应节点460处接收

的供应电压vdd偏置的第一通道驱动器输出。供应节点460是经由启动电阻器462及二极管463连接以在电路板迹线436处提供第一供应电压信号vdda。第一驱动器453接收第一供应电压vdda作为上部轨供应,且驱动器453的下部轨连接到电路板迹线434以在参考电压vssa下操作。外部电路系统包含连接于端子414与416之间的启动电容器464,且驱动器453的输出连接到端子15以提供第一栅极驱动输出。第二接收器输出通道(例如,通道“b”)包含第二半导体裸片452的第二驱动器454,其根据端子411及409处分别的供应电压vdd及接地参考电压vssb而偏置。外部电路系统还包含连接于供应电压vdd与接地参考节点429处的接地参考电压vssb之间的供应电压电容器466。在操作中,驱动器453及454根据经由经隔离电容式耦合通道从逻辑电路440接收的信号来操作且提供连接到相应高侧晶体管471及低侧晶体管472的栅极的相应栅极驱动信号outa及outb。高侧晶体管471具有连接到高电压供应电压hv的漏极端子470,且电容器474连接于漏极端子470与接地参考节点429之间。高侧晶体管471的源极端子及低侧晶体管472的漏极端子连接到切换节点434。

39.还参考图5到25,图5展示制作包含在多层级金属化结构中具有隔离组件(例如,电容器、变压器等)及多层级隔离结构的第一裸片的封装式电子装置的方法500。图6到25展示经历根据方法500的制作处理的图1到4的第一裸片100的部分视图。方法500展示与并入有电容器104及导电屏蔽件105的多层级金属化结构的构造相关联的步骤,例如动作及/或事件。所描述步骤可同时用于单个半导体裸片100中其它电子电路及/或组件(例如,晶体管电路,以形成图4中的逻辑电路440等)的制作及互连。在一个实例中,多层级金属化结构103包含将隔离组件104的端子电耦合到一或多个内部组件(未展示)的金属线、圆柱形通路及沟槽通路。

40.方法500包含502处的前段处理,例如,在开始晶片上及/或中制作一或多个电路组件(例如,晶体管等)。在图1的电子装置100中,502处的前段处理包含处理开始半导体晶片,例如p型硅晶片、具有硅层、硅-锗层或具有半导体材料的另一层的soi结构。在一个实例中,501处的处理还包含在半导体层101上及/或中制作晶体管,及在半导体层101的顶部侧上及/或中形成隔离结构,例如所图解说明sti结构102。

41.图9到18展示半导体层101上方的如在504、506、510、520、530及540处形成的金属化结构103。实例方法500包含在504处形成预金属电介质层,以及在506处形成相关联接点(例如,钨)以建立pmd层级110。此后,逐层级制作多层级金属化结构103的n个金属化结构层级。图6展示504处的处理的一个实例,其中执行在半导体层101上沉积预金属电介质pmd层111(例如,sio2)的沉积过程600。在一个实例中,过程600沉积二氧化硅以将pmd层111形成为约1.2μm的厚度。

42.方法500在506处继续穿过pmd层111形成接点(例如,接点114及118)。图7展示一个实例,其中执行穿过pmd层111及在半导体层101上形成圆柱形接点114及预金属沟槽接点118的接点形成过程700。在一个实例中,过程700包含用以形成用于相应圆柱形接点及沟槽接点的圆柱形孔及沟槽的图案化蚀刻(未展示),及在开口中沉积适合金属(例如,是或包含钨)的一或多个沉积步骤,后续接着用以提供pmd层111以及所形成相应圆柱形接点114及沟槽接点118的平面顶部侧的平面化步骤(例如,化学机械抛光或cmp)。在一个实例中,沟槽形成会建立用于包围pmd层111的第一区域196(上文图1)的一部分的预金属沟槽接点118的连续沟槽,且对应沟槽及所产生接点118向下延伸到半导体层101上以开始上文所描述的接地

导电屏蔽件105。在实例实施方案中,圆柱形预金属层级接点114与电子装置100的一或多个电子电路组件电耦合(例如,用于图4的逻辑电路440中的信号路由)。另外,在506处在图7的实例中在电子装置100的所图解说明部分的外周边附近的区域119(图1)中形成其它沟槽接点118,例如以提供对抗装置100上的裂缝及机械应力的保护,尽管这并不是所有可能实施方案的严格要求。

43.方法500在图5中的510处继续在pmd层111上形成第一金属化结构层级120。图8及9展示其中在图5的512及514处形成第一金属化结构层级120的实例实施方案。第一金属化结构层级120包含预金属沟槽接点118上的第一金属线126、金属布线特征125。另外,金属化结构层级120包含pmd层111上的第一ild层121、第一金属线126及金属布线特征125,以及布线通路127及第一金属线126上的第一沟槽通路128。如上文所论述,第一沟槽通路128及第一金属线126将第一金属化结构层级120的第一区域196(除了在其中125穿过126的间隙区域中,如图3中所展示)包围在第一金属化结构层级120的第二区域198内,且金属布线特征125延伸穿过第一金属线126中的间隙g(例如,上文图3)。

44.在图5中的512处,沉积且图案化第一金属层特征(m1)。图8展示一个实例,其中执行过程800,在pmd层111上沉积金属层(例如,铝,达到0.61μm的厚度),且使用图案化蚀刻掩模(未展示)蚀刻经沉积金属的经暴露部分以形成第二区域(上文图1中的区域198)中的金属布线特征122以及第一区域(在图1中,196)中的金属布线特征125及第一金属线126。在514处,在pmd层111上沉积第一ild层121。图9展示一个实例,其中执行在pmd层111上沉积ild层121(例如,二氧化硅,达到1.2μm的厚度)的沉积过程900。在516处,在经沉积ild层121中蚀刻沟槽及圆柱形孔。图10展示一个实例,其中使用图案化蚀刻掩模1002执行蚀刻过程1000。蚀刻过程1000形成用于未来通路的圆柱形孔及用于未来沟槽通路的沟槽。516处的处理还包含用导电金属(例如,钨)填充经蚀刻圆柱形孔及沟槽以形成圆柱形布线通路124及沟槽通路128。图11展示一个实例,其中执行沉积过程1100,在经蚀刻通路孔及沟槽中沉积钨以形成圆柱形布线通路124及第一金属线126上的第一沟槽通路128以便在第一金属化结构层级120中继续导电屏蔽件105。在一个实例中,图5中的510处的处理还在电子装置100的所图解说明部分的外周边附近的区域119中形成其它沟槽接点128,尽管这并不是所有可能实施方案的严格要求。在一个实例中,510处的处理还包含在填充通路孔中的沟槽之后进行平面化。

45.方法500在图5中的520处继续在第一金属化结构层级120上形成第二金属化结构层级130。一个实例包含在522处形成及图案化第二金属层(m2)以形成第一沟槽通路128上的第二金属线136以及隔离组件104的与第二金属线136横向间隔开且在多层级金属化结构103的第一部分中的布线通路127的至少一部分上延伸的第一端子106。图12展示在形成第二金属化结构层级130以及相应第三金属化结构层级140及第四金属化结构层级150之后的实例电子装置100。在图5中的524处,在第一ild层121、第二金属线136及第一端子106上沉积第二ild层131(例如,二氧化硅,达到大约1.2μm的厚度)。在526处,在第二ild层131中蚀刻沟槽及圆柱形通路孔,且用钨填充这些沟槽及圆柱形通路孔以形成第二金属线136上的第二沟槽通路138及互连通路134以及多层级金属化结构103的第二部分198。在所图解说明的实例中,520处的第二金属化结构层级处理还在电子装置100的所图解说明部分的外周边附近的区域119中形成其它沟槽通路138,尽管这并不是所有可能实施方案的严格要求。

46.在一个实例中,在图5中的530处形成其它金属化结构层级。图12进一步展示上文所描述的第二金属化结构层级130上的第三金属化结构层级140,以及形成第四金属化结构层级150的处理1200。可在530处形成任何数目个中间金属化结构层级,其具有包围多层级金属化结构103的第一部分196的相应金属线及沟槽通路。在所图解说明的实例中,通过以下方式建立个别金属化结构层级:首先沉积且图案化金属线层,沉积ild层,对ild层进行化学机械抛光以移除形貌,在ild层中蚀刻圆柱形通路孔及沟槽,及用钨填充所述孔及沟槽,后续接着化学机械抛光(例如,cmp)以从ild表面移除不想要的钨。图13展示在电子装置100中形成实例第五金属化结构层级160的处理1300(例如,图5中的530处)。

47.图14到24中图解说明第六金属化结构层级170及第七金属化结构层级180的制作(在图5中的530及540处),包含图14中的沉积且图案化第六金属线176、划刻密封堆叠172的第六层级部分及其间的任何其它第六金属布线(未展示)的过程1400。图15展示在先前第五ild层161、第七金属线176及划刻密封堆叠172的第七层级部分上方沉积第六ild层171的进一步处理1500。

48.方法500还包含在图5中的540处形成最终金属化结构层级(例如,第n金属化结构层级180)。第n金属化结构层级180包含下伏的金属化结构层级170的沟槽通路178上的第n金属线186以及隔离组件104的第二端子108及第n金属线186上的层183。图16及17展示沉积电介质层181及182的相应沉积过程1600及1700。在一个实例中,沉积过程1600沉积氮氧化硅181达到大约0.3μm的厚度,且沉积过程1700沉积氮化硅182达到大约0.65μm的厚度。图18中的处理1800蚀刻沟槽及圆柱形通路孔且用钨填充所述孔及沟槽以在多层级金属化结构103的第二部分中形成第六沟槽通路178及第六圆柱形钨通路174。图19图解说明在利用蚀刻掩模1902沉积顶部金属化层之后蚀刻顶部金属化层的经暴露部分以形成结构108、184及186的蚀刻过程1900。

49.层级180的形成在图20中继续使用掩模2002蚀刻层182及181以暴露第六ild层171的顶部的部分的蚀刻处理2000。通过图21中的沉积过程序列2100在第n金属线186上沉积保护性外涂覆层183的一部分(例如,通过高密度等离子体(hdp)沉积二氧化硅达到1.5μm的厚度,后续接着通过等离子体增强化学沉积(pecvd)沉积二氧化硅达到3.6μm的厚度)。然后对通过过程序列2100沉积的双层183进行化学机械抛光达在层180的1.5um内以移除形貌。在图22中,执行沉积最终层185的沉积过程2200,所述最终层与183一起形成装置100的保护性外涂覆(po)堆叠。在一个实例中,所述过程沉积氮氧化硅185达到大约2.8μm的厚度。在图23中,利用蚀刻掩模2302执行蚀刻过程2300。蚀刻过程2300在保护性外涂覆堆叠中蚀刻开口,包含暴露电容器隔离组件104的第二端子108的顶部侧192的开口。在图24中,执行施配或屏蔽过程2400,此在保护性外涂覆堆叠187的部分上方形成聚酰亚胺层190(例如,达到大约10μm的厚度)以建立应力屏障来减轻半导体层101及多层级金属化结构103上的机械应力。如图24中所展示,聚酰亚胺层190具有暴露第二端子108的顶部侧192的间隙。

50.还参考图25到27,方法500在550处继续自晶片分离出包含半导体层101及多层级金属化结构103的第一半导体裸片(例如,上文图4中的裸片100)。另外,将所述裸片附接到引线框架且在550处执行导线接合处理以提供到第二电容器端子108的电连接。图26展示在550处的处理期间的封装式电子装置,其中半导体裸片100附接到具有如先前所描述的引线或端子401到406、408到411及414到416的引线框架结构2600的第一裸片附接垫2601。在此

实例中,550处的裸片附接处理还包含将裸片451及452(例如,上文图4)附接到引线框架的相应裸片附接垫2602及2603。接合导线连接(例如,焊接、超声焊接等)于裸片100、451、452的导电特征之间及/或连接(例如,焊接、超声焊接等)到引线401到406、408到411及414到416中的特定引线。如图4、25及26中所展示,导线接合还将上文所描述的导线188接合到电容器隔离组件104的相应第二端子108的经暴露顶部侧192。在此实例中,接合导线188的第二端分别耦合到裸片451及452的对应第二电容器板108以便在第一裸片100的驱动器输出与裸片451及452的电路系统之间建立串联连接的电容器耦合。在550处可使用其它电连接技术,例如球栅阵列或到衬底的导电特征的焊料球连接等,以在550处在隔离组件104的第二端子108与第二半导体裸片的导电特征之间形成电连接。方法500还包含图5中的560处的模制及装置分离。图27展示包含经模制封装结构2700(例如,模制化合物)的经模制且经单片化的封装式电子装置400,所述经模制封装结构围封裸片100、451及452、电连接188且沿着封装结构2700的一或多个侧暴露导电引线或端子401、402、403、404、405、406、408的部分。图27的实例是四方扁平无引线(qfn)封装式装置400。在另一实例中,不同封装类型及形式是可能的,且在一个实例中,方法500还包含引线修整及成形以提供具有鸥翼形引线、j型引线等的完成封装式电子装置。

51.上文所描述的封装式电子装置2700及电子装置100使用在金属化处理期间在多层级金属化结构103中及在顶部金属层中形成的导电屏蔽件105提供具有第一部分196与第二部分198之间的保护的高级高电压隔离屏障。导电屏蔽件105通过由沟槽接点/通路118、128、138、148、158、168及178结合所连接金属线126、136、146、156、166、176、178及186形成的增强限定的接地环为经围封隔离屏障电容器组件104提供对抗附近eos事件的稳健保护。在所图解说明的实例中,沟槽接点/通路118、128、138、148、158、168及178设置在多层级金属化结构103的所有层级处,尽管这并不是所有可能实施方案的严格要求。在一个实例中,不存在沟槽式接点118及通路层级128。另外,实例导电屏蔽件105通过经由最下部沟槽通路118连接到半导体层101而接地,尽管这并不是所有可能实施方案的要求。所揭示实例通过以下方式减轻在发生eos的情况下装置失去隔离完整性的风险:建立基本上、完全或至少部分地环绕高电压隔离组件104的金属壁,以减轻响应于eos事件而开裂,例如,以环绕组件的渐缩或垂直金属壁环绕周界区的至少90%。在一个实例中,环绕hv区域的沟槽通路包含偶尔的裂口以部分地环绕高电压组件或装置,例如通路1结构与通路2结构和第一金属层级中的裂口匹配以允许连接到底部板的情况。此外,所描述的eos保护不需要在制作封装式电子装置时添加其它电路组件,例如保险丝或其它一次性装置。

52.还参考图28到30,图28展示在由半导体层101上面的多层级金属化结构103中的导电屏蔽件2805包围的第一区域2896中具有隔离变压器隔离组件2804的另一电子装置2800的截面侧视图。图29展示沿着图28的电子装置2800中的线29-29截取的部分截面俯视平面图,且图30展示沿着图28的电子装置2800中的线30-30截取的部分俯视平面图。电子装置2800包含与上文结合图1到3描述的那些类似编号的结构及尺寸。在此实例中,隔离组件2804是在第二金属化结构层级130中具有形成为变压器绕组或第一变压器线圈的第一端子2806的变压器。在此实例中,第二端子2808是第二变压器线圈或第二变压器绕组,如图29中所展示,且在一个实例中,第一线圈(第一端子)2806具有类似形状。导电屏蔽件2805使用如上文所描述的导电金属线及沟槽通路将高电压第一区域2896与低电压域第二区域2898分

隔开。如图30中进一步展示,在第一金属线126中形成两个间隙以便提供连接到初级变压器线圈2806的相应第一及第二端的第一及第二布线结构125,且在此实例中,第七金属化结构层级180提供次级变压器线圈2808的第一及第二端的经暴露部分以用于电连接到外部装置(例如,电连接到封装式电子装置中的另一裸片,未展示)。

53.以上实例仅图解说明本公开的各种方面的数个可能实施方案,其中所属领域的技术人员在阅读并理解本说明书及附图之后将即刻联想到等效更改及/或修改。修改在所描述实例中为可能的,且其它实施方案在权利要求书的范围内为可能的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。