用于局部应力调节的uv固化

通过引用并入

1.pct申请表作为本技术的一部分与本说明书同时提交。如在同时提交的pct申请表中所标识的本技术要求享有其权益或优先权的每个申请均通过引用全文并入本文且用于所有目的。

背景技术:

2.半导体制造处理涉及许多沉积及蚀刻操作,其会剧烈地改变晶片弯曲性。例如,在3d-nand制作(其因较低成本及在诸多应用中具更高可靠性而逐渐取代2d-nand芯片)中,具有厚、高应力的基于碳的硬掩模的多堆叠膜和/或金属化线会造成明显的晶片翘曲,从而导致前侧光刻覆盖不匹配,或甚至晶片弯曲超过静电卡盘的夹持极限。

3.这里提供的背景技术是为了总体呈现本公开的背景的目的。当前指定的发明人的工作在其在此背景技术以及在提交申请时不能确定为现有技术的说明书的各方面中描述的范围内既不明确也不暗示地承认是针对本公开的现有技术。

技术实现要素:

4.本文提供了一种调节衬底上的局部应力的方法。所述方法包括:提供弯曲半导体衬底;在所述弯曲半导体衬底上沉积uv可固化膜;以及通过使所述一或更多个第一区域暴露于uv辐射并且使用第一预图案化掩模选择性固化所述uv可固化膜的一或更多个第一区域,以局部调节所述uv可固化膜上的应力,其中所述uv可固化膜减轻所述弯曲半导体衬底的弯曲。

5.在一些实施方案中,所述方法还包括:在uv源与所述弯曲半导体衬底之间提供所述第一预图案化掩模,其中所述第一预图案化掩模包括与所述uv可固化膜的所述一或更多个第一区域对应的一或更多个开口。在一些实施方案中,所述方法还包括:测量整个所述弯曲半导体衬底上的翘曲以确定所述弯曲半导体衬底上的局部化应力;以及在掩模中图案化所述一或更多个开口以形成所述第一预图案化掩模,所述一或更多个开口至少基于所述弯曲半导体衬底上的所述局部化应力而被图案化。在一些实施方案中,所述uv可固化膜的所述一或更多个第一区域根据uv辐射的受控时间、温度、强度和/或波长而暴露于所述uv辐射,以局部调节所述uv可固化膜的所述一或更多个第一区域中的所述应力。在一些实施方案中,暴露于所述uv辐射的温度介于约200℃与约500℃之间。在一些实施方案中,所述uv辐射的强度介于约1μw/cm2与约10w/cm2之间。在一些实施方案中,所述uv辐射配置成将所述uv可固化膜上的应力局部调节介于约200mpa与约4000mpa之间的量。在一些实施方案中,所述弯曲半导体衬底呈不对称弯曲,其具有大于约

±

300μm的翘曲。在一些实施方案中,在所述弯曲半导体衬底上沉积所述uv可固化膜发生于所述弯曲半导体衬底的背侧。

6.还提供了一种制备用于局部化应力调节的掩模的方法。所述方法包括:在掩模中图案化一或更多个开口以形成一预图案化掩模,所述一或更多个开口至少基于半导体衬底的应力图和/或所述半导体衬底的预定管芯间距而被图案化;以及提供所述预图案化掩模

至uv室,其中所述预图案化掩模被配置成当所述半导体衬底暴露于uv辐射时,使沉积于所述半导体衬底上的uv可固化膜的一或更多个暴露区域变得比所述uv可固化膜的一或更多个未暴露区域更具拉伸性。

7.在一些实施方案中,所述方法还包括:接收半导体衬底的应力图,其指示所述半导体衬底的一或更多个区域中的不对称弯曲的程度。

8.还提供了一种用于调节衬底上应力的装置。所述装置包括:处理室,其包括衬底支撑件,其用于支撑弯曲半导体衬底,以及uv源,其用于使所述弯曲半导体衬底暴露于uv辐射;以及控制器。所述控制器被配置有用于执行以下操作的指令:在所述处理室中提供所述弯曲半导体衬底,使uv可固化膜沉积于所述弯曲半导体衬底的前侧或背侧上;以及通过使用第一预图案化掩模,选择性地固化所述uv可固化膜的一或更多个第一区域,所述第一预图案化掩模使所述一或更多个第一区域选择性地暴露于uv辐射,以局部调节所述uv可固化膜上的应力,其中所述uv可固化膜减轻所述弯曲半导体衬底的弯曲。

9.在一些实施方案中,所述控制器被配置有用于当选择性地固化所述uv可固化膜的所述一或更多个第一区域时改变uv辐射的时间、温度、强度和/或波长的指令。在一些实施方案中,所述装置还包括沉积室,其与所述处理室分开;其中所述控制器还被配置有用于执行以下操作的指令:在所述弯曲半导体衬底的所述前侧或背侧上沉积所述uv可固化膜。

附图说明

10.图1a示出了示例性弯曲半导体衬底的示意图在x-y平面中的顶视图。

11.图1b示出了图1a的弯曲半导体衬底在y轴方向上的侧视图。

12.图1c示出了图1a的弯曲半导体衬底在x轴方向上的侧视图。

13.图2a示出了根据一些实施方案调节弯曲的半导体衬底上的局部应力的示例性方法的流程图。

14.图2b示出了根据一些实施方案制备用于局部化应力调节的掩模的示例性方法的流程图。

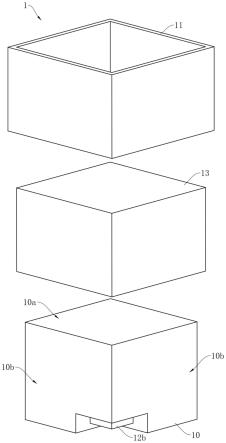

15.图3a-3d示出了根据一些实施方案的弯曲半导体衬底的横截面示意图,该弯曲半导体衬底通过选择性紫外线(uv)固化进行局部化应力调节处理以减轻弯曲。

16.图4示出了根据一些实施方案的示例性预图案化掩模的示意图,该预图案掩模用于选择性地暴露uv可固化膜的区域以进行局部化应力调节。

17.图5示出了根据一些实施方案用于沉积uv可固化膜的示例性装置的示意图。

18.图6示出了根据一些实施方案用于uv可固化膜的uv固化的示例性装置示意图。

19.图7示出了根据一些实施方案用于执行局部化应力调节操作的示例性处理工具的示意图。

具体实施方案

20.在本发明中,术语“半导体晶片”、“晶片”、“衬底”、“晶片衬底”、以及“部分已制成的集成电路”可互换使用。本领域技术人员应理解,术语“部分已制成的集成电路”可以指集成电路制造的许多阶段中任一者期间的硅晶片。半导体设备产业中所使用的晶片或衬底通常具有200mm或300mm或450mm的直径。以下详细描述假定本发明被实施于晶片上。然而,本

发明不限于此。工件可以具有多种形状、尺寸和材料。

21.半导体制作处理涉及各种结构的形成,其中许多可以是二维的。随着半导体设备尺寸微缩,并且设备缩至更小,整个半导体衬底上的特征的密度增大,从而导致以多种方式(包括三维方式)蚀刻且沉积的材料层。例如,3d-nand为一项变得更受欢迎的技术,其原因在于,相较于其他技术(例如2d-nand)有较低成本和增加的存储器密度,且在多种应用中有更高的可靠度。在3d-nand结构的制作期间,晶片弯曲会极大变化。例如,在制作3d-nand结构时,沉积厚的硬掩模材料以及沿晶片表面蚀刻沟槽会导致晶片弯曲。由于膜层在制作期间彼此上下堆叠,因而更多应力被引导至半导体晶片上,其会导致弯曲。可使用光学技术来测量弯曲。可通过获得晶片图或应力图来测量或评估晶片弯曲。可使用如本文所述的弯曲值或翘曲值(其被测量为半导体晶片的最低点到晶片上最高点之间的竖直距离)来量化弯曲。翘曲值可沿着一或更多个轴-例如,不对称翘曲的晶片可以具有x轴翘曲和/或y轴翘曲。

22.在弓形晶片中,最低点为晶片的中心,而最高点为晶片的边缘。在圆顶形晶片中,最低点为晶片的边缘,而最高点为晶片的中心。弓形和圆顶形晶片具有对称或大部分对称弯曲。晶片也可以具有不对称弯曲。在不对称弯曲中,翘曲是沿x轴及y轴来测量。不对称弯曲的晶片对于x轴翘曲及y轴翘曲具有不同的值。在一些案例中,不对称弯曲的晶片具有负的x轴翘曲及正的y轴翘曲。在一些案例中,不对称弯曲的晶片具有正的x轴翘曲及负的y轴翘曲。在一些案例中,不对称弯曲的晶片具有正的x轴翘曲和正的y轴翘曲,但翘曲值不同。在一些案例中,不对称弯曲的晶片具有负的x轴翘曲和负的y轴翘曲,但翘曲值不同。不对称弯曲晶片的一示例为鞍形晶片。对于鞍形晶片,在一示例中,x轴上的翘曲可为 200μm,而y轴上的翘曲可为-200μm。鞍形晶片具有向上弯的晶片的两相对边缘,而晶片的另两相对边缘则向下弯。如本文所使用的,翘曲可以指晶片呈现偏离平面度的任何偏差,其中弓形晶片、圆顶形晶片以及鞍形晶片为晶片中不同类型的翘曲的示例。

23.弯曲会对后续处理造成问题,例如在光刻期间,如果半导体衬底翘曲,则蚀刻会不均匀。高弯曲可能是由厚的高应力的基于碳的硬掩模层的沉积所引起。此外,由于多堆叠膜以及这种制作处理中所使用的厚的高应力的基于碳的硬掩模的存在,蚀刻会导致一些不对称翘曲,而沉积处理会引起高达介于弯曲 500μm至-1300μm之间变化的明显晶片翘曲。例如,可灰化硬掩模可具有高达-1000mpa的应力值,并具有高达-1000μm的弯曲值。解决这种晶片翘曲会是一项挑战,因为后续处理可能会受到超过 500μm的晶片翘曲的影响,尤其是当晶片用于涉及夹持晶片至静电卡盘的后续处理中时,由于许多静电卡盘具有“夹持极限”(其定义为无法有效夹持晶片之前所容许的最大翘曲),故其会是一项特殊挑战。许多静电卡盘具有约

±

300μm的夹持极限。因此,高度翘曲的半导体衬底可能无法在一些工具中进行处理。另外,高度翘曲的半导体衬底的处理可能引起进一步的翘曲。例如,在一方向上蚀刻沟槽会因半导体衬底上的不对称应力而导致呈不对称弯曲的翘曲。

24.存在一些用于解决半导体晶片弯曲的技术。在一些案例中,可使用技术以在半导体晶片的背侧上沉积补偿层。然而,利用补偿层的背侧沉积的应用已限于单调全局晶片翘曲减轻。具体地,用于解决半导体晶片弯曲的技术一般已限于轴向对称或多轴向对称的技术。

25.随着3d-nand技术不断扩大且高深宽比特征变得越来越普遍,正出现与半导体衬底上局部化应力和管芯间应力变化有关的新挑战。局部化应力及管芯间应力变化可能会导

致区块弯折(block-bending)、单元串扰(cell cross-talk)、单元损耗(cell loss)和/或单元错位(cell misalignments)。局部化应力是指以不均匀方式发生在晶片内的应力变化,例如,不易以应力相对于(x,y)位置的线性函数或高阶多项式函数描述。这与全局应力相反,全局应力可以用这种线性或多项式函数来描述。管芯间应力是局部化应力的示例。被不良补偿/校正的局部化应力可能会导致局部化晶片形貌(topology)发生变化,其进而可能导致光刻期间的不良对准。这种不良对准通常根据平面内变形(ipd)来观察,其为晶片上对准标记因晶片形貌而偏离其预期位置的向量位移的量化。光刻期间的高ipd可能会导致关键尺寸或光刻步骤中定义的任何其他特征发生非所期望的变化,因此可能因光刻错误而出现前述的区块弯折、单元串扰、单元损耗和/或单元错位的现象。

26.在一些案例中,金属化结构和/或线沿y轴方向或x轴方向沉积,但不一定都沉积。图1a示出了示例性弯曲半导体衬底的示意图在x-y平面中的顶视图。半导体衬底100可以包括沉积在半导体衬底100中心附近的金属线101。金属线101沿着半导体衬底100的y方向延伸。然而,并无沿着半导体衬底100的x方向延伸的金属线。这产生呈炸玉米饼形(taco-shaped)或卡诺里卷形(cannoli-shaped)的弯曲,如图1b所示。图1b示出了图1a的弯曲半导体衬底在y轴方向上的侧视图。如图1b所示,从y轴角度观看,半导体衬底100朝弯曲半导体衬底的中心向下弯。图1c示出了图1a的弯曲半导体衬底在x轴方向上的侧视图。如图1c所示,从x轴角度观看,半导体衬底100是平坦的。如上所讨论的,翘曲是指晶片呈现偏离平面度的任何偏差,其中炸玉米饼形晶片或卡诺里卷形晶片代表晶片中翘曲的示例。

27.图1a-1c示出了可能导致不对称弯曲的局部化应力变化的示例。另外,在切割半导体衬底时,半导体衬底中的局部化应力变化可能导致一或更多管芯变成弯曲。用于补偿弯曲半导体衬底上弯曲的现有技术一般未能减轻单轴方向或局部化形式的弯曲。

28.本发明提供了用于减轻弯曲半导体衬底中弯曲度的方法,其通过在弯曲半导体衬底上沉积紫外线(uv)可固化膜,并选择性地固化uv可固化膜的一或更多个区域,以局部调节uv可固化膜上的应力。通过选择性地将uv可固化膜的某些区域暴露于适当波长的uv光并且局部调节uv可固化膜上的应力,即可调整弯曲半导体衬底上的局部应力以达到局部翘曲形貌。uv可固化膜可沉积于弯曲半导体衬底的前侧或背侧上。在uv可固化膜沉积在弯曲半导体衬底上后,在uv源与uv可固化膜之间提供预图案化掩模。预图案化掩模选择性地阻挡uv暴露,从而使一或更多区域暴露于uv辐射,导致uv可固化膜中的局部化应力发生变化,以局部调节应力。可控制uv暴露的时间、温度、强度和波长,以调整局部应力调节。

29.图2a示出了根据一些实施方案调节弯曲半导体衬底上局部应力的示例性方法的流程图。可以不同顺序和/或以不同、更少或额外操作来执行处理200的操作。处理200的操作可使用图5中用于膜沉积的装置、图6中用于uv暴露的装置或其组合来执行。在一些实施方案中,处理200的操作可至少部分地根据储存于一或更多个非瞬时计算机可读介质中的软件来实施。

30.在处理200的框210中,提供弯曲半导体衬底。弯曲半导体衬底可提供于处理室中,以执行沉积和/或uv暴露操作。衬底可以是硅晶片,例如200mm晶片、300mm晶片或450mm晶片,包括其上沉积有一或更多层材料(例如介电、导电或半导电材料)的晶片。该一或更多层中的一些可被图案化。层的非限定示例包括介电层和导电层,例如氧化硅、氮化硅、碳化硅、金属氧化物、金属氮化物、金属碳化物和金属层。在多种实施方案中,对衬底进行图案化。

31.在一些实施方案中,半导体衬底包括图案化3d-nand结构和衬底中的一或更多蚀刻沟槽。在一些实施方案中,图案化3d-nand结构包括一或更多金属层或线,其在单轴方向上沿半导体衬底纵向地延伸。半导体衬底可能弯曲。在一些实施方案中,弯曲半导体衬底具有压缩弯曲。在一些实施方案中,弯曲半导体衬底具有拉伸弯曲。在一些实施方案中,弯曲半导体衬底可以是不对称弯曲。

32.弯曲半导体衬底可具有约

±

1000μm的翘曲。在一些实施方案中,弯曲半导体衬底具有大于约

±

300μm的翘曲。在一些实施方案中,弯曲半导体衬底具有大于约

±

300μm且小于约

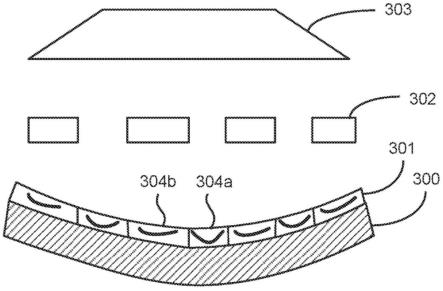

±

1000μm的翘曲。翘曲可能发生在弯曲半导体衬底的一或更多个局部化区域。翘曲在x轴翘曲与y轴翘曲之间可能具有不同的值。因此,沿一轴的翘曲可能比另一轴更明显。在一些实施方案中,弯曲半导体衬底呈炸玉米饼形。

33.在一些实施方案中,弯曲半导体衬底被提供于用于执行沉积操作的处理室中,其中用于执行沉积操作的处理室可被配置成用于背侧或前侧沉积。在一些实施方案中,背侧沉积可通过将弯曲半导体衬底上下颠倒放置以使背侧朝向处理室的顶部喷头来实现。在一些实施方案中,背侧沉积可通过将处理气体从处理室的底部喷头输送至弯曲半导体衬底的背侧(从喷头到基座)来实现。

34.图3a示出了弯曲半导体衬底的横截面示意图。弯曲半导体衬底300可具有压缩弯曲。在一些实施方案中,压缩弯曲可沿着弯曲半导体衬底300的单轴方向发生。弯曲半导体衬底300可以是不对称弯曲,其中翘曲可以在x轴翘曲与y轴翘曲之间具有不同的值。弯曲半导体衬底300的一或更多个局部化区域可以具有不同应力水平。弯曲半导体衬底300的应力图可指示弯曲半导体衬底300的一或更多个局部化区域中的弯曲程度。弯曲的程度与弯曲半导体衬底300的一或更多个局部化区域中的应力水平相关。

35.返回图2a,在处理200的框220中,将uv可固化膜沉积在弯曲半导体衬底上。uv可固化膜被沉积在弯曲半导体衬底的前侧或背侧上。在一些实施方案中,uv可固化膜被沉积在弯曲半导体衬底的背侧上。那样,uv可固化膜避免沉积在弯曲半导体衬底的前侧上的电路、晶体管或其他设备组成件上。uv可固化膜可作为弯曲补偿层,以用于减轻弯曲半导体衬底中的弯曲。

36.在一些实施方案中,uv可固化膜不仅配置成通过暴露于紫外线辐射而被固化,且uv可固化膜也被配置成发生显著量的应力值变化。uv可固化膜被配置成发生大于约200mpa量的应力值变化,例如介于约200mpa与约4000mpa之间的量。换言之,刚沉积(as-deposited)的uv可固化膜的应力值与固化后的uv可固化膜的应力值之间的差大于约200mpa,例如介于约200mpa与约4000mpa之间。例如,uv可固化膜的刚沉积应力值可小于约-100mpa,而uv可固化膜的固化后应力值可大于约 100mpa。在一些实施方案中,刚沉积的uv可固化膜可更具压缩性,而固化后的uv可固化膜可更具拉伸性。

37.在一些实施方案中,uv可固化膜包括介电材料,例如超低k介电材料。在一些实施方案中,uv可固化膜包括氮化物或掺杂氮化物。氮化物在uv固化后可能会发生显著应力变化,而许多氧化物及碳化物则不会发生显著的应力变化。在一些示例中,uv可固化膜包括氮化硅。在一些示例中,uv可固化膜包括碳氮化硅。在一些实施方案中,uv可固化膜的厚度介于约20nm与约150nm之间、介于约25nm与约100nm之间、或介于约30nm与约100nm之间。uv可固化膜的厚度足够薄以供uv辐射完全穿透,且又足够厚以在底下弯曲半导体衬底上引起应

力。

38.uv可固化膜可通过任何合适的沉积技术沉积在弯曲半导体衬底上。在一些实施方案中,uv可固化膜通过例如等离子体增强化学气相沉积(pecvd)处理的化学气相沉积(cvd)处理来沉积。uv可固化膜可以在用于沉积的处理室中沉积,其中用于沉积的合适的沉积处理室示于图5中。在pecvd期间,例如硅烷(sih4)之类的含硅前体可以与暴露于等离子体的一或更多种反应性气体反应,以在弯曲半导体衬底上形成氮化硅。在一些实施方案中,硅烷(sih4)可以与氨(nh3)和/或氮(n2)一起流入处理室。可能存在惰性气体,例如氦(he)。pecvd氮化硅可以在介于约250℃与约550℃之间的温度下沉积。pecvd氮化硅可以在介于约2托与约20托之间的压强下沉积。

39.通过pecvd沉积的膜一般含有大量的氢。例如,pecvd氮化硅膜含有si-h和n-h键形式的氢。不受限于任何理论,据信应力变化是由于氢减少且空隙收缩的pecvd氮化硅的uv处理而产生。

40.图3b示出了沉积在图3a的弯曲半导体衬底上的uv可固化膜的横截面示意图。uv可固化膜301可沉积于弯曲半导体衬底300的前侧或背侧上。在一些实施方案中,uv可固化膜301为氮化物,例如氮化硅。uv可固化膜301可以是压缩性氮化物,其中uv可固化膜301的刚沉积应力值为负的。例如,uv可固化膜的刚沉积应力值小于约-100mpa(更负)、小于约-200mpa或小于约-300mpa。uv可固化膜301可配置成在uv处理后发生应力值的显著变化,其中应力变化可以大于约200mpa、介于约200mpa与约4000mpa之间、或介于约200mpa与约2000mpa之间。在一些实施方案中,uv可固化膜301通过pecvd来沉积。

41.返回图2,在处理200的框230中,uv可固化膜的一或更多个第一区域通过将一或更多个第一区域暴露于uv辐射并且使用第一预图案化掩模来选择性地固化,以局部调节uv可固化膜上的应力。选择性固化后的uv可固化膜减轻弯曲半导体衬底中的弯曲。第一预图案化掩模被提供于uv源与弯曲半导体衬底之间,其中第一预图案化掩模包括一或更多个开口,其对应于uv可固化膜的一或更多个第一区域。

42.第一预图案化掩模选择性地阻挡uv暴露,使得仅弯曲半导体衬底的某些区域暴露于uv辐射。这样,uv可固化膜的暴露区域被选择性地固化并发生应力变化,而uv可固化膜的未暴露区域被阻挡不经历uv暴露且不发生应力变化。如本文所使用,uv可固化膜的暴露区域可以与uv可固化膜的一或更多个第一/第二区域互换使用。在一些实施方案中,相比于未暴露区域,uv可固化膜的暴露区域可变得更具应力上的拉伸性或更具压缩性。因此,相比于未暴露区域,暴露区域的局部化压缩应力或拉伸应力增加。uv可固化膜的暴露区域中应力的这些变化可诱导至弯曲半导体衬底的一或更多个区域,因而局部地调节应力以减轻弯曲半导体衬底中的弯曲。换言之,如果弯曲半导体衬底的一或更多个区域因压缩应力而弯曲,则直接覆盖于弯曲半导体衬底的一或更多个区域上的uv可固化膜的暴露区域在拉伸应力上增加以进行补偿。因此,减轻弯曲半导体衬底的一或更多个区域中的弯曲。

43.未受限于任何理论,应力变化可能是由于uv固化期间uv可固化膜中的氢减少而产生。这可以在pecvd氮化硅膜中观察到。氢的损失和/或空隙的收缩可导致uv可固化膜的体积减小。然而,半导体衬底的约束可以防止任何侧向收缩,因而在uv可固化膜的暴露区域中施加拉伸应变。在一些实施方案中,选择性地固化uv可固化膜的一或更多个第一区域导致暴露区域变得比uv可固化膜的未暴露区域更具应力上的拉伸性。

44.第一预图案化掩模可以由阻挡或实质上阻挡uv辐射的材料制成。在一些实施方案中,第一预图案化掩模包括金属、陶瓷或硅。第一预图案化掩模中的一或更多个开口可以进行几何形状设计,以用uv暴露对准弯曲半导体衬底的一或更多个区域,从而减轻弯曲半导体衬底的一或更多个区域中的弯曲。该一或更多个开口可以是圆形、矩形或任何合适的形状。在一些实施方案中,可基于弯曲半导体衬底上局部化应力的测量来对该一或更多个开口进行图案化。弯曲半导体衬底上局部化应力的测量可以从应力图生成。

45.固化uv可固化膜的一或更多个第一区域通过uv暴露来进行。如本文所使用的,uv辐射可广泛地包括150nm至红外区域(约1-10μm)的辐射。在一些实施方案中,uv源可提供约200-800nm范围内的uv暴露。uv源可发出范围或单一波长的uv辐射。uv源可以连续模式或脉冲模式发射uv辐射,以控制膜应力变化。uv可固化膜的选择性固化导致在一或更多个第一区域中引起较高的应力值。

46.该一或更多个第一区域中的局部应力调节程度取决于uv固化期间的处理条件。在一些实施方案中,该一或更多个第一区域中的局部应力调节程度取决于uv辐射的时间、温度、强度和/或波长。然而,本领域技术人员将理解,可控制uv固化期间的其他条件以影响局部应力调节程度。然而,通过调节以下一或更多者:(1)uv暴露的时间、(2)uv暴露期间的衬底温度、(3)uv暴露的强度、以及(4)uv暴露的波长,在暴露区域中所引起的应力变化量相比于未暴露区域将有所变化。例如,较长uv暴露时间导致较高应力值,较高衬底温度导致较高应力值,而较高强度导致较高应力值。应理解,更长的uv暴露时间、更高的衬底温度和更高的强度可以在控制应力值方面达到某些极限。可微调uv暴露的时间、温度、强度和波长,以在该一或更多第一区域中达到一定程度的局部应力调节。uv源可配置成控制uv暴露的时间(即剂量)、uv暴露的强度和uv暴露的波长。衬底支撑件(即,基座)可以配置成控制衬底温度。

47.在一些实施方案中,uv暴露的时间介于约0.5分钟与约120分钟之间、介于约1分钟与约60分钟之间、或介于约2分钟与约30分钟之间。uv暴露的时间或持续时间足以观察到所期望的应力变化。在一些实施方案中,uv暴露期间的温度介于约100℃与约700℃之间、介于约150℃与约550℃之间、或介于约200℃与约500℃之间。温度状况可能受限于热预算约束,其意指uv处理期间的衬底温度受到半导体衬底上的设备和膜的影响。例如,使用单硅化镍(nisi)层将衬底温度限制在小于400℃,而使用镍铂硅化物(niptsi)层将衬底温度限制在小于480℃。在一些实施方案中,uv暴露的强度介于约1μw/cmw约10w/cm2之间、介于约10μw/cm2与约5w/cm2之间、或介于约50μw/cm2与约1w/cm2之间。uv辐射的强度可提供破坏uv可固化膜中某些键(例如,si-h和n-h键)的足够能量。

48.可控制uv固化期间的其他条件以影响uv处理。在一些实施方案中,选择性固化uv可固化膜可以在介于约1托与约760托之间、介于约2托与约300托之间、或介于约5托与约15托之间的压强下发生。在一些实施方案中,惰性气体或载气例如氦(he)、氩(ar)或氮(n2)可以在uv可固化膜的一或更多个第一区域的选择性固化期间流动。

49.在一些实施方案中,在uv可固化膜的选择性固化后,uv可固化膜的暴露区域可实质上调节应力值,其中暴露区域可调节大于约200mpa、介于约200mpa与约4000mpa之间、或介于约200mpa与约2000mpa之间的量。举例来说,uv可固化膜的暴露区域在选择性固化之前可各自具有约-100mpa或更小(更负)的应力值。uv可固化膜的暴露区域在选择性固化之后

可各自具有约 100mpa或更大的应力值。作为可替代示例,uv可固化膜的暴露区域在选择性固化之前可各自具有约 100mpa或更大的应力值。uv可固化膜的暴露区域在选择性固化之后可各自具有约-100mpa或更小(更负)的应力值。在这些实例中,这表示uv可固化膜的暴露区域在选择性固化后可调节200mpa或更多。如上所讨论的,暴露区域在应力上的调节的多寡可取决于uv暴露条件。

50.在一些实施方案中,处理200可进一步包括在uv源与弯曲半导体衬底之间提供第二预图案化掩模,以及使用选择性将一或更多个第二区域暴露于uv辐射的第二预图案化掩模来选择性地固化uv可固化膜的一或更多个第二区域,以局部地调节uv可固化膜中的应力。在一些实施方案中,该一或更多个第二区域可以与uv可固化膜的该一或更多个第一区域不同。在一些实施方案中,该一或更多个第二区域中的至少一些可以与uv可固化膜的该一或更多个第一区域相同。第二预图案化掩模的应用允许对整个uv可固化膜上不同区域进行不同程度的局部化应力调节。选择性地固化一或更多个第二区域是在不同于选择性地固化一或更多个第一区域的条件下发生。使用第一预图案化掩模进行选择性固化时的时间、温度、强度和波长,可以不同于使用第二预图案化掩模进行选择性固化时的时间、温度、强度和波长。因此,uv可固化膜的该一或更多个第二区域中的应力调节可以不同于该一或更多个第一区域中的应力调节。

51.图3c示出了图3b的弯曲半导体衬底选择性地暴露于uv辐射的横截面示意图。预图案化掩模302位于弯曲半导体衬底300的uv可固化膜301与uv源303之间。uv源303被配置成朝弯曲半导体衬底300发射uv辐射。预图案化掩模302选择性地允许uv辐射固化uv可固化膜301的一些区域,并选择性地对uv可固化膜301的其他区域阻挡uv辐射。预图案化掩模302具有一或更多个开口。预图案化掩模302中的该一或更多个开口有助于弯曲半导体衬底300的局部化应力调节。

52.可微调uv处理条件以控制局部化应力调节的量。可控制uv处理条件,例如uv暴露的时间、温度、强度和波长,以改变局部化应力调节。这些旋钮可用于调整相比于uv可固化膜301的未暴露区域在uv可固化膜301的每一暴露区域中调节多少应力。在一些实施方案中,uv暴露的时间可以介于约0.5分钟与约120分钟之间、介于约1分钟与约60分钟之间、或介于约2分钟与约30分钟之间。在一些实施方案中,uv暴露期间的衬底温度可以介于约100℃与约700℃之间、介于约150℃与约550℃之间、或介于约200℃与约500℃之间。在一些实施方案中,uv暴露的强度可介于约1μw/cm2与约10w/cm2之间、介于约10μw/cm2与约5w/cm2之间、或介于约50μw/cm2与约1w/cm2之间。在一些实施方案中,uv暴露的波长可介于约200nm与约800nm之间。

53.图3d示出了图3c的弯曲半导体衬底在uv可固化膜(设置于弯曲半导体衬底上)的一或更多个暴露区域选择性固化后的横截面示意图。uv可固化膜301包括被选择性地uv固化的暴露区域304a以及选择性隔离uv暴露的未暴露区域304b。暴露区域304a与未暴露区域304b之间的局部应力差可能很大,其中局部应力差可至少为几百mpa(例如200mpa或更大)。未暴露区域304b中的应力变化小于暴露区域304a中的应力变化。如图3d所示,在uv暴露之后,未暴露区域304b呈较小应力,而暴露区域304a呈较大应力。用预图案化掩模302进行的uv固化在弯曲半导体衬底300上提供选择性且局部化的应力变化。

54.图2b示出了根据一些实施方案制备用于局部化应力调节的掩模的示例性方法的

流程图。可以不同顺序和/或以不同、更少或额外操作来执行处理250的操作。处理250的操作可使用用于图案化掩模的装置来执行。在一些实施方案中,处理250的操作可至少部分地根据储存于一或更多个非瞬时计算机可读介质中的软件来实施。

55.在处理250的框260中,可选地接收半导体衬底的应力图,其指示半导体衬底的一或更多个区域中不对称弯曲的程度。在一些实施方案中,半导体衬底包括图案化3d-nand结构及半导体衬底中的一或更多个蚀刻沟槽。应力图可指示半导体衬底的局部化区域中的弯曲程度。半导体衬底的一或更多个区域反应高压缩应力或拉伸应力的区域。高压缩应力或拉伸应力的区域可大于约

±

200mpa。

56.在处理250的框270中,在掩模中图案化一或更多个开口以形成预图案化掩模,其中图案化的一或更多个开口至少部分地基于半导体衬底的应力图和/或半导体衬底的管芯间距。可使用不同几何形状掩模技术来制作掩模中的一或更多个开口,以形成预图案化掩模。在一些实施方案中,识别高压缩或拉伸应力的区域。在一些实施方案中,该一或更多个开口对应于高压缩或拉伸应力的区域。额外或可替代地,确定半导体衬底的管芯间距。在一些实施方案中,该一或更多个开口基于预定的管芯间距而间隔开。预图案化掩模可由配置成阻挡或实质上阻挡uv辐射的材料制成。

57.图4示出根据一些实施方案的示例性预图案化掩模的示意图,该预图案化掩模用于选择性地暴露uv可固化膜的区域以进行局部化应力调节。预图案化掩模400配置成覆盖半导体衬底(未示出)。预图案化掩模中的开口401允许uv辐射通过。开口401的位置、尺寸和形状被设计成解决半导体衬底中局部化弯曲/应力的区域。在一些案例中,局部化弯曲/应力的区域可能是3d-nand结构中沿单轴方向(例如y轴方向)纵向延伸的金属线所导致。然而,3d-nand结构可能缺少沿垂直方向(例如,x轴方向)延伸的金属线。因此,开口401可被图案化以对应于半导体衬底上3d-nand结构中的金属线的配置。

58.返回图2b,在处理250的框280中,将预图案化掩模提供在uv室中,其中预图案化掩模被配置成,当半导体衬底暴露于uv辐射时,使沉积在半导体衬底上的uv可固化膜的一或更多个暴露区域变得比uv可固化膜的一或更多个未暴露区域更具拉伸性或更具压缩性。预图案化掩模被提供于配置成发射uv辐射的uv源与半导体衬底之间。uv可固化膜可沉积于半导体衬底的前侧或背侧上。在一些实施方案中,uv可固化膜包含超低k介电材料或氮化物,例如氮化硅。预图案化掩模下方的区域被阻止uv固化以限定未暴露区域,而一或更多个开口下方的区域则暴露于uv固化以限定暴露区域。暴露区域比未暴露区域发生更大的应力变化,从而可在半导体衬底中调节局部化应力。装置

59.所公开的实施方案可以在任何合适的装置或工具中执行。装置或工具可包括一或更多个处理站。以下描述可用于一些实施方案中的示例性处理站和工具。

60.图5示出了根据一些实施方案用于沉积uv可固化膜的示例性装置的示意图。在一些实施方案中,处理站500被配置成用于pecvd处理。处理站500包括能够维持在低压环境的处理室主体502。在一些实施方案中,pecvd处理站500的一或更多个硬件参数(包括以下详细讨论的那些)可由一或更多个计算机控制器550以程序化方式进行调整。

61.pecvd处理站500与反应物输送系统501a流体连通,以将处理气体输送至分布喷头506。反应物输送系统501a包括混合容器504,其用于混合和/或调节处理气体,以输送至喷

头506。处理气体(例如用于在衬底上沉积uv可固化膜的那些)可使用反应物输送系统501a经由喷头506输送至处理室主体502。在一些实施方案中,反应性物质可使用反应物输送系统501a来输送。一或更多个混合容器入口阀520可控制处理气体引入混合容器504。这些阀可根据在多种操作期间是否打开气体来控制。

62.注意,在一些实施方案中,可不使用液体反应物。然而,在一些实施方案中,可使用液体反应物以形成本文所述的拉伸或压缩膜。举例而言,图5的实施方案包含汽化点503,用于汽化将供应至混合容器504的液体反应物。在一些实施方案中,汽化点503可以是加热的蒸发器。从这样的蒸发器产生的饱和的反应物蒸气会在下游输送管道凝结。不兼容气体暴露至凝结的反应物会产生小颗粒。这些小颗粒可能阻塞管道、阻碍阀操作、污染衬底等。处理这些问题的一些方法涉及在汽化反应物之前或之后清扫和/或排空输送管道以去除残留反应物。然而,清扫输送管道会增加处理站循环时间、降低处理站吞吐量。因此,在一些实施方案中,汽化点503下游的输送管道可以被热追踪。在一些示例中,混合容器504也可以被热追踪。在一个非限制性示例中,汽化点503下游的管道具有增大的温度分布,在混合容器504处从约100℃延伸至约150℃。

63.在一些实施方案中,液体前体或者液体反应物(例如含硅前体)可以在液体喷射器处汽化。例如,液体喷射器可以将液体反应物的脉冲喷射到混合容器上游的载气流中。在一个实施方案中,液体喷射器可以通过将液体从较高压闪变到较低压来汽化反应物。在另一个示例中,液体喷射器可以将液体雾化为接下来在加热的输送管中汽化的分散的微滴。较小的液滴比较大的液滴可以较快汽化,从而减小了在液体注入和完成汽化之间的延迟。较快的汽化可以减小汽化点503下游的管道长度。在一个方案中,液体喷射器可以直接装载到混合容器504。在另一个方案中,液体喷射器可以直接安装到喷头506上。

64.在一些实施方案中,可以在汽化点503上游设置液体流控制器(lfc)来控制用于汽化并输送至处理站500的液体的质量流量。例如,lfc可以包含位于lfc下游的热质量流量计(mfm)。然后可以响应于由与mfm电通信的比例积分微分(pid)控制器提供的反馈控制信号,来调节lfc的柱塞阀。然而,其可以采取一秒或一秒以上来使用反馈控制以稳定液体流。这可以延长使液体反应物流动的时间。因此,在一些实施方案中,lfc可以在反馈控制模式和直接控制模式之间动态切换。在一些实施方案中,这可以通过禁用pid控制器和lfc的感测管道来进行。

65.喷头506向衬底512分布气体。例如,喷头506可在多种操作中将用于沉积uv可固化膜的处理气体分布至衬底512的背侧或前侧,例如含硅气体和/或含氧或含氮气体。在图5所示的实施方案中,衬底512位于喷头506下方,并显示为留置于基座508上。在一些实施方案中,基座508可以包括通过边缘保持晶片的晶片保持件以及用于将气体输送至晶片背侧的底部喷头(未示出)。喷头506可具有任何合适的形状,且可具有用于将处理气体分布至衬底512的任何适当数量和布置的端口。屏蔽件(未示出)也可存在于室主体502中。

66.在另一情况中,调整基座508高度可允许在所公开的处理期间改变等离子体密度,从而改变晶片与底部喷头之间的等离子体密度。例如,等离子体可在处理气体流至室主体502时被激励。在该处理结束时,可在另一衬底转移阶段期间降低基座508,以允许衬底512从基座508上移除。

67.在一些实施方案中,喷头506及基座508与射频(rf)功率供应源514和匹配网络516

电气连通以对等离子体供电。在一些实施方案中,等离子体能量可通过控制处理站压力、气体浓度及气体分压或气体流速、rf源功率及rf源频率中的一或更多者来控制。例如,rf功率源514和匹配网络516可以在任何合适的功率下进行操作,以形成具有所期望的自由基物质的组分的等离子体。同样,rf功率源514可提供任何合适频率的rf功率。在一些实施方案中,rf功率源514可以被配置为控制彼此独立的高频rf功率源和低频rf功率源。示例性的低频rf频率可以包含,但不限于,介于0khz和500khz之间的频率。示例性的高频rf频率可以包含,但不限于,介于1.8mhz和2.45ghz之间的频率,或大于约13.56mhz、或大于27mhz、或大于40mhz、或大于60mhz的频率。应当理解,任何合适的参数可被离散地或连续地调整,以对用于沉积弯曲补偿层的反应提供等离子体能量。

68.在一些实施方案中,等离子体可由一个或多个等离子体监控器原位监控。在一种情形中,等离子体功率可通过一个或多个电压、电流传感器(例如,vi探针)进行监控。在另一种情况下,等离子体密度和/或处理气体的浓度可以由一个或多个光发射光谱传感器(oes)来测量。在一些实施方案中,一个或多个等离子体参数可基于来自这样的原位等离子体监控器的测量结果通过编程方式进行调节。例如,oes传感器可用于反馈回路中以提供对等离子体功率的编程式控制。应理解的是,在一些实施方案中,可使用其它监控器来监控等离子体和其它工艺特性。这样的监控器可包含,但不限于,红外(ir)监控器、声学监控器、以及压力传感器。

69.在一些实施方案中,可以经由输入/输出控制(ioc)测序指令来提供用于控制器450的指令。在一个示例中,用于设置处理阶段的条件的指令可被包含在处理配方的相应的配方阶段中。在某些情况下,处理配方阶段可按顺序排列,使得用于处理阶段的所有指令与该处理阶段同时进行。在一些实施方案中,用于设定一个或多个反应器参数的指令可以被包含在配方阶段中。例如,第一配方阶段可包括用于设定一或更多种气体(例如,含硅气体及含氮气体)的流速的指令以及用于第一配方阶段的时间延迟指令。第二后续配方阶段可包括用于设定清扫气体的流速的指令以及用于第二配方阶段的时间延迟指令。替代地,第三配方阶段可包括用于设定一或更多种气体(例如,含硅气体及含氧气体)的流速的指令以及用于第三配方阶段的时间延迟指令。应理解,这些配方阶段可在本发明的范围内以任何合适的方式进一步细分和/或重复。控制器550也可包括以下关于图7中的控制器750所述的任何特征。

70.在一些实施方案中,基座508可通过加热器510进行温度控制。加热器510可用于加热衬底。例如,在一些实施方案中,在加热期间,加热器510可设定成介于约200℃与约500℃之间的温度。此外,在一些实施方案中,对处理站500的压力控制可通过蝶阀518来提供。如图5的实施方案中所示,蝶阀518对下游真空泵(未示出)所提供的真空进行节流。然而,在一些实施方案中,处理站500的压力控制也可通过改变引入处理站500的一或更多种气体的流速来调整。

71.图6示出了根据一些实施方案用于uv可固化膜的uv固化的示例性装置示意图。装置601适合涉及宽带uv源的用途。装置601包括多个固化站603和705,每一固化站容纳衬底613和615。衬底613和615位于基座623和625上方。衬底与基座之间存在间隙604。衬底可以通过固定件(例如销)支撑于基座上方,或漂浮在气体上。抛物线或平面冷镜653和655位于宽带uv源633和635上方。来自灯组633和635的uv光穿过窗口643和645。衬底613和615接着

暴露于uv辐射。在可替代实施方案中,衬底可由基座623和625支撑。在这种实施方案中,灯可配有或可不配备冷镜。通过与基座完全接触,可通过使用传导气体(例如氦或氦与氩的混合物)来维持衬底温度,该传导气体处于足以热传导的压力,通常介于约20与约760托之间、或介于约100托与600托之间。

72.在操作中,衬底进入站603处的室,第一uv固化操作在其中执行。第一预图案化掩模(未示出)可提供于衬底613与窗口643之间。站603处的基座温度设定成例如介于约200℃与约500℃之间的第一温度,且站603上方的uv灯设定成例如100%最大强度的第一强度和例如约200-800nm的第一波长范围。在一些实施方案中,在站603中固化足够时间之后,衬底可被转移至站605以进一步固化。第二预图案化掩模(未示出)可以提供于衬底615与窗口645之间。站605处的基座温度设定成与第一站相同或不相同的第二温度,而uv强度设定成例如90%强度的第二强度。额外的站可用于在不同条件下进行额外uv固化。

73.为了在使用宽带uv源(其产生宽光谱的辐射)时以不同波长或波长范围照射衬底,可在辐射源中使用光学部件以调节宽光谱到达衬底的部分。例如,反射片、滤光片或反射片与滤光片两者的组合可用于从辐射中减去光谱的一部分。到达滤光片后,光可被反射、吸收至滤光片材料中或透射穿过。

74.高通滤光片(long pass filter)为干涉滤光片,其提供特定波长以下的锐截止。其可用于隔离光谱的特定区域。高通滤光片用于通过或透射一定波长范围,并阻止或反射通带的较短波长侧的其他波长。长波长辐射透射,而短波长辐射反射。高透射率的区域称为通带,高反射率的区域称为阻带或反射带。滚降(roll-off)区域将通带与反射带分开。长通滤波片的复杂度主要取决于过渡区域的陡度,还取决于通带中的涟波(ripple)规格。在相对高入射角的案例中,可能发生偏振相关的损耗。长通滤波片由硬的、耐用的表面材料覆盖介电涂层所构成。其设计成能承受常规清洁及处理。

75.另一类型的滤光片为uv截止滤光片。这些滤光片不允许低于例如280nm设定值的uv穿透。这些滤光片通过吸收低于截止值的波长来作用。这可能有助于将所期望的固化效果优化。

76.可用于选择波长范围的另一滤光片为带通滤光片。光学带通滤波片被设计成传送特定波段。其由许多介电材料薄层所组成,这些薄层具有不同的折射率,以在透射光中产生建设性和破坏性干涉。如此一来,光学带通滤波片可设计成仅传送特定波段。该范围限制通常取决于干涉滤光透镜和薄膜滤光材料的组成。入射光穿过两个涂覆反射面。反射涂层之间的距离决定哪些波长将产生破坏性干涉以及哪些波长将被允许通过涂覆表面。在反射光束同相(in phase)的情况下,光将穿过两个反射面。然而,如果波长反相(out of phase),破坏性干涉将阻挡大部分反射,几乎没有任何透射。以此方式,干涉滤光片能够衰减高于或低于所期望范围的波长处的透射光强度。

77.可衰减到达衬底的辐射波长的另一滤光片为窗口643,其通常由石英制成。通过改变金属杂质的水平和水含量,可使石英窗阻挡非所期望的波长的辐射。金属杂质极少的高纯度二氧化硅石英越深入,紫外线越透光。作为一示例,厚度为1cm的石英在170nm波长下将具有约50%的透射率,而在160nm处则下降至仅百分之几。增加石英中杂质含量导致较低波长uv的透射率降低。电熔融石英具有更多金属杂质的存在,将其uv透射波长限制至200nm左右或更长。另一方面,合成二氧化硅具有更高纯度,并将下移至170nm。对于红外辐射,通过

石英的透射率取决于水含量。石英中更多水意味着更容易吸收红外辐射。石英中的水含量可通过制造处理来控制。因此,可控制穿过石英窗的辐射透射光谱,以截止或减小较短波长的uv透射和/或减小较长波长的红外透射。

78.除了通过改变到达衬底的辐射来改变波长外,还可通过改变光产生器的性质来控制辐射波长。宽带uv源可产生uv到红外线的广泛辐射光谱,但其他光产生器也可用于放出较小光谱或增加较窄光谱的强度。其他光产生器可以是汞蒸气灯、掺杂汞蒸气灯、电极灯、准分子灯、准分子激光、脉冲氙灯、掺杂氙灯。激光(例如准分子激光)可发射单一波长的辐射。当对汞蒸气和氙灯中添加掺杂物时,窄波段的辐射可能会变得更强。常见的掺杂物为铁、镍、钴、锡、锌、铟、镓、铊、锑、铋或这些的组合。例如,掺杂有铟的汞蒸气灯在可见光谱和450nm左右强放光;铁,在360nm处强放光;而镓,在320nm处强放光。辐射波长也可通过改变灯的填充压力来控制。例如,可用高压汞蒸气灯以更强地发射250nm至440nm(尤其是310nm至350nm)的波长。低压汞蒸气灯发射较短波长。

79.除了改变光产生器性质以及使用滤光片外,也可使用优先传送灯光谱输出的一或更多个片段的反射片。常用的反射片为冷镜,其允许红外辐射通过但反射其他光。可使用优先反射谱带的光的其他反射片。因此,衬底可在不同站处暴露于不同波长的辐射。当然,辐射波长在一些站中可以相同。

80.在图6中,基座623和625是固定的。转位器(indexer)611在每个暴露时段之间将每一衬底从一基座提升并移动至另一者。转位器611包括附接至具有旋转以及轴向运动的运动机构631的转位板621。对转位板621供给向上轴向运动以从每一基座拾取衬底。旋转运动用于将衬底从一站推进至另一站。然后,运动机构接着对板供给向下轴向运动,以将衬底向下放至站上。

81.基座623和625被电加热并保持于所期望的处理温度。基座623和625也可配置有冷却线以实现精确的衬底温度控制。在可替代实施方案中,可使用大的加热块来支撑衬底,以取代各个基座。使用导热气体(例如氦)以在基座与衬底之间达到良好的热耦合。在一些实施方案中,可使用具有同轴热交换器的铸造基座。

82.图6仅示出了合适装置的示例,并且可使用针对先前和/或后续处理中涉及的其他方法所设计的其他装置。例如,在使用宽带uv源的另一实施方案中,衬底支撑件为转盘(carousel)。不同于固定式基座衬底支撑件,衬底不会相对于转盘移动。在衬底装载至转盘上之后,如果需要,转盘旋转以将衬底暴露于来自uv灯组的光。转盘在暴露期间是静止的。暴露期过后,转盘旋转以推进每一衬底以暴露至下一组灯。加热和冷却元件可嵌于旋转的转盘内。可替代地,转盘可与加热板接触或保持衬底,使得其悬挂于加热板上方。

83.在某些实施方案中,将衬底暴露于来自聚焦而非泛光灯的uv辐射。不同于衬底在暴露期间呈静止(如图6所示)的宽带源实施方案,当扫描衬底时,在暴露于聚焦光期间,衬底与光源之间有相对移动。在其他实施方案中,衬底可相对于光源旋转,以平均衬底上的强度差异。

84.图7示出了根据一些实施方案用于执行局部化应力调节操作的示例性处理工具的示意图。多站处理工具700可包括入站装载室702和出站装载室704,其一者或两者可以包括等离子体源和/或uv源。处于大气压下的机械手706配置成将晶片通过晶舟(pod)708装载的盒通过大气端口710移动至入站装载室702。晶片(未示出)通过机械手706被放置在入站装

载室702中的基座712上,大气端口710被关闭,接着入站装载室702被抽空。在入站装载室702包括远程等离子体源的情况下,晶片可以在引入处理室714之前暴露于入站装载室702中的远程等离子体处理。此外,晶片也可在入站装载室702中被加热,例如以去除水分及吸附的气体。接着,打开通往处理室714的室转移端口716,且另一机械手(未示出)将晶片放入反应器中第一站的基座上(示于反应器中)以进行处理。尽管描绘于图7中的实施方案包括装载室,但应理解,在一些实施方案中,可使晶片直接进入处理站。

85.所描绘的处理室714包括四个处理站,在图7所示的实施方案中从1到4编号。每一站具有加热基座(示于站1的718)及气体管线入口。应理解,在一些实施方案中,每一处理站可具有不同或多个目的。例如,在一些实施方案中,处理站可在cvd与pecvd处理模式之间切换。在另一示例中,可在一站中执行沉积操作,并可在另一站中执行暴露于uv辐射以进行uv固化。在一些实施方案中,沉积和uv固化在同一站中进行。尽管所描绘的处理室714包括四个站,但应理解,根据本发明的处理室可具有任何合适数量的站。例如,在一些实施方案中,处理室可具有五或更多站,而在其他实施方案中,处理室可以具有三个或更少站。

86.图7绘出了用于在处理室714内传输晶片的晶片搬运系统790的一个实施方案。在一些实施方案中,晶片搬运系统790可以在各种处理站之间和/或处理站与装载室之间传输晶片。应该理解的是,可以采用任何适当的晶片搬运系统。非限制性示例包含晶片转盘和搬运晶片的机械手。图7还绘出了用来控制处理工具700的处理条件和硬件状态的系统控制器750的一个实施方案。系统控制器750可以包含一个或多个存储器设备756、一个或多个海量存储设备754和一个或多个处理器752。处理器752可以包含计算机或者cpu、模拟和/或数字输入/输出连接、步进马达控制器板等。

87.在一些实施方案中,系统控制器750控制处理工具700的所有活动。系统控制器750执行存储在海量存储设备754、载入存储器设备756、并由处理器752执行的系统控制软件758。替代地,控制逻辑可以在控制器750中硬编码。特定应用集成电路、可编程逻辑设备(例如,现场可编程栅极阵列、或者fpga)等可以用于这些目的。在下面的讨论中,无论使用“软件”还是“代码”,可以使用功能上相当的硬编码的逻辑来取代。系统控制软件758可以包含用于控制时序、气体的混合、气体流率、室和/或站压强、室和/或站温度、晶片温度、目标功率电平、rf功率电平、衬底基座、卡盘和/或基座位置、以及由处理工具700进行的特定处理的其它参数的指令。系统控制软件758可以以任何适当的方式配置。例如,各种处理工具组件子程序或者控制对象可以写入以控制用于进行各种处理工具处理的处理工具组件的操作。系统控制软件758可以以任何适当的计算机可读编程语言来编码。

88.在一些实施方案中,系统控制软件758可以包含用于控制上述各种参数的输入/输出控制(ioc)测序指令。在一些实施方案中可以采用与系统控制器750关联的、存储在海量存储设备754和/或存储器设备756的其它计算机软件和/或程序。用于该目的的程序或者程序段的示例包含衬底定位程序、处理气体控制程序、压力控制程序、加热器控制程序、以及等离子体控制程序。

89.衬底定位程序可以包含用于处理工具组件的程序代码,该处理工具组件用于将衬底装载到基座718,并且控制衬底和处理工具700的其它部分之间的间隔。

90.处理气体控制程序可以包含用于控制气体组成(例如,本文所述的诸如含硅气体、含氧气体、用于执行投配后处理的气体、和清扫气体)和流率的代码和任选地用于使气体在

沉积之前流到一个或多个处理站中以稳定在处理站中的压强的代码。压强控制程序可以包含用于通过调节例如在处理站的排放系统中的节流阀、流入处理站内的气流等等来控制处理站内的压强的代码。

91.加热器控制程序可包含用于控制流向用于加热衬底的加热单元的电流的代码。替代地,加热器控制程序可控制传热气体(如氦气)朝向衬底的传送。

92.等离子体控制程序可包含用于根据本文的实施方案设置施加到一个或多个处理站内的处理电极的rf功率电平的代码。

93.压强控制程序可以包含用于根据本文的实施方案保持反应室内的压强的代码。

94.在一些实施方案中,可以存在与系统控制器750相关联的用户界面。用户界面可以包含显示屏、装置和/或工艺条件的图形软件显示器、以及诸如定点设备、键盘、触摸屏、麦克风等用户输入设备。

95.在一些实施方案中,由系统控制器750调节的参数会涉及工艺条件。非限制性实例包含处理气体组成和流率、温度、压强、等离子体条件(例如,rf偏置功率电平)、压强、温度等。这些参数可以以配方的形式提供给用户,配方可以利用所述用户界面输入。

96.用于监控处理的信号可以由系统控制器750的模拟和/或数字输入连接件从各种处理工具传感器提供。用于控制处理的信号可以通过处理工具700的模拟和数字输出连接件输出。可被监控的处理工具传感器的非限制性实例包含质量流量控制器、压力传感器(例如压力计)、热电偶等等。经适当编程的反馈和控制算法可以与来自这些传感器的数据一起使用,以保持工艺条件。

97.系统控制器750可以提供用于进行上述沉积处理的程序指令。所述程序指令可以控制多种处理参数,如dc功率电平、rf偏置功率电平、压强、温度等。所述指令可以控制这些参数以根据本发明所描述的多种实施方案操作膜叠层的原位沉积。

98.系统控制器750将通常包含一个或多个存储器设备和被配置成进行指令的一个或多个处理器以使该装置将进行根据所公开的实施方案所述的方法。包含用于控制根据所公开的实施方案的处理操作的指令的机器可读的介质可以耦合到系统控制器750。

99.在一些实现方案中,系统控制器750是系统的一部分,该系统可以是上述示例的一部分。这种系统可以包含半导体处理设备,该半导体处理设备包含一个或多个处理工具、一个或多个处理室、用于处理的一个或多个平台和/或具体的处理组件(晶片基座、气流系统等)。这些系统可以与用于控制它们在处理半导体晶片或衬底之前、期间和之后的操作的电子器件一体化。电子器件可以称为“控制器”,该控制器可以控制一个或多个系统的各种元件或子部件。根据处理要求和/或系统的类型,系统控制器750可以被编程以控制本文公开的任何工艺,包含控制处理气体输送、温度设置(例如,加热和/或冷却)、压强设置、真空设置、功率设置、射频(rf)产生器设置、rf匹配电路设置、频率设置、流率设置、流体输送设置、位置及操作设置、晶片转移进出工具和其它转移工具和/或与具体系统连接或通过接口连接的装载室。

100.广义而言,系统控制器750可以定义为接收指令、发布指令、控制操作、启用清洁操作、启用端点测量等等的具有各种集成电路、逻辑、存储器和/或软件的电子器件。集成电路可以包含存储程序指令的固件形式的芯片、数字信号处理器(dsp)、定义为专用集成电路(asic)的芯片和/或一个或多个微处理器或进行程序指令(例如,软件)的微控制器。程序指

令可以是以各种单独设置的形式(或程序文件)传送到系统控制器750的指令,该设置定义用于在半导体晶片或系统上或针对半导体晶片或系统进行特定处理的操作参数。在一些实施方案中,操作参数可以是由工艺工程师定义的用于在制备晶片的一个或多个(种)层、材料、金属、氧化物、硅、二氧化硅、表面、电路和/或管芯期间完成一个或多个处理步骤的配方(recipe)的一部分。

101.在一些实现方案中,系统控制器750可以是与系统集成、耦合或者说是通过网络连接系统、或它们的组合的计算机的一部分或者与该计算机耦合。例如,系统控制器750可以在“云端”或者是晶片厂(fab)主机系统的全部或一部分,从而可以允许远程访问晶片处理。计算机可以启用对系统的远程访问以监控制造操作的当前进程、检查过去的制造操作的历史、检查多个制造操作的趋势或性能标准,以改变当前处理的参数、设置处理步骤以跟随当前的处理或者开始新的工艺。在一些示例中,远程计算机(例如,服务器)可以通过网络给系统提供工艺配方,网络可以包含本地网络或互联网。远程计算机可以包含允许输入或编程参数和/或设置的用户界面,该参数和/或设置然后被从远程计算机传送到系统。在一些示例中,系统控制器750接收数据形式的指令,该指令指明在一个或多个操作期间将要进行的每个处理步骤的参数。应当理解,参数可以针对将要进行的工艺类型以及工具类型,系统控制器750被配置成连接或控制该工具类型。因此,如上所述,系统控制器750可以例如通过包含一个或多个分立的控制器而为分布式,这些分立的控制器通过网络连接在一起并且朝着共同的目标(例如,本文所述的工艺和控制)工作。用于这些目的的分布式控制器的一个示例可以是与结合以控制室内工艺的一个或多个远程集成电路(例如,在平台水平或作为远程计算机的一部分)通信的室上的一个或多个集成电路。其他实施方案

102.在前文描述中,阐述许多具体细节以提供对所呈现的实施方案的透彻理解。可在没有这些具体细节中的一些或全部的情况下实行所公开的实施方案。在其他实例中,不再详细描述众所周知的处理操作,以免不必要地使所公开的实施方案难以理解。尽管结合具体实施方案来描述所公开的实施方案,但应理解,其并非意在限制所公开的实施方案。

103.虽然上述实施方案已经为了清楚理解的目的在一些细节方面进行了描述,但显而易见的是,某些变化和修改方案可在所附权利要求的范围内实施。应当注意的是,具有实施本发明的实施方案的过程、系统和装置的许多替代方式。因此,本发明的实施方案应被视为是说明性的而不是限制性的,并且所述实施方案并不限于本文所给出的细节。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。