基于频域的时钟恢复

背景技术:

1.在串行通信中,串行数据从发射器传输到接收器。在一些串行通信技术中,时钟不与数据一起传输。相反,接收器包括时钟和数据恢复(cdr)电路,以从串行数据中提取时钟,并使用所提取的时钟对所传输的符号进行解码。

2.一些cdr实施方式需要使用参考时钟。用于cdr电路的参考时钟在包含接收器的芯片外部生成,并因此一个引脚专用于接收参考时钟。在有损信道中,接收器接收到的串行数据可能遭受较大的符号间干扰。

技术实现要素:

3.在一个示例中,时钟数据恢复电路包括具有数据输入端、第二输入端和输出端的相位检测器(pd)。该电路还包括滤波器、第一电荷泵和第二电荷泵、压控振荡器(vco)和频率检测器(fd)。第一电荷泵耦合在pd的输出端和滤波器之间。vco具有第一输入端和第二输入端以及输出端。vco的第一输入端耦合到滤波器,并且vco的输出端耦合到pd的第二输入端。fd具有数据输入端、第二输入端以及第一输出端和第二输出端。fd的第二输出端耦合到vco的第二输入端。fd的数据输入端耦合到相位检测器的数据输入端,并且fd的第二输入端耦合到vco的输出端。第二电荷泵耦合在fd的第一输出端和滤波器之间。

附图说明

4.对于各种示例的详细描述,现在将参考附图,在附图中:

5.图1示出了根据所公开示例的包括具有cdr电路的接收器的示例串行通信。

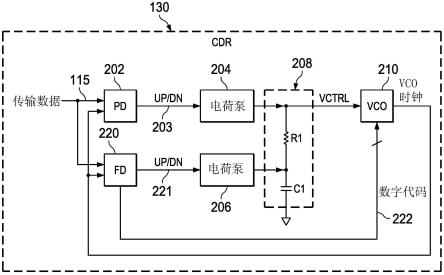

6.图2示出了图1的cdr电路的示例实施方式。

7.图3示出了用于在图2的cdr电路中使用的压控振荡器的示例。

8.图4示出了图2的cdr电路的频率检测器的示例实施方式。

9.图5示出了图4的频率检测器的传输单频(tone)提取器的示例实施方式。

10.图6示出了图4的频率检测器的峰值单频检测器的示例实施方式。

11.图7图示了图6的峰值单频检测器的操作。

12.图8图示了图4的频率检测器内的数字代码生成器有限状态机的操作。

13.图9图示了图4的频率检测器用于生成上/下信号到图2的cdr电路内的滤波器的操作。

具体实施方式

14.如上所述,一些cdr实施方式需要使用外部供应的参考时钟。这种参考时钟通常需要芯片上的专用引脚来接收外部生成的参考时钟。使用专用引脚抬高物料清单(bom)成本,并使其上使用了需要外部供应的参考时钟的接收器的印刷电路板的设计复杂化。本文描述的示例涉及不需要外部供应的参考时钟的cdr电路。此外,本文描述的cdr电路独立于数据调制技术,这意味着该cdr电路可以从已用各种调制技术(例如,脉冲幅度调制(pam)、不归

零(nrz)等)中的任何调制技术调制的串行数据中恢复时钟。

15.图1图示了串行通信系统100,该系统包括通过通信链路115耦合到接收器120的发射器110。发射器110使用传输时钟将数据编码成串行通信流,并通过串行通信链路115将传输数据发送到接收器120。传输数据速率是发射器110向接收器120传输串行数据的频率。接收器120包括cdr电路130,该电路从于发射器接收的串行传输数据中提取时钟并使用所提取的时钟来对传输的符号进行解码,从而产生恢复的数据,以供例如包含rx 120的半导体管芯(芯片)内的其他电路使用。虽然传输数据在图1的示例中被示出为cdr 130的输入,但是cdr 130的输入不一定是直接来自通信链路115的传输数据。在一些示例中,接收器可以具有在该接收器的输入端和cdr之间的其他部件,诸如连续时间均衡器(也称作ctle或连续时间线性均衡器)。

16.图2示出了cdr电路130的至少一部分的示例。在该示例中,cdr电路130包括相位检测器(pd)202、电荷泵204和206、滤波器208、压控振荡器210和频率检测器(fd)220。来自发射器110的传输数据被提供给pd 202和fd 220两者的输入端。vco 210的输出端提供了被提供给pd 202和fd 220的其他输入端的vco时钟。vco时钟频率可以是“恢复的时钟频率”的约数(submultiple),该“恢复的时钟频率”是接收器对传输数据速率的估计。pd 202基于输入传输数据和vco时钟之间的相位差生成输出上和下(up/dn)信号203。来自pd 202的输出上/下信号203被提供给电荷泵204。电荷泵204耦合到滤波器208。基于up/dn信号203,正电流要么从电荷泵204流入滤波器208(例如,当up激活时),要么从滤波器流入电荷泵(例如,当dn激活时)。滤波器208向vco 210提供压控(vctrl)信号。vctrl控制vco 210产生的vco时钟的频率。

17.fd 220基于传输数据速率和恢复的时钟频率之间的频率差向其对应的电荷泵206生成up/dn信号221。fd 220还向vco 210生成数字代码222。如下文所述,数字代码由fd 220生成并且还控制vco的vco时钟的频率。当cdr 130“锁定”(即,锁定到传输数据频率)时,vco时钟表示从传输数据中提取的时钟,并且可以由数据恢复电路使用以恢复所传输的单频。

18.在图2中可以看出,cdr电路130不使用外部提供的参考时钟。在其他cdr实施方式中,参考时钟可以用于控制到vco的数字代码值。然而,在图2的示例中,fd 220不使用外部提供的参考时钟来向vco 210生成数字代码。相反,fd 220基于包括传输数据和vco时钟的信号来生成数字代码222。

19.图3示出了图2的vco 210的示例实施方式。在图3的示例中,vco 210是lc vco并包括电感器l1和l2、晶体管m1、m2、m3和m4、电容器c1、c2、

……

、cn。对于每个电容器c1-cn,对应的开关sw1、sw2、

……

、swn将电容器耦合到地。每个电容器可以通过接通相应开关来选择(耦合到地),并且可以通过关断相应开关来取消选择。fd 220生成的数字代码用于控制开关sw1-swn的通/断状态。

20.电感器l1耦合在vdd和m1的漏极以及节点x处的示意图左侧上的电容器之间。l2耦合在vdd和m2的漏极以及节点y处的示意图右侧上的电容器之间。m1的栅极耦合到节点y,并且m2的栅极耦合到节点x。电流源iss耦合到m1和m2的源极,并提供通过m1和m2的偏置电流。

21.m3的栅极耦合到节点x。m3的漏极和源极耦合在一起并接收控制电压vctrl。类似地,m4的栅极耦合到节点y。m4的漏极和源极耦合在一起并且也接收控制电压vctrl。lc vco的振荡频率随着连接到节点x和y的电容c的增加而降低。电容c可以分为由数字代码控制的

电容cx和由控制电压vctrl控制的通常是“变容管(varactor)”另一电容cy。图3的vco的输出是节点x和y之间的电压差。在其他实施方式中,vco 210可以包括环形振荡器。同样在这种情况下,vco频率将具有由数字代码控制的分量和由模拟控制电压vctrl控制的另一分量。

22.图4示出了fd 220的示例实施方式。fd 220包括传输单频提取器310、峰值单频检测器320、数字代码生成器有限状态机(fsm)和up/dn脉冲生成器339。up/dn脉冲生成器339包括减法器340和符号(sign)电路350。传输单频提取器310具有接收传输数据的输入端并产生输出信号y(n),如下文将说明的。传输单频提取器310的输出端耦合到峰值单频检测器320的输入端。峰值单频检测器320将y(n)转换到频域并确定出现最大谱单频所在的频率(fpk)。最大谱单频的幅度为。被提供给数字代码生成器fsm 330。数字代码生成器fsm 330基于的值生成数字代码222。峰值单频检测器320向减法器340提供fpk322,该减法器确定fpk的频率和恢复的时钟频率(fbrx)之间的差。该差被提供给sign 350,该sign 350向电荷泵206生成up/dn信号222。如果fpk-fbrx大于或等于0,则sign 350向电荷泵206生成up脉冲。否则(如果fpk-fbrx小于0),则sign 350生成dn脉冲。

23.图5示出了传输单频提取器310的示例实施方式。示例传输单频提取器310包括采样器410、sign 420和转变检测器429。来自通信链路115的传输数据被提供给采样器410的一个端子。传输数据包括根据提供给采样器410的时钟采样的模拟电压。控制采样器410的时钟可以从vco时钟得出。

24.来自采样器410的输出包括一系列离散时间采样的模拟电压,然后将该模拟电压提供给sign 420。sign 420对采样电压进行量化以产生x(n)。针对等于或大于阈值(例如,0)的每一个输入采样电压,sign 420输出 1(或等效值);否则(对于小于阈值的输入采样电压),sign 420输出-1(或等效值)。这样,sign 420将来自采样器410的输入采样电压的时间序列转换为 1和-1的输出序列x(n)。

25.如下文将关于图6说明的,峰值单频检测器320将其输入信号转换到频域以识别具有峰值谱单频的频率,其为传输数据速率。在调制方案(诸如nrz或pam4(或其他更高级的方案))中,所传输的信号的dft或傅里叶谱可以示出为在传输数据速率的整数倍下具有空值(值0)。即使在任何连续时间均衡以及sign 420操作之后,空值也将保持不变。因此,x(n)的dft在传输数据速率的整数倍下也将具有空值。

26.如上所示,通过例如离散傅里叶变换器将来自采样器410的采样电压或来自sign 420的x(n)直接转换到频域将导致传输数据速率下的零谱值。因此,计算来自采样器410的采样电压或x(n)的离散傅里叶变换(dft)将是没有用的。相反,x(n)被提供给产生输出信号y(n)的转变检测器429。转变检测器429包括乘法器440和延迟元件430,并且将y(n)计算为x(n)x(x(n-1),即x(n)与x(n)的一个样本延迟版本的乘积。在一个实施方式中,乘法器440被实施为异或门。通常,转变检测器429是确保在传输数据速率下存在输出的傅里叶变换的非零值的任何非线性运算。

27.计算y(n)的dft有利地导致在传输数据速率下的非零谱单频。例如,对于无损信道,y(n)的离散时间傅里叶变换可以示出为其中ts是采样器

410中使用的时钟的采样率。假设并且因此y(n)是用于提取传输数据速率的方便选择。在一个实施方式中,采样率ts选为1/(4*fbrx),其中fbrx是恢复的时钟频率,因此表示过采样因数4。

28.图6示出了峰值单频检测器320的示例实施方式。在该示例中,峰值单频检测器320包括耦合到峰值频率检测器520的dft 510。dft 510的输入是来自传输单频提取器310的y(n)。dft 510计算y(n)的dft以将y(n)转换为其频域对应形式。如果dft 510的输入序列y(n)具有n个点,则dft 510的输出由给出。峰值频率检测器520接收并确定和fpk。值是在传输波特率下出现的最大谱单频的幅度,并且fpk是峰值单频的频率(即,fpk表示传输波特率)。峰值频率检测器520可以实施为包括逻辑门、触发器、比较器等的组合的离散数字电路,并且可以使用任何合适的电路合成工具基于本文所述的功能来合成。

29.图7图示了关于峰值频率检测器520如何确定和fpk的一种可能方法。该方法将频率索引k扫过计算出的dft()的频率分量范围,并确定哪个频率分量具有最大幅度。在610处,频率索引(k)、和fpk都初始化为0。在620处,该方法包括确定的绝对值是否大于。如果的绝对值大于,则在630处,将设置为当前索引的频率单频(),并且将fpk设置为当前索引的频率(fpk)。在640处,该方法确定k是否在所计算的dft的末尾。如果k不在所计算的dft的末尾,则k在650处递增,并且过程循环回到操作620。

30.在620处,如果确定的绝对值不大于,则跳过更新和fpk的操作630。一旦索引k达到dft谱的末尾,则该过程停止。

31.如图4所示,被提供给数字代码生成器fsm 330。值表示所计算的dft的最大幅度谱分量,并因此表示传输波特率。数字代码生成器fsm330使用生成待提供给vco 210的数字代码222。

32.图8提供了用于数字代码生成器fsm 330如何使用pk生成数字代码222的示例方法700。数字代码生成器fsm 330将数字代码222扫过其可能值的全部范围并确定dft谱针对哪个数字代码值具有最大的频率单频(即,针对哪个数字代码值,是最大值)。

33.在710和720处,数字代码生成器fsm 330将数字代码初始化为其最低值(例如,0)并将初始化为当前值。当前值是在数字代码初始化为0的情况下的最大频率单频值。该过程将迭代地增加数字代码,向上排序数字代码直到数字代码达到其最大值(最大数字代码)。在一个示例中,数字代码是m位二进制值,并从[00

…

0]到[11

…

1]排序。在一些实施方式中,数字代码被初始化为其最大值,并且然后随着通过过程的每次迭代而递减至其最小值。

[0034]

在730处,数字代码生成器fsm 330确定是否小于(对于数字代码的当前值)。第一次执行操作730,当然等于,但是对于通过该方法的每个连续迭代可能不是这种情况。如果小于,则在735处将临时变量“最佳数字代码”设置为数字代码的当前值,并在740处将重置为的当前值。在750处,数字代码生成器fsm 330确定数字代码的当前值是否已经达到其最大值(最大数字代码)。如果数字代码没有达到其最大值,则在760处,数字代码生成器fsm 330将数字代码递增并控制循环回到操作730,在操作730处,数字代码生成器fsm 330确定先前确定的是否小于针对新数字代码设置的新。一旦数字代码达到其最大值(如在750处确定的),在770处将cdr电路130从该点向前使用的数字代码的值设置为最佳数字代码,即,确定为导致最大的谱单频的数字代码。

[0035]

一旦如图8的示例方法700中所示确定了适当的数字代码,则发生cdr电路130的精细锁定。当数字代码生成器fsm 330已经完成图7的逻辑时,数字代码生成器fsm 330将标志en_cal断言(asserts)为0。图9图示了up/dn脉冲生成器339的示例操作。在810处,updn变量被初始化为0。只要en_cal不为0(如在820处确定的),控制循环回到810。一旦en_cal被确定为0(这发生在数字代码生成器fsm 330确定数字代码的适当值后),在830处根据fpk和fbrx之间的差的符号来生成up/dn脉冲(例如,如果差为正值,则为正脉冲,如果差为负值,则为负脉冲,并且如果fpk等于fbrx,则无脉冲)。电荷泵206使用up/dn脉冲将vctrl改变为vco 210。

[0036]

fd 220的频率分辨率小于pd 202的锁定范围。因此,pd 202能够锁定到传输波特率。一旦cdr电路130实现对传输波特率(在预定阈值内)的频率锁定,标志lock_det被设置为值1以指示已经实现锁定条件。在840处,方法800确定lock_det是否为1。如果不是1,则在830处生成另一个或多个up/dn脉冲。一旦实现锁定(lock_det等于1),则生成up/dn脉冲以改变vctrl的幅度的过程停止并且vctrl保持稳定在其当前水平,并伴有由于始终开启的pd 202环路而偶尔发生的变化。另外,还有其他方式确定锁相锁频已经发生,这些方式可以用于停止生成up/pdn脉冲。

[0037]

在整个说明书中使用术语了“耦合”。该术语可以涵盖实现与本公开的描述一致的功能关系的连接、连通或信号路径。例如,如果设备a生成信号以控制设备b来执行动作,则在第一示例中,设备a耦合到设备b,或在第二示例中,如果介入部件c基本上不改变设备a和设备b之间的功能关系,则设备a通过介入部件c耦合到设备b,使得设备b经由设备a生成的控制信号被设备a控制。在权利要求的范围内,在所描述的实施例中可以进行修改,并且能够实现其他实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。