1.本实用新型涉及一种栅极驱动电路,且特别是有关于一种具有低电荷分享效应的栅极驱动电路。

背景技术:

2.一般来说,栅极驱动电路包括彼此串联的多个栅极驱动单元。所述多个栅极驱动单元分别会产生栅极驱动信号以对显示面板(如,液晶显示面板、led显示显示面板、主动矩阵有机发光二极管等)的多个像素进行扫描。基于显示面板的高分辨率需求,位于像素中的电路会更为简化,从而使栅极驱动单元的电路更为复杂。

3.应注意的是,在栅极驱动单元的电路复杂度增加时,栅极驱动单元中的晶体管的寄生电容的数量会增加。寄生电容的数量的增加会产生电荷分享(charge sharing)效应。电荷分享效应会将用以产生栅极驱动信号的偏压值的电荷分享到寄生电容。因此,偏压值会被降低,进而使栅极驱动单元无法提供具有正确波型的栅极驱动信号。

4.因此,如何提供一种具有低电荷分享效应的栅极驱动电路,是本领域技术人员的研究重点之一。

技术实现要素:

5.本实用新型提供一种具有低电荷分享效应的栅极驱动电路。

6.本实用新型的栅极驱动电路包括彼此串联耦接的多个栅极驱动单元。所述多个栅极驱动单元当中的第n级栅极驱动单元包括预充电电路、复本电路、输出电路以及桥接晶体管。预充电电路反应于第(n-a)级复本信号来对偏压节点的偏压值进行预充电。复本电路耦接于偏压节点。复本电路反应于偏压值来将时钟信号作为第n级复本信号。输出电路反应于偏压值来将时钟信号作为第n级栅极驱动信号。桥接晶体管耦接于偏压节点与输出电路之间。当偏压值低于预设电压值时,桥接晶体管将偏压节点耦接至输出电路。当偏压值大于或等于预设电压值时,桥接晶体管将偏压节点与输出电路进行隔离。n是大于1的正整数。a是小于n的正整数。

7.基于上述,输出电路反应于偏压值来将时钟信号作为第n级栅极驱动信号。桥接晶体管耦接于偏压节点与输出电路之间。当偏压值大于或等于预设电压值时,桥接晶体管能够将偏压节点与输出电路进行隔离。如此一来,栅极驱动电路能够降低电荷分享效应,从而使栅极驱动单元能够提供具有正确波型的栅极驱动信号。

8.为让本实用新型的上述特征和优点能更明显易懂,下文特举实施例,并配合所附附图作详细说明如下。

附图说明

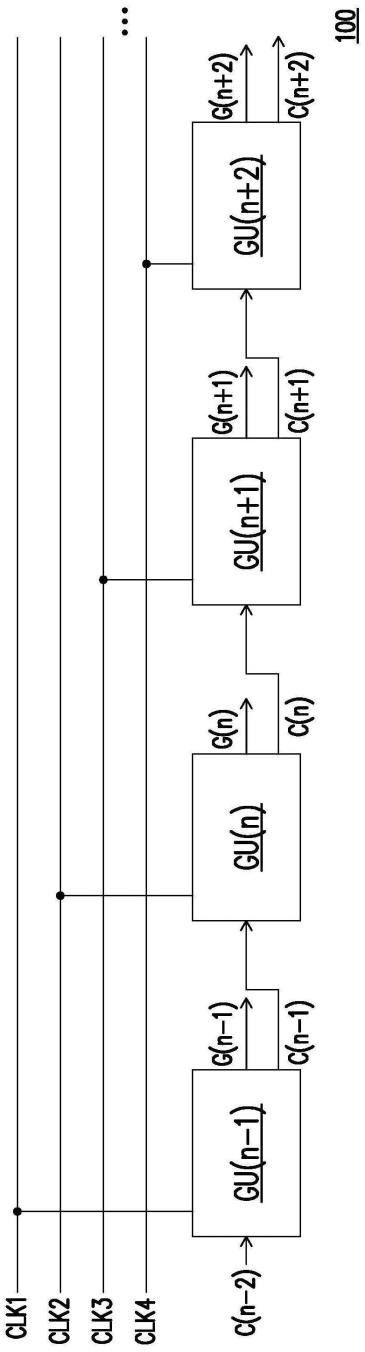

9.图1是依据本实用新型一实施例所绘示的栅极驱动电路的示意图。

10.图2是依据本实用新型第一实施例所绘示的栅极驱动单元的示意图。

11.图3是依据本实用新型第二实施例所绘示的栅极驱动单元的示意图。

12.图4是依据本实用新型一实施例所绘示的栅极驱动单元的电路图。

13.图5是依据图4所绘示的时序图。

14.图6是依据本实用新型另一实施例所绘示的栅极驱动电路的示意图。

15.附图标记说明

16.100、200:栅极驱动电路

17.110、210、310、gu(n):第n级栅极驱动单元

18.111、211、311:预充电电路

19.112、212、312:复本电路

20.113、213、313:输出电路

21.214、314:补偿电路

22.215、315:预补偿电路

23.216、316:重置电路

24.217、317:抗噪电路

25.aclk:补偿时钟信号

26.ag(n-1)、ag(n)、ag(n 1)、ag(n 2):补偿信号

27.bs、rs:信号

28.c(n-2):第(n-2)级复本信号

29.c(n-1):第(n-1)级复本信号

30.c(n-a):第(n-a)级复本信号

31.c(n):第n级复本信号

32.c(n 1):第(n 1)级复本信号

33.c(n 2):第(n 2)级复本信号

34.c(n 3):第(n 3)级复本信号

35.c(n 4):第(n 4)级复本信号

36.c(n b):第(n b)级复本信号

37.ca:电容器

38.cc:复本电容器

39.cg:输出电容器

40.ck:补偿电容器

41.clk、clk1~clk4:时钟信号

42.g(n-1):第(n-1)级栅极驱动信号

43.g(n):第n级栅极驱动信号

44.g(n 1):第(n 1)级栅极驱动信号

45.g(n 2):第(n 2)级栅极驱动信号

46.gu(n-1):第(n-1)级栅极驱动单元

47.gu(n 1):第(n 1)级栅极驱动单元

48.gu(n 2):第(n 2)级栅极驱动单元

49.m、p、q’、z:节点

50.tb1、tb2:桥接晶体管

51.q(n):偏压节点

52.rst:重置信号

53.t0~t9:时间点

54.ta1~ta5、tn1~tn10:晶体管

55.tc:复本晶体管

56.td1:显示期间

57.td2:消隐期间

58.tg:输出晶体管

59.tk:补偿晶体管

60.tp:预充电晶体管

61.tr1、tr2:重置晶体管

62.vdd:参考高电压

63.vss:参考低电压

具体实施方式

64.本实用新型的部分实施例接下来将会配合附图来详细描述,以下的描述所引用的组件符号,当不同附图出现相同的组件符号将视为相同或相似的组件。这些实施例只是本实用新型的一部分,并未揭示所有本实用新型的可实施方式。更确切的说,这些实施例只是本实用新型的专利申请范围中的范例。

65.请参考图1,图1是依据本实用新型一实施例所绘示的栅极驱动电路的示意图。在本实施例中,栅极驱动电路100对显示面板(如,液晶显示面板、led显示显示面板、主动矩阵有机发光二极管等)的多个像素进行扫描。栅极驱动电路100包括多个栅极驱动单元。所述多个栅极驱动单元彼此串联耦接。为了便于说明,本实施例示出第(n-1)级栅极驱动单元gu(n-1)、第n级栅极驱动单元gu(n)、第(n 1)级栅极驱动单元gu(n 1)以及第(n 2)级栅极驱动单元gu(n 2)来示例,本实用新型并不以此为限。

66.在本实施例中,第(n-1)级栅极驱动单元gu(n-1)接收时钟信号clk1以及第(n-2)级复本信号c(n-2),并反应于时钟信号clk1以及第(n-2)级复本信号c(n-2)来提供第(n-1)级复本信号c(n-1)以及第(n-1)级栅极驱动信号g(n-1)。第n级栅极驱动单元gu(n)接收时钟信号clk2以及第(n-1)级复本信号c(n-1),并反应于时钟信号clk2以及第(n-1)级复本信号c(n-1)来提供第n级复本信号c(n)以及第n级栅极驱动信号g(n)。第(n 1)级栅极驱动单元gu(n 1)接收时钟信号clk3以及第n级复本信号c(n),并反应于时钟信号clk3以及第n级复本信号c(n)来提供第(n 1)级复本信号c(n 1)以及第(n 1)级栅极驱动信号g(n 1)。第(n 2)级栅极驱动单元gu(n 2)接收时钟信号clk4以及第(n 1)级复本信号c(n 1),并反应于时钟信号clk4以及第(n 1)级复本信号c(n 1)来提供第(n 2)级复本信号c(n 2)以及第(n 2)级栅极驱动信号g(n 2)。在本实施例中,n是大于1的正整数。举例来说,当第(n-1)级栅极驱动单元gu(n-1)是第1级栅极驱动单元时,第(n-2)级复本信号c(n-2)可以是初始信号。

67.请参考图2,图2是依据本实用新型第一实施例所绘示的栅极驱动单元的示意图。第n级栅极驱动单元110可以实现如图1所示的第n级栅极驱动单元gu(n)。在本实施例中,第

n级栅极驱动单元110包括预充电电路111、复本电路112、输出电路113以及桥接晶体管tb1。预充电电路111反应于第(n-a)级复本信号c(n-a)来对位于偏压节点q(n)的偏压值进行预充电。a是小于n的正整数。复本电路112耦接于偏压节点q(n)。复本电路112反应于位于偏压节点q(n)的偏压值来将时钟信号clk作为第n级复本信号c(n)。输出电路113反应于位于偏压节点q(n)的偏压值来将时钟信号clk作为第n级栅极驱动信号g(n)。

68.在本实施例中,桥接晶体管tb1耦接于偏压节点q(n)与输出电路113之间。当偏压值低于第一预设电压值时,桥接晶体管tb1将偏压节点q(n)耦接至输出电路113。当偏压值大于或等于第一预设电压值时,桥接晶体管tb1则将偏压节点q(n)与输出电路113进行隔离。在此值得一提的是,输出电路113反应于偏压值来将时钟信号作为第n级栅极驱动信号g(n)。桥接晶体管tb1耦接于偏压节点q(n)与输出电路113之间。当偏压值大于或等于第一预设电压值时,桥接晶体管tb1能够将偏压节点q(n)与输出电路113进行隔离。输出电路113所接收到的偏压值不会因为电荷分享效应而被降低。如此一来,第n级栅极驱动信号g(n)能够提供具有正确波型的第n级栅极驱动信号g(n)。

69.进一步来说明,桥接晶体管tb1的第一端(如,漏极)耦接于偏压节点q(n)。桥接晶体管tb1的第二端(如,源极)耦接于输出电路113。桥接晶体管tb1例如是n型晶体管。进一步来说,桥接晶体管tb1例如是nmos晶体管。桥接晶体管tb1的控制端(如,栅极)接收高参考电压vdd。此外,上述的第一预设电压值是高参考电压vdd的电压值与桥接晶体管tb1的临界电压值之间的电压差值。因此,当输出电路113所接收到的偏压值小于对应于第一预设电压值时,高参考电压vdd的电压值与偏压值之间的电压差值大于桥接晶体管tb1的临界电压值。因此,桥接晶体管tb1的导通电流会大于0而呈现导通状态。

70.在另一方面,当输出电路113所接收到的偏压值大于或等于第一预设电压值时,高参考电压vdd的电压值与输出电路113所接收到的偏压值之间的电压差值小于或等于桥接晶体管tb1的临界电压值。因此,桥接晶体管tb1的导通电流会等于0而呈现隔离状态,或称高阻抗(hi-z)状态。当输出电路113所接收到的偏压值大于或等于第一预设电压值时,桥接晶体管tb1会对偏压节点q(n)与输出电路113进行隔离。因此,输出电路113所接收到的偏压值的电荷并不会被分享到其他的电路或是其他的栅极驱动单元。

71.请参考图3,图3是依据本实用新型第二实施例所绘示的栅极驱动单元的示意图。第n级栅极驱动单元210可以实现如图1所示的第n级栅极驱动单元gu(n)。在本实施例中,第n级栅极驱动单元210包括预充电电路211、复本电路212、输出电路213、补偿电路214、预补偿电路215、重置电路216、抗噪电路217以及桥接晶体管tb1、tb2。预充电电路211反应于第(n-a)级复本信号c(n-a)来对偏压节点q(n)的偏压值进行预充电。复本电路212耦接于偏压节点q(n)。复本电路212反应于位于偏压节点q(n)的偏压值来将时钟信号clk作为第n级复本信号c(n)。输出电路213反应于位于偏压节点q(n)的偏压值来将时钟信号clk作为第n级栅极驱动信号g(n)。桥接晶体管tb1耦接于偏压节点q(n)与输出电路213之间。当偏压值低于第一预设电压值时,桥接晶体管tb1将偏压节点q(n)耦接至输出电路213。当偏压值大于或等于第一预设电压值时,桥接晶体管tb1则将偏压节点q(n)与输出电路213进行隔离。在本实施例中,桥接晶体管tb1将偏压节点q(n)与输出电路213进行隔离的实施方式已在图2的实施例中清楚说明,故不在此重述。

72.在本实施例中,补偿电路214反应于偏压值来将补偿时钟信号aclk作为补偿信号

ag(n)。桥接晶体管tb2耦接于偏压节点q(n)与补偿电路214之间。当偏压值低于第二预设电压值时,桥接晶体管tb2将偏压节点q(n)耦接至补偿电路214。当偏压值大于或等于第二预设电压值时,桥接晶体管tb2则将偏压节点q(n)与补偿电路214进行隔离。

73.在本实施例中,桥接晶体管tb2的第一端(如,漏极)耦接于偏压节点q(n)。桥接晶体管tb2的第二端(如,源极)耦接于补偿电路214。桥接晶体管tb2例如是n型晶体管。进一步来说,桥接晶体管tb2例如是nmos晶体管。桥接晶体管tb2的控制端(如,栅极)接收高参考电压vdd。此外,上述的第二预设电压值是高参考电压vdd的电压值与桥接晶体管tb2的临界电压值之间的电压差值。因此,当补偿电路214所接收到的偏压值小于对应于第二预设电压值时,高参考电压vdd的电压值与偏压值之间的电压差值大于桥接晶体管tb2的临界电压值。因此,桥接晶体管tb2的导通电流会大于0而呈现导通状态。

74.在另一方面,当补偿电路214所接收到的偏压值大于或等于第二预设电压值时,高参考电压vdd的电压值与补偿电路214所接收到的偏压值之间的电压差值小于或等于桥接晶体管tb2的临界电压值。因此,桥接晶体管tb2的导通电流会等于0而呈现隔离状态,或称高阻抗状态。当补偿电路214所接收到的偏压值大于或等于第二预设电压值时,桥接晶体管tb2会对偏压节点q(n)与补偿电路214进行隔离。因此,补偿电路214所接收到的偏压值的电荷并不会被分享到其他的电路或是其他的栅极驱动单元。

75.在本实施例中,基于桥接晶体管tb1、tb2的设计,第二预设电压值与第一预设电压值大致相同。在一些实施例中,第二预设电压值不同于第一预设电压值。

76.在本实施例中,预补偿电路215耦接于偏压节点q(n)。预补偿电路215在显示期间利用第(n-a)级复本信号c(n-a)的正脉波来存储电能。预补偿电路215在消隐期间利用所述电能来抬升位于偏压节点q(n)的偏压值。因此,在消隐期间,补偿电路214会反应于高偏压值来将补偿时钟信号aclk作为补偿信号ag(n)。补偿信号ag(n)的正脉波在消隐期间被输出。在本实施例中,补偿信号ag(n)的正脉波能够对在消隐期间对对应于第n级栅极驱动单元210的扫描线进行补偿。

77.在本实施例中,重置电路216耦接于偏压节点q(n)。重置电路216反应于重置信号rst以及第(n b)级复本信号c(n b)的至少其中之一来重置位于偏压节点q(n)的偏压值。b是正整数。抗噪电路217耦接于偏压节点q(n)、复本电路212、输出电路213以及补偿电路214。抗噪电路217反应于位于偏压节点q(n)的低偏压值来下拉第n级复本信号c(n)的电压值以及第n级栅极驱动信号g(n)的电压值以及补偿信号ag(n)的电压值。

78.请参考图4,图4是依据本实用新型一实施例所绘示的栅极驱动单元的电路图。第n级栅极驱动单元310可以实现如图1所示的第n级栅极驱动单元gu(n)。在本实施例中,第n级栅极驱动单元310包括预充电电路311、复本电路312、输出电路313、补偿电路314、预补偿电路315、重置电路316、抗噪电路317以及桥接晶体管tb1、tb2。

79.在本实施例中,预充电电路311包括预充电晶体管tp。预充电晶体管tp的第一端接收高参考电压vdd。预充电晶体管tp的第二端耦接于偏压节点q(n)。预充电晶体管tp的控制端接收第(n-a)级复本信号c(n-a)。预充电电路311反应于第(n-a)级复本信号c(n-a)的正脉波来导通预充电晶体管tp。第(n-a)级复本信号c(n-a)的时序会领先第(n)级复本信号c(n)的时序以及第n级栅极驱动信号g(n)。因此,预充电晶体管tp利用高参考电压vdd来对偏压节点q(n)的偏压值进行预充电。

80.复本电路312包括复本晶体管tc以及复本电容器cc。复本晶体管tc的第一端接收时钟信号clk。复本晶体管tc的第二端用以输出第(n)级复本信号c(n)。复本晶体管tc的控制端耦接于偏压节点q(n)。复本电容器cc耦接于复本晶体管tc的控制端与复本晶体管tc的第二端之间。

81.输出电路313包括输出晶体管tg以及输出电容器cg。输出晶体管tg的第一端接收时钟信号clk。输出晶体管tg的第二端用以输出第n级栅极驱动信号g(n)。输出晶体管tg的控制端耦接于桥接晶体管tb1的第二端。输出电容器cg耦接于输出晶体管tg的控制端与输出晶体管tg的第二端之间。

82.补偿电路314包括补偿晶体管tk以及补偿电容器ck。补偿晶体管tk的第一端接收补偿时钟信号aclk。补偿晶体管tk的第二端用以输出补偿信号ag(n)。补偿晶体管tk的控制端耦接于桥接晶体管tb2的第二端。补偿电容器ck耦接于补偿晶体管tk的控制端与补偿晶体管tk的第二端之间。此外,补偿晶体管tk的控制端还耦接于节点q’。

83.预补偿电路315包括晶体管ta1~ta5以及电容器ca。晶体管ta1的第一端接收第(n-a)级复本信号c(n-a)。晶体管ta1的第二端耦接于晶体管ta2的第一端。晶体管ta1的控制端以及晶体管ta2的控制端共同接收信号rs。晶体管ta2的第二端耦接于节点m。电容器ca耦接于高参考电压vdd与节点m之间。晶体管ta3的第一端耦接于高参考电压vdd。晶体管ta3的第二端耦接于晶体管ta1的第二端。晶体管ta3的控制端耦接于节点m。晶体管ta4的第一端耦接于高参考电压vdd。晶体管ta4的第二端耦接于节点z。晶体管ta4的控制端耦接于节点m。晶体管ta5的第一端耦接于节点z。晶体管ta5的第二端耦接于偏压节点q(n)。晶体管ta5的控制端接收信号bs。

84.重置电路316包括重置晶体管tr1、tr2。重置晶体管tr1的第一端耦接于偏压节点q(n)。重置晶体管tr1的第二端耦接于低参考电压vss。重置晶体管tr1的控制端接收重置信号rst。重置晶体管tr2的第一端耦接于偏压节点q(n)。重置晶体管tr2的第二端耦接于低参考电压vss。重置晶体管tr2的控制端接收第(n b)级复本信号c(n b)。

85.抗噪电路317包括晶体管tn1~tn10。晶体管tn1的第一端以及晶体管tn1的控制端耦接于高参考电压vdd。晶体管tn2的第一端耦接于高参考电压vdd。晶体管tn2的第二端耦接于节点p。晶体管tn2的控制端耦接于晶体管tn1的第二端。晶体管tn3的第一端耦接于偏压节点q(n)。晶体管tn3的第二端耦接于低参考电压vss。晶体管tn3的控制端耦接于节点p。晶体管tn4的第一端耦接于晶体管tn1的第二端。晶体管tn4的第二端耦接于低参考电压vss。晶体管tn4的控制端耦接于偏压节点q(n)。晶体管tn5的第一端耦接于节点p。晶体管tn5的第二端耦接于低参考电压vss。晶体管tn5的控制端接收第(n-a)级复本信号c(n-a)。晶体管tn6的第一端耦接于节点p。晶体管tn6的第二端耦接于低参考电压vss。晶体管tn6的控制端耦接于偏压节点q(n)。晶体管tn7的第一端耦接于节点p。晶体管tn7的第二端耦接于低参考电压vss。晶体管tn7的控制端接收信号bs。晶体管tn8的第一端耦接于复本晶体管tc的第二端。晶体管tn8的第二端耦接于低参考电压vss。晶体管tn8的控制端耦接于节点p。晶体管tn9的第一端耦接于输出晶体管tg的第二端。晶体管tn9的第二端耦接于低参考电压vss。晶体管tn9的控制端耦接于节点p。晶体管tn10的第一端耦接于补偿晶体管tk的第二端。晶体管tn10的第二端耦接于低参考电压vss。晶体管tn10的控制端耦接于节点p。

86.在本实施例中,桥接晶体管tb1、tb2、预充电晶体管tp、复本晶体管tc、输出晶体管

tg、补偿晶体管tk、晶体管ta1~ta5、tn1~tn10以及重置晶体管tr1、tr2分别例如是nmos晶体管。

87.请同时参考图4以及图5,图5是依据图4所绘示的时序图。在显示期间td1中,第(n-a)级复本信号c(n-a)在时间点t0、t1之间具有正脉波。本实施例的a等于1(本实用新型并不以此为限)。因此,充电晶体管tp在时间点t0、t1之间被导通以对偏压节点q(n)以及节点q’进行预充电。信号rs也在时间点t0、t1之间具有正脉波。晶体管ta1、ta2被导通并使节点m存储第(n-a)级复本信号c(n-a)的正脉波的电能。晶体管ta3、ta4基于所述电能被导通。因此,晶体管ta4会利用所述电能对节点z进行充电。晶体管ta5反应于处于低电压电平的信号bs被断开。因此,节点z在时间点t0、t1之间会存储电能(即,正电荷)。在时间点t0,复本晶体管tc、输出晶体管tg以及补偿晶体管tk反应于偏压节点q(n)的偏压值开始被导通。

88.此外,在时间点t0、t1之间,抗噪电路317在反应于偏压节点q(n)的高偏压值来导通晶体管tn4、tn6及/或反应于第(n-a)级复本信号c(n-a)来导通晶体管tn5。位于节点p的电压电平会被下拉至低参考电压vss的电压值。因此,晶体管tn2、tn3、tn8~tn10被断开以使抗噪电路317停止执行抗噪操作。

89.在显示期间td1的时间点t1、t2之间,时钟信号clk具有正脉波。复本晶体管tc会将时钟信号clk作为第(n)级复本信号c(n)。因此,第(n)级复本信号c(n)在时间点t1、t2之间也具有正脉波。此外,复本电容器cc会基于时钟信号clk的正脉波将偏压节点q(n)的高偏压值进一步地耦合到更高的偏压值,从而确保复本晶体管tc的导通。在时间点t1、t2之间,输出晶体管tg会将时钟信号clk作为第n级栅极驱动信号g(n)。因此,第n级栅极驱动信号g(n)在时间点t1、t2之间也具有正脉波。此外,输出电容器cg会基于时钟信号clk的正脉波将输出电路313所接收到的偏压值进一步地耦合到更高的偏压值,从而确保输出晶体管tg的导通。此外,第(n-a)级复本信号c(n-a)在时间点t1、t2之间不具有正脉波。因此,晶体管ta1~ta4被断开以停止对节点z进行充电。

90.应注意的是,在本实施例中,第n级栅极驱动单元310包含了晶体管ta1~ta5、tn1~tn10以及重置晶体管tr1、tr2等晶体管。当输出电路313所接收到的偏压值大于或等于第一预设电压值时,高参考电压vdd的电压值与输出电路313所接收到的偏压值之间的电压差值小于或等于桥接晶体管tb1的临界电压值。桥接晶体管tb1会对偏压节点q(n)与输出电路313进行隔离。位于输出晶体管tg的控制端的电荷并不会被分享到上述多个晶体管的寄生电容。如此一来,位于输出晶体管tg的高偏压值不会被下降。

91.在显示期间td1的时间点t2、t3之间,时钟信号clk不具有正脉波。因此,第(n)级复本信号c(n)以及第n级栅极驱动信号g(n)在时间点t2、t3之间也不具有正脉波。

92.在显示期间td1的时间点t3、t4之间,第(n b)级复本信号c(n b)具有正脉波。本实施例的b等于2(本实用新型并不以此为限)。反应于第(n b)级复本信号c(n b)的正脉波,重置晶体管tr2会被导通以将位于偏压节点q(n)以及节点q’的偏压值下拉至低偏压值。因此,抗噪电路317的晶体管tn4~tn6被断开。晶体管tn2被导通。位于节点p的电压电平会被抬升。因此,tn3、tn8~tn10被导通以使抗噪电路317开始执行抗噪操作。抗噪电路317会将第n级复本信号c(n)的电压值以及第n级栅极驱动信号g(n)的电压值以及补偿信号ag(n)的电压值下拉至低参考电压vss的电压值,并将位于偏压节点q(n)的偏压值维持于低偏压值。

93.在消隐期间td2的时间点t5、t6之间,信号bs具有正脉波。存储于节点z的电能会对

偏压节点q(n)以及节点q’进行充电。位于节点p的电压电平会被下拉至低参考电压vss的电压值。因此,抗噪电路317开始停止执行抗噪操作。此外,复本晶体管tc、输出晶体管tg以及补偿晶体管tk反应于偏压节点q(n)的偏压值被导通。

94.在消隐期间td2的时间点t6、t7之间,补偿时钟信号aclk具有正脉波。因此,补偿信号ag(n)在时间点t6、t7之间也具有正脉波。此外,补偿电容器ck会基于补偿时钟信号aclk的正脉波将节点q’的高偏压值进一步地耦合到更高的偏压值,从而确保补偿晶体管tk的导通。信号bs处于低电压电平。因此,晶体管ta5被断开。

95.应注意的是,当节点q’的偏压值大于或等于第二预设电压值时,高参考电压vdd的电压值与补偿电路314所接收到的偏压值之间的电压差值小于或等于桥接晶体管tb2的临界电压值。桥接晶体管tb1会对偏压节点q(n)与节点q’进行隔离。位于节点q’的电荷并不会被分享到上述多个晶体管的寄生电容。如此一来,位于节点q’的高偏压值不会被下降。

96.在本实施例中,补偿时钟信号aclk的正脉波宽度大于于时钟信号clk的正脉波宽度。补偿时钟信号aclk的正脉波宽度可决定在消隐期间对扫描线进行补偿的电荷量。

97.在消隐期间td2的时间点t7、t8之间,补偿时钟信号aclk不具有正脉波。因此,补偿信号ag(n)在时间点t7、t8之间也不具有正脉波。

98.在消隐期间td2的时间点t8、t9之间,信号rs具有正脉波。第(n-a)级复本信号c(n-a)处于低电压电平。因此,晶体管ta1、ta2被导通以释放节点m的电能。晶体管ta3、ta4被断开。此外,重置信号rst具有正脉波。重置晶体管tr1反应于重置信号rst的正脉波被导通。因此,位于偏压节点q(n)以及节点q’的高偏压值被重置为低偏压值。时间点t8、t9之间可以被视为重置期间。

99.请参考图6,图6是依据本实用新型另一实施例所绘示的栅极驱动电路的示意图。在本实施例中,栅极驱动电路200包括多个栅极驱动单元。所述多个栅极驱动单元彼此串联耦接。为了便于说明,本实施例示出第(n-1)级栅极驱动单元gu(n-1)、第n级栅极驱动单元gu(n)、第(n 1)级栅极驱动单元gu(n 1)以及第(n 2)级栅极驱动单元gu(n 2)来示例,本实用新型并不以此为限。

100.第(n-1)级栅极驱动单元gu(n-1)接收时钟信号clk1、第(n-2)级复本信号c(n-2)、第(n 1)级复本信号c(n 1)、补偿时钟信号aclk、高参考电压vdd、低参考电压vss、信号rs、bs以及重置信号rst,并提供第(n-1)级复本信号c(n-1)、第(n-1)级栅极驱动信号g(n-1)以及补偿信号ag(n-1)。

101.第n级栅极驱动单元gu(n)接收时钟信号clk2、第(n-1)级复本信号c(n-1)、第(n 2)级复本信号c(n 2)、补偿时钟信号aclk、高参考电压vdd、低参考电压vss、信号rs、bs以及重置信号rst,并提供第n级复本信号c(n)、第n级栅极驱动信号g(n)以及补偿信号ag(n)。

102.第(n 1)级栅极驱动单元gu(n 1)接收时钟信号clk3、第n级复本信号cn、第(n 3)级复本信号c(n 3)、补偿时钟信号aclk、高参考电压vdd、低参考电压vss、信号rs、bs以及重置信号rst,并提供第(n 1)级复本信号c(n 1)、第(n 1)级栅极驱动信号g(n 1)以及补偿信号ag(n 1)。

103.第(n 2)级栅极驱动单元gu(n 2)接收时钟信号clk4、第(n 1)级复本信号cn、第(n 4)级复本信号c(n 4)、补偿时钟信号aclk、高参考电压vdd、低参考电压vss、信号rs、bs以及重置信号rst,并提供第(n 2)级复本信号c(n 2)、第(n 2)级栅极驱动信号g(n 2)以及补

偿信号ag(n 2)。

104.综上所述,输出电路反应于偏压值来将时钟信号作为第n级栅极驱动信号。第一桥接晶体管耦接于偏压节点与输出电路之间。当偏压值大于或等于第一预设电压值时,桥接晶体管能够将偏压节点与输出电路进行隔离。如此一来,栅极驱动电路能够降低电荷分享效应,从而使栅极驱动单元能够提供具有正确波型的栅极驱动信号。此外,补偿电路反应于偏压值来将时钟信号作为补偿信号。第二桥接晶体管耦接于偏压节点与补偿电路之间。当偏压值大于或等于第二预设电压值时,第二桥接晶体管能够将偏压节点与补偿电路进行隔离。如此一来,补偿电路能够提供具有正确波型的补偿信号。

105.最后应说明的是:以上各实施例仅用以说明本实用新型的技术方案,而非对其限制;尽管参照前述各实施例对本实用新型进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本实用新型各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。