1.本发明涉及包括电力分配网络(pdn)的电子系统。

背景技术:

2.作为超越摩尔(moore)定律的前进道路,下一代硅技术的2.5d和3d集成已经出现。这样的方案提供了soc/sip级别的持续系统扩展、性能增强、更高频操作、功耗的总体降低、设备小型化以及成本最小化。此外,2.5d/3d技术还加快了从低端便携式电子设备到高端超级计算机等新系统应用的上市时间。因此,2.5d和3d硅管芯堆叠和硅封装集成带动了整个半导体产业的发展。然而,这样的集成正在产生其他问题,例如,在需要时以给定频率向这些硅管芯提供电力的电力管理、热管理等。为了管理系统中的电力需求和分配,使用了电力分配/输送网络(pdn)。pdn的作用是从电源(通常称为稳压器模块(vrm))向系统中的所有部件输送稳定的电力供应。

3.在管芯级别,在cmos电路中,逻辑管芯在其晶体管切换时消耗电流,从而导致pdn中的波纹电压。这种效应被称为同步开关噪声(ssn),并且被认为是数字ic中的主要噪声源。由于在电路层面,高逻辑状态和低逻辑状态是通过感测电压(具有接受裕度)来定义的,因此pdn中的电压纹波超过该裕度可能导致核心处理中的逻辑错误。随着晶体管技术的进步,今天的晶体管可以在更高的频率下切换,从而更频繁地导致出现ssn噪声。

4.为了保持性能提高的过程,微电子器件的传统架构正在向3d集成电路架构(3dic)发展,其中异构管芯彼此堆叠。虽然全3d堆叠解决方案等待整个行业生态系统的发展,但是2.5d已成为设计和工艺成熟度方面的中间步骤,其中硅管芯并排放置或者以所谓的小芯片的形式放置,以集成在例如硅或玻璃的插入器上。具有更高互连密度的插入器允许在其表面上堆叠多个异构管芯,从而增加它们的通信带宽。然而,插入器的添加通过引入新元件(例如tsv、μ-凸块、正面和背面再分配层(rdl)给整体封装结构带来了复杂化,这些新元件在系统的pdn中充当寄生元件。

5.众所周知,对于经典电路,电力管理中的主要问题来自芯片/封装反谐振,当在片上电容c

fe

与封装电感之间形成并联lc谐振器电路时会发生芯片/封装反谐振。这样的问题对于2.5d/3d封装变得更加突出。由堆叠管芯引起的复杂性对pdn的质量产生了多个明显的影响。如果多个逻辑管芯集成在同一平台上,则晶体管在切换期间消耗的电流会增加,从而导致更高的ssn。插入器结构中存在的新元件促进了中频处更高的阻抗峰值。

6.小型化不仅仅发生在管芯或封装级别。例如,终端用户对更薄/紧凑但功能更强大的智能电话的需求不断增加,需要不断减小容纳所有部件的逻辑板的面积。

7.例如,板面积的这种减小将允许实现更大的电池。

8.然而,当数字部件转换逻辑状态时,印刷电路板(pcb)或类衬底pcb(slp)会受到pdn中产生的电力和返回平面反弹的影响。状态变化会在每个边沿时间导致电力轨和返回轨中的显著电流尖峰,并且有时被称为“接地反弹”或“击穿”电位。如果电力引脚和返回引

脚的能量存储不足,则将发生平面反弹。

9.pcb/slp中的电力平面和返回平面都被视为传输线,并且这些平面必须以它们的特征阻抗终止。当部件切换状态时,发生传播波效应,传播到pcb/slp的边缘并反射回来。对于多个开关频率,相位加法/减法将在pdn内的某处发生。如果振铃的相加值超过部件的电力/返回引脚的阈值电平,则可能出现功能问题。导致平面反弹的原因已知有两个:(a)去耦电容器或掩埋电容缺乏能量存储,以及(b)反射波切换与布局中“不能”被电容结构移除的“孔”相互作用。此外,电力/返回平面对的阻抗在整个频谱范围内变化。在例如智能电话/计算机的复杂系统中,总是存在多个部件同时切换逻辑状态。如果平面反弹超过电压裕度水平,则数字部件可能会停止正常工作。

10.在pcb/slp级别,当部件在特定的x/y轴位置与电容器直接连接时,该位置可能会产生低阻抗。当部件由于器件与电容器之间的距离间隔而没有被电容器去耦时,该部件可能会受到大的平面反弹,并且可能会因过孔反焊盘的孔而加重。这种大的平面反弹是由多个传播波的相位相加引起的,这些波从板边缘以及从pcb/slp组件的z轴方向上的通孔过孔中断反射回来。因此,电力分配网络(pdn),即电力和返回平面,必须在边缘转换期间提供足够的能量电荷。在小工具中使用的功能性pcb可能具有数百甚至数千个开关元件,这使得解决这种pdn中的平面反弹问题更加重要。

11.现有技术的逻辑板的整体结构复杂性要求增加对pdn阻抗的控制。为了解决这个问题,电路设计者广泛使用的确保pdn可靠性的方法是定义目标阻抗z

target

。在存在电流瞬变的整个工作频率范围内,电网阻抗响应必须保持在该值以下。z

target

值定义为:

12.z

target

=v

dd

α/(i

max-i

min

)

13.其中,v

dd

表示逻辑核心电压,α是允许的纹波电压比,i

max

是电路中流动的最大电流并且i

min

是空闲状态下的最小电流。电路中的瞬时电流是i

max

与i

min

之差。z

target

预计会随着ic技术的发展而减小,从22nm技术节点的典型值0.5ohm减小到10nm技术节点的0.38ohm,趋势是目标阻抗进一步减小。

14.谨慎的pdn设计和导电材料的选择可以将pdn中的电感减小到由形成互连的材料的固有阻抗定义的某个限制。为了进一步改进pdn功能,使用了电容器。在pdn中,去耦电容器充当向开关晶体管提供电子的本地能量存储装置,这对于降低高瞬时电流噪声和提供低阻抗电力传输路径至关重要。此外,电力供应可能会受到电路回路中互连的寄生阻抗的影响,从而引发反谐振效应。因此,pdn中的这些各种储能电容器的适当分布使得pdn设计者能够减轻反谐振峰值,以便在器件的整个工作频率范围内将pdn阻抗保持在z

target

以下。

15.因此,去耦电容器广泛用于当今的高性能电力分配系统中,为快速开关电路供应峰值电流需求,降低电磁干扰(emi),在电力轨与接地轨之间提供ac路径以用于返回电流,并且降低电力分配网络的总阻抗。然而,去耦性能由电容值及其逻辑所见的访问阻抗驱动,这尤其取决于其在pdn中的位置。

16.由于不同的尺寸、操作带宽、有效功能范围和相关成本,不同的电容器值需要分布在不同的电路布局图中。最常用的去耦电容器以分立部件形式即表面贴装器件(smd)电容器存在,并且由于这些电容器的体积庞大,所以通常放置在pcb上。具有中间尺寸的电容器以例如沟槽硅电容器(tsc)的形式用于插入器平面设计。片上电容器(c

fe

)位于逻辑管芯(前端)的晶体管平面中和/或片上不同互连金属层之间。

17.不同类型的去耦电容器的实现支持不同频率范围的pdn。例如,c

pcb

允许引入大电容值,但是与片上去耦电容器方法相比,它们的高访问阻抗/环路电感(高达数nh)限制了它们对较低频率(~100mhz)的响应。另一方面,c

fe

表现出有限的电容值和非常低的访问阻抗,从而允许对较高频率(》2ghz)进行去耦。然而,由于芯片面积不足,片上nmos去耦电容器的电容有限(≤0.1μf)。

18.将电力从电源带到管芯焊盘的互连网络会产生环路电感。该环路电感可能会导致pdn两端的电压降(δv),管芯焊盘会经历这种情况。这样的电压降(δv)成为突出的问题,其中工作电压已经降低到1.8伏以下并且正在稳步缩小。在这样的工作电压下,由环路电感引起的电压降可能高到足以影响连接至管芯焊盘的电子器件(例如晶体管)的开/关功能。随着时钟频率的增加,环路电感的问题也变得更糟,这会减少器件的开/关状态的持续时间。δv与电感(l)之间的关系由δv=ldi/dt表示,其中电压降(δv)等于电感(l)乘以电流增加或减小速率di/dt。如前所述,时钟频率越高,di/dt越高。另一方面,先进器件的较低工作电压将可接受的δv推得更低。因此,必须将包括任何寄生效应在内的总环路电感降至最低,以使δv在可接受的范围内。

19.然而,通过增加片上电容来解决管芯级别的pdn问题会导致尺寸的过度增加,从而导致逻辑管芯的成本过度增加。这样的方法在us 2017/0069601中公开,其中在管芯中使用片上电容器以提供增强的片上去耦电容以用于存储器管芯的电力管理。该方法还涉及在每个管芯中存在昂贵的硅通孔(tsv),这成本高昂。us 2017/0012029描述了在管芯的背面形成mim电容器结构。然而,这样的方案需要与cmos兼容,并且必须在要组装的每个管芯上完成。

20.迄今为止,已经发现添加封装上去耦电容器对于限制中频处的反谐振相当有效。在us 7518881中解释了在插入器上具有集成的硅基电容器的优点。us 7488624描述了如何在插入器中配置多个硅基集成电容器。us 8618651中公开了集成电容器的又一示例,其中硅电容器形成在盲tsv通孔内。在us 9236442和us 9257383中公开了基于硅沟槽的电容器的另外的示例,其中使用高纵横比的硅沟槽来制造电容器器件。

21.因此,传统的基于硅的嵌入式高纵横比沟槽电容器技术已经成熟,可用于量产,并且可以在当今的智能电话封装中找到。然而,鉴于小型化的趋势,硅基电容器技术的潜力受限于调整每单位面积电容器密度的能力,以及不希望的寄生电阻、加工期间硅衬底中增加的膜应力、升级每个功能的制造复杂性和成本经济性。

22.另一方面,mlcc是世界上使用的最突出的分立电容器部件类型。每年使用数以万亿计的这种分立部件。当今制造这样的分立部件的行业标准mlcc/tsc/licc电容器技术面临着挑战,以适应对低于100μm并且优选地低于20μm的低高度(z高度)的日益增长的需求。这种需求是由于集成在封装soc/sip封装中的ic需要低于50μm的电容器高度以适应soc/sip封装解决方案的事实,因为凸块互连高度和间距/间隔减小。因此,基于这些成熟技术的这些部件的进一步小型化可能不像以前那样具有成本竞争力。满足2d和3d空间中足够小的需求尤其具有挑战性,以便分立电容器部件可以安装在倒装芯片凸块互连之间而不影响成本。

23.因此,尽管集成电容器以及分立电容器的开发方面取得了技术进步,但是目前还没有电容器技术能够满足pdn配置对未来高封装密度和高性能电子设备的全部要求和需

求。

24.因此,期望提供一种改进的电子系统,以提供改进的电力分配。

技术实现要素:

25.鉴于上述情况,本发明的目的是提供一种改进的电子系统,以提供改进的电力分配。

26.根据本发明的第一方面,因此提供一种电子系统,包括:具有衬底导体图案的衬底,衬底具有包括在衬底导体图案中的衬底焊盘;半导体部件,其具有有源电路和耦接至半导体部件的有源电路的部件焊盘,部件焊盘连接至衬底的衬底焊盘;电源接口,其用于从电源接收电力,电源接口连接至衬底导体图案;以及电力分配网络,其用于将电力从电源接口分配到半导体部件的有源电路,电力分配网络包括:第一电容器,其由包括在半导体部件中的导电结构实现,第一电容器耦接至半导体部件的第一部件焊盘和第二部件焊盘;第二电容器,其布置在衬底与半导体部件之间,第二电容器耦接至部件封装的第一部件焊盘和第二部件焊盘;以及衬底导体图案的电网部分。

27.电子系统可以是在电子设备中或者在包括一个或多个电子系统的其他设备或机器中提供功能的任何电子系统。电子系统的示例可以是移动电话、计算机或车辆等中的逻辑板。

28.衬底可以有利地是多层衬底,其中导体图案包括由电介质层分开的多层导电结构。合适的衬底的示例可以包括印刷电路板(pcb)、类衬底pcb(slp)、玻璃、ltcc(低温共烧陶瓷)或硅基衬底。

29.电力接口可以被配置成从各种电源接收电力,各种电源包括例如vrm、电池、低压降线性调节器(ldo)、dc-dc转换器、smps、pmu、pmic、功率ic或其组合、或工业中在pdn的不同阶段使用的任何其他类型的电源。

30.半导体部件可以是所谓的裸管芯半导体部件的形式,或者半导体部件可以包括接合至载体的一个或多个集成电路管芯。这样的集成电路管芯例如可以是独立的ic或一起提供所需的功能的所谓的小芯片的集合。在实施方式中,半导体部件可以包括所谓的插入器。取决于应用,半导体部件可以嵌入或不嵌入电介质封装材料中。当然,电子系统可以有利地包括安装在衬底上并连接至衬底焊盘的多个半导体部件。半导体部件可以布置在衬底的一侧或衬底的两侧。

31.实现第一电容器的导电结构可以是一个或多个半导体集成电路管芯的导电结构,例如金属层。替选地或组合地,实现第一电容器的导电结构可以使用后处理技术形成在一个或多个半导体集成电路管芯的表面上。

32.本发明的当前方面是基于这样的认识:可以通过提供第一电容器和第二电容器作为pdn或电子系统的一部分来实现电子系统中期望的改进的电力分配,第一电容器由包括在半导体部件中的导电结构实现并且耦接至一对部件焊盘,第二电容器布置在衬底与半导体部件之间并且耦接至同一对部件焊盘。

33.特别地,第二电容器的这种布置可以减小第一电容器与第二电容器之间的导电路径的长度,这进而减小了pdn的该部分中的电感。此外,可以提供宝贵的衬底表面空间,从而实现更紧凑的电子系统。

34.有利地,第二电容器可以是分立电容器部件,其具有接合至第一部件焊盘的第一连接结构和接合至第二部件焊盘的第二连接结构。

35.有利地,第二电容器可以是分立的基于纳米结构的电容器,其包括:至少多个第一导电纳米结构;嵌入多个第一导电纳米结构中的每个纳米结构中的电介质材料;导电连接至多个第一纳米结构中的每个纳米结构的第一电极;通过电介质材料与多个第一纳米结构中的每个纳米结构分离的第二电极;导电连接至第一电极的第一连接结构,第一连接结构接合至第一部件焊盘;以及导电连接至第二电极的第二连接结构,第二连接结构接合至第二部件焊盘。

36.可以通过在电力分配网络中包括分立的基于纳米结构的电容器来进一步改进电子系统中的电力分配,从而提供改进的特性,包括每单位面积的更高电容、更低的部件高度、减小的等效串联电感(esl)、当在电容器两端施加dc偏压时不会减小的电容值等中的一个或多个。

37.根据各种实施方式,多个第一导电纳米结构中的导电纳米结构可以是从第一电极层生长的垂直纳米结构。使用生长的纳米结构允许对纳米结构的特性进行广泛的调整。例如,可以选择生长条件以实现使每个纳米结构具有大表面积的形态,这进而可以增加纳米结构能量存储装置的能量存储容量。此外,可以选择生长条件以实现基于纳米结构的电容器部件的期望自谐振频率(srf)。

38.纳米结构可以选自纳米线、纳米角、纳米管、纳米壁、晶体纳米结构或无定形纳米结构中的一种。

39.纳米结构可以有利地是碳纳米结构,例如碳纳米纤维、碳纳米管或碳化物衍生的碳纳米结构。

40.根据实施方式,电介质材料可以有利地被布置为多个第一导电纳米结构中的每个纳米结构上的保形涂层。

41.根据实施方式,第二电极可以覆盖电介质材料。

42.此外,根据各种实施方式,纳米结构能量存储装置还可以包括嵌入电介质材料中的多个第二导电纳米结构。

43.在这样的实施方式中,第二电极可以导电连接至多个第二纳米结构中的每个纳米结构。

44.在一些实施方式中,多个第二导电纳米结构中的每个纳米结构可以有利地从第二电极生长。

45.第二电极或第二电极的一部分可以替代地连接至多个第二纳米结构中的纳米结构的尖端。在这样的实施方式中,纳米结构可以生长,嵌入电介质材料中,并且然后通过去除电介质材料例如通过干法或湿法蚀刻或抛光,暴露纳米结构的尖端。

46.根据另外的实施方式,第一电极或第一电极的一部分也可以连接至多个第一纳米结构中的纳米结构的尖端。在这样的实施方式中,纳米结构可以生长,嵌入电介质材料中,并且然后通过去除电介质材料例如通过干法或湿法蚀刻或抛光,暴露纳米结构的尖端。因此,可以在纳米结构生长之后提供第一电极和第二电极。

47.基于纳米结构的电容器中的电介质材料通过防止从多个第一纳米结构中的导电纳米结构到第二电极的电传导来提供能量存储。因此,可以通过在纳米结构-电介质接口

处的电荷累积来存储能量。电介质可以有利地是所谓的高k电介质。高k电介质材料例如是hfox、tiox、taox、niox、moox、cuox或其他公知的高k电介质。替选地,电介质可以是基于聚合物的,例如聚丙烯、聚苯乙烯、聚(对二甲苯)、聚对二甲苯基等。也可以使用其他公知的电介质材料,例如siox或sinx等。可以通过cvd、热处理、ald或旋涂或喷涂或工业中使用的任何其他合适的方法来沉积电介质材料。

48.在实施方式中,第一电容器可以具有小于100nf的电容;并且第二电容器可以是分立电容器部件,其部件厚度小于100μm并且每部件占用面积的电容大于1000nf/mm2。

49.通过这种特性的组合,可以促进pdn的电气设计/阻抗优化。即使采用用于将半导体部件接合至衬底的现有技术的、低剖面的接合解决方案,极小的部件厚度也使得能够在衬底与半导体部件之间布置第二电容器。此外,出色的电容密度使得能够提供具有高电容值的第二电容器,同时仍然物理地装配在第一部件焊盘与第二部件焊盘之间。

50.根据实施方式,电力分配网络还可以包括接合至衬底导体图案的电网部分的电容器组。

51.接合至衬底导体图案的电网部分的电容器组中的至少一个电容器对于电容器的自谐振频率(srf)与1000倍srf之间的频率范围内的每个频率可以有利地表现出小于100ph的等效串联电感。

52.接合至衬底导体图案的电网部分的电容器组中的每个电容器与其在未偏置状态下的电容相比,在受到dc电压偏置时可以有利地表现出不变的或增加的电容。

53.接合至衬底导体图案的电网部分的电容器组中的每个电容器可以有利地是基于纳米结构的电容器,包括:至少多个第一导电纳米结构;嵌入多个第一导电纳米结构中的每个纳米结构中的电介质材料;导电连接至多个第一纳米结构中的每个纳米结构的第一电极;通过电介质材料与多个第一纳米结构中的每个纳米结构分离的第二电极;导电连接至第一电极的第一连接结构,第一连接结构接合至衬底导体图案的电网部分;以及导电连接至第二电极的第二连接结构,第二连接结构接合至衬底导体图案的电网部分。

54.根据本发明的第二方面,提供了一种电子系统,包括:衬底,其具有衬底导体图案和包括在衬底导体图案中的衬底焊盘;半导体部件,其具有有源电路和耦接至有源电路的部件焊盘,部件焊盘连接至衬底焊盘;电源接口,其用于从电源接收电力,电源接口连接至衬底导体图案;以及电力分配网络,其用于将电力从电源接口分配到半导体部件的有源电路,电力分配网络包括:衬底导体图案的电网部分;第一组电容器,其接合至衬底导体图案的电网部分;以及集成在半导体部件中的第二组电容器,其中,第一组电容器中的每个电容器是分立的基于纳米结构的电容器,包括:至少多个第一导电纳米结构;嵌入多个第一导电纳米结构中的每个纳米结构的电介质材料;导电连接至多个第一纳米结构中的每个纳米结构的第一电极;通过电介质材料与多个第一纳米结构中的每个纳米结构分离的第二电极;导电连接至第一电极的第一连接结构,第一连接结构接合至衬底导体图案的电网部分;以及导电连接至第二电极的第二连接结构,第二连接结构接合至衬底导体图案的电网部分。

55.接合至衬底导体图案的电网部分的第一组电容器可以包括至少一个分立电容器部件。应当理解,“分立”部件是可以附接至载体并导电连接至载体上的导体图案的独立部件,而不是在载体上以逐步工艺形成。

56.集成在半导体部件中的第二组电容器可以是使用一个或多个半导体集成电路管

芯的导电结构(例如金属层)形成的一个或更多个电容器。替选地或组合地,第二组电容器中的一个或更多个电容器可以使用后处理技术形成在一个或多个半导体集成电路管芯的表面上,并且/或者第二组电容器中的一个或更多个电容器可以是接合至半导体部件的导体图案的一个或多个分立电容器。

57.关于基于纳米结构的电容器的配置,应当理解,第一电极可以导电连接至纳米结构,使得电流可以从第一电极流动到纳米结构。

58.本发明的当前方面基于这样的认识:可以通过在电力分配网络中包括分立电容器来实现电子系统中的期望的改进的电力分配,从而提供改进的特性,包括每单位面积的更高电容、更低的部件高度、减小的等效串联电感(esl)、当在电容器两端施加dc偏压时不会减小的电容值等中的一个或多个;以及可以通过基于纳米结构的分立电容器来实现这样的特性。

59.第一组电容器中的至少一个电容器可以有利地在电容器的自谐振频率(srf)与1000倍srf之间的范围内表现出小于100ph的等效串联电感(esl)。

60.为了在该频率范围内实现如此低的esl,发明人已经发现,使用本身已知的技术将分立的基于纳米结构的电容器中的纳米结构定制为具有特定尺寸以及将分立的基于纳米结构的电容器配置为具有特定纵横比可能是有益的。

61.根据一个有利的实施方式,分立的基于纳米结构的电容器中的纳米结构的平均长度可以是0.1μm至100μm,分立的基于纳米结构的电容器中的纳米结构的平均直径可以是1nm至150nm,并且平均长度与平均直径之间的比率可以是至少2:1,即,平均长度可以是平均直径的至少两倍。

62.根据另一有利的实施方式,分立的基于纳米结构的电容器中的纳米结构的平均长度可以是0.1μm至100μm,分立的基于纳米结构的电容器中的纳米结构的平均直径可以是1nm至75nm,并且平均长度与平均直径之间的比率可以是至少10:1,即,平均长度可以是平均直径的至少十倍。

63.此外,每个分立纳米结构电容器可以有利地具有矩形占用空间,该矩形占用空间具有第一长边和第二长边以及第一短边和第二短边,其中,可以沿着第一长边提供第一连接结构,并且可以沿着第二长边提供第二连接结构。

64.每个分立纳米结构电容器的长边的长度可以是分立纳米结构电容器的短边的至少两倍。

65.此外,第一连接结构可以沿着第一长边的长度的至少一半延伸,并且第二连接结构可以沿着第二长边的长度的至少一半延伸。

66.有利地,对于甚至更低的esl,特别是对于更高的频率,第一连接结构可以沿着第一长边的长度的至少80%延伸,并且第二连接结构可以沿着第二长边的长度的至少80%延伸。

67.有利地,对于甚至更低的esl,特别是对于更高的频率,第一连接结构和第二连接结构都可以在部件的外围具有多个替选端子或接触点。它可以是多端部件设备。

68.第一组电容器中的每个电容器与其在未偏置状态下的电容相比,在受到dc电压偏置时可以有利地表现出不变的或增加的电容。

69.为此,本发明人已经发现,将多个第一纳米结构中的每个纳米结构与第二电极分

离的电介质材料可以有利地是非铁电介质。

70.通过本发明的各方面能够实现的进一步改进的电力分配网络(pdn),可以提供更紧凑和/或更高性能(更高开关频率)的电子系统。

71.根据各种实施方式,多个第一导电纳米结构中的导电纳米结构可以是从第一电极层生长的垂直纳米结构。使用生长的纳米结构允许对纳米结构的特性进行广泛的调整。例如,可以选择生长条件以实现使每个纳米结构具有大表面积的形态,这进而可以增加纳米结构能量存储装置的能量存储容量。

72.纳米结构可以选自纳米线、纳米角、纳米管、纳米壁、晶体纳米结构或无定形纳米结构中的一种。

73.纳米结构可以有利地是碳纳米结构,例如碳纳米纤维、碳纳米管或碳化物衍生的碳纳米结构。

74.根据实施方式,电介质材料可以有利地被布置为多个第一导电纳米结构中的每个纳米结构上的保形涂层。

75.根据实施方式,第二电极可以覆盖电介质材料。

76.此外,根据各种实施方式,纳米结构能量存储装置还可以包括嵌入电介质材料中的多个第二导电纳米结构。

77.在这样的实施方式中,第二电极可以导电连接至多个第二纳米结构中的每个纳米结构。

78.在一些实施方式中,多个第二导电纳米结构中的每个纳米结构可以有利地从第二电极生长。

79.第二电极或第二电极的一部分可以替代地连接至多个第二纳米结构中的纳米结构的尖端。在这样的实施方式中,纳米结构可以生长,嵌入电介质材料中,并且然后通过去除电介质材料例如通过干法或湿法蚀刻或抛光,暴露纳米结构的尖端。

80.根据另外的实施方式,第一电极或第一电极的一部分也可以连接至多个第一纳米结构中的纳米结构的尖端。在这样的实施方式中,纳米结构可以生长,嵌入电介质材料中,并且然后通过去除电介质材料例如通过干法或湿法蚀刻或抛光,暴露纳米结构的尖端。因此,可以在纳米结构生长之后提供第一电极和第二电极。

81.基于纳米结构的电容器中的电介质材料通过防止从多个第一纳米结构中的导电纳米结构到第二电极的电传导来提供能量存储。因此,可以通过在纳米结构-电介质接口处的电荷累积来存储能量。电介质可以有利地是所谓的高k电介质。高k电介质材料例如是hfox、hfalox、tiox、taox、niox、moox、cuox、pzt、batiox或其他公知的高k电介质。替选地,电介质可以是基于聚合物的,例如聚丙烯、聚苯乙烯、聚(对二甲苯)、聚对二甲苯基、pbo等。也可以使用其他公知的电介质材料,例如siox或sinx等。可以通过cvd、热处理、ald或旋涂或喷涂或工业中使用的任何其他合适的方法来沉积电介质材料。

82.根据实施方式,第一组电容器的子组中的每个电容器可以布置在衬底与半导体部件之间。第一组电容器中的一个或多个电容器的这种布置可以减小半导体部件的有源电路与电容器之间的导电路径的长度,这进而减小了pdn的该部分中的电感。此外,可以提供宝贵的衬底表面空间,从而实现更紧凑的电子系统。

83.根据本发明的第三方面,提供了一种电子系统,包括:衬底,其具有衬底导体图案

和包括在衬底导体图案中的衬底焊盘;半导体部件,其具有有源电路和耦接至有源电路的部件焊盘,部件焊盘连接至衬底焊盘;电源接口,其用于从电源接收电力,电源接口连接至衬底导体图案;以及电力分配网络,其用于将电力从电源接口分配到半导体部件的有源电路,电力分配网络包括:衬底导体图案的电网部分;接合至衬底导体图案的电网部分的第一组电容器;以及集成在半导体部件中的第二组电容器,其中,第一组电容器中的每个电容器是分立电容器部件,该分立电容器部件对于电容器部件的自谐振频率(srf)与1000倍srf之间的频率范围内的每个频率表现出小于100ph的等效串联电感。

84.本发明的当前方面是基于这样的认识:可以通过在电力分配网络中包括分立电容器来实现电子系统中的期望的改进的电力分配,从而提供改进的特性,包括每表面积的更高电容、更低的部件高度、减小的等效串联电感(esl)、当在电容器两端施加dc偏压时不会减小的电容值等中的一个或多个。

85.第一组电容器中的每个电容器的极低的esl为pdn的电气设计/阻抗优化提供了便利。

86.根据另一方面,第一组电容器中的每个电容器可以是分立电容器部件,该分立电容器部件与其在未偏置状态下的电容相比,在受到dc电压偏置时表现出不变的或增加的电容。

87.此外,有利地,第一组电容器中的每个电容器可以是分立电容器部件,其每部件占用面积的电容大于5000nf/mm2。

88.根据实施方式,第一组电容器中的每个电容器可以是分立的基于纳米结构的电容器,包括:至少多个第一导电纳米结构;嵌入多个第一导电纳米结构中的每个纳米结构的电介质材料;导电连接至多个第一纳米结构中的每个纳米结构的第一电极;通过电介质材料与多个第一纳米结构中的每个纳米结构分离的第二电极;导电连接至第一电极的第一连接结构,第一连接结构接合至衬底导体图案的电网部分;以及导电连接至第二电极的第二连接结构,第二连接结构接合至衬底导体图案的电网部分。

89.可以通过在电力分配网络中包括分立的基于纳米结构的电容器来进一步改进电子系统中的电力分配,从而提供改进的特性,包括每表面积的更高电容、更低的部件高度、减小的等效串联电感(esl)、当在电容器两端施加dc偏压时不会减小的电容值等中的一个或多个。

90.根据各种实施方式,多个第一导电纳米结构中的导电纳米结构可以是从第一电极层生长的垂直纳米结构。使用生长的纳米结构允许对纳米结构的特性进行广泛的调整。例如,可以选择生长条件以实现使每个纳米结构具有大表面积的形态,这进而可以增加纳米结构能量存储装置的能量存储容量。

91.纳米结构可以选自纳米线、纳米角、纳米管、纳米壁、晶体纳米结构或无定形纳米结构中的一种。

92.纳米结构可以有利地是碳纳米结构,例如碳纳米纤维、碳纳米管或碳化物衍生的碳纳米结构。

93.根据实施方式,电介质材料可以有利地被布置为多个第一导电纳米结构中的每个纳米结构上的保形涂层。

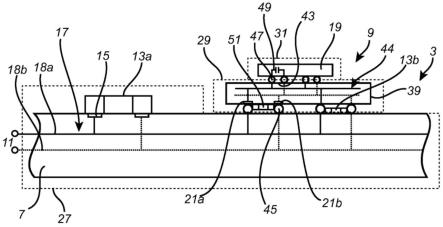

94.根据实施方式,第二电极可以覆盖电介质材料。

95.此外,根据各种实施方式,纳米结构能量存储装置还可以包括嵌入电介质材料中的多个第二导电纳米结构。

96.在这样的实施方式中,第二电极可以导电连接至多个第二纳米结构中的每个纳米结构。

97.在一些实施方式中,多个第二导电纳米结构中的每个纳米结构可以有利地从第二电极生长。

98.第二电极或第二电极的一部分可以替代地连接至多个第二纳米结构中的纳米结构的尖端。在这样的实施方式中,纳米结构可以生长,嵌入电介质材料中,并且然后通过去除电介质材料例如通过干法或湿法蚀刻或抛光,暴露纳米结构的尖端。

99.根据另外的实施方式,第一电极或第一电极的一部分也可以连接至多个第一纳米结构中的纳米结构的尖端。在这样的实施方式中,纳米结构可以生长,嵌入电介质材料中,并且然后通过去除电介质材料例如通过干法或湿法蚀刻或抛光,暴露纳米结构的尖端。因此,可以在纳米结构生长之后提供第一电极和第二电极。

100.基于纳米结构的电容器中的电介质材料通过防止从多个第一纳米结构中的导电纳米结构到第二电极的电传导来提供能量存储。因此,可以通过在纳米结构-电介质接口处的电荷累积来存储能量。电介质可以有利地是所谓的高k电介质。高k电介质材料例如是hfox、tiox、taox、niox、moox、cuox或其他公知的高k电介质。替选地,电介质可以是基于聚合物的,例如聚丙烯、聚苯乙烯、聚(对二甲苯)、聚对二甲苯基等。也可以使用其他公知的电介质材料,例如siox或sinx等。可以通过cvd、热处理、ald或旋涂或喷涂或工业中使用的任何其他合适的方法来沉积电介质材料。

101.根据实施方式,电力分配网络还可以包括接合至部件载体导体图案的第三组电容器。

102.第三组电容器中的至少一个电容器可以是分立电容器部件,该分立电容器部件的部件厚度小于100μm并且每部件占用面积的电容大于1000nf/mm2。

103.通过这种特性的组合,可以促进pdn的电气设计/阻抗优化。即使采用用于将半导体部件接合至衬底的现有技术的、低剖面的接合解决方案,极小的部件厚度也使得能够在衬底与半导体部件之间布置第三组电容器中的一个或更多个电容器。

附图说明

104.现在将参照示出本发明的示例实施方式的附图更详细地描述本发明的这些和其他方面,在附图中:

105.图1示意性地示出了包括根据本发明的实施方式的电子系统的、此处是移动电话的形式的示例电子设备;

106.图2是图1中的电子系统的一部分的放大视图;

107.图3是根据本发明的示例实施方式的电子系统的简化图示;

108.图4是图3中的电子系统的pdn的等效电路图示;

109.图5是示出与pdn的设计方面有关的频率特性的阻抗图;

110.图6是根据本发明的示例实施方式的电子系统的简化示意性截面图;

111.图7是包括在根据本发明的其他示例实施方式的电子系统中的半导体部件的简化

截面视图;

112.图8是包括在根据本发明的示例实施方式的电子系统的pdn中的示例性电容器部件的示意图示;

113.图9是图8中的电容器部件的内部构造的图示;以及

114.图10是包括在根据本发明的示例实施方式的电子系统的pdn中的另一示例性电容器部件的示意图示。

具体实施方式

115.图1示意性地示出了根据本发明的实施方式的电子设备,此处是移动电话1的形式。在图1的简化和示意性的图示中,示出了移动电话,像大多数电子设备一样,包括控制电子设备1的操作的电子系统3以及用于向电子系统3和电子设备1的其他部分供应电力的电源,此处是电池5的形式。

116.尽管此处已经通过移动电话1来例示包括根据本发明的实施方式的电子系统的电子设备,但是应当理解,根据本发明的各种实施方式的电子系统可以同样包括在其他类型的电子设备中,并且对于其他类型的电子设备同样有用,其他类型的电子设备例如:ar、vr、mr;娱乐单元;导航设备;通信设备;固定位置数据单元;移动位置数据单元;全球定位系统(gps)设备;智能手表;可穿戴计算设备;平板电脑;服务器;计算机;便携式计算机;移动计算设备;电池充电器;usb设备;台式计算机;个人数字助理(pda);监视器;计算机监视器;电视机;调谐器;无线电;卫星无线电;音乐播放器;数字音乐播放器;便携式音乐播放器;数字视频播放器;汽车;电动车辆;车辆部件;航空电子系统;无人机以及多旋翼飞行器。

117.在现代电子设备中,电子系统3(在一些应用中也称为逻辑板)需要能够处理非常繁重的计算任务,例如可能包括高级图像处理等。电子系统3可能还需要间歇性地同时处理各种不同的任务。这样的任务可能涉及由不同半导体部件执行的处理,这些半导体部件可能至少部分地专用于执行它们各自的任务。

118.图2是图1中的电子系统3的放大视图,并且示意性地示出了电子系统3包括衬底7、多个半导体部件9(为了避免使附图混乱,图2中仅一个半导体部件用附图标记指示)和用于从电源5接收电力的电源接口11。为了有效且可靠地将电力从电源接口11分配到半导体部件9,电子系统3还包括电力分配网络(pdn)。如上文进一步讨论和解释的,对pdn可能有严格的要求。pdn应当能够在很宽的频率范围内以明确定义的电压电平向电子系统3的所有半导体部件9供应足够的电力。例如,不同的半导体部件9可能表现出所需电力的突然变化。pdn应当能够适应这种情况,而不会过度改变供应电压,也不会干扰对其他半导体部件的电力供应。因此,设计和确定pdn的尺寸是开发电子系统3的团队面临的一项具有挑战性的任务。成功的pdn可能需要仔细设计衬底7、半导体部件9以及有目的地选择和布置大量电容器部件13(再次,在图2中,pdn中包括的电容器中的仅一个电容器由附图标记指示)。

119.本发明的实施方式使得能够设计电子系统中的pdn,其中电容器占据的衬底空间较少。这进而提供了更紧凑的电子系统,这可以允许具有更小尺寸和/或改进的性能的电子设备。例如,对于电子设备(例如移动电话1)的给定整体尺寸,可以容纳更大的电池。电子系统的较小的物理尺寸本身可以有助于促进电子系统的pdn的设计和配置,因为导体长度较短而减小了电感。

120.此外,所公开的主题为电路设计者提供了新颖的手段来满足由终端用户(例如给定设备(例如,移动电话、计算机等)的制造商)设定的电力完整性准则。

121.在各种示例实施方式中,根据本发明,提供了一种电力分配/输送网络(pdn),其包括在电源与接地轨之间以及在电源与(半导体部件中的)有源电路之间的体积显著减小的分立电容器部件,在系统中紧贴实际需求。因此,可以实现最小的环路电感,并且可以使对应的电压降最小化。

122.本发明的实施方式可以满足以下要求:(a)非常高的每单位面积/体积的静电或电化学电容值,(b)在2d和z方向上的低剖面,(c)表面贴装兼容并且适用于2d、2.5d和3d封装/组装/嵌入技术,(d)易于设计外形因子,(e)对温度和施加电压的稳定和鲁棒性能,(f)低等效串联电感(esl),(g)在没有电容退化的情况下更长的寿命或增强的寿命周期,(h)低环路电感,以及(i)成本效益。

123.现在将首先参照图3更详细地描述本发明的各个方面和实施方式,该图是根据本发明的示例实施方式的电子系统的简化图示。

124.如图3中示意性地示出的,电子系统3包括衬底7、半导体部件9、电源接口11和第一组电容器13a-c。衬底7具有带有衬底焊盘15(在图3中仅一个衬底焊盘用附图标记表示)的衬底导体图案。衬底导体图案包括电网部分17,其是导体图案的一部分,用于将电力从电源接口11分配到电子系统3中包括的半导体部件9。如图3中示意性所示,电网部分17至少包括地线18a和电力线18b。应当注意,诸如图2中的电子系统3所需的更复杂的pdn的电网部分17通常将包括可以布置在衬底的不同层中的多个接地线和多个电力线。半导体部件9具有连接至对应的衬底焊盘15的有源电路19和部件焊盘21。在图3中,有源电路被示意性地示出为包括在封装内的半导体管芯19中。然而,应当注意,半导体部件9不一定是封装的半导体部件,而是可以由裸露的半导体管芯或由配备有再分配层(rdl)的半导体管芯等构成。

125.图3中的电子系统3包括用于将电力从电源接口11分配到半导体部件9的有源电路的pdn。在图3的示例配置中,pdn包括衬底导体图案的电网部分17、接合至衬底导体图案的电网部分17的第一组电容器13a-c、集成在半导体部件9中的第二组电容器(图3中未示出/可见)、以及衬底导体图案的电网部分17与半导体管芯19之间的电力分配接口。在图3的示例配置中,该电力分配接口可以包括接合至衬底导体图案的电网部分17的连接结构(例如凸块或柱等)以及将这些连接结构与半导体管芯19电连接的任何结构。

126.关于电容器到衬底导体图案或在本说明书中提及的任何其他导体图案的接合,应当理解,接合是电气和机械连接,其可以通过例如金属到金属接合、压缩接合、焊接接合、具有或不具有底部填充fc接合、acf膜接合、超声波接合或其组合、或工业使用的任何其他接合来实现。

127.此外,第一组电容器可以包括单个电容器,或者可以包括彼此并联或串联电耦接的两个或更多个电容器。根据本发明的各种实施方式,电容器可以被定制为适当的特性,例如能量存储水平、分立部件的外形因子(在x、y和z中)、有效等效电阻和有效等效电感,以符合抑制噪声信号进入半导体部件9的有源电路的电路需要。尽管在附图中没有明确示出,但是实施方式可以包含其他噪声过滤元件,例如铁氧体磁珠。

128.通过能够在需要的附近提供电容器部件,可以创建更可靠、更短的电流回路,这进而降低了进入半导体部件9的有源电路中的瞬时噪声。

129.电子系统3的pdn可以适当地由图4中的简化pdn rlc电等效模型23表示,该模型将电力从电源接口11分配到半导体部件9的有源电路25。如等效模型23下的线示意性所示,简化的pdn表示包括在电气上表示衬底导体图案的电网部分17和第一组电容器13a-c的第一部分27、在电气上表示衬底导体图案的电网部分17与半导体管芯19之间的电力分配接口的第二部分29、以及作为半导体管芯19的电力分配结构的简化电气表示的第三部分31。

130.如图4中示意性所示,pdn电等效模型23的第一部分27包括具有电容cs、等效串联电感esls和等效串联电阻esrs的并联支路,以及具有电感ls和电阻rs的串联支路。pdn电等效模型23的第二部分29包括具有电容c

p

、等效串联电感esl

p

和等效串联电阻esr

p

的并联支路,以及具有电感l

p

和电阻r

p

的串联支路。pdn电等效模型23的第三部分31包括具有电容cd、等效串联电感esld和等效串联电阻esrd的并联支路。基于pdn电等效模型23中的等效电路元件的特性,有源电路25和电源接口11将经历总频率相关阻抗z(f)。

131.当设计电子系统3的pdn时,通常会定义目标阻抗z

target

,这将几乎肯定地确保供应电力在给定的瞬时电流下不会超过指定的电压裕度。然后pdn的设计者旨在将pdn的阻抗z(f)保持在目标阻抗z

target

以下以用于高达电子系统3的最高开关频率的频率。

132.图5的图中示出了作为频率f的函数的pdn阻抗z(f)的示意性图示。在该图中,存在低频阻抗峰值33、中频阻抗峰值35和高频阻抗峰值37。pdn的设计者可用于努力将pdn阻抗z(f)从低频率到足够高的频率保持在目标阻抗z

target

以下的主要工具对于不同的频率范围是不同的。为了减小低频阻抗峰值33,衬底7的配置以及第一组电容器中的电容器13a-c的特性和布置可以有效地优化pdn电等效模型23的第一部分27中的上述等效电特性值。为了减小中频阻抗峰值35,衬底导体图案的电网部分17与半导体管芯19之间的连接结构的配置可以有效地优化pdn电等效模型23的第二部分29中的上述等效电特性值。为了减小高频阻抗峰值37,如果需要,可以在受常规半导体管芯19的严格物理空间约束的电路设计中限制选项。

133.在下文中,将解释本发明的各个方面和实施方式如何为pdn设计者提供新的工具来实现具有改进的特性的pdn,这也可以允许包括这样的pdn的更紧凑和更有成本效益的电子系统。

134.为了说明的目的,在图6中提供了根据本发明的实施方式的电子系统3的简化示意性截面图。

135.在该示例配置中,接合至衬底导体图案的电网部分17的第一组电容器包括:相对靠近电源接口11布置的第一电容器13a,以及布置在衬底7与半导体部件9之间的第二电容器13b。

136.此外,半导体部件9包括部件载体39,该部件载体39具有部件焊盘21、管芯接合焊盘43以及连接部件焊盘21和管芯接合焊盘43的部件载体导体图案。部件载体导体图案包括电网部分44。如图6中示意性示出的,使用第一连接结构45将部件焊盘21连接至衬底焊盘,并且使用第二连接结构47将管芯接合焊盘43连接至半导体管芯19的管芯焊盘。图6中还示意性地示出了:由包括在半导体部件中(此处在半导体管芯19中)的导电结构实现的第一电容器49,以及布置在衬底7与半导体部件9之间的第二电容器51。在图6的示例配置中,上述第一电容器49耦接至半导体部件9的第一部件焊盘21a和第二部件焊盘21b,并且第二电容器51耦接至第一部件焊盘21a和第二部件焊盘21b。在图6中,部件载体39示意性地示出为插

入器。然而,部件载体39不限于是插入器,而是可以是任何其他合适的部件载体,例如引线框。

137.在图6中,示意性地示出了与图4中的pdn电等效模型23的第一部分27、第二部分29和第三部分31相对应的电子系统3的部分。pdn的低频第一部分27包括衬底导体图案的电网部分17和第一组电容器中的上述第一电容器13a。此处,pdn的中频第二部分29包括第一组电容器中的上述第二电容器13b、部件载体导体图案的上述电网部分44、上述第二电容器51、以及上述第一连接结构45和第二连接结构47。此处,pdn的高频第三部分31包括半导体管芯19的前端线(feol)结构和后端线(beol)结构,包括上述第一电容器49。如下面将进一步解释的,取决于第二电容器51和连接结构的配置和特性,至少上述第二电容器51以及连接第一电容器49和第二电容器51的结构可以被认为包括在pdn的高频第三部分31中。

138.图7是包括在根据本发明的其他示例实施方式的电子系统3中的半导体部件的简化截面图。图7中的电子系统3与图6中的电子系统的主要区别在于:半导体部件9不包括部件载体,使得半导体管芯19直接耦接至衬底17的衬底导体图案。

139.在图7中,与图6中一样,示意性地示出了与图4中的pdn电等效模型23的第一部分27、第二部分29和第三部分31相对应的电子系统3的部分。在图7的示例实施方式中,pdn的低频第一部分27包括衬底导体图案的电网部分17和第一组电容器中的第一电容器13a。此处,pdn的中频第二部分29包括:第一组电容器中的第二电容器13b(也对应于上述第二电容器51)以及衬底7与半导体部件9之间的连接结构45。此处,pdn的高频第三部分31包括半导体管芯19的前端线(feol)结构和后端线(beol)结构,包括上述第一电容器49。如下面将进一步解释的,取决于第二电容器51和连接结构的配置和特性,至少上述第二电容器51以及连接第一电容器49和第二电容器51的结构可以被认为包括在pdn的高频第三部分31中。

140.在实施方式中,电子系统3可以被配置为图6中的配置和图7中的配置的混合。因此,可以存在连接在图6中的一对第二连接结构47之间的附加电容器部件,该对第二连接结构47也连接至第一电容器49。

141.可以说,本发明的各个方面和实施方式具有不同的出发点,以用于提供电子系统3的pdn的改进。

142.根据一个方面,取决于第一电容器49与第二电容器51之间的导体的尺寸以及第二电容器51的电特性,提供布置在衬底7与半导体部件9之间并且耦接至半导体部件9的第一部件焊盘21a和第二部件焊盘21b的上述第二电容器51可以明显地减小pdn的中频第二部分29中的等效串联电感esl

p

,并且还可以减小pdn的高频第三部分31中的等效串联电感esld。这对于减小图5中的图中的第二峰值35和第三峰值37可能特别有用,而无需利用半导体部件9之间的任何衬底面积。

143.为了在电子系统3中方便地实现,第二电容器51可以有利地是分立电容器,如在附图中示意性示出的。此外,为了能够以图6和图7中的简化图示所示的方式在衬底7与半导体部件9之间布置第二电容器51,分立电容器部件51的厚度可以有利地小于100μm。此外,分立电容器部件51的每部件占用面积的电容可以有利地大于1000nf/mm2。根据本发明的实施方式,表现出这样的有益特性的分立电容器部件51可以是基于纳米结构的电容器部件。下面将进一步详细描述这种基于纳米结构的电容器部件的示例配置。

144.根据另一方面,通过将第一组电容器中的每个电容器13a提供为分立电容器部件,

可以潜在地使用第一组电容器中的数目减少的电容器13a来改进pdn的低频第一部分27的特性,分立电容器部件在从电容器的自谐振频率到1000倍自谐振频率的频率范围内表现出小于100ph的等效串联电感。由此,可以减小pdn的低频第一部分27中的等效串联电感esls。这对于减小图5中的图中的第一峰值33可能特别有用,同时在半导体部件9之间使用更少的衬底面积。当第一组电容器中的每个电容器部件13a还表现出大于5000nf/mm2的每部件占用面积的电容时,情况尤其如此。根据本发明的实施方式,表现出这样的有益特性的分立电容器部件13a可以是基于纳米结构的电容器部件。下面将进一步详细描述这种基于纳米结构的电容器部件的示例配置。应当注意,根据本发明实施方式的电子系统3中包括的任何基于纳米结构的电容器部件中的纳米结构可以选自纳米线、纳米角、纳米管、纳米壁、晶体纳米结构、无定形纳米结构、si纳米线、金属纳米线或任何其他合适的细长的功能化或非功能化纳米结构中的一种。此外,当在本技术中提及“导电的”或“传导的”纳米结构时,应当理解,该词包括固有导电的纳米结构以及通过诸如金属材料的导电材料的薄层保形涂覆的电绝缘纳米结构。

145.在本发明的实施方式的各种示例中,所使用的分立电容器可以具有范围在40nf到1000nf之间的电容以及低于150mohms的等效串联电阻。这些电容器可以具有范围在50mhz到400mhz之间的自谐振频率。

146.在本发明的实施方式的各种示例中,所使用的分立电容器可以具有范围在1nf到10nf之间的电容以及低于50mohms的等效串联电阻。这些电容器可以具有范围在100mhz到2000mhz之间的自谐振频率。

147.在不同的示例实施方式中,对于在电容器的自谐振频率(srf)与1000倍srf之间的频率范围内的每个频率,一个或更多个电容器的等效串联电感(esl)可以有利地小于25ph,并且甚至更有利地小于10ph。

148.图8是示例性的基于纳米结构的电容器部件53的示意图示,该电容器部件53可以包括在根据本发明的示例实施方式的电子系统3的pdn中。该电容器部件53是分立电容器部件,包括mim布置55、第一连接结构(此处为第一端连接器57的形式)、第二连接结构(此处为第二端连接器59的形式)以及至少部分地嵌入mim布置55的电绝缘封装材料61。如图8所示,电绝缘封装材料61至少部分地形成能量存储部件的外边界表面。第一连接结构57和第二连接结构59也至少部分地形成能量存储部件的外边界表面。在图8中,第一连接结构57和第二连接结构59被示出为布置在矩形部件53的短边上。在实施方式中,第一连接结构57和第二连接结构59可以替代地布置在部件的长边上。这样的配置可以提供部件的减小的串联电感。

149.现在将参照图9描述mim布置55的示例配置。如图9中示意性示出的,mim布置55包括mim布置衬底81上的第一电极层63、从第一电极层63垂直生长的多个导电纳米结构65、保形地涂覆多个导电纳米结构中的每个纳米结构65和未被导电纳米结构65覆盖的第一电极层63的固体电介质材料层67、以及覆盖固体电介质材料层67的第二电极层69。如图9所示,第二电极层69完全填充相邻纳米结构之间的超过纳米结构65的底部71与顶部73之间的一半的空间。在图9的示例性mim布置55中,第二电极层69完全填充相邻纳米结构65之间的从底部71一直到顶部73并且超过顶部73的空间。

150.如图9中纳米结构65与第二电极层69之间的边界的放大视图所示,第二电极层69

包括保形地涂覆固体电介质材料层67的第一子层75、第二子层77、以及第一子层75与第二子层77之间的第三子层79。

151.此外,根据本发明公开内容,可以方便地存在图中未示出的例如作为金属扩散阻挡层的附加子层。

152.电介质材料层67可以是多层结构,其可以包括不同材料成分的子层。

153.根据本发明的实施方式,mim布置55可以包括分层配置的固体电介质和电解质。在这样的实施方式中,部件53可以被视为电容器型(静电)与电池型(电化学)能量存储装置之间的混合体。这种配置可以提供比纯电容器部件更高的能量密度和电力密度以及比纯电池部件更快的充电。

154.现在将描述制造包括图9中的示例性mim布置55的分立的基于纳米结构的电容器部件53的示例方法。

155.在第一步骤中,提供mim布置衬底81。可以使用各种衬底,例如,硅、玻璃、不锈钢、陶瓷、sic或工业中发现的任何其他合适的衬底材料。然而,衬底可以是高温聚合物,例如聚酰亚胺。有利地,mim布置衬底81可以是电绝缘衬底。

156.在随后的步骤中,在衬底81上形成第一电极层63。第一电极层63可以通过物理气相沉积(pvd)、化学气相沉积(cvd)、原子层沉积(ald)或工业中使用的任何其他方法形成。在一些实现方式中,第一电极层63可以包括选自以下的一种或更多种金属:cu、ti、w、mo、co、pt、ai、au、pd、ni、fe和硅化物。在一些实现方式中,第一电极层63可以包括选自以下的一种或更多种导电合金:tic、tin、wn和ain。在一些实现方式中,第一金属层63可以包括一种或更多种导电聚合物。在一些实现方式中,第一电极层63可以是金属氧化物,例如licoo2、掺杂硅。在一些实现方式中,第一金属层63可以是衬底本身,例如al/cu/ag箔等。

157.在下一步骤中,可以在第一电极层63上设置催化剂层。催化剂可以是例如镍、铁、铂、钯、硅化镍、钴、钼、au或其合金,或者可以与其他材料(例如硅)组合。催化剂可以是可选的,因为本文描述的技术也可以应用于纳米结构的无催化剂生长过程。还可以通过旋涂催化剂颗粒来沉积催化剂。

158.在一些实现方式中,催化剂层用于生长纳米结构以及用作连接电极。在这样的实现方式中,催化剂可以是镍、铁、铂、钯、硅化镍、钴、钼、au或其合金的厚层,或者可以与来自元素周期表的其他材料组合。催化剂层(图9中未示出)可以作为均匀层或作为图案化层提供。图案化层的形成当然需要比未图案化层更多的处理,但是可以提供更高或更低且密度更规则的纳米结构65,这进而可以针对完成的基于纳米结构的电容器部件53提供更高的电容,或者在多于一个电容器被嵌入电容器部件53中的情况下对每个电容器器件的绝对电容值提供更多的控制。

159.然后从催化剂层生长纳米结构65。使用垂直生长的纳米结构允许对纳米结构的特性进行广泛调整。例如,可以选择生长条件以实现使每个纳米结构具有大表面积的形态,这进而可以增加电荷存储电容或每2d占用空间的电容。作为cnf的替代,纳米结构可以是金属碳纳米管或碳化物衍生的碳纳米结构、纳米线例如铜、铝、银、硅化物或其他类型的具有导电特性的纳米线。有利地,可以以本身已知的方式选择催化剂材料和生长气体等,以实现纳米结构65的所谓尖端生长,这可以在纳米结构65的尖端73处产生催化剂层材料。在垂直排列的导电纳米结构65生长之后,纳米结构65和第一电极层63可以可选地被金属层保形地涂

覆,主要用于改善纳米结构65与导电控制材料之间的粘附性。

160.在垂直排列的导电纳米结构65生长之后,纳米结构65和未被纳米结构65覆盖的第一电极层63的部分可以被固体电介质材料层67保形地涂覆。固体电介质材料层67可以有利地由所谓的高k电介质制成。高k电介质材料可以是例如hfox、tiox、taox或其他公知的高k电介质。替选地,电介质可以是基于聚合物的,例如聚丙烯、聚苯乙烯、聚(对二甲苯)、聚对二甲苯基等。其他公知的电介质材料,例如siox或sinx等也可以用作电介质层。可以适当地使用任何其他合适的导电控制材料。可以通过cvd、热处理、原子层沉积(ald)或旋涂或喷涂或工业中使用的任何其他合适的方法来沉积电介质材料。在各种实施方式中,使用多于一个电介质层或具有不同电介质常数或不同电介质材料厚度的相异电介质材料来控制有效电介质常数或影响击穿电压或其组合以控制电介质膜特性可能是有利的。有利地,固体电介质材料层67以原子均匀性均匀地涂覆在纳米结构65上,使得电介质层覆盖整个纳米结构65,使得电容器器件的漏电流最小化。提供具有原子均匀性的固体电介质层67的另一优点是固体电介质层67可以顺应导电纳米结构65的极小表面不规则性,这可以在纳米结构的生长期间引入。这提供了mim布置55的增加的总电极表面积,这进而针对给定的部件尺寸提供了更高的电容。

161.此后,将粘附金属层——第二电极层69的上述第一子层75——保形地涂覆在固体电介质材料层67上。粘附金属层75可以有利地使用ald形成,并且用于粘附金属层75的合适材料的示例可以是ti或tin。

162.在粘附金属层75的顶部上,可以可选地形成所谓的种子金属层79——第二电极层69的上述第三子层79。种子金属层79可以保形地涂覆在粘附金属层75上。种子金属层79可以例如由al、cu或任何其他合适的种子金属材料制成。

163.在形成种子金属层79之后,设置上述第二子层77。第二电极层63的该第二子层77可以例如通过化学方法(例如电镀、化学电镀或本领域已知的任何其他方法)形成。如图9中示意性指示的,第二子层77可以有利地填充纳米结构65之间的空间以提供改善的结构鲁棒性等。

164.可以使用本身已知的技术形成第一连接结构57和第二连接结构59,例如凸块、球或柱。此后,设置绝缘封装材料61以至少部分地嵌入mim布置55。任何已知的合适的封装剂材料(例如,硅树脂、环氧树脂、聚酰亚胺、bcb、树脂、硅胶、环氧树脂底层填料等)可以用于封装剂层。在一些方面,如果硅材料适合某些其他ic封装方案,则硅材料可能是有利的。封装剂可以固化以形成封装层。在本发明的一些方面中,封装剂层可以是可固化材料,使得可以通过固化工艺来附接无源部件。在一些方面中,封装剂的电介质常数不同于mim构造中使用的电介质材料的电介质常数。在一些方面中,与在制造mim电容器中使用的电介质材料相比,优选具有较低电介质常数的封装剂材料。在一些方面中,sin、sio或旋涂玻璃也可以用作封装剂材料。封装剂层可以通过cvd或通过本领域已知的任何其他方法来旋涂并干燥、沉积。

165.在该步骤之后,取决于完成的电容器部件53的期望配置,可以可选地使衬底81变薄或完全去除。

166.对于衬底是第一电极的情况,除非需要使衬底进一步变薄,否则该步骤是可选的。

167.在接下来的步骤中,使用已知技术对面板或晶片进行单片化以提供分立的mim电

容器部件53。

168.任何前述实施方式都适合于以工业中使用的晶片级工艺和面板级工艺来制造。它们可以方便地分别被称为晶片级处理和面板级处理。在晶片级处理中,通常使用圆形衬底,尺寸范围从2英寸到12英寸晶片。在面板级处理中,尺寸由机器容量限定,并且可以是圆形或矩形或正方形,尺寸通常较大,但不限于12英寸到100英寸。面板级处理通常用于生产智能电视。因此,尺寸可以是电视的尺寸或更大。在晶片级工艺的一个方面中,上述实施方式中的至少一个在半导体加工厂中以晶片级进行处理。在另一方面中,对于面板级处理,上述实施方式中的至少一个通过使用面板级处理来处理。根据设计要求,在处理之后,利用标准切割、等离子体切割或激光切割将晶片或面板切割成更小的块。可以通过切割或等离子体切割或激光切割来配置这种单体化处理步骤,以根据需要定制形成的分立部件的形状和尺寸。

169.本发明还预期可兼容用于卷对卷制造技术。卷对卷处理是在塑料或金属箔的卷上生产柔性和大面积电子设备的方法。该方法也被描述为印刷方法。在卷对卷印刷中使用的衬底材料通常是纸、塑料膜或金属箔或不锈钢。与其他方法(如晶片级或面板级)相比,卷对卷方法能够实现高得多的吞吐量,并且具有小得多的碳足迹并且利用更少的能量。卷到卷处理应用于许多制造领域,例如柔性和大面积电子设备、柔性太阳能板、印刷/柔性薄膜电池、纤维和纺织品、金属箔和片材制造、医疗产品、建筑中的能源产品、膜和纳米技术。

170.根据图10中示意性示出的mim布置55的另一示例配置,可以存在嵌入在电介质材料61中的多个第二导电纳米结构66。多个第二导电纳米结构中的每个纳米结构66可以垂直布置在第二电极层64上,第二电极层64可以形成在与第一电极层63相同的平面中。

171.在本发明的实施方式中,纳米结构的数目和/或几何形状或其组合可被调整或配置成控制包括纳米结构的分立电容器部件53的有效自谐振频率(srf)。

172.根据实施方式,纳米结构可以被配置成基本上彼此平行。有利地,相互平行的纳米结构可以被布置成六边形晶胞构造,这提供了增加的每单位面积电容。

173.替选地,纳米结构可以是随机取向的。

174.根据实施方式,电容器子组中的每个电容器可以被设计和布置成对于具有因此适配的特征自谐振频率(srf)的低频、中频和高频操作范围之一有效。

175.在实施方式中,纳米结构的数目和/或几何形状可以被配置成控制基于纳米结构的电容器部件53的有效q值小于120。

176.包括在根据本发明的实施方式的电子系统3的pdn中的一个或更多个电容器部件可以形成噪声抑制滤波器的至少一部分。

177.电容器部件可以与半导体部件9串联连接。

178.根据实施方式,不排除包括tsc、mlcc、钽或licc的任何其他类型的电容器的存在,并且在不脱离本发明的范围的情况下,因此可以提供这样的其他类型的电容器作为形成pdn网络系统的结构的一部分。

179.此外,本发明公开内容预期,通过实现本文呈现的所公开主题的各种实施方式中的一个或更多个,可以实现例如pcb或管芯上的面积(例如,电容器部件的x-y占用空间)和体积(例如,与电容器部件的高度组合的面积)的显著节省。面积和体积的节省可以极大地帮助满足未来几代的各种外形因子和降低的成本/材料清单。

180.本领域技术人员认识到,本发明决不限于上述优选实施方式。相反,在所附权利要求的范围内,许多修改和变型是可能的。

181.在权利要求中,词语“包括”不排除其他元件或步骤,并且不定冠词“一”或“一个”不排除多个。单个处理器或其他单元可以实现权利要求中所述的多个项的功能。在相互不同的从属权利要求中陈述某些措施的仅有事实并不表示不能有利地使用这些措施的组合。权利要求中的任何附图标记不应解释为限制范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。