1.本发明涉及一种适用于各种电子设备的多层压敏电阻。

背景技术:

2.近年来,随着家用电器和车载电子设备的小型化,作为家用电器和车载电子设备的部件的压敏电阻也需要小型化。此外,随着频率的增加,静电电容对性能产生影响,因此需要在确保规定的压敏电阻电压的同时具有低静电电容并且静电电容的变化很小的压敏电阻。当压敏电阻成对使用时,提出在一个元件中形成两个压敏电阻,以减小压敏电阻对之间的静电容量差。应当注意,已知专利文献1是与本技术的发明相关的现有技术文献信息的示例。

3.然而,在常规的多层压敏电阻中,杂散电容不仅在提供压敏电阻性能的内部电极之间产生,而且在两个外部电极之间产生。因此,发生串扰,即信号从两个外部电极中的一个泄漏到两个外部电极中的另一个,这可能扰乱信号波形。

4.引文列表

5.专利文献

6.专利文献1:jp h 07-235406 a

技术实现要素:

7.本公开的一个方面的多层压敏电阻包括烧结体、第一外部电极、第二外部电极、第三外部电极、第一内部电极、第二内部电极和第三内部电极。烧结体具有在第一方向上彼此相对的第一端面和第二端面、在第二方向上彼此相对的第一侧面和第二侧面,以及在第三方向上彼此相对的第一主面和第二主面。烧结体具有包括在第三方向上层叠的多个层的层叠结构,并且呈长边在第一方向上延伸的长方体形状。第一外部电极设置在第一侧面或第二侧面中的至少一个上。第二外部电极和第三外部电极设置在第一侧面或第二侧面中的至少一个上并且位于第一外部电极的相对侧上。第一内部电极设置在烧结体的内部,并且电连接到第一外部电极。第二内部电极设置在烧结体的内部,并且电连接到第二外部电极。第三内部电极设置在烧结体的内部,并且电连接到第三外部电极。在第三方向上,第一内部电极设置在第二内部电极与第三内部电极之间。

附图说明

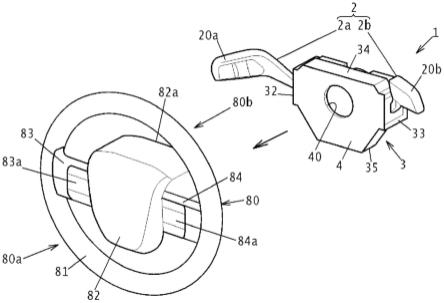

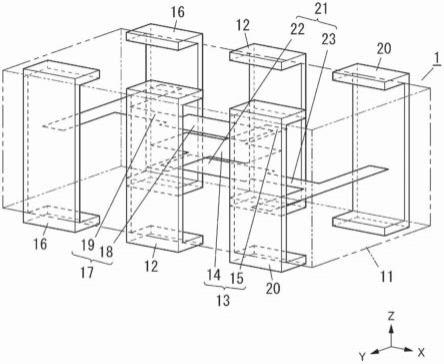

8.图1是本公开的第一实施例的多层压敏电阻的透视立体图;

9.图2是本公开的第一实施例的多层压敏电阻的透视俯视图;

10.图3是本公开的第一实施例的多层压敏电阻的截面图;

11.图4是本公开的第一实施例的多层压敏电阻的外部透视图;

12.图5是本公开的第一实施例的多层压敏电阻的使用例的电路图;

13.图6是本公开的第二实施例的多层压敏电阻的透视立体图;

14.图7是本公开的第二实施例的多层压敏电阻的外部透视图;

15.图8是本公开的第三实施例的多层压敏电阻的透视立体图;

16.图9是本公开的第三实施例的多层压敏电阻的透视俯视图;

17.图10是本公开的第三实施例的多层压敏电阻的截面图;以及

18.图11是本公开的变形例的多层压敏电阻的截面图。

具体实施方式

19.(1)第一实施例

20.下面将参考附图描述本公开的第一实施例的多层压敏电阻。

21.图1是第一实施例的多层压敏电阻1的透视立体图。图2是多层压敏电阻1的透视俯视图。图3是多层压敏电阻1的截面图。多层压敏电阻1包括烧结体11、第一外部电极12、第二外部电极16、第三外部电极20、第一内部电极13、第二内部电极17和第三内部电极21。除了多层压敏电阻1的外部电极以外,烧结体11例如呈长1.6mm、宽0.8mm并且高0.8mm的长方体形状。应当注意,在诸如图3的外部透视图中,烧结体11的外形以长方体的形式示出,但是烧结体11的拐角可以相应地斜切,或者烧结体11的拐角可以被倒圆。

22.在下面的描述中,如图1中所示,将与烧结体11的长边方向平行的x轴方向定义为左/右方向,将y轴方向定义为前/后方向(深度方向),将z轴方向定义为上/下方向。此外,将x轴的正方向定义为右侧,将y轴的正方向定义为前侧,并且将z轴的正方向定义为上侧。然而,这些方向仅是示例,并且不应解释为限制多层压敏电阻1在使用时的方向。另外,图中表示各方向的箭头仅作为辅助说明而显示,不具有实体。

23.如图2和图3中所示,烧结体11具有在第一方向上彼此相对的第一端面s11和第二端面s12、在第二方向上彼此相对的第一侧面s21和第二侧面s22,以及在第三方向上彼此相对的第一主面s31和第二主面s32。烧结体11具有包括在第三方向上层叠的多个层ly11至ly14(参考图3)的层叠结构,并且呈长边在第一方向上延伸的长方体形状。

24.烧结体11包括具有非线性电阻特性的半导体陶瓷成分。烧结体11例如包括zno作为主要成分,可以包括选自由bi2o3、co2o3、mno2和sb2o3组成的组中的至少一种作为副成分,并且可以包括选自由pr6o

11

、co2o3、caco3和cr2o3组成的组中的至少一种。在烧结体11中,zno被烧结,并且其他副成分沉积在zno颗粒的晶界上,并且内部电极形成在层叠层之间。在zno颗粒之间形成的晶界势垒表现出非线性电阻特性。烧结体11例如通过将包括zno作为主成分的四个层ly11至ly14(参见图3)彼此层叠,然后对四个层ly11至ly14进行烧结而形成。

25.第一外部电极12设置在烧结体11的长边侧面的中心部。第一外部电极12电连接到第一内部电极13。在本实施例中,烧结体11设置有两个第一外部电极12,并且两个第一外部电极12中的一个设置在第一侧面s21上,而两个第一外部电极12中的另一个设置在第二侧面s22上。两个第一外部电极12经由第一内部电极13相互电连接。

26.第二外部电极16和第三外部电极20设置在第一外部电极12的相对侧。在本实施例中,第二外部电极16和第三外部电极20设置在两个第一外部电极12中的每一个的相对侧。即,在第一侧面s21上,第二外部电极16和第三外部电极20设置在第一外部电极12的相对侧上,并且在第二侧面s22上,第二外部电极16和第三外部电极20设置在第一外部电极12的相对侧上。换言之,烧结体11设置有两个第二外部电极16,并且两个第二外部电极16中的一个

设置在第一侧面s21上,而两个第二外部电极16中的另一个设置在第二侧面s22上。类似地,烧结体11设置有两个第三外部电极20,并且两个第三外部电极20中的一个设置在第一侧面s21上,而两个第三外部电极20中的另一个设置在第二侧面s22上。

27.电连接到第二外部电极16的第二内部电极17和电连接到第三外部电极20的第三内部电极21设置在烧结体11的内部。第二外部电极16电连接到第二内部电极17,并且第三外部电极20电连接到第三内部电极21。即,设置在烧结体11上的两个第二外部电极16经由第二内部电极17彼此电连接,并且设置在烧结体11上的两个第三外部电极20经由第三内部电极21彼此电连接。

28.在本实施例中,烧结体11例如包括在第三方向上层叠的四个层ly11至ly14(参见图3)。第一内部电极13例如通过印刷在四个层ly11至ly14中的层ly12的上表面(以下也称为第一层叠面sf1)上而设置。第二内部电极17例如通过印刷在层ly13的上表面(以下也称为第二层叠面sf2)上而设置,其中层ly13层叠在层ly12的上侧。第三内部电极21例如通过印刷在层ly11的上表面(以下也称为第三层叠面sf3)上而设置,其中层ly11层叠在层ly12的下侧。换言之,第一内部电极13设置在烧结体11内部的第一层叠面sf1上。第二内部电极17设置在烧结体11的内部不同于第一层叠面sf1的第二层叠面sf2上。第三内部电极21设置在烧结体11内部不同于第一层叠面sf1和第二层叠面sf2的第三层叠面sf3上。因此,在第三方向(上/下方向)上,第一内部电极13设置在第二内部电极17与第三内部电极21之间。

29.第一内部电极13包括第一对向部14和第一引出部15。第一引出部15中的每一个的宽度小于第一对向部14的宽度。第一引出部15沿第二方向从第一对向部14突出。在本实施例中,两个第一引出部15从第一对向部14向前和向后突出。两个第一引出部15中的一个电连接到设置在第一侧面s21上的第一外部电极12,并且两个第一引出部15中的另一个电连接到设置在第二侧面s22上的第一外部电极12。

30.第二内部电极17包括第二对向部18和第二引出部19。第二引出部19的宽度小于第二对向部18的宽度。第二引出部19沿第一方向从第二对向部18突出。在本实施例中,如图2中所示,第二引出部19包括将两个第二外部电极16彼此连接的第一连接部19b,以及沿第一方向从第二对向部18突出并且连接到第一连接部19b的第一突出部19a。此处,第一突出部19a例如从第二对向部18向左突出。第一连接部19b从第一突出部19a的左端向前和向后突出以将两个第二外部电极16彼此连接。

31.第三内部电极21包括第三对向部22和第三引出部23。第三引出部23的宽度小于第三对向部22的宽度。第三引出部23沿第一方向从第三对向部22突出。在本实施例中,第三引出部23沿远离第二引出部19的方向例如向右突出。如图2中所示,第三引出部23包括将两个第三外部电极20彼此连接的第二连接部23b,以及沿第一方向从第三对向部22突出并且连接到第二连接部23b的第二突出部23a。此处,第二突出部23a例如从第三对向部22向右突出。第二连接部23b从第二突出部23a的右端向前和向后突出以将两个第三外部电极20彼此连接。

32.此处,第一内部电极13设置在第一层叠面sf1上,第二内部电极17设置在第二层叠面sf2上,并且第三内部电极21设置在第三层叠面sf3上,并且第一内部电极13、第二内部电极17和第三内部电极21均沿第二方向设置。

33.在本实施例中,在第一方向上,第一对向部14的长度大于第二对向部18和第三对

向部22中的每一个的长度。此外,在第二方向上,第一对向部14的长度大于第二对向部18和第三对向部22中的每一个的长度。因此,第一对向部14的面积大于第二对向部18和第三对向部22中的每一个的面积。具有这种尺寸的第一对向部14设置在第二对向部18与第三对向部22之间,因此,在第二对向部18与第三对向部22之间产生的杂散电容减小,从而抑制了串扰。

34.如上所述,在本实施例中,两个第一外部电极12、两个第二外部电极16和两个第三外部电极20设置在沿层叠方向观察烧结体11时作为长边的两个侧面(第一侧面s21和第二侧面s22)上。在第一方向上,第一外部电极12中的每一个设置在第二外部电极16与第三外部电极20之间,因此可以减小第二外部电极16与第三外部电极20之间的杂散电容。此外,两个第一外部电极12经由第一引出部15彼此连接,两个第二外部电极16经由第二引出部19彼此连接,并且两个第三外部电极20经由第三引出部23彼此连接。这种结构能够同时形成第一外部电极12、第二外部电极16和第三外部电极20,因此,形成这些电极的步骤被简化并且这些电极可以稳定地形成形状,从而能够得到特性偏差少的多层压敏电阻1。

35.另外,在烧结体11的层叠方向上,第一内部电极13设置在第二内部电极17与第三内部电极21之间。即,在第三方向上,第一内部电极13设置在第二内部电极17与第三内部电极21之间。具体而言,第一对向部14设置在第二内部电极17与第三内部电极21之间。换言之,第二对向部18与第三对向部22彼此相对,并且第一内部电极13设置在第二对向部18与第三对向部22之间。因此,第一对向部14设置在第二对向部18与第三对向部22之间。第二对向部18面向第一对向部14,并且第一对向部14面向第三对向部22,从而形成压敏电阻区域。

36.图5是本实施例的多层压敏电阻1的使用例的示意性电路图。本实施例的多层压敏电阻1包括:形成在第一外部电极12和第二外部电极16之间的第一压敏电阻1a;以及形成在第一外部电极12和第三外部电极20之间的第二压敏电阻1b。图5中的电路图示出了设置在通信ic 2附近的多层压敏电阻1,该通信ic 2被配置成基于两线差分电压传输方案进行通信。信号线3和4的焊盘以及接地线5的焊盘连接到通信ic 2。设置在第一侧面s21和第二侧面s22上的成对的第一外部电极12连接到接地线5的焊盘,设置在第一侧面s21和第二侧面s22上的成对的第二外部电极16连接到信号线3的焊盘,并且设置在第一侧面s21和第二侧面s22上的成对的第三外部电极20连接到信号线4的焊盘。在这样的电路中,例如,当静电叠加在信号线3上并且因此高于规定阈值电压的电压被施加到第一压敏电阻1a时,第一压敏电阻1a的电阻急剧减小,并且电流流过第一压敏电阻1a,从而保护了通信ic 2。应当注意,图5中所示的电路仅是应用多层压敏电阻1的电路的示例,因此可以对该电路进行相应的修改。

37.在本实施例的多层压敏电阻1中,第一对向部14例如是边长为0.46mm

×

0.20mm的长方形,并且第二对向部18和第三对向部22各自是例如边长为0.40mm

×

0.14mm的长方形。另外,第一对向部14和第二对向部18彼此隔开例如0.035mm的距离而彼此对向。类似地,第一对向部14和第三对向部22隔开例如0.035mm的距离而彼此对向。此处,当从层叠方向观察时,第一对向部、第二对向部和第三对向部的中心位于相同位置。即,当从层叠方向观察时,第一对向部14比第二对向部18和第三对向部22多延伸0.03mm,并且完全覆盖第二对向部18和第三对向部22的周缘。换言之,当从第三方向观察时,第一对向部14覆盖第二对向部18和第三对向部22的外周。这防止了在第二对向部18与第三对向部22之间产生杂散电容,从而

抑制串扰。应当注意,上述尺寸仅仅是示例,并且可以相应地进行修改。

38.具有例如0.1mm宽度的第二引出部19从第二对向部18延伸并且连接到第二外部电极16。类似地,具有例如0.1mm宽度的第三引出部23从第三对向部22延伸并且连接到第三外部电极20。此外,具有例如0.1mm宽度的第一引出部15从第一对向部14延伸并且连接到第一外部电极12。如上所述,内部电极经由宽度小于对向部的引出部连接到外部电极,因此,每个第二外部电极16与每个第三外部电极20之间的杂散电容可以减小,从而使对串扰的影响最小化。

39.此处,在第二方向上,第二引出部19的宽度期望地小于或等于第二对向部18的宽度的90%。此外,在第二方向上,第二引出部19的宽度更期望地小于或等于第二对向部18的宽度的70%。类似地,在第二方向上,第三引出部23的宽度期望地小于或等于第三对向部22的宽度的90%。另外,在第二方向上,第二引出部19的宽度更期望地小于或等于第二对向部18的宽度的70%。相反地,如果第二引出部19的宽度和第三引出部23的宽度分别大于第二对向部18的宽度和第三对向部22的宽度的90%,则影响串扰的杂散电容增加,因此,这样的宽度是不希望的。另外,通过使在第二方向上第二引出部19的宽度小于或等于第二对向部18的宽度的90%,在第一压敏电阻1a中产生的杂散电容减小,从而抑制串扰的发生。另外,通过使在第二方向上第三引出部23的宽度小于或等于第三对向部22的宽度的90%,在第二压敏电阻1b中产生的杂散电容减小,从而抑制串扰的发生。此外,通过减小第一压敏电阻1a的杂散电容与第二压敏电阻1b的杂散电容之差的绝对值,抑制了串扰。

40.此外,在第二方向上,第二引出部19的宽度期望地大于或等于0.08mm,并且更期望地大于或等于0.1mm。类似地,在第二方向上,第三引出部23的宽度期望地大于或等于0.08mm,并且更期望地大于或等于0.1mm。如果第二引出部19和第三引出部23中每一个的宽度小于0.08mm,则第二引出部19和第三引出部23中每一个的形状趋于变得不稳定,因此,第二引出部19与第二外部电极16的连接以及第三引出部23与第三外部电极20的连接容易变得不稳定。通过使第二引出部19和第三引出部23均具有大于或等于0.08mm的宽度,提供了容易保持第二引出部19和第三引出部23中每一个的形状的优点。

41.此外,在第一方向上,第一引出部15的宽度期望地小于或等于第一对向部14的宽度的90%。此外,在第一方向上,每个第一引出部15的宽度更期望地小于或等于第一对向部14的宽度的70%。通过使在第一方向上每个第一引出部15的宽度小于或等于第一对向部14的宽度的90%,减小了杂散电容,从而抑制串扰的发生。另外,在第一方向上,第一引出部15的宽度期望地大于或等于0.08mm,并且更期望地大于或等于0.1mm。这提供了容易保持每个第一引出部15的形状的优点。

42.此外,当从上面观察时,在第一方向上,第一对向部14从第二对向部18和第三对向部22的外周延伸的尺寸期望地大于或等于第二对向部18和第三对向部22中每一个的长边的7.5%并且小于或等于15%。换言之,在第一方向上,第一对向部14的长度优选大于或等于第二对向部18或第三对向部22的长度的107.5%并且小于或等于第二对向部18或第三对向部22的长度的115%。这是因为如果第一对向部14的突出量小于第二对向部18和第三对向部22中每一个的长边的7.5%,则串扰迅速增加,并且如果突出量大于长边的15%,则无法减少制造中的错位,导致第一压敏电阻1a与第二压敏电阻1b之间的容量差大。应当注意,在第一方向上,第一对向部14的长度更优选地大于或等于第二对向部18或第三对向部22的

长度的9%并且小于或等于第二对向部18或第三对向部22的长度的13.5%,在这种情况下,可以进一步减少串扰,并且可以减少制造中的错位。

43.应当注意,在第二方向上,第一对向部14的长度优选地大于或等于第二对向部18或第三对向部22的长度的107.5%并且小于或等于第二对向部18或第三对向部22的长度的115%。这是因为如果第一对向部14的突出量小于第二对向部18和第三对向部22中每一个的长边的7.5%,则串扰迅速增加,并且如果突出量大于长边的15%,则无法减少制造中的错位,这导致第一压敏电阻1a与第二压敏电阻1b之间的容量差大。

44.此外,在烧结体11中,第一对向部14与第二对向部18之间的区域的体积优选地小于或等于烧结体11的总体积的5%,并且期望地小于或等于1%。这是因为如果体积大于1%,则整个压敏电阻区域都在外部电极附近,这会增加影响串扰的电容。

45.此外,第一对向部14的面积优选大于第二对向部18或第三对向部22的面积。在本实施例中,第一内部电极13、第二内部电极17和第三内部电极21形成为使得第一对向部14的面积大于第二对向部18的面积并且大于第三对向部22的面积。

46.顺便提及,第一内部电极13的第一对向部14被设置为在烧结体11的内部在第三方向上与第二内部电极17的第二对向部18和第三内部电极21的第三对向部22重叠。即,第一内部电极13具有在第三方向上与第二内部电极17和第三内部电极21重叠的重叠区域a1(参见图2)。

47.重叠区域a1是长边方向沿第一方向延伸的长方形区域。重叠区域a1在第一方向上的长度l1大于重叠区域a1在第二方向上的长度l2。第一方向上的长度l1大于第二方向上的长度l2,从而减小了在夹持着第一对向部14设置的第二对向部18与第三对向部22之间产生的杂散电容,从而抑制了串扰。

48.此外,本实施例的多层压敏电阻1包括第一压敏电阻1a和第二压敏电阻1b,其中第一压敏电阻1a的静电电容和第二压敏电阻1b的静电电容分别优选地小于或等于200pf。此外,第一压敏电阻1a的静电电容与第二压敏电阻1b的静电电容之差优选为大于或等于第一压敏电阻1a的静电电容的-20%并且小于或等于第一压敏电阻1a的静电电容的 20%。这可以在将多层压敏电阻1连接到如图5中所示的通信ic 2时抑制串扰,从而提高通信质量。

49.(2)第二实施例

50.下面将参考图6和图7描述第二实施例的多层压敏电阻1。

51.图6是第二实施例的多层压敏电阻1的透视立体图。图7是第二实施例的多层压敏电阻1的外部透视图。

52.在第一实施例的多层压敏电阻1中,第二外部电极16和第三外部电极20设置在用作长边的两个侧面上,而在第二实施例的多层压敏电阻1中,第二外部电极16设置在烧结体11的第一端面s11上,并且第三外部电极20设置在烧结体11的第二端面s12上。应当注意,第一内部电极13、第二内部电极17和第三内部电极21的结构与第一实施例中的结构类似,因此用相同的附图标记标注共同的部件并且省略其说明。

53.在第二实施例的多层压敏电阻1中,第一外部电极12设置在第一侧面s21的一部分和第二侧面s22的一部分上。

54.第二外部电极16设置在第一端面s11的至少一部分上。在本实施例中,第二外部电极16设置在整个第一端面s11上,并且从第一端面s11延伸到第一侧面s21、第二侧面s22、第

一主面s31和第二主面s32中每一个的一部分。

55.此外,第三外部电极20设置在第二端面s12的至少一部分上。在本实施例中,第三外部电极20设置在整个第二端面s12上,并且从第二端面s12延伸到第一侧面s21、第二侧面s22、第一主面s31和第二主面s32中每一个的一部分。

56.应当注意,在第二实施例的多层压敏电阻1中,第二外部电极16从第一端面s11延伸到第一侧面s21、第二侧面s22、第一主面s31和第二主面s32中每一个的一部分,因此,与第一实施例的多层压敏电阻1相比,第二外部电极16与第一外部电极12中每一个之间的距离可以更大,从而减小了第二外部电极16与第一外部电极12中每一个之间的杂散电容。

57.此外,在第二实施例的多层压敏电阻1中,第三外部电极20从第二端面s12延伸到第一侧面s21、第二侧面s22、第一主面s31和第二主面s32中每一个的一部分,因此,与第一实施例的多层压敏电阻1相比,第三外部电极20与第一外部电极12中每一个之间的距离可以更大,从而减小了第三外部电极20与第一外部电极12中每一个之间的杂散电容。

58.此外,第二外部电极16设置在烧结体11的第一端面s11上,并且第三外部电极20设置在烧结体11的第二端面s12上,因此,与第一实施例的多层压敏电阻1相比,第二外部电极16与第三外部电极20之间的距离可以更大,从而进一步减小对串扰的影响。

59.(3)第三实施例

60.下面将参考图8至图10描述第三实施例的多层压敏电阻1。

61.图8是第三实施例的多层压敏电阻1的透视立体图。图9是第三实施例的多层压敏电阻1的透视俯视图。图10是第三实施例的多层压敏电阻1的截面图。

62.在第二实施例的多层压敏电阻1中,第一对向部14覆盖第二对向部18和第三对向部22的外周,而在第三实施例中,第二对向部18和第三对向部22中每一个的一部分突出到第一对向部14的外侧,如图9和图10中所示。应当注意,除了第一内部电极13、第二内部电极17和第三内部电极21之外的部件具有与第二实施例的多层压敏电阻1类似的结构,因此用相同的附图标记标注与第二实施例相同的部件并且省略其说明。

63.第二对向部18具有长边方向沿第一方向延伸的长方形形状。第二对向部18在第一方向上的长度大于第一对向部14在第一方向上的长度,并且第二对向部18在第二方向上的长度小于第一对向部14在第二方向上的长度。

64.类似地,第三对向部22具有长边方向沿第一方向延伸的长方形形状。第三对向部22在第一方向上的长度大于第一对向部14在第一方向上的长度,并且第三对向部22在第二方向上的长度小于第一对向部14在第二方向上的长度。

65.第一对向部14和第二对向部18隔开规定距离彼此对向,并且第一对向部14和第三对向部22隔开规定距离彼此对向。当从层叠方向观察时,第一对向部14、第二对向部18和第三对向部22的中心位于相同位置处,并且当从层叠方向观察时,第二对向部18和第三对向部22基本彼此重叠。此外,当从层叠方向观察时,在第一方向上,第二对向部18的右端和左端从第一对向部14突出,并且第三对向部22的右端和左端从第一对向部14突出。除了从第一对向部14突出的右端和左端之外,第二对向部18被第一对向部14覆盖。类似地,除了从第一对向部14突出的右端和左端之外,第三对向部22被第一对向部14覆盖。

66.此处,在印刷内部电极、层叠和切割层、形成外部电极等步骤中引起的内部电极的位移可能导致第一内部电极13相对于第二内部电极17和第三内部电极21沿第一方向的位

移。第一内部电极13相对于第二内部电极17和第三内部电极21沿第一方向的位移可能导致第一外部电极12中的每一个与第二外部电极16之间产生的静电电容与第一外部电极12中的每一个与第三外部电极20之间产生的静电电容的容量差增大。在本实施例的多层压敏电阻1中,第二对向部18和第三对向部22沿第一方向在第一对向部14的两侧上突出,因此,即使当第一内部电极13相对于第二内部电极17和第三内部电极21沿第一方向移位时,也可以减小第一外部电极12中的每一个与第二外部电极16之间产生的静电电容与第一外部电极12中的每一个与第三外部电极20之间产生的静电电容的容量差。这提供了可以抑制由于第一压敏电阻1a与第二压敏电阻1b之间的容量差引起的串扰的优点。

67.下面的表1示出了重叠区域a1的纵向尺寸(长度l1)与横向尺寸(长度l2)的比率与由于尺寸变化引起的容量差之间的关系。尺寸变化是在印刷内部电极、层叠和切割层、形成外部电极等的每个步骤中引起的内部电极之间的尺寸或内部电极与外部电极之间的尺寸的变化。容量差是在第一内部电极13与第二内部电极17之间产生的杂散电容与在第一内部电极13与第三内部电极21之间产生的杂散电容之差的绝对值。在表1中,对示例1、3和4以及比较示例1和2的容量差进行评价,其中示例2的容量差为1。此处,烧结体11呈长1.6mm、宽0.8mm并且高0.8mm的长方体形状,第一对向部14呈长0.44mm并且宽0.22mm的长方形形状,并且第二对向部18和第三对向部22分别呈长0.54mm并且宽0.12mm的长方形形状。

68.[表1]

[0069][0070][0071]

根据表1的结果,重叠区域a1在第一方向上的长度l1与重叠区域a1在第二方向上的长度l2的比率优选地大于或等于1.3并且小于或等于7.5。减小第一压敏电阻1a与第二压敏电阻1b之间的静电电容差可以提高通信质量。

[0072]

此外,下面的表2示出了重叠区域a1的面积与烧结体11的第一层叠面sf1的面积的比率(面积比)与由于尺寸变化引起的容量差之间的关系。与上述同样,尺寸变化是在印刷内部电极、层叠和切割层、形成外部电极等每个步骤中引起的内部电极之间的尺寸或内部电极与外部电极之间的尺寸的变化。容量差是在第一内部电极13与第二内部电极17之间产生的杂散电容与在第一内部电极13与第三内部电极21之间产生的杂散电容之差的绝对值。在表2中,对示例5和6以及比较示例3和4的容量差进行评价,其中示例2的容量差为1。此处,烧结体11呈长1.6mm、宽0.8mm并且高0.8mm的长方体形状,第一对向部14呈长0.44mm并且宽0.22mm的长方形形状,并且第二对向部18和第三对向部22分别呈长0.54mm并且宽0.12mm的长方形形状。

[0073]

[表2]

[0074] 面积比容量差比较示例30.0200.85示例50.0240.86示例20.0401.00示例60.1611.26比较示例40.3911.63

[0075]

根据表2的结果,重叠区域a1的面积与烧结体11在第一层叠面sf1上的截面积的比率优选地大于或等于0.024并且小于或等于0.161。减小第一压敏电阻1a与第二压敏电阻1b之间的静电电容差可以提高通信质量。

[0076]

应当注意,在第三实施例的多层压敏电阻1中,与第一实施例和第二实施例中每一个实施例的多层压敏电阻1同样,第一内部电极13具有在第三方向上与第二内部电极17和第三内部电极21重叠的重叠区域a1。此处,在第一层叠面sf1上,重叠区域a1在除了第一区域a2之外的第二区域a3中,其中第一外部电极12、第二外部电极16和第三外部电极20中的每一个投影在第一区域a2上。这减小了在第一外部电极12中的每一个与第二外部电极16之间产生的杂散电容以及在第一外部电极12中的每一个与第三外部电极20之间产生的杂散电容,从而抑制了串扰。应当注意,第一实施例和第二实施例中每一个实施例的多层压敏电阻1在第一层叠面sf1上包括位于除了第一区域a2之外的第二区域a3中的重叠区域a1,从而抑制串扰,其中第一外部电极12、第二外部电极16和第三外部电极20中的每一个投影在第一区域a2上。

[0077]

应当注意,第三实施例的第一内部电极13、第二内部电极17和第三内部电极21可以应用于第一实施例的多层压敏电阻1,从而提供与由第三实施例的多层压敏电阻1提供的优点类似的优点。

[0078]

(4)变型

[0079]

下面将描述本公开的多层压敏电阻的变型。

[0080]

图1中的多层压敏电阻1包括:包括彼此对向的第二内部电极17和第一内部电极13的一个层;以及包括彼此对向的第三内部电极21和第一内部电极13的一个层。然而,替代地,如图11中所示,可以设置各自包括彼此对向的第二内部电极17和第一内部电极13的多个层以及各自包括彼此对向的第三内部电极21和第一内部电极13的多个层。在这种情况下,优选地将这些层竖直分离,使得各自包括第二内部电极17和第一内部电极13的多个层例如设置在上表面侧,并且各自包括第三内部电极21和第一内部电极13的多个层例如设置在下表面侧,如图11中所示。这种配置可以进一步抑制串扰。此外,通过增大第二内部电极17与第一内部电极13的对向面积以及第三内部电极21与第一内部电极13的对向面积,可以提高作为压敏电阻的性能。

[0081]

应当注意,在第二实施例和第三实施例中每一个实施例的多层压敏电阻1中,多个第二内部电极17和多个第一内部电极13可以彼此对向,和/或多个第三内部电极21和多个第一内部电极13可以彼此对向。

[0082]

此外,在第一实施例的多层压敏电阻1中,第一外部电极12、第二外部电极16和第三外部电极20设置在第一侧面s21和第二侧面s22两者上,但是第一外部电极12、第二外部

电极16和第三外部电极20可以设置在第一侧面s21或第二侧面s22中的至少一个上。也就是说,第一外部电极12、第二外部电极16和第三外部电极20可以仅设置在第一侧面s21或第二侧面s22上。

[0083]

此外,在上述实施例中,将四个层ly11至ly14相互层叠,从而形成烧结体11,但烧结体11不限于具有包括四个层的层叠结构。烧结体11至少具有包括多个层的层叠结构。

[0084]

根据本公开的多层压敏电阻1减小了在外部电极之间产生的杂散电容,因此抑制了串扰,因此该多层压敏电阻1在工业上是有用的。

[0085]

附图标记列表

[0086]

1多层压敏电阻

[0087]

1a第一压敏电阻

[0088]

1b第二压敏电阻

[0089]

11烧结体

[0090]

12第一外部电极

[0091]

13第一内部电极

[0092]

14第一对向部

[0093]

15第一引出部

[0094]

16第二外部电极

[0095]

17第二内部电极

[0096]

18第二对向部

[0097]

19第二引出部

[0098]

19a第一突出部

[0099]

19b第一连接部

[0100]

20第三外部电极

[0101]

21第三内部电极

[0102]

22第三对向部

[0103]

23第三引出部

[0104]

23a第二突出部

[0105]

23b第二连接部

[0106]

a1重叠区域

[0107]

a2第一区域

[0108]

a3第二区域

[0109]

ly11至ly14层

[0110]

s11第一端面

[0111]

s12第二端面

[0112]

s21第一侧面

[0113]

s22第二侧面

[0114]

s31第一主面

[0115]

s32第二主面

[0116]

sf1第一层叠面

[0117]

sf2第二层叠面

[0118]

sf3第三层叠面。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。