1.本发明涉及微弱信号检测仪器领域,更具体地,涉及一种光电隔离的高频数字锁相放大器。

背景技术:

2.锁相放大器利用相敏检测的方法,能在强噪声背景下提取出特定频率的信号,在微弱信号检测领域中有着广泛的应用。在系统架构上,数字锁相放大器相对于模拟锁相放大器而言,将算法的核心相敏检测器在数字器件中实现,能更好地提升锁相放大器的测量线性度和动态储备。

3.如图1所述,现有的数字锁相放大器的信号链路是待测信号或参考信号输入系统后,都依次经过低噪声模拟调理链路、模数转换器、数字信号处理器件,同时有一时钟管理芯片为数字信号处理器件和模数转换器提供时钟。

4.在带宽超过100mhz的高频应用场景中,数字信号处理器件、模数转换器、时钟管理芯片之间由于高速并行数字接口时序的要求,必须在物理空间上尽可能相近,而低噪声模拟调理链路和模数转换器由于必须保证模拟信号的质量,它们也不可避免地在空间上要相近以减小传输中的损耗和信号畸变。因此现有的数字锁相放大器的整个信号链路各部分之间的物理距离必须相近,这样会导致数字信号处理器件和时钟管理芯片的噪声通过空间辐射,干扰低噪声模拟调理链路和模数转换器,并且不同的输入通道间也会相互干扰,造成测量的精确度下降。

5.另外,由于现有高速数字隔离器的通道间延迟差较大,难以直接在数字信号处理器件与模数转换器插入数字隔离器实现电气隔离,使得数字信号处理器件和不同输入通道之间共用一个电源轨和地,这将导致数字噪声和同步开关噪声通过电源轨耦合干扰模拟信号的精确测量。

6.现有技术中公开了一种模拟数字混合结构的锁相放大器及其锁相放大方法和一种基于dsp和fpga的高速数字锁相放大器的专利,这些专利都依次经过低噪声模拟调理链路、模数转换器、数字信号处理器件,同时有一时钟管理芯片为数字信号处理器件和模数转换器提供时钟,结构复杂,难以实现数字信号处理器件和不同输入通道之间的电气隔离和空间分离。

技术实现要素:

7.本发明提供一种光电隔离的高频数字锁相放大器,该锁相放大器实现数字信号处理器件和不同输入通道之间的电气隔离和空间分离,对高频信号测量精度较高。

8.为了达到上述技术效果,本发明的技术方案如下:

9.一种光电隔离的高频数字锁相放大器,包括信号处理模块、信号传输介质接口、信号输入通道模块;所述信号处理模块通过信号传输介质接口与信号输入通道模块相连接,待测信号和参考信号从信号输入通道模块输入;

10.所述信号处理模块包括相敏检测模块、第一数字逻辑器件、光接收模块、数字正弦发生器、数字锁相环、第一时钟管理芯片、低噪声晶振和微处理器;所述光接收模块、第一数字逻辑器件和相敏检测模块顺次连接,微处理器、数字锁相环、数字正弦发生器和相敏检测模块顺次连接;相敏检测模块还直接连接到微处理器上,第一数字逻辑器件还分别与数字锁相环和第一时钟管理芯片相连,第一时钟管理芯片还与微处理器和低噪声晶振连接;

11.所述信号传输介质接口包括光纤、第一电连接器和第二电连接器;光纤连接到光接收模块上,第一电连接器与第一时钟管理芯片连接,第二电连接器与微处理器连接;

12.所述信号输入通道模块包括光发射模块、第二数字逻辑器件、模数转换器、第一隔离器、第二时钟管理芯片、线性光耦、第二隔离器、低通滤波器和低噪声放大电路;所述低噪声放大电路、低通滤波器、线性光耦、模数转换器、第二数字逻辑器件和光发射模块顺次连接,第一隔离器、第二时钟管理芯片和模数转换器顺次连接,第二隔离器、第二时钟管理芯片和第二数字逻辑器件顺次连接,第二隔离器还与模数转换器连接;待测信号和参考信号从低噪声放大电路输入;

13.所述光发射模块还与光纤连接,第一隔离器还与第一电连接器连接,第二隔离器还与第二电连接器连接。

14.进一步地,所述第一数字逻辑器件将来自光接收模块的电信号进行解码和串并转换后得到参考输入通道数字信号和待测输入通道数字信号,数字锁相环选择参考输入通道数字信号作为输入,进行锁相后连接至数字正弦发生器控制相位和频率。

15.进一步地,所述数字正弦发生器根据来自数字锁相环的控制信号产生一个数字正弦波输入相敏检测模块。

16.进一步地,所述相敏检测模块选择待测输入通道数字信号作为输入,并将其和来自数字正弦发生器的数字正弦波输入进行相乘并滤波,然后连接至微处理器。

17.进一步地,分别记待测输入通道数字信号和参考输入信号为si=aisin(ω0t θ)和sr=arsin(ω0t φ),相敏检测模块输出t φ),相敏检测模块输出和微处理器根据x和y计算出待测幅值和相位差

18.进一步地,所述低噪声晶振产生一低噪声的周期信号作为电路系统的时钟源,连接至第一时钟管理芯片;

19.所述第一时钟管理芯片产生传输时钟信号分别连接至信号传输介质接口内的第一连接器,同时连接至第一逻辑器件和微处理器作为逻辑时钟输入。

20.进一步地,所述低噪声放大电路接收外部信号输入,对其放大并经过低通滤波器滤波后得到输入通道模拟信号,连接至线性光耦;

21.所述线性光耦对输入通道模拟信号进行模拟量的隔离传输后连接至模数转换器;

22.所述模数转换器将来自线性光耦的信号转换成输入通道数字信号,并通过第二数字逻辑器件进行编码和并串转换后,再经过光发射模块将电信号转换为光信号,连接至对应的信号传输介质接口内的光纤。

23.进一步地,所述第一隔离器连接至对应的信号传输介质接口内的第一连接器,将传输时钟信号进行电气隔离转换后连接至第二时钟管理芯片;

24.所述第二时钟管理芯片分别连接至第二数字逻辑器件和模数转换器作为高速驱

动时钟;

25.所述第二隔离器连接至对应的信号传输介质接口内的第二连接器,将来自微处理器的控制信号进行电气隔离转换后连接至第二时钟管理芯片和模数转换器。

26.进一步地,所述第一电连接器和第二电连接器是带屏蔽的网线和排线,以实现传输时钟信号和控制信号的低失真传输。

27.进一步地,所述低噪声晶振产生一25mhz低噪声低抖动的周期信号作为系统的时钟源给到第一时钟管理芯片;第一时钟管理芯片产生100mhz和250mhz分别给到微处理器和第一数字逻辑器件,并产生一25mhz通过第一电连接器和第一隔离器给到第二时钟管理芯片;第二时钟管理芯片产生250mhz时钟给到第二数字逻辑器件和模数转换器,并可以调整输出相位使得第一数字逻辑器件和第二数字逻辑器件时钟同步。

28.与现有技术相比,本发明技术方案的有益效果是:

29.本发明较现有传统架构的数字锁相放大器而言,能够实现数字信号处理器件和不同输入通道之间的电气隔离和数米的空间分离,消除通过共用电源轨耦合的噪声干扰,同时减少通过空间辐射传递的干扰噪声,提高锁相放大器测量高频信号的精度。并且,由信号传输介质接口实现的光电隔离,可以方便实现待测信号的远距离测量。

附图说明

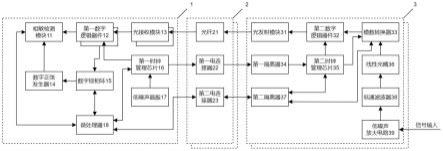

30.图1为现有技术中传统的数字锁相放大器信号链路图;

31.图2为数字锁相放大器的简要系统框图;

32.图3为数字锁相放大器的完整系统框图;

33.图4为数字锁相放大器的时钟分配的示意图;

34.图5为数字锁相放大器的系统相对空间位置的示意图。

具体实施方式

35.附图仅用于示例性说明,不能理解为对本专利的限制;

36.为了更好说明本实施例,附图某些部件会有省略、放大或缩小,并不代表实际产品的尺寸;

37.对于本领域技术人员来说,附图中某些公知结构及其说明可能省略是可以理解的。

38.下面结合附图和实施例对本发明的技术方案做进一步的说明。

39.实施例1

40.如图2所示,一种光电隔离的高频数字锁相放大器,包括信号处理模块1、信号传输介质接口2、信号输入通道模块3;所述信号处理模块1通过信号传输介质接口2与信号输入通道模块3相连接,待测信号和参考信号从信号输入通道模块3输入;

41.信号处理模块1包括相敏检测模块11、第一数字逻辑器件12、光接收模块13、数字正弦发生器14、数字锁相环15、第一时钟管理芯片16、低噪声晶振17和微处理器18;光接收模块13、第一数字逻辑器件12和相敏检测模块11顺次连接,微处理器18、数字锁相环15、数字正弦发生器14和相敏检测模块11顺次连接;相敏检测模块11还直接连接到微处理器18上,第一数字逻辑器件12还分别与数字锁相环15和第一时钟管理芯片16相连,第一时钟管

理芯片16还与微处理器18和低噪声晶振17连接;

42.信号传输介质接口2包括光纤21、第一电连接器22和第二电连接器23;光纤21连接到光接收模块13上,第一电连接器22与第一时钟管理芯片16连接,第二电连接器23与微处理器18连接;

43.信号输入通道模块3包括光发射模块31、第二数字逻辑器件32、模数转换器33、第一隔离器34、第二时钟管理芯片35、线性光耦36、第二隔离器37、低通滤波器38和低噪声放大电路39;低噪声放大电路39、低通滤波器38、线性光耦36、模数转换器33、第二数字逻辑器件32和光发射模块31顺次连接,第一隔离器34、第二时钟管理芯片35和模数转换器33顺次连接,第二隔离器37、第二时钟管理芯片35和第二数字逻辑器件32顺次连接,第二隔离器37还与模数转换器33连接;待测信号和参考信号从低噪声放大电路39输入;

44.光发射模块31还与光纤21连接,第一隔离器34还与第一电连接器22连接,第二隔离器37还与第二电连接器23连接。

45.实施例2

46.如图3所示,一种光电隔离的高频数字锁相放大器,包括一个信号处理模块1、两个信号传输介质接口2、两个信号输入通道模块3,所述的信号处理模块1通过两个信号传输介质接口2,分别与两个信号输入通道模块3相连接;信号输入通道模块3分别连接待测信号输入和参考信号输入;

47.信号处理模块1包括相敏检测模块11、两个第一数字逻辑器件12、两个光接收模块13、数字正弦发生器14、数字锁相环15、第一时钟管理芯片16、低噪声晶振17和微处理器18;

48.两个光接收模块13分别连接至两个信号传输介质接口2内的光纤21,接收串行数据流并将光信号转换为电信号后,再分别连接至两个第一数字逻辑器件12;

49.两个第一数字逻辑器12件将来自两个光接收模块13的电信号进行解码和串并转换后得到两个输入通道数字信号,然后同时连接至相敏检测模块11和数字锁相环15;

50.数字锁相环15选择参考输入通道数字信号作为输入,进行锁相后连接至数字正弦发生器14控制相位和频率;

51.数字正弦发生器14根据来自数字锁相环15的控制信号产生一个数字正弦波输入相敏检测模块11;

52.相敏检测模块11选择待测输入通道数字信号作为输入,并将其和来自数字正弦发生器14的数字正弦波输入进行相乘并滤波,然后连接至微处理器18;

53.分别记待测输入通道数字信号和参考输入信号为si=aisin(ω0t θ)和sr=arsin(ω0t φ),相敏检测模块11输出和和微处理器根据x和y可以计算出待测幅值和相位差

54.低噪声晶振17产生一低噪声的周期信号作为电路系统的时钟源,连接至第一时钟管理芯片16;

55.第一时钟管理芯片16产生两个传输时钟信号分别连接至两个信号传输介质接口2内的第一连接器22,同时连接至第一逻辑器件12和微处理器18作为逻辑时钟输入;

56.微处理器18分别和相敏检测模块11、数字锁相环15、第一时钟管理芯片16和两个信号传输介质接口2内的第二连接器23相连,传输控制信号;

57.相敏检测模块11、第一数字逻辑器件12、数字正弦发生器14、数字锁相环15和微处理器18可以在含有数字逻辑器件和微处理器的soc芯片上实现。

58.两个信号传输介质接口2内分别包括光纤21、第一电连接器22、第二电连接器23,用以连接信号处理模块1和两个信号输入通道模块3;

59.第一电连接器22和第二电连接器23可由带屏蔽的网线和排线实现,以实现传输时钟信号和控制信号的低失真传输。

60.两个信号输入通道模块3包括光发射模块31、第二数字逻辑器件32、模数转换器33、第一隔离器34、第二时钟管理芯片35、线性光耦36、第二隔离器37、低通滤波器38、低噪声放大电路39;

61.低噪声放大电路39接收外部信号输入,对其放大并经过低通滤波器38滤波后得到输入通道模拟信号,连接至线性光耦36;

62.线性光耦36对输入通道模拟信号进行模拟量的隔离传输后连接至模数转换器33;

63.模数转换器33将来自线性光耦36的信号转换成输入通道数字信号,并通过第二数字逻辑器件32进行编码和并串转换后,再经过光发射模块31将电信号转换为光信号,连接至对应的信号传输介质接口2内的光纤21;

64.第一隔离器34连接至对应的信号传输介质接口2内的第一连接器22,将传输时钟信号进行电气隔离转换后连接至第二时钟管理芯片35;

65.第二时钟管理芯片35分别连接至第二数字逻辑器件32和模数转换器33作为高速驱动时钟;

66.第二隔离器37连接至对应的信号传输介质接口2内的第二连接器23,将来自微处理器18的控制信号进行电气隔离转换后连接至第二时钟管理芯片35和模数转换器33。

67.如图4所示,低噪声晶振17产生一25mhz低噪声低抖动的周期信号作为系统的时钟源给到第一时钟管理芯片16;第一时钟管理芯片16产生100mhz和250mhz分别给到微处理器18和第一数字逻辑器件12,并产生一25mhz通过第一电连接器22和第一隔离器34给到第二时钟管理芯片35;第二时钟管理芯片35产生250mhz时钟给到第二数字逻辑器件32和模数转换器33,并可以调整输出相位使得第一数字逻辑器件12和第二数字逻辑器件32时钟同步。

68.如图5所示,信号处理模块1通过两个信号传输介质接口2分别连接两个信号输入通道模块3;由于系统实现了信号处理模块1和信号输入通道模块3之间的光电隔离,在电气层面上做到独立隔离,并且能在空间位置上实现远距离的分离,在本实施例中信号处理模块1和两个信号输入通道模块3之间的距离可超过1米达到数米量级;由光电隔离实现的电气隔离和空间分离,使得信号处理模块1和两个信号输入通道模块3之间没有通过共用电源轨耦合的噪声干扰,并大幅减少通过近距离空间辐射导致的噪声干扰,使得数字锁相放大器系统的测量精度提高。

69.实施例3

70.如图2所示,一种光电隔离的高频数字锁相放大器,包括信号处理模块1、信号传输介质接口2、信号输入通道模块3;所述信号处理模块1通过信号传输介质接口2与信号输入通道模块3相连接,待测信号和参考信号从信号输入通道模块3输入;

71.信号处理模块1包括相敏检测模块11、第一数字逻辑器件12、光接收模块13、数字正弦发生器14、数字锁相环15、第一时钟管理芯片16、低噪声晶振17和微处理器18;光接收

模块13、第一数字逻辑器件12和相敏检测模块11顺次连接,微处理器18、数字锁相环15、数字正弦发生器14和相敏检测模块11顺次连接;相敏检测模块11还直接连接到微处理器18上,第一数字逻辑器件12还分别与数字锁相环15和第一时钟管理芯片16相连,第一时钟管理芯片16还与微处理器18和低噪声晶振17连接;

72.信号传输介质接口2包括光纤21、第一电连接器22和第二电连接器23;光纤21连接到光接收模块13上,第一电连接器22与第一时钟管理芯片16连接,第二电连接器23与微处理器18连接;

73.信号输入通道模块3包括光发射模块31、第二数字逻辑器件32、模数转换器33、第一隔离器34、第二时钟管理芯片35、线性光耦36、第二隔离器37、低通滤波器38和低噪声放大电路39;低噪声放大电路39、低通滤波器38、线性光耦36、模数转换器33、第二数字逻辑器件32和光发射模块31顺次连接,第一隔离器34、第二时钟管理芯片35和模数转换器33顺次连接,第二隔离器37、第二时钟管理芯片35和第二数字逻辑器件32顺次连接,第二隔离器37还与模数转换器33连接;待测信号和参考信号从低噪声放大电路39输入;

74.光发射模块31还与光纤21连接,第一隔离器34还与第一电连接器22连接,第二隔离器37还与第二电连接器23连接。

75.第一数字逻辑器件12将来自光接收模块13的电信号进行解码和串并转换后得到参考输入通道数字信号和待测输入通道数字信号,数字锁相环15选择参考输入通道数字信号作为输入,进行锁相后连接至数字正弦发生器14控制相位和频率。

76.数字正弦发生器14根据来自数字锁相环15的控制信号产生一个数字正弦波输入相敏检测模块11。

77.相敏检测模块11选择待测输入通道数字信号作为输入,并将其和来自数字正弦发生器14的数字正弦波输入进行相乘并滤波,然后连接至微处理器18。

78.分别记待测输入通道数字信号和参考输入信号为si=aisin(ω0t θ)和sr=arsin(ω0t φ),相敏检测模块11输出和和微处理器18根据x和y计算出待测幅值和相位差

79.低噪声晶振17产生一低噪声的周期信号作为电路系统的时钟源,连接至第一时钟管理芯片16;

80.第一时钟管理芯片16产生传输时钟信号分别连接至信号传输介质接口2内的第一连接器22,同时连接至第一逻辑器件12和微处理器18作为逻辑时钟输入。

81.低噪声放大电路39接收外部信号输入,对其放大并经过低通滤波器38滤波后得到输入通道模拟信号,连接至线性光耦36;

82.线性光耦36对输入通道模拟信号进行模拟量的隔离传输后连接至模数转换器33;

83.模数转换器33将来自线性光耦36的信号转换成输入通道数字信号,并通过第二数字逻辑器件32进行编码和并串转换后,再经过光发射模块31将电信号转换为光信号,连接至对应的信号传输介质接口2内的光纤21。

84.第一隔离器34连接至对应的信号传输介质接口2内的第一连接器22,将传输时钟信号进行电气隔离转换后连接至第二时钟管理芯片35;

85.第二时钟管理芯片35分别连接至第二数字逻辑器件32和模数转换器33作为高速

驱动时钟;

86.第二隔离器37连接至对应的信号传输介质接口2内的第二连接器23,将来自微处理器18的控制信号进行电气隔离转换后连接至第二时钟管理芯片35和模数转换器33。

87.第一电连接器22和第二电连接器23是带屏蔽的网线和排线,以实现传输时钟信号和控制信号的低失真传输。

88.低噪声晶振17产生一25mhz低噪声低抖动的周期信号作为系统的时钟源给到第一时钟管理芯片16;第一时钟管理芯片16产生100mhz和250mhz分别给到微处理器18和第一数字逻辑器件12,并产生一25mhz通过第一电连接器22和第一隔离器34给到第二时钟管理芯片35;第二时钟管理芯片35产生250mhz时钟给到第二数字逻辑器件32和模数转换器33,并可以调整输出相位使得第一数字逻辑器件12和第二数字逻辑器件32时钟同步。

89.相同或相似的标号对应相同或相似的部件;

90.附图中描述位置关系的用于仅用于示例性说明,不能理解为对本专利的限制;

91.显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包括在本发明权利要求的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。