半导体装置及其制造方法

1.[关联申请]

[0002]

本技术采用日本专利申请2021-32632号(申请日:2021年3月2日)作为基础申请的优先权。本技术通过参考该基础申请而包括基础申请的全部内容。

技术领域

[0003]

本发明的实施方式涉及半导体装置及其制造方法。

背景技术:

[0004]

在半导体装置的制造方法中,除了蚀刻、沉积工序等的形成半导体装置的工序以外,还包括观察形成有用于布线、通孔、接触件等的槽、孔的层间绝缘膜、或者观察形成有布线等的布线层的观察工序。在观察工序中,例如使用光学显微镜或扫描型电子显微镜(sem),确认意料外的颗粒的飞散的有无等制造上的问题的有无。在发现了成为制造上的问题的部位的情况下,其位置信息成为为了改善成品率等而重要的信息。然而,在基板上重复形成相同的图案的情况下,有时难以判断通过观察而取得的图像与设计数据上的哪个部分对应。

技术实现要素:

[0005]

一个实施方式提供能够容易地将观察图像上的位置与设计数据上的位置建立对应的半导体装置及其制造方法。

[0006]

根据一个实施方式,提供一种半导体装置,包含:电路图案,包含至少在一个方向上重复配置的多个单位图案;以及判别图案,设置于该电路图案内,能够进行单位图案的判别。

附图说明

[0007]

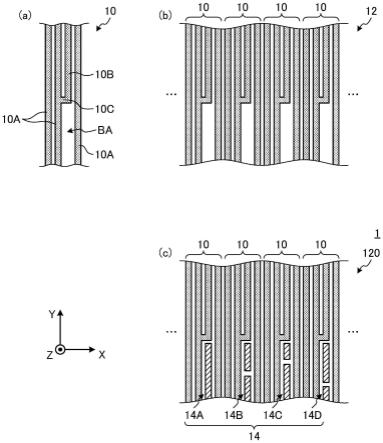

图1是说明实施方式的半导体装置中设置的、重复排列单位图案而形成的电路图案的图。

[0008]

图2是说明本实施方式的半导体装置的电路图案的效果的图。

[0009]

图3是示意性地表示变形例的电路图案的俯视图。

[0010]

图4是示意性地表示其他变形例的电路图案的俯视图。

[0011]

图5是示意性地表示其他变形例的电路图案的俯视图。

[0012]

图6是示意性地表示其他变形例的电路图案的俯视图。

[0013]

图7是示意性地表示其他变形例的电路图案的俯视图。

[0014]

图8是说明另一变形例的电路图案的说明图。

[0015]

图9是示意性地表示nand存储器的结构的框图。

[0016]

图10是示意性地表示dram存储器的结构的框图。

[0017]

图11是示意性地表示摄像元件的结构的框图。

[0018]

附图标记说明

[0019]1…

半导体装置,10、100、101、102

…

单位图案,114、120、121、130、131、150、161、170

…

电路图案,14、16、140、160

…

判别图案,c、c1、c2、c3

…

连接部,opl、opl1~opl6、opu、opu1~opu6、opm

…

开口,dp、dp1、dp2、dp3

…

截断部。

具体实施方式

[0020]

以下,参照附图对本发明的非限定性的例示的实施方式进行说明。在全部附图中,对相同或对应的部件或零部件标注相同或对应的参照附图标记,并省略重复的说明。另外,附图不是以表示部件或零部件间的相对比为目的,因此,具体的厚度、尺寸可以参照以下的非限定性的实施方式,由本领域技术人员决定。

[0021]

参照图1,对实施方式的半导体装置所具有的电路图案的一例进行说明。本实施方式中的半导体装置没有限定,例如可以是半导体存储装置。另外,作为电路图案,例示了在一个方向上重复排列具有相同形状的多个单位图案而形成的电路图案。本实施方式中的电路图案在半导体装置的制造工序中取得观察图像时,将在该观察图像中出现的图形作为对象。因此,假定观察图像是从半导体基板的上表面取得的图像。另外,在电路图上与元件连接的布线的形状、在电路图上不与元件连接的布线的形状都出现在观察图像中,因此成为电路图案的对象。另外,如后所述,电路图案不限于布线,也可以是在观察图像中出现的槽或孔。关于形成这样的电路图案的电路、半导体装置的例子,在后面进行说明。

[0022]

图1的(a)是示意性地表示单位图案的俯视图,图1的(b)是示意性地表示由多个单位图案形成的电路图案的俯视图,图1的(c)是示意性地表示本实施方式的半导体装置1所具有的电路图案的俯视图。单位图案、电路图案以及判别图案例如包含由金属、导电性的多晶硅等导电材料在绝缘膜上形成的布线。换言之,单位图案、电路图案及辨别图案可以是形成于半导体装置1中的相同层的布线。

[0023]

如图1的(b)所示,图1的(a)所示的单位图案10在x方向上重复排列而形成电路图案12。单位图案10可以是相对于作为半导体存储装置的本实施方式的半导体装置1的例如一个列(或行)而形成的布线图案。在图示的例子中,单位图案10包括在y方向上延伸的多个线10a、同样在y方向上延伸但比线10a短的线10b、以及将线10b与线10a连接的连接部10c。单位图案10例如相对于一个列(或行)而形成,并重复设置列(或行)。重复配置单位图案10,形成电路图案12。

[0024]

本实施方式中的电路图案120如图1的(c)所示,除了电路图案12之外还具有判别图案14。在图示的例子中,判别图案14具有4种判别图形14a、14b、14c、14d。判别图形14a是在y方向上连续地延伸的线,判别图形14b~14d是y方向的长度不同的多个线的组合。这样,判别图形14a~14d具有互不相同的形状,因此能够将各自进行区分。另外,判别图形14a~14d依次设置于4个单位图案10各自的空白区域ba(图1的(a)),因此,以该顺序沿着x方向排列。在此,空白区域ba是不形成线等电路要素,而与构成电路图案的布线层的基底层或构成电路图案的布线层同层的绝缘膜在比较宽的范围内露出的区域。另外,虽然省略了图示,但单位图案10也重复配置于图中的左侧及右侧,相对于这些单位图案10,判别图形14a~14d也沿着x方向以该顺序周期性地排列。

[0025]

电路图案120预先根据设计数据生成,各单位图案10以及判别图形14a~14d的位

置能够在设计数据上以规定的坐标基准点(例如对准标记)为原点的坐标来确定。另外,电路图案120可以通过使用了基于设计数据而制作的光掩模的光刻工序,例如在绝缘膜上形成沟槽等、利用金属等导电材料填埋沟槽等并通过化学机械研磨(cmp)法将绝缘膜上的导电材料去除的镶嵌法(damascene)而形成。另外,也可以使用通过金属或导电性的多晶硅等导电材料的薄膜的沉积工序、使用了基于设计数据而制作的光掩模的光刻工序和蚀刻工序而形成电路图案120的反应性离子蚀刻(rie)法。

[0026]

另外,电路图案12内的单位图案10,分别包括判别图形14a~14d,由此不具有相同的形状。因此,也成为重复排列相同形状的单位图案而成的电路图案并不存在的情况。因此,在此,重复排列相同形状的单位图案而成的电路图案,是指如果没有能够进行单位图案的判别的判别图案,则无法通过表面观察手段个别地判别单位图案的图案。

[0027]

另外,电路图案12内的单位图案10的形状只要在制造工艺的误差的范围内相同即可。在附图中,例如判别图形14a~14d具有直角的角部,但在现实中,根据制造工艺(蚀刻),也可以具有带有圆角的角部。

[0028]

接着,参照图2,对由电路图案120起到的效果进行说明。图2是说明本实施方式的半导体装置1的电路图案120的效果的图。具体而言,图2的(a)是示意性地表示具有作为比较例的电路图案12的半导体基板的俯视图,图2的(b)是示意性地表示具有电路图案120的半导体基板的俯视图。在图2的(a)以及(b)中,示出了通过作为表面观察手段的扫描型电子显微镜(sem)对电路图案12以及120进行摄像时的摄像范围(视野)ir。即,取得摄像范围ir内的形状作为一张图像数据。

[0029]

在使用sem以所谓的die-to-die方式观察电路图案12的结果是检测出微粒pcl的情况下,如图2的(a)所示,在sem的图像数据中显示出具有微粒pcl的电路图案12的图像。此时,虽然微粒pcl实际上位于位置pt,但有时也通过die-to-die方式来表示“微粒pcl在位置pf”这样的坐标信息。这样的偏移例如可能由于伴随着在sem内对作为被测定对象的基板进行保持的工作台的移动而产生的误差等而产生。在该情况下,即使想要确定微粒pcl实际存在的位置pt在设计数据上的位置,由于在电路图案12中单位图案10重复,因此判别在哪个单位图案10的附近存在位置pt并不容易。

[0030]

但是,根据本实施方式,如图2的(b)所示,电路图案120具有判别图案14,判别图形14a~14d各自的形状不同。因此,根据sem的图像数据,来掌握在微粒pcl的位置pt的附近存在判别图形14b这一情况。因此,即使通过die-to-die方式示出的微粒的位置pf的坐标与实际上微粒pcl所在的位置pt的设计数据上的坐标偏移,也能够基于判别图形14b的坐标进行校正。这样,能够确定微粒pcl在设计数据上的位置。即,由于存在判别图案14,因此通过sem取得的图像数据与设计数据的匹配变得容易,能够在设计数据上求出微粒pcl的位置。

[0031]

另外,判别图形的种类数也可以不与单位图案10的重复数相等。例如,也可以不对单位图案10的每一个赋予判别图形,而是隔一个、隔两个或者以两个以上的间隔地赋予判别图形。由此,能够减少应该准备的判别图形的种类数,进而能够使判别图形各自的形状明确地不同。

[0032]

另外,应该准备的判别图形的种类数,可以基于在规定的摄像范围、摄像倍率下用sem图像的整体所捕捉到的单位图案的数量来决定。例如,在x方向上重复配置的各单位图案的宽度(重复间距)为400nm、sem的摄像范围ir的宽度在基板上相当于9μm的情况下,在

sem图像中能够捕捉22个单位图案10。此时,可以准备具有不同形状的22种判别图形,并分别分配给22个单位图案10。在该情况下,具有不同形状的22种判别图形周期性地排列,全部的单位图案10都具有判别图形。另外,也可以准备具有不同形状的11种判别图形并每隔一个单位图案10进行分配,每隔一个地分配了判别图形的22个单位图案10周期性地排列。另外,也可以准备具有不同形状的例如8种不同的判别图形并每隔两个单位图案10进行分配,每隔两个地分配了判别图形的22个单位图案10周期性地排列。进而,也可以每隔三个以上的单位图案10地设置判别图形。

[0033]

另外,应该准备的判别图形的种类数,可以考虑通过die-to-die方式可能产生的位置误差(在上述例子中来说,为位置pt与位置pf之差)来决定。通过die-to-die方式可能产生的位置误差例如被认为是0.5μm~2μm,但在假设为1.5μm,单位图案10的宽度为400nm的情况下,只要准备3种判别图形即可。由此,能够知道通过die-to-die方式示出的位置pf的附近的判别图形的位置,因此能够确定实际的位置pt。同样地,在位置误差为1.5μm、且重复间距为80nm的情况下,只要准备13种判别图形即可,在重复间距为40nm的情况下,只要准备25种判别图形即可。另外,在位置误差为1.5μm的情况下,如果按照比位置误差小、且比位置误差的一半大的、例如每1μm配置判别图形,则能够对通过die-to-die方式示出的微粒pcl的位置pf进行校正,并确定实际的位置pt。

[0034]

另外,sem的摄像倍率被认为根据电路图案12的宽度、线宽、间距而不同。如果sem的摄像倍率不同,则摄像范围ir、可能产生的位置误差、在摄像范围ir内观察到的单位图案10的数量不同,因此,在判别图形的种类、配置的决定中,也可以考虑摄像倍率、析像度(分辨率)。

[0035]

(变形例)

[0036]

接着,参照图3对电路图案的变形例进行说明。图3是示意性地表示变形例的电路图案的俯视图。

[0037]

参照图3的(a),电路图案121具有在x方向上重复配置的单位图案10和判别图案16。判别图案16具有判别图形16a、16b、16c、16d,这些判别图形16a~16d与单位图案10对应地设置。判别图形16a~16d分别具有长度不同的线形状,在单位图案10的空白区域ba(参照图1的(a))中,与单位图案10的线10a、10b分离地配置。由于长度不同,因此能够区分判别图形16a~16d,由此,能够进行分别配置有判别图形16a~16d的单位图案10的判别。

[0038]

参照图3的(b),电路图案130具有在x方向上重复配置的单位图案10和判别图案160。判别图案160具有判别图形160a、160b、160c、160d,这些判别图形160a~160d与单位图案10对应地设置。判别图形160a~160d与图3的(a)所示的判别图形16a~16d同样地,分别具有长度不同的线形状,并配置于单位图案10的空白区域ba(参照图1的(a))。但是,判别图形160a~160d在与单位图案10的线10b连接这一点上与判别图形16a~16d不同。这样,即使与单位图案10连接,也能够根据长度的不同来区分判别图形160a~160d,由此,也能够进行分别配置有判别图形160a~160d的单位图案10的判别。此外,若对作为布线图案的单位图案10连接判别图形160a~160d,则例如寄生电容等电路常数有偏差,进而在半导体装置的动作中也有可能产生偏差。因此,在由电路常数等的偏差造成的影响少的情况下,优选使用判别图形160a~160d。

[0039]

如图3的(c)所示,电路图案131具有在x方向上重复配置的单位图案10和判别图案

140。判别图案140具有判别图形140a、140b、140c、140d,它们分别具有与图1的(c)所示的判别图形14a~14d相同的形状。然而,判别图形14a~14d与单位图案10分离,与此相对,判别图形140a~140d与单位图案10连接。即使在该情况下,判别图形140a~140d也具有不同的形状,因此能够进行区分,因此,被分配了判别图形140a~140d的单位图案10也能够进行判别。另外,判别图形140a~140d与图3的(b)所示的判别图形160a~160d同样,在由电路常数等的偏差造成的影响少的情况下是有用的。

[0040]

接着,参照图4至图6,对电路图案的其他变形例进行说明。在此前说明的电路图案120、121、130、131中,对重复配置的单位图案10分别赋予与它们不同的判别图案14、16、140、160,与此相对,在这以后的变形例中,单位图案10变形而形成判别图案。

[0041]

如图4的(a)所示,单位图案100具有在y方向上延伸的多个线100a和具有比线100a宽的宽度(x方向的长度)的线100b。进而,在单位图案100设置有连接部c,通过连接部c连接有2个线100a。即,这2个线100a相互电导通。若这样的单位图案100单纯地重复排列,则形成图4的(b)所示的电路图案110。如图示那样,在电路图案110中,如以虚线l1以及l2所示,各单位图案100的连接部c在y方向上配置于相同的位置。

[0042]

另一方面,在变形例的电路图案114中,如图4的(c)所示,设置有连接部c、c1、c2、c3。连接部c1、c2虽然具有与连接部c大致相同的形状,但是根据该图中的与虚线l1以及l2的相对位置可知,相对于连接部c在y方向上分别配置于不同的位置。另外,连接部c3在y方向上比连接部c、c1、c2长。进而,在图中的右端的单位图案100中,形成有2个连接部c3。电路图案114中的连接部c~c3在位置和/或形状这一点上不同,因此能够相互区分。因此,这些连接部c~c3能够具有与上述判别图形14a等相同的功能。换言之,通过连接部c~c3构成判别图案。即,通过这样变更单位图案100的一部分(在图示的例子中为连接部)的位置、形状,也能够得到判别图案。此外,不言而喻,这样的变更应该以不影响半导体装置的特性的方式进行。

[0043]

接着,参照图5的(a),单位图案101具有沿y方向延伸的多个线101a和具有比线100a宽的宽度的线101b。在线101b上形成有2个开口opl以及opu。如果这样的单位图案101单纯地重复排列,则形成图5的(b)所示的电路图案111。如图示那样,在电路图案111中,如虚线l3以及l4所示,各单位图案101的2个开口opl以及opu在y方向上分别配置于相同的位置。

[0044]

另一方面,在变形例的电路图案150中,在一个单位图案101(图中的左端)中配置有开口opl以及opu,另一方面,在其他的单位图案101中配置有不同的开口。具体而言,在该图中的左起第二个单位图案101的线101b中配置有开口opl1以及opu1,在从左起第三个单位图案101的线101b中配置有开口opl2以及opu2,在从左起第四个单位图案101的线101b中配置有开口opl3以及opu3,在从左起第五个单位图案101的线101b中配置有开口opl4以及opu4,在从左起第六个单位图案101的线101b中配置有开口opl5以及opu5,在最右侧的单位图案101的线101b中配置有开口opl6、开口opm以及opu6。

[0045]

根据虚线l3可知,相对于开口opu,开口opu1和开口opu2在y方向上配置于相同的位置,另一方面,相对于开口opl,开口opl1和开口opl2向图中的下侧偏移而配置。并且,开口opl2与开口opl1相比向下侧更大地偏移。另外,根据虚线l4可知,相对于开口opl,开口opl3和开口opl4在y方向上配置于相同的位置,另一方面,相对于开口opu,开口opu3和开口

opu4向图中的上侧偏移地配置。而且,开口opu4与开口opu3相比向上侧更大地偏移。根据以上那样的配置的不同,能够分别区分开口opl与开口opu的组合、开口oplx与开口opux(x为1~4的整数)的组合。

[0046]

另外,开口opu5虽然其下端的位置与开口opu的下端的位置在y方向上相同,但上端的位置与开口opu的上端的位置相比向图中的下侧偏移。即,开口opu5在y方向上比开口opu短。由此也能够针对上述开口的组合,区分开口opl5和开口opu5的组合。开口opl6、开口opm以及开口opu6的组合也能够与其他组合相区分。即,由于形状和/或位置的不同,这些开口的组合能够具有与上述判别图形14a等同样的功能,通过它们来构成判别图案。

[0047]

另外,参照图6的(a),单位图案102具有在y方向上延伸的多个线102a和2个线102b。线102b隔着截断部dp而对置,且都在y方向上延伸。如果这样的单位图案102单纯地重复排列,则形成图6的(b)所示的电路图案112。如图示那样,在电路图案112中,如虚线l5以及l6所示,各单位图案102的截断部dp在y方向上配置于相同的位置。

[0048]

另一方面,在变形例的电路图案161中,如图6的(c)所示,设置有截断部dp、dp1、dp2、dp3、dp4。截断部dp1、dp2虽然沿着y方向具有与截断部dp大致相同的长度,但是根据与该图中的虚线l5以及l6的相对位置可知,相对于截断部dp在y方向上分别配置于不同的位置。另外,截断部dp3与截断部dp、dp1、dp2相比,在y方向上较长。进而,在图中的右端的单位图案100中,形成有2个截断部dp4。电路图案161中的截断部dp~dp4在位置和/或形状这一点上不同,因此能够相互区分。因此,这些截断部dp~dp4能够具有与上述的判别图形14a等相同的功能,通过截断部dp~dp4构成判别图案。

[0049]

此外,此前着眼于单位图案在x方向上的重复配置,但也存在在x方向上重复配置在y方向上较长地延伸的单位图案的情况。在这样的情况下,可以如图7所示那样、将一连串的判别图案在y方向上隔开规定的间隔地配置。图7是示意性地表示图4的(a)所示的单位图案100在y方向上比较长地延伸的情况下的电路图案的俯视图。如图示那样,在电路图案170上设置有以大致沿着在x方向上延伸的虚线l7及l8的方式分别周期性地排列的2列连接部c、c1、c2、c3。在此,2个列的间隔(虚线l7与l8的间隔)例如可以考虑基于sem的摄像范围ir、基于die-to-die方式的位置误差来决定。

[0050]

(其他变形例)

[0051]

此前,对重复配置由布线形成的单位图案的情况进行了说明,但不限于此,在重复配置由通孔、贯通接触件形成的单位图案的情况下也能够应用本实施方式。以下,参照图8,例如以通过设置于绝缘膜的通孔、贯通接触件所用的孔来形成单位图案并将其重复配置的情况为例,对进另一变形例进行说明。图8是说明另一变形例的电路图案的说明图。

[0052]

参照图8的(a),形成包括布线104a和宽度比布线104a宽的布线104b在内的布线图案104。布线104a、104b例如可以由cu等金属或导电性的多晶硅形成。如图8的(a)的沿着a-a线的剖视图即图8的(b)所示,布线104b(布线104a也同样)形成于绝缘膜51上,并以覆盖它们的方式形成有绝缘膜53。即,布线104a、104b是下层布线,图8的(a)表示根据绝缘膜53的材料、厚度而通过绝缘膜53能够视觉辨认其形状的布线104a、104b。

[0053]

如图8的(a)及图8的(b)所示,形成有贯通绝缘膜53而到达布线104b的多个孔h,布线104b在多个孔h的底面露出。这些孔h例如可通过光刻工序及蚀刻工序而形成。另外,之后,在孔h中填埋例如cu等金属,从而形成与布线104b连接的通孔(或接触件)。

[0054]

如图8的(a)所示,多个孔h被分为2个孔组gh1、gh2。孔组gh1具有5个孔h,它们配置成大致五边形。详细而言,5个孔h中的3个配置于底边沿x方向延伸的等腰三角形的顶点。在相对于在该底边的两端的顶点配置的2个孔h而言在y方向上错开的位置配置有剩余的2个。孔组gh2也具有5个孔h,它们也配置成与孔组gh1的孔h同样的大致五边形。但是,在图示的例子中,孔组gh1的孔h和孔组gh2的孔h相对于x轴对称地配置。

[0055]

如果将这样的一对孔组gh1、gh2作为单位图案gh(图8的(a)),将单位图案gh与下层的布线图案104一起在x方向上重复配置,则如图8的(c)所示,形成电路图案141。在该情况下,由于重复排列有与孔h同样地排列的单位图案gh,因此与参照图2说明的电路图案12同样地,即使在绝缘膜53上观察到微粒等缺陷,也不容易在设计数据上确定该位置。

[0056]

此外,在观察绝缘膜53上的微粒等缺陷时,根据绝缘膜53的材料、厚度,通过绝缘膜53,布线104a、104b也能够被识别到,但由于包含它们的布线图案104也重复排列,所以从布线104a、104b的位置确定微粒等缺陷在设计数据上的位置也还是不容易。另外,在绝缘膜53较厚的情况下等,无法识别布线104a、104b的形状。

[0057]

另一方面,参照图8的(d),在本变形例的电路图案151中,代替图8的(c)等中的孔组gh2,孔组gh21、gh22、gh23、gh24、gh25以与孔组gh1成对的方式设置。孔组gh21~gh25与孔组gh2同样地具有5个孔h,但其配置不同。详细而言,在孔组gh21~gh25中,孔h不是大致五边形,在x-y平面中的2行3列的矩阵的6处的配置位置中的除了1处以外的5处配置有孔h。而且,该1个部位的位置在孔组gh21~gh25中分别不同。更详细而言,未配置孔h的该1个部位在各个孔组gh21、gh22、gh23、gh24、gh25中,相当于1行3列、1行2列、1行1列、2行1列、2行2列的位置。根据这样的配置的不同,孔组gh21~gh25能够具有与上述的判别图形14a等同样的功能,能够说通过单位图案gh的变形而构成了判别图案。

[0058]

另外,如上所述,布线104a、104b通过绝缘膜53清楚地识别并不容易,因此即使对布线104a、104b分配了规定的判别图案,根据该判别图案来确定绝缘膜53上的缺陷在设计数据上的位置也还是不容易。与此相对,在孔h的情况下,在其底面露出的布线104a、104b能够通过sem等明确地识别,因此缺陷在设计数据上的位置的确定变得容易。

[0059]

另外,即使如各孔组gh21~gh25那样配置分别不同,由于孔h的数量相同,因此用金属填埋孔h而形成的通孔等与布线104b之间的电阻在任意的配置中都能够大致相同。另外,虽然例示了分别具有5个孔h的孔组gh1、gh2,但孔h的数量并不限定于5个,也可以考虑sem等观察装置中的摄像范围、摄像倍率、基于die-to-die方式的位置误差来适当决定。进而,也可以代替图8的(c)所示的孔组gh2而使用孔h的配置分别不同的孔组gh21~gh25,代替孔组gh1而使用孔h的配置分别不同的多个孔组。进而,在图8的(d)中,例如也可以将孔组gh21和孔组gh1在y方向(图中的上下方向)上对调,将孔组gh24和孔组gh1在y方向上对调。即,也可以在图8的(c)中的单位图案gh中包含的孔组gh1和孔组gh2中的任一方(或双方)中改变孔h的配置。

[0060]

另外,对在绝缘膜53上形成了孔h之后进行缺陷等的观察(检查)的情况进行了说明,但也可以在向孔h中填埋金属(例如cu)并形成通孔等之后进行缺陷等的观察。即使在该情况下,也能够如上述那样、基于孔组gh21~gh25,在设计数据上确定基板上的缺陷位置。另外,如上述那样,电路图案120等是沟槽等用金属等导电材料填埋而形成的,但也可以在形成了填埋导电材料前的沟槽(槽)等之后,观察缺陷等。即,观察对象的电路图案不限于布

线、通孔等,也可以是孔、槽。另外,在图8中,使用孔的底面为与层间绝缘膜不同的材料的情况进行了说明。然而,sem图像在表面的凹凸观察方面优异,因此即使在孔、槽的底面与其他区域的材料相同的情况下,也能够在sem图像上识别孔、孔的位置。

[0061]

接着,对设置有由具有相同形状的多个单位图案在一个方向上重复排列而形成的电路图案的半导体装置进行说明。图9是示意性地表示nand存储器的结构的框图,图10是示意性地表示dram存储器的结构的框图,图11是示意性地表示摄像元件的结构的框图。

[0062]

参照图9,作为半导体存储装置的nand存储器nm包含核心部cor、输入输出部io以及周边电路per。在核心部cor设置有存储单元阵列mca、行解码器rd及读出放大器sa,在存储单元阵列mca中设置有分别包含多个存储单元的多个块blk(blk0、blk1、blk2、

…

)。详细而言,块blk各自具有多个串单元su(su0、su1、su2、

…

),串单元su具有多个nand串ns,在nand串内,存储单元被串联连接。

[0063]

在存储单元阵列mca中设置有多个字线wl和多个位线bl(在图中,表示了一个字线和一个位线)。多个字线wl沿x方向延伸,与行解码器rd连接。另外,多个字线wl分别共通地连接于对应的块blk中各个串单元su的多个nand串ns中的第n个存储单元。另一方面,多个位线bl在y方向上延伸,与读出放大器sa连接。另外,多个位线bl中的一个位线bl共通地连接于多个块blk间的第m个nand串ns。在多个字线wl与多个位线bl分别交叉的点配置有存储器单元。

[0064]

行解码器rd对从nand存储器nm的外部的规定的控制部接收到的块地址进行解码,选择块blk和该块blk内的字线wl。读出放大器sa在读取数据时,读出从存储单元读取的数据并放大。然后,根据需要将读取数据输出至规定的控制部。另外,在数据的编程时,将从规定的控制部接收到的写入数据转送至存储单元。

[0065]

输入输出部io与规定的控制部之间进行各种命令或数据的收发。输入输出部io例如具有数据输入输出端子dq0~dq7、触发(toggle)信号输入输出端子dqs、/dqs、外部控制端子/cen、cle、ale、/we、re、/re,从外部的控制器接收与这些端子对应的信号。周边电路per包括序列发生器seq、电荷泵chp、寄存器reg及驱动器drv。驱动器drv将数据的程序、读取及擦除(erase)所需的电压供给至行解码器rd、读出放大器sa。该电压被施加于存储单元阵列mca内的各种布线。电荷泵chp对从外部提供的电源电压进行升压,并对驱动器drv供给必要的电压。寄存器reg保持各种信号。例如,保持数据的程序、擦除动作的状态,由此向规定的控制部通知动作是否正常完成。定序器seq控制nand存储器nm整体的动作。

[0066]

在如以上那样的nand存储器nm中,在存储单元阵列mca内,构成存储单元的晶体管、以字线wl、位线bl为主的各种电路要素以同一电路布局周期性地配置。因此,在供各字线wl连接的行解码器rd中,也成为具有相同形状的单位图案通过多个字线wl或其他布线在一个方向上重复排列而形成的电路图案。在供多个位线bl连接的读出放大器sa中也是同样的。上述的电路图案120等能够应用于这样的行解码器rd、读出放大器sa。

[0067]

接着,参照图10,作为半导体存储装置的dram存储器80包含存储单元阵列ma。存储单元阵列ma具有多个字线wl和多个位线bl,在它们的交点配置有存储单元mc。字线wl由行解码器83r选择,位线bl由列解码器83c选择。另外,在dram存储器80中设置有命令地址端子t1、时钟端子t2、数据端子t3以及电源端子t4、t5。时钟信号ck、/ck被输入至时钟端子t2。向电源端子t5供给电源电压,电源电压进一步被供给至内部电压产生电路88。内部电压产生

电路88基于电源电压而产生各种内部电压,并从端子it对各部输出。另外,在图10中,为了便于说明,省略了在dram存储器中设置的刷新(refresh)电路等。

[0068]

从外部向命令地址端子t1输入地址信号以及命令信号。被输入至命令地址端子t1的地址信号经由命令地址输入电路81被供给至地址解码器82a。地址解码器82a将地址信号as供给至行解码器83r或列解码器83c。另一方面,被输入至命令地址端子t1的命令信号经由命令地址输入电路81被供给至命令解码器82c。命令解码器82c通过对所输入的命令信号进行解码而生成各种内部命令信号。内部命令信号中包括激活(active)信号ats和列信号cs。

[0069]

当命令信号是激活命令时,激活信号ats被活化。当激活信号ats被活化时,地址信号as从地址解码器82a被供给至行解码器83r。由此,由该地址信号as所指定的字线wl被选择。在命令信号是读取命令或写入命令的情况下,列信号cs被活化。当列信号cs被活化时,地址信号as从地址解码器82a被供给至列解码器83c。由此,由该地址信号as所指定的位线bl被选择。

[0070]

因此,当被输入激活命令及读取命令时,从由通过地址信号as指定的字线wl及位线bl所确定的存储单元mc读出读取数据。读取数据经由读出放大器84、输入输出电路85及数据端子t3从数据端子t3被输出至外部。另一方面,当被输入激活命令及读取命令、且数据端子t3被输入写入数据时,对由通过地址信号as指定的字线wl及位线bl所确定的存储单元阵列ma,经由数据端子t3、输入输出电路85及读出放大器15供给写入数据,并写入。

[0071]

在如以上那样的dram存储器80中,在存储单元阵列ma内,构成存储单元的晶体管、以字线wl、位线bl为主的各种电路要素以同一电路布局周期性地配置。因此,在供各字线wl连接的行解码器83r中,也成为具有相同形状的单位图案通过多个字线wl或其他布线在一个方向上重复排列而形成的电路图案。在多个位线bl列解码器83c中也是同样的。上述的电路图案120等能够应用于这样的行解码器83r或列解码器83c。

[0072]

接下来,参考图11,图像传感器90具有像素阵列pa和周边电路,并且周边电路包括行扫描电路91、列处理电路92、列扫描电路93、系统控制部94及信号处理部96。

[0073]

像素阵列pa具有多个像素pxl。这些像素pxl在行方向及列方向上配置为2维格子状。在此,行方向是指图中的横向,列方向是指图中的纵向。各像素pxl具有生成并蓄积与接收到的光量相应的电荷的光电变换元件。在各像素pxl的光入射面可以设置规定的滤波器。这样的滤波器例如可以是拜尔滤波器。

[0074]

在像素阵列pa中,像素驱动线pdl被共通地连接到在行方向上排列的像素pxl,垂直信号线vsl被共通地连接到在列方向上排列的像素pxl。像素驱动线pdl的一端部与行扫描电路91连接。行扫描电路91生成用于进行来自像素的信号读出驱动的驱动信号,通过像素驱动线pdl,同时或者以行单位等对像素阵列pa的全部像素pdl进行驱动。

[0075]

从由行扫描电路91驱动的像素pdl输出的信号按在行方向上排列的每个像素pds中通过各个垂直信号线vsl被输入至列处理电路92。列处理电路92能够对通过垂直信号线vsl输入的信号进行规定的信号处理而生成像素信号,并且暂时保持该像素信号。例如,列处理电路92进行噪声去除处理、模拟-数字变换(ad变换)处理等。通过ad变换所获得的数字信号被输出至信号处理部96。列扫描电路93依次选择与列处理电路92的像素列对应的读出电路。通过该列扫描电路93的选择扫描,在列处理电路92中按每个像素电路依次输出被信

号处理后的像素信号。

[0076]

系统控制部94经由外部的控制器接收系统时钟sysclk信号等。系统控制部94包括定时发生器等,基于由此生成的各种定时信号来驱动行扫描电路91、列处理电路92及列扫描电路93等。信号处理部96至少具有运算处理功能,对从列处理电路92输出的像素信号进行运算处理等各种信号处理。另外,从信号处理部96输出的数字信号被输出至图像处理部,在那里进行规定的处理,生成在规定的显示器上显示图像所用的图像信号。

[0077]

在如以上那样构成的图像传感器90中,在像素阵列pa内,构成光电变换元件的例如光电二极管、以像素驱动线pdl、垂直信号线vsl为主的各种电路要素以同一电路布局周期性地配置。因此,在供各像素驱动线pdl连接的行扫描电路91中,也成为具有相同形状的单位图案通过多个像素驱动线pdl或其他布线在一个方向上重复排列而形成的电路图案。在供多个垂直信号线vsl连接的列处理电路92中也同样适用。上述电路图案120等能够应用于这样的行扫描电路91、列处理电路92、以及与列处理电路92连接的列扫描电路93。

[0078]

另外,不限于上述的nand存储器、dram、摄像元件,在fpga(现场可编程门阵列)、交叉点存储器等中,有时也设置将具有相同形状的单位图案在一个方向上重复排列而形成的电路图案。另外,即使是具有与上述nand存储器nm中的行解码器rd、读出放大器sa中的一个相当的电路的半导体器件,也能够对该电路应用上述的电路图案120等。

[0079]

对本发明的几个实施方式(变形例)进行了说明,但这些实施方式是作为例子而提出的,意图不是限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围或主旨内,并且包含在权利要求书所记载的发明及其等同的范围内。

[0080]

另外,在本说明书中作为缺陷例示了微粒pcl,但不限于此,在确定重复排列有单位图案的电路图案中的、例如在蚀刻时可能产生的布线的断线、短路等缺陷的情况下,实施方式的电路图案是有用的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。