适用于有损信源编码的原模图ldpc码的结构优化方法及装置

技术领域

1.本发明涉及通信编码领域,特别涉及一种适用于有损信源编码的原模图ldpc码的结构优化方法及装置。

背景技术:

2.有损信源编码在学术界和工业界仍然有很高的需求。根据信源编码和信道编码的对偶性,性能良好的信道码可以作为有损信源编码的候选者。此外,之前的矢量量化很难处理成千上万长度的序列。作为低密度奇偶校验码(low density parity check,ldpc)的一类,原模图ldpc码因其具有线性的编译码复杂度以及易于硬件实现的优异特性而备受关注。因此,考虑到原模图ldpc码相较于传统的ldpc码具有出色的纠错性能;

3.在将结构化码-原模图ldpc码应用于有损信源编码,方案的矢量量化采用了洗牌rbp(shuffled rbp,s-rbp)算法,其消息更新过程不同于rbp算法,有效提高了系统的收敛性,但可能会导致量化的性能损失。因此,该方案并未获得靠近理论率失真界的性能;

4.为了获得靠近理论率失真界的系统性能,我们重新构建了系统框架进行研究。研究发现,传统的原模图ldpc码并不适用于有损信源编码。

5.有鉴于此,提出本技术。

技术实现要素:

6.本发明公开了一种适用于有损信源编码的原模图ldpc码的结构优化方法、装置、设备及可读存储介质,旨在构建一种适用于有损信源编码的原模图ldpc码。

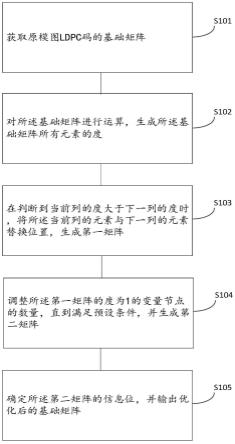

7.本发明第一实施例提供了一种适用于有损信源编码的原模图ldpc码的结构优化方法,包括:

8.获取原模图ldpc码的基础矩阵;

9.对所述基础矩阵进行运算,生成所述基础矩阵所有元素的度;

10.在判断到当前列的度大于下一列的度时,将所述当前列的元素与下一列的元素替换位置,生成第一矩阵;

11.调整所述第一矩阵的度为1的变量节点的数量,直到满足预设条件,并生成第二矩阵;

12.确定所述第二矩阵的信息位,并输出优化后的基础矩阵。

13.优选地,所述对所述基础矩阵进行运算,生成所述基础矩阵所有元素的度,具体为:

14.调用度的运算模型,对所述基础矩阵进行计算,生成所有元素的度,其中,所述运算模型为:d

vj

=b

1j

b

2j

... b

mj

;

15.其中,b

ij

为基础矩阵的具体元素值,i=1,2,...,m,j=1,2,...,n。

16.优选地,所述调整所述第一矩阵的度为1的变量节点的数量,直到满足预设条件,并生成第二矩阵具体为:

17.将所述第一矩阵前m列均调成度为1,且调整时把减少的度数加到最后1列的相应行上,即b

ij-1;b

in

1,直至满足以下条件:

[0018][0019]

优选地,还包括:

[0020]

在判断到所述第二矩阵的行数与列数的差值小于预设值时,继续把n-1列调成度为2,且调整时把减少的度数加到最后1列的相应行上,即b

i(n-1)-1;b

in

1,直至满足以下条件:

[0021]

将转换为

[0022]

本发明第二实施例提供了一种适用于有损信源编码的原模图ldpc码的结构优化装置,包括:

[0023]

基础矩阵获取单元,用于获取原模图ldpc码的基础矩阵;

[0024]

运算单元,用于对所述基础矩阵进行运算,生成所述基础矩阵所有元素的度;

[0025]

第一矩阵生成单元,用于在判断到当前列的度大于下一列的度时,将所述当前列的元素与下一列的元素替换位置,生成第一矩阵;

[0026]

第二矩阵生成单元,用于调整所述第一矩阵的度为1的变量节点的数量,直到满足预设条件,并生成第二矩阵;

[0027]

输出单元,用于确定所述第二矩阵的信息位,并输出优化后的基础矩阵。

[0028]

优选地,所述对所述基础矩阵进行运算,生成所述基础矩阵所有元素的度,具体为:

[0029]

调用度的运算模型,对所述基础矩阵进行计算,生成所有元素的度,其中,所述运算模型为:d

vj

=b

1j

b

2j

... b

mj

;

[0030]

其中,b

ij

为基础矩阵的具体元素值,i=1,2,...,m,j=1,2,...,n。

[0031]

优选地,所述调整所述第一矩阵的度为1的变量节点的数量,直到满足预设条件,并生成第二矩阵具体为:

[0032]

将所述第一矩阵前m列均调成度为1,且调整时把减少的度数加到最后1列的相应行上,即b

ij-1;b

in

1,直至满足以下条件:

[0033][0034]

优选地,还包括:

[0035]

在判断到所述第二矩阵的行数与列数的差值小于预设值时,继续把n-1列调成度为2,且调整时把减少的度数加到最后1列的相应行上,即b

i(n-1)-1;b

in

1,直至满足以下条件:

[0036]

将转换为

[0037]

本发明第三实施例提供了一种适用于有损信源编码的原模图ldpc码的结构优化设备,包括存储器以及处理器,所述存储器内存储有计算机程序,所述计算机程序能够被所述处理器执行,以实现如权利上任意一项所述的一种适用于有损信源编码的原模图ldpc码的结构优化方法。

[0038]

本发明第四实施例提供了一种计算机可读存储介质,存储有计算机程序,所述计算机程序能够被所述计算机可读存储介质所在设备的处理器执行,以实现如上任意一项所述的一种适用于有损信源编码的原模图ldpc码的结构优化方法。

[0039]

基于本发明提供的一种适用于有损信源编码的原模图ldpc码的结构优化方法、装置、设备及计算机可读存储介质,通过对原模图ldpc码的基础矩阵进行运算,生成所述基础矩阵所有元素的度(即基础矩阵每一列和值),在判断到当前列的度大于下一列的度时,将所述当前列的元素与下一列的元素替换位置,生成第一矩阵,进一步调整所述第一矩阵的度为1的变量节点的数量,直到满足预设条件,并生成第二矩阵,最后确定所述第二矩阵的信息位,并输出优化后的基础矩阵,经过优化后得到的码族使得有损信源编码系统获得了靠近率失真理论曲线的性能,即获得了显著的性能增益。

附图说明

[0040]

图1是本发明第一实施例提供了一种适用于有损信源编码的原模图ldpc码的结构优化方法的流程示意图;

[0041]

图2是本发明提供的ar3a-sc码族与ar3a码族的率失真性能对比仿真图;

[0042]

图3是本发明提供的ar4ja-sc码族与ar4ja码族的率失真性能对比仿真图;

[0043]

图4是本发明第二实施例提供了一种适用于有损信源编码的原模图ldpc码的结构优化装置的模块示意图;

具体实施方式

[0044]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完

整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0045]

为了更好的理解本发明的技术方案,下面结合附图对本发明实施例进行详细描述。

[0046]

应当明确,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本发明保护的范围。

[0047]

在本发明实施例中使用的术语是仅仅出于描述特定实施例的目的,而非旨在限制本发明。在本发明实施例和所附权利要求书中所使用的单数形式的“一种”、“所述”和“该”也旨在包括多数形式,除非上下文清楚地表示其他含义。

[0048]

应当理解,本文中使用的术语“和/或”仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本文中字符“/”,一般表示前后关联对象是一种“或”的关系。

[0049]

取决于语境,如在此所使用的词语“如果”可以被解释成为“在

……

时”或“当

……

时”或“响应于确定”或“响应于检测”。类似地,取决于语境,短语“如果确定”或“如果检测(陈述的条件或事件)”可以被解释成为“当确定时”或“响应于确定”或“当检测(陈述的条件或事件)时”或“响应于检测(陈述的条件或事件)”。

[0050]

实施例中提及的“第一\第二”仅仅是是区别类似的对象,不代表针对对象的特定排序,可以理解地,“第一\第二”在允许的情况下可以互换特定的顺序或先后次序。应该理解“第一\第二”区分的对象在适当情况下可以互换,以使这里描述的实施例能够以除了在这里图示或描述的那些以外的顺序实施。

[0051]

以下结合附图对本发明的具体实施例做详细说明。

[0052]

本发明公开了一种适用于有损信源编码的原模图ldpc码的结构优化方法、装置、设备及可读存储介质,旨在提高原模图ldpc码的压缩性能,获得靠近理论曲线的率失真性能。

[0053]

本发明第一实施例提供了一种适用于有损信源编码的原模图ldpc码的结构优化方法,其可由原模图ldpc码的结构优化设备(以下简称优化设备)来执行,特别的,由所述优化设备内的一个或者多个处理器来执行,以至少实现如下步骤:

[0054]

s101,获取原模图ldpc码的基础矩阵;

[0055]

在本实施例中,所述评价设备可为台式电脑、笔记本电脑、服务器、工作站等具有数据处理分析能力的终端,其中,所述优化设备内可安装有相应的操作系统以及应用软件,并通过操作系统以及应用软件的结合来实现本实施例所需的功能。

[0056]

需要说明的是,所述原模图ldpc码的基础矩阵可以是行数为m和列数为n的基础矩阵。

[0057]

s102,对所述基础矩阵进行运算,生成所述基础矩阵所有元素的度;

[0058]

具体地,在本实施例中,调用度的运算模型,对所述基础矩阵进行计算,生成所有元素的度,其中,所述运算模型为:d

vj

=b

1j

b

2j

... b

mj

;

[0059]

其中,b

ij

为基础矩阵的具体元素值,i=1,2,...,m,j=1,2,...,n。

[0060]

s103,在判断到当前列的度大于下一列的度时,将所述当前列的元素与下一列的元素替换位置,生成第一矩阵;

[0061]

具体地:在本实施例中,当j=1,2,...,n时,如果d

vj

》d

vj 1

,那么将第j个vnvj与第j 1个vnv

j 1

交换位置。

[0062]

s104,调整所述第一矩阵的度为1的变量节点的数量,直到满足预设条件,并生成第二矩阵;

[0063]

具体地:将所述第一矩阵前m列均调成度为1,且调整时把减少的度数加到最后1列的相应行上,即b

ij-1;b

in

1,直至满足以下条件:

[0064][0065]

在本发明一个可能的实施例中,在判断到所述第二矩阵的行数与列数的差值小于预设值时,继续把n-1列调成度为2,且调整时把减少的度数加到最后1列的相应行上,即b

i(n-1)-1;b

in

1,直至满足以下条件:

[0066]

将转换为

[0067]

需要说明的是,考虑影响原模图ldpc码性能的因素,尤其是度为1的变量节点(variable node,vn)和度为2的vn在vns中所占的比例,设计与优化出适用于有损信源编码系统的原模图ldpc码,获得了靠近率失真理论曲线的性能。

[0068]

s105,确定所述第二矩阵的信息位,并输出优化后的基础矩阵。

[0069]

需要说明的是,选择最后k列(即变量节点度大的k列)为信息位,其中,k=n-m。这里信息位的位置对应的就是压缩序列v选取的位置。

[0070]

在本实施例中,vj表示基础矩阵b的第j个变量节点,dvj表示第j个变量节点的度的大小,b

ij

≥0,i、o1和o2分别表示(m-α)

×

(n-2)的单位矩阵、α

×

β的全零矩阵、以及(m-2)

×

1的全零矩阵。当n-m≥2时,α=β=0,也就是说此时o1不存在。

[0071]

一种扩展方式:

[0072]

码率为(n 1)/(n 2)(n》1时)的ar3a码和ar4ja码对应的优化后的基础矩阵b-sc,与1/2码率的ar3a码和ar4ja码的原模图进行扩展的方式一样,由1/2码率的ar3a-sc和ar4ja-sc进行相应的扩展得到。

[0073]

以下用一个例子进行阐述:

[0074]

以1/2码率的累加-重复3-累加(accumulate repeat-3 accumulate,ar3a)码为例,其具体实施步骤如下:

[0075]

步骤1:输入原模图ldpc码的基础矩阵行数m=3和列数n=5。

[0076]

步骤2:计算基础矩阵所有vns的度,得到

[0077]dv1

=1,d

v2

=5,d

v3

=4,d

v4

=2,d

v5

=2。

[0078]

步骤3:当j=1,2,...,4,5时,如果d

vj

》d

vj 1

,那么将第j个vnvj与第j 1个vnv

j 1

交换位置,则有:

[0079][0080]

步骤4:令b

ij-1;b

in

1,直至满足以下条件:

[0081][0082]

那么,可得:

[0083][0084]

步骤5:n-m=5-3=2;不满足该步骤条件,跳过。

[0085]

步骤6:选择最后k=n-m=5-3=2列(即变量节点度大的k=2列)为信息位。这里信息位的位置对应的就是压缩序列v选取的位置。

[0086]

步骤7:输出优化后的基础矩阵

[0087]

同理,可以得到针对累加-重复4-累加(accumulate repeat-4 jagged accumulate,ar4ja)码进行结构优化设计以后的码,并应用“一种扩展方式”中的方式进行码率扩展得到相应的码族。在此我们将优化后的相应的码记为ar3a-sc码和ar4ja-sc码。图2和图3为结构优化前后相应的系统的率失真性能仿真图。

[0088]

在所有实验中,信源统计概率为0.5,码长n为2520比特,每个点表示50次实验的平均失真,每次试验的最大迭代次数为300次。rbp算法的参数γ1固定为1,并且γ∈[0,1]为常数。

[0089]

图2所示的是使用本发明方法提出的ar3a-sc码族和ar3a码族之间的率失真性能对比。图3所示的是使用本发明方法提出的ar4ja-sc码族和ar4ja码族之间的率失真性能对

比。从两幅图中均可以看出,使用经典的p-ldpc码族得到的率失真性能非常差,使用本发明方法设计与优化后的码族获得的率失真性能均能靠近理论曲线。而且,在2/3码率时,分别获得了高达2.657db和2.556db的性能增益,在1/5码率、2/9码率时编码剩余度分别低至0.0148、0.0136。

[0090]

以上对本实施例所陈述的用作有损信源编码的原模图ldpc码的结构优化方法进行了详细的介绍和说明,上述具体实施方式可用于帮助理解本发明的核心思想。传统的原模图ldpc码用于有损信源编码系统的率失真性能极差,本实施例从影响原模图ldpc码性能的关键因素出发,提出了一种适用于有损信源编码的码型结构优化方法,经过该方法优化后得到的码族使得有损信源编码系统获得了靠近率失真理论曲线的性能,即获得了显著的性能增益。

[0091]

本发明第二实施例提供了一种适用于有损信源编码的原模图ldpc码的结构优化装置,包括:

[0092]

基础矩阵获取单元,用于获取原模图ldpc码的基础矩阵;

[0093]

运算单元,用于对所述基础矩阵进行运算,生成所述基础矩阵所有元素的度;

[0094]

第一矩阵生成单元,用于在判断到当前列的度大于下一列的度时,将所述当前列的元素与下一列的元素替换位置,生成第一矩阵;

[0095]

第二矩阵生成单元,用于调整所述第一矩阵的度为1的变量节点的数量,直到满足预设条件,并生成第二矩阵;

[0096]

输出单元,用于确定所述第二矩阵的信息位,并输出优化后的基础矩阵。

[0097]

优选地,所述对所述基础矩阵进行运算,生成所述基础矩阵所有元素的度,具体为:

[0098]

调用度的运算模型,对所述基础矩阵进行计算,生成所有元素的度,其中,所述运算模型为:d

vj

=b

1j

b

2j

... b

mj

;

[0099]

其中,b

ij

为基础矩阵的具体元素值,i=1,2,...,m,j=1,2,...,n。

[0100]

优选地,所述调整所述第一矩阵的度为1的变量节点的数量,直到满足预设条件,并生成第二矩阵具体为:

[0101]

将所述第一矩阵前m列均调成度为1,且调整时把减少的度数加到最后1列的相应行上,即b

ij-1;b

in

1,直至满足以下条件:

[0102][0103]

优选地,还包括:

[0104]

在判断到所述第二矩阵的行数与列数的差值小于预设值时,继续把n-1列调成度为2,且调整时把减少的度数加到最后1列的相应行上,即b

i(n-1)-1;b

in

1,直至满足以下条件:

[0105]

将转换为

[0106]

本发明第三实施例提供了一种适用于有损信源编码的原模图ldpc码的结构优化设备,包括存储器以及处理器,所述存储器内存储有计算机程序,所述计算机程序能够被所述处理器执行,以实现如权利上任意一项所述的一种适用于有损信源编码的原模图ldpc码的结构优化方法。

[0107]

本发明第四实施例提供了一种计算机可读存储介质,存储有计算机程序,所述计算机程序能够被所述计算机可读存储介质所在设备的处理器执行,以实现如上任意一项所述的一种适用于有损信源编码的原模图ldpc码的结构优化方法。

[0108]

基于本发明提供的一种适用于有损信源编码的原模图ldpc码的结构优化方法、装置、设备及计算机可读存储介质,通过对原模图ldpc码的基础矩阵进行运算,生成所述基础矩阵所有元素的度(即基础矩阵每一列和值),在判断到当前列的度大于下一列的度时,将所述当前列的元素与下一列的元素替换位置,生成第一矩阵,进一步调整所述第一矩阵的度为1的变量节点的数量,直到满足预设条件,并生成第二矩阵,最后确定所述第二矩阵的信息位,并输出优化后的基础矩阵,经过优化后得到的码族使得有损信源编码系统获得了靠近率失真理论曲线的性能,即获得了显著的性能增益。

[0109]

示例性地,本发明第三实施例和第四实施例中所述的计算机程序可以被分割成一个或多个模块,所述一个或者多个模块被存储在所述存储器中,并由所述处理器执行,以完成本发明。所述一个或多个模块可以是能够完成特定功能的一系列计算机程序指令段,该指令段用于描述所述计算机程序在所述实现一种适用于有损信源编码的原模图ldpc码的结构优化设备中的执行过程。例如,本发明第二实施例中所述的装置。

[0110]

所称处理器可以是中央处理单元(central processing unit,cpu),还可以是其他通用处理器、数字信号处理器(digital signal processor,dsp)、专用集成电路(application specific integrated circuit,asic)、现成可编程门阵列(field-programmable gate array,fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件等。通用处理器可以是微处理器或者该处理器也可以是任何常规的处理器等,所述处理器是所述的一种原模图ldpc码的结构优化方法的控制中心,利用各种接口和线路连接整个所述实现对一种适用于有损信源编码的原模图ldpc码的结构优化方法的各个部分。

[0111]

所述存储器可用于存储所述计算机程序和/或模块,所述处理器通过运行或执行存储在所述存储器内的计算机程序和/或模块,以及调用存储在存储器内的数据,实现一种适用于有损信源编码的原模图ldpc码的结构优化方法的各种功能。所述存储器可主要包括存储程序区和存储数据区,其中,存储程序区可存储操作系统、至少一个功能所需的应用程序(比如声音播放功能、文字转换功能等)等;存储数据区可存储根据手机的使用所创建的数据(比如音频数据、文字消息数据等)等。此外,存储器可以包括高速随机存取存储器,还可以包括非易失性存储器,例如硬盘、内存、插接式硬盘、智能存储卡(smart media card,smc)、安全数字(secure digital,sd)卡、闪存卡(flash card)、至少一个磁盘存储器件、闪

存器件、或其他易失性固态存储器件。

[0112]

其中,所述实现的模块如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本发明实现上述实施例方法中的全部或部分流程,也可以通过计算机程序来指令相关的硬件来完成,所述的计算机程序可存储于一个计算机可读存储介质中,该计算机程序在被处理器执行时,可实现上述各个方法实施例的步骤。其中,所述计算机程序包括计算机程序代码,所述计算机程序代码可以为源代码形式、对象代码形式、可执行文件或某些中间形式等。所述计算机可读介质可以包括:能够携带所述计算机程序代码的任何实体或装置、记录介质、u盘、移动硬盘、磁碟、光盘、计算机存储器、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、电载波信号、电信信号以及软件分发介质等。需要说明的是,所述计算机可读介质包含的内容可以根据司法管辖区内立法和专利实践的要求进行适当的增减,例如在某些司法管辖区,根据立法和专利实践,计算机可读介质不包括电载波信号和电信信号。

[0113]

需说明的是,以上所描述的装置实施例仅仅是示意性的,其中所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部模块来实现本实施例方案的目的。另外,本发明提供的装置实施例附图中,模块之间的连接关系表示它们之间具有通信连接,具体可以实现为一条或多条通信总线或信号线。本领域普通技术人员在不付出创造性劳动的情况下,即可以理解并实施。

[0114]

以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。