技术特征:

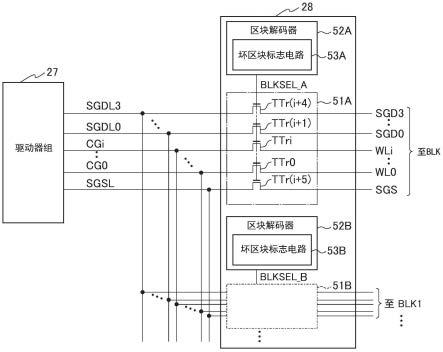

1.一种非易失性半导体存储装置,具备:存储单元阵列,具有多个选择区块与多个非选择区块;以及行解码器,具有对所述选择区块或者所述非选择区块进行切换的区块解码器,所述区块解码器具备坏区块标志电路,所述坏区块标志电路具有存储多值数据的多个锁存电路,所述区块解码器,在基于所述多值数据判断为是坏区块的情况下,切换为所述非选择区块,在基于所述多值数据判断为不是坏区块的情况下,切换为所述选择区块。2.如权利要求1所述的非易失性半导体存储装置,还具备寄存器,该寄存器保持指令和区块地址的信息,所述指令用于执行写入、读入以及擦除,所述行解码器根据所述寄存器的所述指令,基于所述多值数据,由所述非选择区块切换为所述选择区块。3.如权利要求1所述的非易失性半导体存储装置,所述多值数据是多个测试存储分区的每一个的坏区块标志的信息。4.如权利要求2所述的非易失性半导体存储装置,所述多值数据是多个测试存储分区的每一个的坏区块标志的信息。5.如权利要求3所述的非易失性半导体存储装置,所述坏区块标志的信息是单元测试的合格/失败信息、输入缓冲器的写入时间可否的判定信息、以及失败比特计数的判定测试中的至少任一个。6.如权利要求4所述的非易失性半导体存储装置,所述坏区块标志的信息是单元测试的合格/失败信息、输入缓冲器的写入时间可否的判定信息、以及失败比特计数的判定测试中的至少任一个。7.如权利要求2所述的非易失性半导体存储装置,所述指令具有:第一指令,用于执行作为1比特信息的二值的单层单元缓存;以及第二指令,用于执行作为3比特信息的八值的三层单元的写入。8.如权利要求3所述的非易失性半导体存储装置,在所述多个锁存电路中包含第一锁存电路与第二锁存电路,所述第一锁存电路中被设置所述多个测试存储分区中的第一测试分区的坏区块标志的信息,所述第二锁存电路中被设置所述多个测试存储分区中的第二测试分区的坏区块标志的信息。9.如权利要求8所述的非易失性半导体存储装置,所述行解码器基于包含所述第一测试分区的坏区块标志的信息与所述第二测试分区的坏区块标志的信息在内的所述多值数据,由所述非选择区块切换为所述选择区块。10.如权利要求8所述的非易失性半导体存储装置,所述第一测试分区的坏区块标志的信息是,表示在所述第一测试分区中是否产生了异常的信息,所述第二测试分区的坏区块标志的信息是,表示在所述第二测试分区中是否产生了异

常的信息。11.如权利要求8所述的非易失性半导体存储装置,所述第一测试分区是多层单元的单元测试分区,所述第二测试分区是单层单元的单元测试分区。12.如权利要求3所述的非易失性半导体存储装置,在所述多个锁存电路中包含第一锁存电路、第二锁存电路、以及第三锁存电路,所述第一锁存电路中被设置所述多个测试存储分区中的第一测试分区的坏区块标志的信息,所述第二锁存电路中被设置所述多个测试存储分区中的第二测试分区的坏区块标志的信息,所述第三锁存电路中被设置所述多个测试存储分区中的第三测试分区的坏区块标志的信息。13.如权利要求12所述的非易失性半导体存储装置,所述行解码器基于包含所述第一测试分区的坏区块标志的信息、所述第二测试分区的坏区块标志的信息、以及所述第三测试分区的坏区块标志的信息在内的所述多值数据,由所述非选择区块切换为所述选择区块。14.如权利要求12所述的非易失性半导体存储装置,所述第一测试分区的坏区块标志的信息是,表示在所述第一测试分区中是否产生了异常的信息,所述第二测试分区的坏区块标志的信息是,表示在所述第二测试分区中是否产生了异常的信息,所述第三测试分区的坏区块标志的信息是,表示在所述第三测试分区中是否产生了异常的信息。15.如权利要求12所述的非易失性半导体存储装置,所述第一测试分区是三层单元的单元测试分区,所述第二测试分区是三层单元的写入动作的时间的测试分区,所述第三测试分区是单层单元的单元测试分区。16.一种非易失性半导体存储装置的动作方法,行解码器从寄存器接收行地址,并基于所述行地址,向多个锁存电路设置多值数据,所述行解码器,在基于所述多值数据判断为是坏区块的情况下,切换为非选择区块,在基于所述多值数据判断为不是所述坏区块的情况下,切换为选择区块。17.如权利要求16所述的非易失性半导体存储装置的动作方法,所述多值数据是多个测试存储分区的每一个的坏区块标志的信息。18.如权利要求17所述的非易失性半导体存储装置的动作方法,所述坏区块标志的信息是单元测试的合格/失败信息、输入缓冲器的写入时间可否的判定信息、以及失败比特计数的判定测试中的至少某一个。19.一种非易失性半导体存储装置的动作方法,行解码器根据在寄存器中保持的指令,从最先的区块起依次检测在多个锁存电路中是否设置了坏区块标志的数据,

在检测出设置了所述坏区块标志的数据的情况下,从坏区块地址提取出在所述多个锁存电路中保持的所述坏区块标志的数据,在基于所述坏区块标志的数据而判定为成为对象的区块为选择区块的情况下,由非选择区块切换为选择区块,并对存储单元阵列执行写入。20.如权利要求19所述的非易失性半导体存储装置的动作方法,所述指令具有:第一指令,用于执行作为1比特信息的二值的单层单元缓存;以及第二指令,用于执行作为3比特信息的八值的三层单元的写入。

技术总结

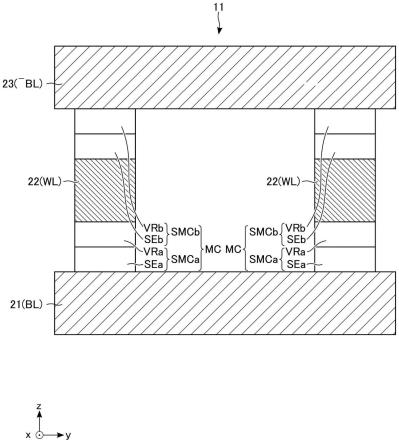

实施方式提供非易失性半导体存储装置,其基于多值数据,将包含坏区块的非选择区块设为能够使用,从而提高了存储单元阵列的良品率。实施方式的非易失性半导体存储装置具备存储单元阵列和行解码器,存储单元阵列具有多个选择区块与多个非选择区块,行解码器具有对选择区块或者非选择区块进行切换的区块解码器。区块解码器基于多值数据,在判断为是坏区块的情况下,切换为非选择区块,在判断为不是坏区块的情况下,切换为选择区块。此外,区块解码器具备坏区块标志电路,该坏区块标志电路具有存储多值数据的多个锁存电路。多值数据的多个锁存电路。多值数据的多个锁存电路。

技术研发人员:小松幸生

受保护的技术使用者:铠侠股份有限公司

技术研发日:2021.08.13

技术公布日:2022/8/25

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。