igbt器件

技术领域

1.本发明涉及一种半导体集成电路,特别是涉及一种igbt器件。

背景技术:

2.igbt器件具有多方面的优势,比如:1.低饱和压;2.简化的驱动能力;3.异常工作时能承受高能耗等。这些优势使其成为点火应用中主流的开关器件。对于点火igbt器件即应用于汽车点火器的igbt器件,其最重要的性能参数是目标钳位电压和钳位能耗(scis),通常在需要igbt中引入一组由背对背串联的齐纳二极管形成的齐纳二极管串联结构104来实现特定的钳位电压,通常的芯片布局如图1所示。

3.现有igbt器件包括:有源区101和终端区102,所述终端区102环绕在所述有源区101的周侧。图1中,有源区101为位于线101a内部的区域,所述终端区102则是位于线101a到线102a之间的区域。

4.在所述有源区101中形成有多个并联连接的igbt原胞(未显示)。

5.各所述igbt原胞的栅极结构包括依次叠加的栅介质层和栅极导电材料层如多晶硅栅,各所述igbt原胞的多晶硅栅连接在一起并通过金属互连结构连接到由正面金属层形成的栅极焊盘103。

6.所述终端区102的最外侧设置有第一导电类型重掺杂的场截止区,也即在靠近线102a处设置有场截止区。所述终端区102用于承受所述有源区101到所述场截止区之间的横向电压。

7.所述齐纳二极管串联结构104的第一端连接所述栅极导电材料层,各所述齐纳二极管串联结构104的第二端连接所述场截止区。

8.如图2所示,是图1中的由齐纳二极管串联结构104形成的反馈钳位电路的俯视面结构放大图;齐纳二极管串联结构104的形成在多晶硅条上,所述多晶硅条上形成有交替排列的第一导电类型掺杂区105和第二导电类型掺杂区106,各所述齐纳二极管由相邻的所述第一导电类型掺杂区105和所述第二导电类型掺杂区106组成。所述齐纳二极管串联结构104的两端的掺杂类型都为第一导电类型也即所述齐纳二极管串联结构104的第一端和第二端都为所述第一导电类型掺杂区105。

9.igbt器件需要在齐纳击穿时达到目标钳位电压和目标钳位电阻,也即,所述齐纳二极管串联结构104的钳位电压要大于等于目标钳位电压,同时所述齐纳二极管串联结构104的钳位电阻要大于等于目标钳位电阻。

10.所述齐纳二极管串联结构104的钳位电压则和所述齐纳二极管串联结构104的长度即版图上的高度相关,所述齐纳二极管串联结构104的长度越长,则串联的齐纳二极管的数量越多,故钳位电压越大。如图1所示,这会使得,所述齐纳二极管串联结构104的长度会大于所述终端区102的宽度,所述齐纳二极管串联结构104的第一端会延伸到有源区101中,从而占用有源区的面积。

11.所述齐纳二极管串联结构104的钳位电阻则和所述齐纳二极管串联结构104的宽

度相关,所述齐纳二极管串联结构104的宽度越大,则所述齐纳二极管串联结构104的钳位电阻会越小,故为了达到目标钳位电阻,需要加宽所述齐纳二极管串联结构104的宽度。

12.由图1所示可知,所述齐纳二极管串联结构104的高度远大于终端区102的宽度,这使得所述齐纳二极管串联结构104需要占有很大比例的有源区101面积,由于钳位能耗很大程度上取决于有源区面积和有源区元胞的均匀性,可以看出,所述齐纳二极管串联结构104的引入对有源区的面积和均匀性都带来不可忽视的影响,进而大大的削弱了钳位能耗。

技术实现要素:

13.本发明所要解决的技术问题是提供一种igbt器件,能使连接在有源区的栅极导电材料层和终端区最外侧表面的场截止区之间的由齐纳二极管连接形成的反馈钳位电路的钳位电压和钳位电阻同时满足要求,且不会占用有源区的面积,从而能提升有源区的实际面积以及有源区的igbt原胞的均匀性,能改善钳位能耗。

14.为解决上述技术问题,本发明提供的igbt器件包括:有源区和终端区,所述终端区环绕在所述有源区的周侧。

15.在所述有源区中形成有多个并联连接的igbt原胞。

16.各所述igbt原胞的栅极结构包括依次叠加的栅介质层和栅极导电材料层,各所述igbt原胞的栅极导电材料层连接在一起。

17.所述终端区的最外侧设置有第一导电类型重掺杂的场截止区。

18.在所述终端区中设置有由多个齐纳二极管原胞并联连接形成的齐纳二极管阵列。

19.各所述齐纳二极管原胞由多个齐纳二极管背靠背串联而成,所述齐纳二极管原胞的两端的掺杂类型都为第一导电类型。

20.各所述齐纳二极管原胞的第一端连接所述栅极导电材料层,各所述齐纳二极管原胞的第二端连接所述场截止区。

21.在俯视面上,所述终端区呈环形结构,令所述终端区的宽度方向为y方向,所述终端区的环绕方向为x方向。

22.各所述齐纳二极管原胞的各所述齐纳二极管形成在多晶硅条上,所述多晶硅条上形成有交替排列的第一导电类型掺杂区和第二导电类型掺杂区,各所述齐纳二极管由相邻的所述第一导电类型掺杂区和所述第二导电类型掺杂区组成。

23.在各所述齐纳二极管原胞设置处,所述多晶硅条的长度方向沿x方向以及宽度方向沿y方向。

24.所述多晶硅条的宽度小于等于所述齐纳二极管原胞的宽度,所述齐纳二极管原胞的宽度小于所述终端区的宽度,使所述齐纳二极管原胞完全设置在所述终端区中,从而不会占用所述有源区面积。

25.所述igbt器件的齐纳击穿发生时的钳位电压为各所述齐纳二极管原胞的原胞钳位电压,所述原胞钳位电压为各所述齐纳二极管的钳位子电压的叠加,所述齐纳二极管原胞中的所述多晶硅条的长度根据所述齐纳二极管原胞中的所述齐纳二极管的数量进行设置,所述齐纳二极管原胞中的所述齐纳二极管的数量根据所述原胞钳位电压的大小进行设置,所述原胞钳位电压大于等于所述钳位电压的目标值。

26.各所述齐纳二极管原胞具有由所述多晶硅条的宽度决定的原胞钳位电阻;所述

igbt器件的齐纳击穿发生时的钳位电阻为所述齐纳二极管阵列的阵列钳位电阻,所述齐纳二极管阵列的阵列钳位电阻由各所述原胞钳位电阻并联而成且所述阵列钳位电阻小于等于所述钳位电阻的目标值,所述原胞钳位电阻大于所述钳位电阻的目标值。

27.进一步的改进是,在所述齐纳二极管原胞中,所述多晶硅条为由多条多晶硅子条首尾连接而成的折叠结构,所述多晶硅条的折叠结构包括:

28.各所述多晶硅子条具有由第一导电类型掺杂区组成的首端和尾端,各所述多晶硅子条的延伸方向为从首端向尾端延伸,相邻两根所述多晶硅子条的延伸方向相反;

29.第一条所述多晶硅子条的首端作为所述齐纳二极管原胞的第一端;

30.最后一条所述多晶硅子条的尾端作为所述齐纳二极管原胞的第二端;

31.在第一条所述多晶硅子条到最后一条所述多晶硅子条之间,各所述多晶硅子条的首端连接位于同一侧的前一个所述多晶硅子条的尾端,各所述多晶硅子条的尾端连接位于同一侧的后一个所述多晶硅子条的首端;

32.所述多晶硅条的长度为所述多晶硅条的折叠结构中的各所述多晶硅子条的展开长度,所述齐纳二极管原胞的长度由各所述多晶硅子条的长度确定使所述齐纳二极管原胞的长度小于所述多晶硅条的长度。

33.进一步的改进是,各所述多晶硅子条的长度相等,各所述多晶硅子条的首端和位于同一侧的相邻的所述多晶硅子条的尾端对齐,各所述多晶硅子条的尾端和位于同一侧的相邻的所述多晶硅子条的首端对齐。或者,各所述多晶硅子条的长度不相等,各所述多晶硅子条的首端和位于同一侧的相邻的所述多晶硅子条的尾端不对齐,各所述多晶硅子条的尾端和位于同一侧的相邻的所述多晶硅子条的首端不对齐。

34.进一步的改进是,各所述多晶硅子条之间通过多晶硅连接条连接,在所述齐纳二极管原胞的第一端和第二端也分别设置有所述多晶硅连接条,所述多晶硅连接条具有第一导电类型掺杂。

35.进一步的改进是,所述igbt器件的齐纳击穿发生时,所述齐纳二极管阵列为所述栅极导电材料层提供反馈的驱动电流,在沿所述终端区的环形结构的环绕方向上,所述齐纳二极管原胞均匀分布以提升所述驱动电流的均匀性。

36.进一步的改进是,所述igbt器件的齐纳击穿发生时,所述齐纳二极管阵列为所述栅极导电材料层提供反馈的驱动电流,在沿所述终端区的环形结构的环绕方向上,所述栅极导电材料层的串联电阻非均匀分布,所述齐纳二极管原胞非均匀分布,所述齐纳二极管原胞的非均匀分布使到达所述栅极导电材料层的驱动电流均匀分布。

37.进一步的改进是,所述igbt原胞还包括:第二导电类型掺杂的体区,第一导电类型掺杂的漂移区,形成于所述体区表面的第一导电类型重掺杂的发射区,位于所述漂移区背面的第二导电类型重掺杂的集电区。

38.进一步的改进是,所述终端区的结构还包括:

39.终端漂移区,由所述有源区中的所述漂移区延伸到所述终端区中形成;所述场截止区形成在所述终端区的最外侧的所述终端漂移区的表面;

40.第二导电类型环,形成于所述终端区的最内侧的所述终端漂移区表面,所述第二导电类型环和所述有源区的最外侧的所述体区横向接触。

41.进一步的改进是,所述发射区连接到由正面金属层组成发射极;

42.所述栅极导电材料层连接到由正面金属层组成栅极;

43.所述集电区连接到由背面金属层组成的集电极。

44.进一步的改进是,所述场截止区连接到所述集电极。

45.进一步的改进是,所述栅极结构为沟槽栅,所述栅介质层形成在栅极沟槽的底部表面和侧面,所述栅极导电材料层填充在形成有所述栅介质层的所述栅极沟槽中;

46.所述栅极沟槽会穿过所述体区,所述栅极导电材料层从侧面覆盖所述体区表面。

47.进一步的改进是,所述栅极结构为平面栅,所述栅极导电材料层从顶部表面覆盖所述体区表面并延伸到所述漂移区的顶部表面之上。

48.进一步的改进是,所述栅极导电材料层为多晶硅栅。

49.进一步的改进是,所述栅介质层的材料包括氧化层。

50.进一步的改进是,所述igbt器件为点火igbt器件。

51.进一步的改进是,所述igbt器件为n型器件,第一导电类型为n型,第二导电类型为p型;或者,所述igbt器件为p型器件,第一导电类型为p型,第二导电类型为n型。

52.本发明将连接在有源区的栅极导电材料层和终端区最外侧表面的场截止区之间的由齐纳二极管连接形成的反馈钳位电路设置为齐纳二极管阵列,齐纳二极管阵列由多个齐纳二极管原胞并联,而齐纳二极管原胞则由多个齐纳二极管串联而成,各齐纳二极管则形成于多晶硅条上;目标钳位电压即钳位电压的目标值通过设置齐纳二极管原胞的长度即可实现,目标钳位电压和多晶硅条的宽度无关,故能通过减少多晶硅条的宽度来减少齐纳二极管原胞的宽度,使得齐纳二极管原胞能完全设置在终端区中,而不需要占用有源区的面积,从而能改善钳位能耗。

53.同时,多晶硅条的宽度减少后,齐纳二极管原胞的原胞钳位电阻虽然会增加并大于目标钳位电阻即钳位电阻的目标值,但是本发明通过将多个齐纳二极管原胞并联形成齐纳二极管阵列后,齐纳二极管阵列的阵列钳位电阻会降低,最终的钳位电阻是阵列钳位电阻,通过设置并联的齐纳二极管原胞的数量即可使阵列钳位电阻达到钳位电阻的目标值。

54.所以,本发明能使连接在有源区的栅极导电材料层和终端区最外侧表面的场截止区之间的由齐纳二极管连接形成的反馈钳位电路的钳位电压和钳位电阻同时满足要求,且不会占用有源区的面积,从而能提升有源区的实际面积以及有源区的igbt原胞的均匀性。

55.另外,本发明的齐纳二极管原胞能沿终端区的环绕方向均匀分布,这也使得由反馈钳位电路形成的驱动电流能通过均匀分布的齐纳二极管原胞均匀提供到有源区的栅极导电材料层中,从而能极大改善发生齐纳击穿时对器件的栅极导电材料层充电的均匀性。

附图说明

56.下面结合附图和具体实施方式对本发明作进一步详细的说明:

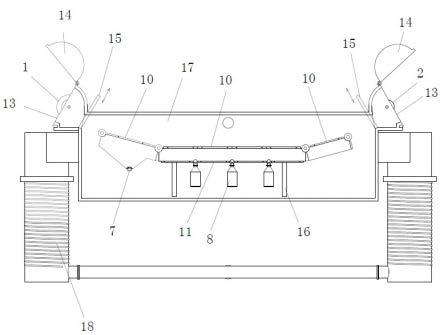

57.图1是现有igbt器件的俯视面结构示意图;

58.图2是图1中的由齐纳二极管串联结构形成的反馈钳位电路的俯视面结构放大图;

59.图3是本发明实施例igbt器件的俯视面结构示意图;

60.图4是本发明实施例igbt器件中的齐纳二极管阵列的俯视面结构放大图;

61.图5是本发明实施例igbt器件中的齐纳二极管原胞的俯视面结构放大图。

具体实施方式

62.如图3所示,是本发明实施例igbt器件的俯视面结构示意图;如图4所示,是本发明实施例igbt器件中的齐纳二极管阵列204的俯视面结构放大图;如图5所示,是本发明实施例igbt器件中的齐纳二极管原胞205的俯视面结构放大图;本发明实施例igbt器件包括:有源区201和终端区202,所述终端区202环绕在所述有源区201的周侧。图3中,有源区201为位于线201a内部的区域,所述终端区202则是位于线201a到线202a之间的区域。

63.在所述有源区201中形成有多个并联连接的igbt原胞(未显示)。

64.各所述igbt原胞的栅极结构包括依次叠加的栅介质层和栅极导电材料层,各所述igbt原胞的栅极导电材料层连接在一起。

65.所述终端区202的最外侧设置有第一导电类型重掺杂的场截止区,也即在靠近线202a处设置有场截止区。所述终端区202用于承受所述有源区201到所述场截止区之间的横向电压。

66.如图4所示,在所述终端区202中设置有由多个齐纳二极管原胞205并联连接形成的齐纳二极管阵列204。

67.如图5所示,各所述齐纳二极管原胞205由多个齐纳二极管背靠背串联而成,所述齐纳二极管原胞205的两端即第一端和第二端的掺杂类型都为第一导电类型。

68.各所述齐纳二极管原胞205的第一端连接所述栅极导电材料层,各所述齐纳二极管原胞205的第二端连接所述场截止区。

69.在俯视面上,所述终端区202呈环形结构,令所述终端区202的宽度方向为y方向,所述终端区202的环绕方向为x方向。

70.各所述齐纳二极管原胞205的各所述齐纳二极管形成在多晶硅条上,所述多晶硅条上形成有交替排列的第一导电类型掺杂区207和第二导电类型掺杂区208,各所述齐纳二极管由相邻的所述第一导电类型掺杂区207和所述第二导电类型掺杂区208组成。由图5所示可知,所述齐纳二极管原胞205的两端的掺杂类型都为第一导电类型也即所述齐纳二极管原胞205的两端都为所述第一导电类型掺杂区207。

71.在各所述齐纳二极管原胞205设置处,所述多晶硅条的长度方向沿x方向以及宽度方向沿y方向。

72.所述多晶硅条的宽度小于等于所述齐纳二极管原胞205的宽度,所述齐纳二极管原胞205的宽度小于所述终端区202的宽度,使所述齐纳二极管原胞205完全设置在所述终端区202中,从而不会占用所述有源区201面积。

73.所述igbt器件的齐纳击穿发生时的钳位电压为各所述齐纳二极管原胞205的原胞钳位电压,所述原胞钳位电压为各所述齐纳二极管的钳位子电压的叠加,所述齐纳二极管原胞205中的所述多晶硅条的长度根据所述齐纳二极管原胞205中的所述齐纳二极管的数量进行设置,所述齐纳二极管原胞205中的所述齐纳二极管的数量根据所述原胞钳位电压的大小进行设置,所述原胞钳位电压大于等于所述钳位电压的目标值。

74.各所述齐纳二极管原胞205具有由所述多晶硅条的宽度决定的原胞钳位电阻;所述igbt器件的齐纳击穿发生时的钳位电阻为所述齐纳二极管阵列204的阵列钳位电阻,所述齐纳二极管阵列204的阵列钳位电阻由各所述原胞钳位电阻并联而成且所述阵列钳位电阻小于等于所述钳位电阻的目标值,所述原胞钳位电阻大于所述钳位电阻的目标值。

75.本发明实施例中,在所述齐纳二极管原胞205中,所述多晶硅条为由多条多晶硅子条206首尾连接而成的折叠结构。所述多晶硅条的折叠结构包括:

76.各所述多晶硅子条206具有由第一导电类型掺杂区207组成的首端和尾端,各所述多晶硅子条206的延伸方向为从首端向尾端延伸,相邻两根所述多晶硅子条206的延伸方向相反。

77.第一条所述多晶硅子条206的首端作为所述齐纳二极管原胞205的第一端。

78.最后一条所述多晶硅子条206的尾端作为所述齐纳二极管原胞205的第二端。

79.在第一条所述多晶硅子条206到最后一条所述多晶硅子条206之间,各所述多晶硅子条206的首端连接位于同一侧的前一个所述多晶硅子条206的尾端,各所述多晶硅子条206的尾端连接位于同一侧的后一个所述多晶硅子条206的首端。

80.所述多晶硅条的长度为所述多晶硅条的折叠结构中的各所述多晶硅子条206的展开长度,所述齐纳二极管原胞205的长度由各所述多晶硅子条206的长度确定使所述齐纳二极管原胞205的长度小于所述多晶硅条的长度。也即,通过所述多晶硅条的折叠结构能减少所述齐纳二极管原胞205的长度,这样能保证所述齐纳二极管原胞205的长度小于对应的所述终端区202的一个侧边对应的长度。在其他实施例中,如果所述多晶硅条的长度本身就小于所述终端区202的最短的侧边对应的长度,则也能不采用折叠结构,而是直接由一条多晶硅组成所述多晶硅条。

81.在一些较佳实施例中,各所述多晶硅子条206的长度相等,各所述多晶硅子条206的首端和位于同一侧的相邻的所述多晶硅子条206的尾端对齐,各所述多晶硅子条206的尾端和位于同一侧的相邻的所述多晶硅子条206的首端对齐。在另一些实施例中,也能为:各所述多晶硅子条206的长度不相等,各所述多晶硅子条206的首端和位于同一侧的相邻的所述多晶硅子条206的尾端不对齐,各所述多晶硅子条206的尾端和位于同一侧的相邻的所述多晶硅子条206的首端不对齐,只要保持所述齐纳二极管原胞205的所述原胞钳位电压满足钳位电压的目标值即可。

82.各所述多晶硅子条206之间通过多晶硅连接条209连接,在所述齐纳二极管原胞205的第一端和第二端也分别设置有所述多晶硅连接条209,所述多晶硅连接条209具有第一导电类型掺杂。

83.在一些较佳实施例中,所述igbt器件的齐纳击穿发生时,所述齐纳二极管阵列204为所述栅极导电材料层提供反馈的驱动电流,在沿所述终端区202的环形结构的环绕方向上,所述齐纳二极管原胞205均匀分布以提升所述驱动电流的均匀性。

84.在另一些较佳实施例中,也能为:所述igbt器件的齐纳击穿发生时,所述齐纳二极管阵列为所述栅极导电材料层提供反馈的驱动电流,在沿所述终端区的环形结构的环绕方向上,所述栅极导电材料层的串联电阻非均匀分布,所述齐纳二极管原胞非均匀分布,所述齐纳二极管原胞的非均匀分布使到达所述栅极导电材料层的驱动电流均匀分布。也即,所述齐纳二极管原胞在物理上是非均匀分布的,但是电学上是均匀分布的,即提供的驱动电流是均匀分布的;这是因为,通过所述齐纳二极管原胞在物理上的非均匀分布对驱动电流的影响来补偿所述栅极导电材料层的串联电阻非均匀分布对驱动电流的影响,最后使得驱动电流分布均匀。

85.本发明实施例中,所述igbt原胞还包括:第二导电类型掺杂的体区,第一导电类型

掺杂的漂移区,形成于所述体区表面的第一导电类型重掺杂的发射区,位于所述漂移区背面的第二导电类型重掺杂的集电区。

86.所述终端区202的结构还包括:

87.终端漂移区,由所述有源区201中的所述漂移区延伸到所述终端区202中形成;所述场截止区形成在所述终端区202的最外侧的所述终端漂移区的表面;

88.第二导电类型环,形成于所述终端区202的最内侧的所述终端漂移区表面,所述第二导电类型环和所述有源区201的最外侧的所述体区横向接触。所述第二导电类型环和所述终端漂移区会形成pn结从而实现承受所述有源区201到所述场截止区之间的横向电压。

89.所述发射区连接到由正面金属层组成发射极,图3中发射极焊盘(pad)形成于所述有源区201的顶部。

90.所述栅极导电材料层连接到由正面金属层组成栅极。图3中,栅极焊盘的形成区域用标记203标出。各所述igbt原胞的所述栅极导电材料层都会电连接到栅极焊盘。

91.所述集电区连接到由背面金属层组成的集电极。

92.在一些实施例中年,所述场截止区也连接到所述集电极。

93.在一些实施例中,所述栅极结构为沟槽栅,所述栅介质层形成在栅极沟槽的底部表面和侧面,所述栅极导电材料层填充在形成有所述栅介质层的所述栅极沟槽中。所述栅极沟槽会穿过所述体区,所述栅极导电材料层从侧面覆盖所述体区表面。所述栅极导电材料层为多晶硅栅。所述栅介质层的材料包括氧化层。在其他实施例中也能为:所述栅极结构为平面栅,所述栅极导电材料层从顶部表面覆盖所述体区表面并延伸到所述漂移区的顶部表面之上。

94.本发明实施例中,所述igbt器件为点火igbt器件。

95.所述igbt器件为n型器件,第一导电类型为n型,第二导电类型为p型。在其他实施例中也能为:所述igbt器件为p型器件,第一导电类型为p型,第二导电类型为n型。

96.本发明实施例将连接在有源区201的栅极导电材料层和终端区202最外侧表面的场截止区之间的由齐纳二极管连接形成的反馈钳位电路设置为齐纳二极管阵列204,齐纳二极管阵列204由多个齐纳二极管原胞205并联,而齐纳二极管原胞205则由多个齐纳二极管串联而成,各齐纳二极管则形成于多晶硅条上;目标钳位电压即钳位电压的目标值通过设置齐纳二极管原胞205的长度即可实现,目标钳位电压和多晶硅条的宽度无关,故能通过减少多晶硅条的宽度来减少齐纳二极管原胞205的宽度,使得齐纳二极管原胞205能完全设置在终端区202中,而不需要占用有源区201的面积。

97.同时,多晶硅条的宽度减少后,齐纳二极管原胞205的原胞钳位电阻虽然会增加并大于目标钳位电阻即钳位电阻的目标值,但是本发明通过将多个齐纳二极管原胞205并联形成齐纳二极管阵列204后,齐纳二极管阵列204的阵列钳位电阻会降低,最终的钳位电阻是阵列钳位电阻,通过设置并联的齐纳二极管原胞205的数量即可使阵列钳位电阻达到钳位电阻的目标值。

98.所以,本发明实施例能使连接在有源区201的栅极导电材料层和终端区202最外侧表面的场截止区之间的由齐纳二极管连接形成的反馈钳位电路的钳位电压和钳位电阻同时满足要求,且不会占用有源区201的面积,从而能提升有源区201的实际面积以及有源区201的igbt原胞的均匀性。

99.另外,本发明实施例的齐纳二极管原胞205能沿终端区202的环绕方向均匀分布,这也使得由反馈钳位电路形成的驱动电流能通过均匀分布的齐纳二极管原胞205均匀提供到有源区201的栅极导电材料层中,从而能极大改善发生齐纳击穿时对器件的栅极导电材料层充电的均匀性。

100.以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。