1.本公开内容涉及碳化硅半导体器件和碳化硅半导体器件的制造方法。本技术主张基于2019年6月10日提交的日本专利申请、即日本特愿2019

‑

107907号的优先权。在该日本专利申请中记载的全部记载内容通过参考被引用到本说明书中。

背景技术:

2.在wo2019/069416号(专利文献1)中记载了具有超结(super junction)部的mosfet(metal oxide semiconductor field effect transistor:金属氧化物半导体场效应晶体管)。现有技术文献专利文献

3.专利文献1:wo2019/069416号

技术实现要素:

4.本公开内容所涉及的碳化硅半导体器件具有碳化硅衬底、第一绝缘体、第一电极和第二电极。碳化硅衬底具有第一主面和与第一主面相反侧的第二主面。碳化硅衬底包含:第一杂质区,所述第一杂质区位于第一主面与第二主面之间,并且具有第一导电型;第二杂质区,所述第二杂质区位于第一主面与第二主面之间,与第一杂质区相接地设置,并且具有与第一导电型不同的第二导电型;第三杂质区,所述第三杂质区位于第一主面与第二主面之间,以与第一杂质区隔开的方式与第二杂质区相接地设置,并且具有第一导电型;第一超结部,所述第一超结部具有第一区和第二区,所述第一区与第一杂质区相接,位于第一杂质区与第二主面之间,并且具有第一导电型,所述第二区与第二杂质区和第一区各自相接,并且具有第二导电型;第四杂质区,所述第四杂质区位于第一主面与第二主面之间,并且具有第一导电型;第五杂质区,所述第五杂质区位于第一主面与第二主面之间,与第四杂质区相接地设置,并且具有第二导电型;第六杂质区,所述第六杂质区位于第一主面与第二主面之间,以与第四杂质区隔开的方式与第五杂质区相接地设置,并且具有第一导电型;和第二超结部,所述第二超结部具有第三区和第四区,所述第三区与第四杂质区相接,位于第四杂质区与第二主面之间,并且具有第一导电型,所述第四区与第五杂质区和第三区各自相接,并且具有第二导电型。第二区具有与第二杂质区相接的第一端面和与第一端面相反侧的第二端面。第四区具有与第五杂质区相接的第三端面和与第三端面相反侧的第四端面。第一区、第二区、第四区、第三区在与第二主面平行的第一方向上排列设置。第二区位于第一区与第四区之间,并且第四区位于第二区与第三区之间。第一主面中设置有第一沟槽,所述第一沟槽将第二区与第四区隔开。第一绝缘体设置在第一沟槽的内部。在相对于第二主面垂直的方向上,第一沟槽的底面位于第二端面与第二主面之间,并且位于第四端面与第二主面之间。

5.本公开内容所涉及的碳化硅半导体器件的制造方法具有以下工序。准备碳化硅外

延衬底,所述碳化硅外延衬底包含碳化硅单晶衬底和碳化硅外延层,所述碳化硅外延层设置在碳化硅单晶衬底上并且具有能够赋予第一导电型的杂质离子。在碳化硅外延层中形成沟槽,所述沟槽具有第一侧面和与第一侧面相对的第二侧面。通过对第一侧面倾斜注入能够赋予第二导电型的杂质离子而形成第二区。通过对第二侧面倾斜注入能够赋予第二导电型的杂质离子而形成第四区。碳化硅外延层包含第一超结部和第二超结部,所述第一超结部具有第二区和具有第一导电型并且与第二区相接的第一区,所述第二超结部具有第四区和具有第一导电型并且与第四区相接的第三区。在相对于碳化硅单晶衬底与碳化硅外延层的边界面垂直的方向上,沟槽的底面位于第二区与碳化硅单晶衬底之间以及第四区与碳化硅单晶衬底之间。利用绝缘体填埋沟槽。

附图说明

6.[图1]图1为示出第一实施方式所涉及的碳化硅半导体器件的构成的截面示意图。[图2]图2为沿图1的ii

‑

ii线得到的截面示意图。[图3]图3为沿图1的iii

‑

iii线得到的截面示意图。[图4]图4为示出第一实施方式所涉及的碳化硅半导体器件200的构成的俯视示意图。[图5]图5为示出第二实施方式所涉及的碳化硅半导体器件的构成的截面示意图。[图6]图6为示出第三实施方式所涉及的碳化硅半导体器件的构成的截面示意图。[图7]图7为示意性地示出第四实施方式所涉及的碳化硅半导体器件的制造方法的流程图。[图8]图8为示出第四实施方式所涉及的碳化硅半导体器件的制造方法的第一工序的截面示意图。[图9]图9为示出第四实施方式所涉及的碳化硅半导体器件的制造方法的第二工序的截面示意图。[图10]图10为示出第四实施方式所涉及的碳化硅半导体器件的制造方法的第三工序的截面示意图。[图11]图11为示出第四实施方式所涉及的碳化硅半导体器件的制造方法的第四工序的截面示意图。[图12]图12为示出第四实施方式所涉及的碳化硅半导体器件的制造方法的第五工序的截面示意图。[图13]图13为示出第四实施方式所涉及的碳化硅半导体器件的制造方法的第六工序的截面示意图。[图14]图14为示出第四实施方式所涉及的碳化硅半导体器件的制造方法的第七工序的截面示意图。[图15]图15为示出第五实施方式所涉及的碳化硅半导体器件的制造方法的第一工序的截面示意图。[图16]图16为示出第五实施方式所涉及的碳化硅半导体器件的制造方法的第二工序的截面示意图。[图17]图17为示出第五实施方式所涉及的碳化硅半导体器件的制造方法的第三

工序的截面示意图。

具体实施方式

[0007]

[本公开内容所要解决的问题]本公开内容的目的在于,提供能够良好地保持超结部的电荷平衡的碳化硅半导体器件和碳化硅半导体器件的制造方法。[本公开内容的效果]根据本公开内容,能够提供能够良好地保持超结部的电荷平衡的碳化硅半导体器件和碳化硅半导体器件的制造方法。[本公开内容的实施方式的说明]首先,列举本公开内容的实施方式进行说明。在本说明书的结晶学方面的记载中,分别将个别取向表示为[],将集合取向表示为<>,将个别面表示为(),将集合面表示为{}。结晶学上的指数为负通常通过将

“‑

(横杠)”标注在数字之上来表示,但在本说明书中,通过在数字前标注负号来表示结晶学上的负指数。

[0008]

(1)本公开内容所涉及的碳化硅半导体器件200具有碳化硅衬底100、第一绝缘体80、第一电极60和第二电极70。碳化硅衬底100具有第一主面1和与第一主面1相反侧的第二主面2。碳化硅衬底100包含:第一杂质区11,所述第一杂质区11位于第一主面1与第二主面2之间,并且具有第一导电型;第二杂质区12,所述第二杂质区12位于第一主面1与第二主面2之间,与第一杂质区11相接地设置,并且具有与第一导电型不同的第二导电型;第三杂质区13,所述第三杂质区13位于第一主面1与第二主面2之间,以与第一杂质区11隔开的方式与第二杂质区12相接地设置,并且具有第一导电型;第一超结部16,所述第一超结部16具有第一区31和第二区32,所述第一区31与第一杂质区11相接,位于第一杂质区11与第二主面2之间,并且具有第一导电型,所述第二区32与第二杂质区12和第一区31各自相接,并且具有第二导电型;第四杂质区21,所述第四杂质区21位于第一主面1与第二主面2之间,并且具有第一导电型;第五杂质区22,所述第五杂质区22位于第一主面1与第二主面2之间,与第四杂质区21相接地设置,并且具有第二导电型;第六杂质区23,所述第六杂质区23位于第一主面1与第二主面2之间,以与第四杂质区21隔开的方式与第五杂质区22相接地设置,并且具有第一导电型;和第二超结部26,所述第二超结部26具有第三区33和第四区34,所述第三区33与第四杂质区21相接,位于第四杂质区21与第二主面2之间,并且具有第一导电型,所述第四区34与第五杂质区22和第三区33各自相接,并且具有第二导电型。第二区32具有与第二杂质区12相接的第一端面17和与第一端面17相反侧的第二端面3。第四区34具有与第五杂质区22相接的第三端面27和与第三端面27相反侧的第四端面4。第一区31、第二区32、第四区34、第三区33在与第二主面2平行的第一方向101上排列设置。第二区32位于第一区31与第四区34之间,并且第四区34位于第二区32与第三区33之间。第一主面1中设置有第一沟槽8,所述第一沟槽8将第二区32与第四区34隔开。第一绝缘体80设置在第一沟槽8的内部。在相对于第二主面2垂直的方向上,第一沟槽8的底面7位于第二端面3与第二主面2之间,并且位于第四端面4与第二主面2之间。

[0009]

(2)在上述(1)所涉及的碳化硅半导体器件200中,第一区31和第三区33各自的杂质浓度可以为3

×

10

16

cm

‑3以上且3

×

10

17

cm

‑3以下。

[0010]

(3)在上述(1)或(2)所涉及的碳化硅半导体器件200中,在第一方向101上将第一区31的宽度设为第一宽度w1、将第二区32的宽度设为第二宽度w2并且将第一区31的杂质浓度设为第一浓度、将第二区32的杂质浓度设为第二浓度的情况下,将其中第一浓度乘以第一宽度w1而得的值除以其中第二浓度乘以第二宽度w2而得的值,由此得到的值可以为0.5以上且1.5以下,并且在第一方向101上将第三区33的宽度设为第三宽度w3、将第四区34的宽度设为第四宽度w4并且将第三区33的杂质浓度设为第三浓度、将第四区34的杂质浓度设为第四浓度的情况下,将其中第三浓度乘以第三宽度w3而得的值除以其中第四浓度乘以第四宽度w4而得的值,由此得到的值可以为0.5以上且1.5以下。

[0011]

(4)在上述(3)所涉及的碳化硅半导体器件200中,第二宽度w2和第四宽度w4各自可以为0.1μm以上且2μm以下。

[0012]

(5)在上述(1)~(4)中任一项所述的碳化硅半导体器件200中,第一方向101上的第一沟槽8的宽度可以为1μm以上且3μm以下。

[0013]

(6)在上述(1)~(5)中任一项所述的碳化硅半导体器件200中,第一沟槽8的深度可以为3μm以上且30μm以下。

[0014]

(7)在上述(1)~(6)中任一项所述的碳化硅半导体器件200中,将第一沟槽8的深度除以第一方向101上的第一沟槽8的宽度而得到的值可以为0.5以上且25以下。

[0015]

(8)在上述(1)~(7)中任一项所述的碳化硅半导体器件200中,第一沟槽8可以具有第一侧面5和第二侧面6,所述第一侧面5与第二区32相接并且从第二区32朝向第一区31凹陷,所述第二侧面6与第四区34相接并且从第四区34朝向第三区33凹陷。

[0016]

(9)在上述(8)所涉及的碳化硅半导体器件200中,在第一方向101上从第一区31的最大宽度减去第一区31的最小宽度而得到的值可以为0.05μm以上且2.0μm以下,并且在第一方向101上从第三区33的最大宽度减去第三区33的最小宽度而得到的值可以为0.05μm以上且2.0μm以下。

[0017]

(10)在上述(1)~(9)中任一项所述的碳化硅半导体器件200中,第一杂质区11与第一区31可以为一体,并且第四杂质区21与第三区33可以为一体。

[0018]

(11)在上述(1)~(10)中任一项所述的碳化硅半导体器件200中,第一主面1中可以设置有第二沟槽9,在相对于第二主面2垂直的方向观察时所述第二沟槽9包围第一沟槽8,并且所述碳化硅半导体器件200可以还具有第二绝缘体90,所述第二绝缘体90设置在第二沟槽9的内部。

[0019]

(12)本公开内容所涉及的碳化硅半导体器件200的制造方法具有以下工序。准备碳化硅衬底100,所述碳化硅衬底100包含碳化硅单晶衬底50和碳化硅外延层40,所述碳化硅外延层40设置在碳化硅单晶衬底50上并且具有能够赋予第一导电型的杂质离子。在碳化硅外延层40中形成沟槽8,所述沟槽8具有第一侧面5和与第一侧面5相对的第二侧面6。通过对第一侧面5倾斜注入能够赋予第二导电型的杂质离子而形成第二区32。通过对第二侧面6倾斜注入能够赋予第二导电型的杂质离子而形成第四区34。碳化硅外延层40包含第一超结部16和第二超结部26,所述第一超结部16具有第二区32和具有第一导电型并且与第二区32相接的第一区31,所述第二超结部26具有第四区34和具有第一导电型并且与第四区34相接的第三区33。在相对于碳化硅单晶衬底50与碳化硅外延层40的边界面45垂直的方向上,沟槽8的底面7位于第二区32与碳化硅单晶衬底50之间以及第四区34与碳化硅单晶衬底50之

间。利用绝缘体80填埋沟槽8。

[0020]

(13)根据上述(12)所涉及的碳化硅半导体器件200的制造方法,在形成第二区32的工序和形成第四区34的工序的各自中,可以对底面7注入能够赋予第二导电型的杂质离子。可以通过蚀刻除去对底面7注入的能够赋予第二导电型的杂质离子。

[0021]

(14)根据上述(12)所涉及的碳化硅半导体器件200的制造方法,在形成第二区32的工序和形成第四区34的工序的各自中,可以以不对底面7注入能够赋予第二导电型的杂质离子的方式进行倾斜注入。[本公开内容的实施方式的详细内容]以下,对本公开内容的实施方式的详细内容进行说明。在以下的说明中,对相同或对应的要素标注相同的符号,对它们不重复相同的说明。

[0022]

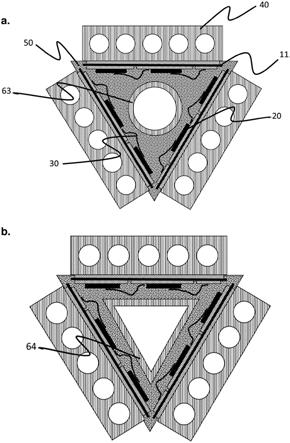

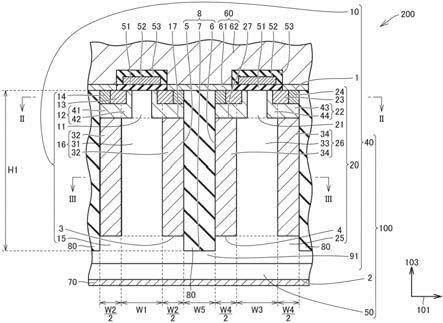

(第一实施方式)首先,对第一实施方式所涉及的碳化硅半导体器件200的构成进行说明。图1为示出第一实施方式所涉及的碳化硅半导体器件200的构成的截面示意图。

[0023]

如图1所示,第一实施方式所涉及的碳化硅半导体器件200例如为平面式mosfet,主要具有:碳化硅衬底100、栅电极52、栅极绝缘膜51、分离绝缘膜53、第一电极60、第二电极70和第一绝缘体80。碳化硅衬底100具有第一主面1和与第一主面1相反侧的第二主面2。碳化硅衬底100包含碳化硅单晶衬底50和设置在碳化硅单晶衬底50上的碳化硅外延层40。碳化硅单晶衬底50构成第二主面2。碳化硅外延层40构成第一主面1。

[0024]

碳化硅单晶衬底50例如由多型4h的六方晶碳化硅构成。第一主面1例如为{0001}面或相对于{0001}面偏离8

°

以下的面。具体而言,第一主面1例如为(0001)面或相对于(0001)面偏离8

°

以下的面。第一主面1例如可以为(000

‑

1)面或相对于(000

‑

1)面偏离8

°

以下的面。

[0025]

碳化硅衬底100包含第一杂质区11、第二杂质区12、第三杂质区13、第一接触区14和第一超结部16。第一杂质区11例如包含n(氮)等能够赋予n型的n型杂质。第一杂质区11例如具有n型(第一导电型)。第一杂质区11例如为漂移区。第二杂质区12与第一杂质区11相接地设置。第一杂质区11位于第一主面1与第二主面2之间。

[0026]

第二杂质区12例如包含al(铝)等能够赋予p型的p型杂质。第二杂质区12具有与n型不同的p型(第二导电型)。第二杂质区12例如为体区。第二杂质区12所包含的p型杂质的浓度可以比第一杂质区11所包含的n型杂质的浓度高。第二杂质区12位于第一主面1与第二主面2之间。

[0027]

第二杂质区12可以具有第五区41和第六区42。第五区41所包含的p型杂质的浓度可以比第六区42所包含的p型杂质的浓度高。第五区41与第二区32、第三杂质区13和第一接触区14相接。第六区42与第一区31、第三杂质区13和第一杂质区11相接。

[0028]

第三杂质区13以与第一杂质区11隔开的方式与第二杂质区12相接地设置。第三杂质区13例如包含p(磷)等能够赋予n型的n型杂质。第三杂质区13例如具有n型。第三杂质区13例如为源极区。第三杂质区13位于第一主面1与第二主面2之间。第三杂质区13所包含的n型杂质的浓度可以比第二杂质区12所包含的p型杂质的浓度高。第一接触区14例如包含al等能够赋予p型的p型杂质。第一接触区14具有p型。第一接触区14所包含的p型杂质的浓度可以比第二杂质区12所包含的p型杂质的浓度高。

[0029]

第一超结部16具有第一区31和第二区32。第一区31与第一杂质区11相接。第一区31位于第一杂质区11与第二主面2之间。第一区31例如包含n等能够赋予n型的n型杂质。第一区31例如具有n型。第一区31可以与第二杂质区12相接。

[0030]

第二区32与第二杂质区12和第一区31的各自相接。第二区32例如包含al等能够赋予p型的p型杂质。第二区32例如具有p型。第一区31例如被一对第二区32所夹住。第一区31和第二区32构成第一超结部16。如图1所示,在相对于第一方向101和第三方向103的各自垂直的方向(第二方向102)观察时,第一区31和第二区32的各自为柱状。

[0031]

碳化硅衬底100包含第四杂质区21、第五杂质区22、第六杂质区23、第二接触区24和第二超结部26。第四杂质区21例如包含n等能够赋予n型的n型杂质。第四杂质区21例如具有n型(第一导电型)。第四杂质区21例如为漂移区。第四杂质区21位于第一主面1与第二主面2之间。

[0032]

第五杂质区22与第四杂质区21相接地设置。第五杂质区22例如包含al等能够赋予p型的p型杂质。第五杂质区22具有与n型不同的p型(第二导电型)。第五杂质区22例如为体区。第五杂质区22所包含的p型杂质的浓度可以比第四杂质区21所包含的n型杂质的浓度高。第五杂质区22位于第一主面1与第二主面2之间。

[0033]

第五杂质区22可以具有第七区43和第八区44。第七区43所包含的p型杂质的浓度可以比第八区44所包含的p型杂质的浓度高。第七区43与第四区34、第六杂质区23和第二接触区24相接。第八区44与第三区33、第六杂质区23和第四杂质区21相接。

[0034]

第六杂质区23以与第四杂质区21隔开的方式与第五杂质区22相接地设置。第六杂质区23例如包含p(磷)等能够赋予n型的n型杂质。第六杂质区23例如具有n型。第六杂质区23例如为源极区。第六杂质区23位于第一主面1与第二主面2之间。第六杂质区23所包含的n型杂质的浓度可以比第五杂质区22所包含的p型杂质的浓度高。第二接触区24例如包含al等能够赋予p型的p型杂质。第二接触区24具有p型。第二接触区24所包含的p型杂质的浓度可以比第五杂质区22所包含的p型杂质的浓度高。

[0035]

第二超结部26具有第三区33和第四区34。第三区33与第四杂质区21相接。第三区33位于第四杂质区21与第二主面2之间。第三区33例如包含n等能够赋予n型的n型杂质。第三区33例如具有n型。第三区33可以与第五杂质区22相接。

[0036]

第四区34与第五杂质区22和第三区33的各自相接。第四区34例如包含al等能够赋予p型的p型杂质。第四区34例如具有p型。第三区33例如被第四区34夹住。第三区33和第四区34构成第二超结部26。如图1所示,在相对于第一方向101和第三方向103的各自垂直的方向(第二方向102)观察时,第三区33和第四区34的各自为柱状。在从第三区33朝向第四区34的方向(第一方向101)上,交替地配置有第一超结部16和第二超结部26。

[0037]

如图1所示,在从第一区31朝向第二区32的方向(第一方向101)上,第一区31的宽度为第一宽度w1,并且第二区32的宽度为第二宽度w2。在从第三区33朝向第四区34的方向(第一方向101)上,第三区33的宽度为第三宽度w3,并且第四区34的宽度为第四宽度w4。需要说明的是,如图1所示,在第二区32被分离为2个的情况下,第二区32的宽度为2个第二区32的宽度的合计。同样地,在第四区34被分离为2个的情况下,第四区34的宽度为2个第四区34的宽度的合计。

[0038]

第二宽度w2和第四宽度w4各自例如为0.3μm以上且0.5μm以下。第二宽度w2和第四

宽度w4各自的上限没有特别限制,例如可以为1μm以下,也可以为2μm以下。第二宽度w2和第四宽度w4各自的下限没有特别限制,例如可以为0.2μm以上,也可以为0.1μm以上。

[0039]

第一区31和第三区33各自的杂质浓度例如为3

×

10

16

cm

‑3以上且3

×

10

17

cm

‑3以下。第一区31和第三区33各自的杂质浓度的上限没有特别限制,例如可以为5

×

10

17

cm

‑3以下,也可以为1

×

10

18

cm

‑3以下。第一区31和第三区33各自的杂质浓度的下限没有特别限制,例如可以为2

×

10

16

cm

‑3以上,也可以为1

×

10

16

cm

‑3以上。

[0040]

在将第一区31的杂质浓度设为第一浓度、将第二区32的杂质浓度设为第二浓度的情况下,将其中第一浓度乘以第一宽度w1而得的值除以其中第二浓度乘以第二宽度w2而得的值,由此得到的值(第一比率)为0.7以上且1.3以下。第一比率的上限没有特别限制,例如可以为1.4以下,也可以为1.5以下。第一比率的下限没有特别限制,例如可以为0.6以上,也可以为0.5以上。

[0041]

在将第三区33的杂质浓度设为第三浓度、将第四区34的杂质浓度设为第四浓度的情况下,将其中第三浓度乘以第三宽度w3而得的值除以其中第四浓度乘以第四宽度w4而得的值,由此得到的值(第二比率)为0.7以上且1.3以下。第二比率的上限没有特别限制,例如可以为1.4以下,也可以为1.5以下。第二比率的下限没有特别限制,例如可以为0.6以上,也可以为0.5以上。

[0042]

碳化硅衬底100包含第一下部漂移区15、第二下部漂移区25和第三下部漂移区91。第一下部漂移区15例如包含n等能够赋予n型的n型杂质。第一下部漂移区15具有n型。第一下部漂移区15与第一区31和第二区32的各自相接。第一下部漂移区15位于第一区31与第二主面2之间以及第二区32与第二主面2之间。第二下部漂移区25具有n型。第二下部漂移区25与第三区33和第四区34的各自相接。第二下部漂移区25位于第三区33与第二主面2之间以及第四区34与第二主面2之间。

[0043]

第三下部漂移区91例如包含n等能够赋予n型的n型杂质。第三下部漂移区91具有n型。第三下部漂移区91位于第一下部漂移区15与第二下部漂移区25之间。第三下部漂移区91与第一下部漂移区15和第二下部漂移区25的各自连接。第一下部漂移区15经由第三下部漂移区91与第二下部漂移区25电连接。

[0044]

如图1所示,第一区31、第二区32、第四区34和第三区33在与第二主面2平行的第一方向101上排列设置。第二区32位于第一区31与第四区34之间,并且第四区34位于第二区32与第三区33之间。如图1所示,第一主面1中设置有第一沟槽8。第一沟槽8将第二区32与第四区34隔开。第一沟槽8位于第二区32与第四区34之间。第一沟槽8具有第一侧面5、第一底面7和第二侧面6。第二侧面6与第一侧面5相对。第一侧面5和第二侧面6各自与第一主面1连接。第一底面7与第一侧面5和第二侧面6各自连接。

[0045]

第二区32具有第一端面17和第二端面3。第一端面17与第二杂质区12相接。第二端面3位于第一端面17的相反侧。第四区34具有第三端面27和第四端面4。第三端面27与第五杂质区22相接。第四端面4位于第三端面27的相反侧。如图1所示,在相对于第二主面2垂直的方向(第三方向103)上,第一沟槽8的第一底面7位于第二端面3与第二主面2之间,并且位于第四端面4与第二主面2之间。从其它观点来说,第一沟槽8的第一底面7位于相对于第二端面3和第四端面4的各自而言靠第二主面2侧的位置。

[0046]

第一接触区14、第二杂质区12、第二区32和第一下部漂移区15与第一侧面5相接。

第二接触区24、第五杂质区22、第四区34和第二下部漂移区25与第二侧面6相接。第三下部漂移区91与第一底面7相接。第二区32和第四区34各自与第一底面7间隔开。

[0047]

如图1所示,在从第二区32朝向第四区34的方向(第一方向101)上的第一沟槽8的宽度(第五宽度w5)例如为1μm以上且3μm以下。第一沟槽8的宽度的上限没有特别限制,例如可以为4μm以下,也可以为5μm以下。第一沟槽8的宽度的下限没有特别限制,例如可以为0.75μm以上,也可以为0.5μm以上。

[0048]

如图1所示,在碳化硅衬底100的厚度方向(第三方向103)上,第一沟槽8的深度(第一深度h1)例如为3μm以上且30μm以下。第一沟槽8的深度的上限没有特别限制,例如可以为50μm以下,也可以为100μm以下。第一沟槽8的深度的下限没有特别限制,例如可以为2μm以上,也可以为1μm以上。

[0049]

将第一沟槽8的深度(第一深度h1)除以从第二区32朝向第四区34的方向(第一方向101)上第一沟槽8的宽度(第五宽度w5)而得到的值(长宽比)例如为2以上且20以下。长宽比的上限没有特别限制,例如可以为1以上,也可以为0.5以上。长宽比的下限没有特别限制,例如可以为25以下,也可以为50以下。

[0050]

如图1所示,第一杂质区11与第一区31优选为一体。第一杂质区11与第一区31优选为一体。具体而言,在第一杂质区11与第一区31的边界区(3μm以上的区)中,沿第三方向103的n型杂质的浓度分布(将从最大浓度减去最小浓度而得的值除以平均浓度而得到的值)在10以内。优选第一杂质区11、第一区31与第一下部漂移区15无缝地连接。从其它观点来说,第一杂质区11、第一区31和第一下部漂移区15在一次外延生长工序中形成。

[0051]

同样地,第四杂质区21与第三区33优选为一体。具体而言,在第四杂质区21与第三区33的边界区(3μm以上的区)中,沿第三方向103的n型杂质的浓度分布(将从最大浓度减去最小浓度而得的值除以平均浓度而得到的值)在10以内。优选第四杂质区21、第三区33与第二下部漂移区25无缝地连接。从其它观点来说,第四杂质区21、第三区33和第二下部漂移区25在一次外延生长工序中形成。

[0052]

第一绝缘体80设置在第一沟槽8的内部。从其它观点来说,第一沟槽8被第一绝缘体80填埋。第一绝缘体80例如为bcb(benzo cyclo butene:苯并环丁烯)树脂。bcb树脂的耐热性、耐化学品性和埋入性优异。第一绝缘体80例如可以为sog(spin on glass:旋涂玻璃)膜或二氧化硅膜。

[0053]

如图1所示,第一杂质区11、第二杂质区12、第三杂质区13、第一接触区14、第一区31、第二区32和第一下部漂移区15可以构成第一台面区10。第四杂质区21、第五杂质区22、第六杂质区23、第二接触区24、第三区33、第四区34和第二下部漂移区25可以构成第二台面区20。第一台面区10与第二台面区20被第一绝缘体80分离。

[0054]

栅极绝缘膜51例如由二氧化硅构成。栅极绝缘膜51以与第一主面1相接的方式设置。栅极绝缘膜在第一主面1上与第一杂质区11、第二杂质区12和第三杂质区13各自相接。在与栅极绝缘膜51相接的第二杂质区12中构成为能够形成沟道。栅极绝缘膜在第一主面1上与第四杂质区21、第五杂质区22和第六杂质区23各自相接。在与栅极绝缘膜51相接的第五杂质区22中构成为能够形成沟道。栅极绝缘膜51的厚度例如为40nm以上且150nm以下。

[0055]

栅电极52设置在栅极绝缘膜51上。栅电极52配置成与栅极绝缘膜51接触。栅电极52例如由掺杂了杂质的多晶硅等导电体构成。

[0056]

分离绝缘膜53以覆盖栅电极52的方式设置。分离绝缘膜53与栅电极52和栅极绝缘膜51各自相接。分离绝缘膜53例如由nsg(none

‑

doped silicate glass:无掺杂硅酸盐玻璃)膜或psg(phosphorus silicate glass:磷硅酸盐玻璃)膜等构成。分离绝缘膜53将栅电极52与第一电极60电绝缘。

[0057]

第一电极60设置于第一主面1上。第一电极60例如为源电极。第一电极60与第三杂质区13和第六杂质区23各自电连接。第一电极60具有电极层61和源极配线62。电极层61例如由ni合金构成。电极层61例如由包含ti(钛)、al(铝)和si(硅)的材料构成。源极配线62例如由包含al的材料构成。

[0058]

第一电极60可以在第一主面1上与第三杂质区13和第六杂质区23各自相接。第一电极60可以在第一主面1上与第一接触区14和第二接触区24各自相接。第一电极60横跨在第一沟槽8上。第一电极60可以与第一绝缘体80相接。

[0059]

第二电极70设置于第二主面2上。第二电极70例如为漏电极。第二电极70与第一区31和第三区33各自电连接。第二电极70在第二主面2上与碳化硅单晶衬底50相接。第二电极70例如由nisi(硅化镍)等能够与n型的碳化硅单晶衬底50欧姆接合的材料构成。

[0060]

图2为沿图1的ii

‑

ii线得到的截面示意图。如图2所示,在与第二主面2垂直的方向观察时,第一沟槽8沿着第二方向102延伸。从其它观点来说,第一沟槽8的长度方向为第二方向102。第一沟槽8的宽度方向为第一方向101。同样地,第一绝缘体80沿着第二方向102延伸。从其它观点来说,第一绝缘体80的长度方向为第二方向102。第一绝缘体80的宽度方向为第一方向101。在与第二主面2垂直的方向观察时,第一沟槽8和第一绝缘体80各自可以实质上为长方形。

[0061]

如图2所示,第一杂质区11、第二杂质区12、第三杂质区13、第一接触区14、第四杂质区21、第五杂质区22、第六杂质区23和第二接触区24各自沿第二方向102延伸。从其它观点来说,第一杂质区11、第二杂质区12、第三杂质区13、第一接触区14、第四杂质区21、第五杂质区22、第六杂质区23和第二接触区24各自的长度方向为第二方向102。第一杂质区11、第二杂质区12、第三杂质区13、第一接触区14、第四杂质区21、第五杂质区22、第六杂质区23和第二接触区24各自的宽度方向为第一方向101。

[0062]

图3为沿图1的iii

‑

iii线得到的截面示意图。如图3所示,在与第二主面2垂直的方向观察时,第一区31和第二区32各自沿第二方向102延伸。从其它观点来说,第一区31和第二区32各自的长度方向为第二方向102。第一区31和第二区32各自的宽度方向为第一方向101。在第一方向101上,第二区32配置在第一区31的两侧。

[0063]

同样地,在与第二主面2垂直的方向观察时,第三区33和第四区34各自沿第二方向102延伸。从其它观点来说,第三区33和第四区34各自的长度方向为第二方向102。第三区33和第四区34各自的宽度方向为第一方向101。在第一方向101上,第四区34配置在第三区33的两侧。

[0064]

需要说明的是,在上述中,第一方向101和第二方向102各自与第二主面2平行。第三方向103相对于第二主面2垂直。第一方向101例如为<11

‑

20>方向。第二方向102例如为<1

‑

100>方向。第三方向103例如为<0001>方向。第一方向101例如可以是将<11

‑

20>方向投影到第一主面1上而得的方向。第二方向102例如可以是将<1

‑

100>方向投影到第一主面1上而得的方向。第三方向103例如可以是相对于<0001>方向倾斜的方向。

[0065]

图4为示出第一实施方式所涉及的碳化硅半导体器件200的构成的俯视示意图。在图4中仅图示了第一绝缘体80、第二绝缘体90、第一沟槽8、第二沟槽9和第一主面1,省略其它构成。

[0066]

如图4所示,在碳化硅衬底100的第一主面1中设置有多个第一沟槽8。多个第一沟槽8各自沿第二方向102延伸。多个第一沟槽8以沿第一方向101彼此间隔的方式配置。第一主面1中设置有第二沟槽9。如图4所示,在相对于第二主面2垂直的方向观察时,第二沟槽9为环状。在相对于第二主面2垂直的方向观察时,第二沟槽9包围第一沟槽8。

[0067]

碳化硅半导体器件200具有第二绝缘体90。第二绝缘体90设置在第二沟槽9的内部。在相对于第二主面2垂直的方向观察时,第二绝缘体90为环状。在相对于第二主面2垂直的方向观察时,第二绝缘体90包围第一绝缘体80。

[0068]

(第二实施方式)接着,对第二实施方式所涉及的碳化硅半导体器件200的构成进行说明。第二实施方式所涉及的碳化硅半导体器件200主要在第一区31和第三区33变狭窄的构成方面与第一实施方式所涉及的碳化硅半导体器件200不同,其它构成与第一实施方式所涉及的碳化硅半导体器件200相同。以下,以与第一实施方式所涉及的碳化硅半导体器件200不同的构成为中心进行说明。

[0069]

图5为示出第二实施方式所涉及的碳化硅半导体器件200的构成的截面示意图。如图5所示,第一沟槽8的第一侧面5与第二区32相接。第一侧面5从第二区32朝向第一区31凹陷。第一沟槽8的第二侧面6与第四区34相接。第二侧面6从第四区34朝向第三区33凹陷。第一侧面5和第二侧面6各自弯曲。

[0070]

如图5所示,在从第一主面1朝向第二主面2的方向上,第一区31的中央部的第一区31宽度可以小于第一区31的上端部的第一区31宽度,并且可以小于第一区31的下端部的第一区31宽度。在从第一区31朝向第二区32的方向上,第一区31的最大宽度(第六宽度w6)例如为0.5μm以上且5.0μm以下。在从第一区31朝向第二区32的方向上,第一区31的最小宽度(第七宽度w7)例如为0.3μm以上且3.0μm以下。

[0071]

在从第一区31朝向第二区32的方向上,从第一区31的最大宽度减去第一区31的最小宽度而得到的值(第一差)例如可以为0.2μm以上且0.5μm以下。对第一差的上限没有特别限制,例如可以为1.0μm以下,也可以为2.0μm以下。对第一差的下限没有特别限制,例如可以为0.1μm以上,也可以为0.05μm以上。

[0072]

如图5所示,在从第一主面1朝向第二主面2的方向上,第三区33的中央部的第三区33宽度可以小于第三区33的上端部的第三区33宽度,并且可以小于第三区33的下端部的第三区33宽度。在从第三区33朝向第四区34的方向上,第三区33的最大宽度(第八宽度w8)例如为0.5μm以上且5.0μm以下。在从第三区33朝向第四区34的方向上,第三区33的最小宽度(第9宽度w9)例如为0.3μm以上且3.0μm以下。

[0073]

在从第三区33朝向第四区34的方向上,从第三区33的最大宽度减去第三区33的最小宽度而得到的值(第二差)例如可以为0.2μm以上且0.5μm以下。对第二差的上限没有特别限制,例如可以为1.0μm以下,也可以为2.0μm以下。对第二差的下限没有特别限制,例如可以为0.1μm以上,也可以为0.05μm以上。

[0074]

(第三实施方式)

接着,对第三实施方式所涉及的碳化硅半导体器件200的构成进行说明。第三实施方式所涉及的碳化硅半导体器件200在为栅极沟槽型mosfet的构成方面与第一实施方式所涉及的碳化硅半导体器件200不同,其它构成与第一实施方式所涉及的碳化硅半导体器件200相同。以下,以与第一实施方式所涉及的碳化硅半导体器件200不同的构成为中心进行说明。

[0075]

图6为示出第三实施方式所涉及的碳化硅半导体器件200的构成的截面示意图。如图6所示,第三实施方式所涉及的碳化硅半导体器件200为栅极沟槽型mosfet。

[0076]

如图6所示,在第一主面1中设置有第一栅极沟槽74。第一栅极沟槽74具有第三侧面71、第四侧面72和第二底面73。第四侧面72与第三侧面71相对。第三侧面71和第四侧面72各自与第一主面1连接。第二底面73与第三侧面71和第四侧面72各自连接。第一栅极沟槽74的第二底面73位于比第一沟槽8的第一底面7浅的位置。从其它观点来说,在与第二主面2垂直的方向(第三方向103)上,第二底面73与第一主面1的距离比第一底面7与第一主面1的距离短。

[0077]

第一杂质区11、第二杂质区12和第三杂质区13各自在第三侧面71与栅极绝缘膜51相接。同样地,第一杂质区11、第二杂质区12和第三杂质区13各自在第四侧面72与栅极绝缘膜51相接。第一杂质区11在第二底面73与栅极绝缘膜51相接。第二区32可以与第三侧面71和第四侧面72各自相对。

[0078]

如图6所示,第一主面1中设置有第二栅极沟槽78。第二栅极沟槽78具有第五侧面75、第六侧面76和第三底面77。第六侧面76与第五侧面75相对。第五侧面75和第六侧面76各自与第一主面1连接。第三底面77与第五侧面75和第六侧面76各自连接。第二栅极沟槽78的第三底面77位于比第一沟槽8的第一底面7浅的位置。从其它观点来说,在与第二主面2垂直的方向(第三方向103)上,第三底面77与第一主面1的距离比第一底面7与第一主面1的距离短。

[0079]

第四杂质区21、第五杂质区22和第六杂质区23各自在第五侧面75与栅极绝缘膜51相接。同样地,第四杂质区21、第五杂质区22和第六杂质区23各自在第六侧面76与栅极绝缘膜51相接。第四杂质区21在第三底面77与栅极绝缘膜51相接。第四区34可以与第五侧面75和第六侧面76各自相对。

[0080]

接着,对各杂质区中的p型杂质的浓度和n型杂质的浓度的测定方法进行说明。

[0081]

各杂质区中的p型杂质的浓度和n型杂质的浓度可以使用sims(secondary ion mass spectrometry:二次离子质谱分析法)进行测定。测定装置例如为cameca公司制造的二次离子质谱装置。测定间距例如为0.01μm。在检测出的n型杂质为氮的情况下,一次离子束(primary ion beam)为铯(cs)。一次离子能量为14.5kev。二次离子的极性(secondary ion polarity)为负(negative)。在检测出的p型杂质为铝或硼的情况下,一次离子束(primary ion beam)为氧(o2)。一次离子能量为8kev。二次离子的极性(secondary ion polarity)为正(positive)。

[0082]

接着,对p型区和n型区的判别方法进行说明。在p型区与n型区的判别方法中使用scm(scanning capacitance microscope:扫描电容显微镜)。测定装置例如为bruker axs公司制造的nanoscope iv。scm是将半导体中的载流子浓度分布可视化的方法。具体而言,使用被金属涂覆的硅探针在试样的表面上进

行扫描。此时,对试样施加高频电压。激励大量载流子从而对体系的静电容量进行调制。施加到试样的高频电压的频率为100khz,电压为4.0v。

[0083]

(第四实施方式)接着,对第四实施方式所涉及的碳化硅半导体器件200的制造方法进行说明。

[0084]

首先,实施准备碳化硅衬底的工序(s10:图7)。例如,将通过改进瑞利法生长的碳化硅单晶锭切片而切出衬底,对衬底的表面进行镜面研磨,由此准备碳化硅单晶衬底50。碳化硅单晶衬底50例如为多型4h的六方晶碳化硅。碳化硅单晶衬底50的直径例如为150mm。

[0085]

接着,实施形成碳化硅外延层40的工序。例如,向碳化硅单晶衬底50上供给包含氢的载气,包含硅烷、丙烷的原料气体和包含氮的掺杂剂气体,在10kpa的压力下,将碳化硅单晶衬底50例如加热至约1550℃。由此,在碳化硅单晶衬底50上形成具有n型的碳化硅外延层40(参见图8)。

[0086]

由此,准备了包含碳化硅单晶衬底50和设置在碳化硅单晶衬底50上的碳化硅外延层40的碳化硅衬底100。碳化硅外延层40具有能够赋予n型(第一导电型)的杂质离子。碳化硅外延层40的第一主面1例如为{0001}面或从{0001}面偏离约8

°

以下的面。

[0087]

接着,对碳化硅外延层40实施离子注入。首先,对碳化硅外延层40离子注入p型杂质。由此,形成第一p型杂质区92。p型杂质例如为铝。接着,对第一p型杂质区92离子注入n型杂质。由此,形成第一n型杂质区93。第一n型杂质区93以与第一p型杂质区92相接的方式形成。n型杂质例如为磷。接着,对第一n型杂质区93离子注入p型杂质。由此,形成第二p型杂质区94。p型杂质例如为铝。第一p型杂质区92成为第二杂质区12和第五杂质区22。第一n型杂质区93成为第三杂质区13和第六杂质区23。第二p型杂质区94成为第一接触区14和第二接触区24。

[0088]

实施形成沟槽的工序(s20:图7)。首先,在第一主面1上形成掩模层54。掩模层54例如由包含沉积氧化膜的材料构成。在掩模层54中在形成第一沟槽8的区域上形成有开口。接着,使用掩模层54对碳化硅外延层40进行蚀刻。

[0089]

由此,在碳化硅外延层40中形成第一沟槽8(参见图10)。第一沟槽8具有第一侧面5、第二侧面6和第一底面7。第二侧面6与第一侧面5相对。第一底面7与第一侧面5和第二侧面6各自连接。第一沟槽8的深度(第一深度h1)例如为3μm以上且30μm以下。第一沟槽8的宽度(第五宽度w5)例如为1μm以上且3μm以下。

[0090]

接着,对蚀刻条件进行说明。作为沟槽内的由等离子体形成的侧壁的蚀刻保护膜,通过使用使得沉积到沟槽侧壁上的c沉积物足够多的条件,形成具有直线状的第一侧面5和第二侧面6的第一沟槽8(参见图1)。另一方面,通过使用使得沉积到沟槽侧壁上的c沉积物不足的条件,形成向两侧凸起的第一沟槽8(参见图5)。

[0091]

接着,实施倾斜离子注入工序(s30:图7)。具体而言,在第一主面1上配置有掩模层54的状态下,对第一沟槽8的第一侧面5例如倾斜注入铝等能够赋予p型(第二导电型)的杂质离子。由此,形成在第一侧面5露出的第二区32(参见图11)。接着,对第一沟槽8的第二侧面6例如倾斜注入铝等能够赋予p型的杂质离子。由此,形成在第二侧面6露出的第四区34(参见图12)。需要说明的是,也可以对第二侧面6倾斜注入能够赋予p型的杂质离子,然后对第一侧面5倾斜注入能够赋予p型的杂质离子。

[0092]

根据第三实施方式所涉及的碳化硅半导体器件200的制造方法,在形成第二区32

的工序和形成第四区34的工序的各自中,以不对底面7注入能够赋予第二导电型的杂质离子的方式进行倾斜注入。具体而言,在将第一沟槽8的宽度设为第五宽度w5、将第一沟槽8的深度设为第一深度h1、将掩模层54的厚度设为第一厚度h3、将第一厚度h3与第一深度h1的合计设为第二厚度h2的情况下,能够对第一侧面5与第一底面7的边界进行离子注入的角度(第一角度θ1)是由将第二厚度h2除以第五宽度w5而得到的值的反正切(arctangent)表示的角度(参见图11)。因此,为了对第一侧面5进行离子注入并且不对第一底面7进行离子注入,调节碳化硅衬底100与离子注入方向所成的角度,使得相对于与第一底面7平行的平面的角度成为小于第一角度θ1的角度(第二角度θ2)。

[0093]

如上所述,在碳化硅外延层40中形成第二区32和第四区34。被一对第二区32夹着的碳化硅外延层40的部分成为第一区31。被一对第四区34夹着的碳化硅外延层40的部分成为第三区33。在相对于碳化硅单晶衬底50与碳化硅外延层40的边界面45垂直的方向上,第一沟槽8的第二底面73位于第二区32与碳化硅单晶衬底50之间以及第四区34与碳化硅单晶衬底50之间。从其它观点来说,第一沟槽8的第二底面73位于比第二区32和第四区34的各自更靠第二主面2侧的位置。可以在倾斜离子注入工序(s30:图7)之后进行活化退火。

[0094]

碳化硅外延层40包含第一超结部16,所述第一超结部16包含具有n型的第一区31和具有p型的第二区32。第一区31与第二区32相接。第一区31和第二区32构成第一超结部16。碳化硅外延层40包含第二超结部26,所述第二超结部26包含具有n型的第三区33和具有p型的第四区34。第三区33与第四区34相接。第三区33和第四区34构成第二超结部26。在第一方向101上交替地配置有第一超结部16和第二超结部26。

[0095]

需要说明的是,如图11和图12所示,在倾斜离子注入工序(s30:图7)中,可以是对第二杂质区12、第三杂质区13、第一接触区14、第五杂质区22、第六杂质区23和第二接触区24各自的一部分注入能够赋予p型的杂质离子的一部分。

[0096]

接着,实施利用绝缘体填埋沟槽的工序(s40:图7)。例如在第一绝缘体80为bcb树脂或sog的情况下,通过旋涂法在第一沟槽8内形成第一绝缘体80。由此,第一沟槽8被第一绝缘体80填埋(参见图13)。

[0097]

接着,形成栅极绝缘膜51。具体而言,在第一主面1上形成栅极绝缘膜51。栅极绝缘膜51在第一主面1上与第一杂质区11、第二杂质区12和第三杂质区13相接。同样地,栅极绝缘膜51在第一主面1上与第四杂质区21、第五杂质区22和第六杂质区23相接。栅极绝缘膜51的厚度例如为40nm以上且150nm以下。

[0098]

接着,形成栅电极52。具体而言,在栅极绝缘膜51上形成栅电极52。栅电极52例如由包含含杂质的多晶硅的材料构成。接着,以覆盖栅电极52的方式形成分离绝缘膜53。分离绝缘膜53例如为二氧化硅膜(参见图14)。

[0099]

接着,形成第一电极60。第一电极60以横跨第一沟槽8的方式形成。具体而言,第一电极60以在第一主面1上与第三杂质区13、第一接触区14、第一绝缘体80、第二接触区24和第六杂质区23相接的方式形成。第一电极60包含电极层61。电极层61例如通过溅射形成。电极层61例如由包含ti、al和si的材料构成。

[0100]

接着,对形成有电极层61的碳化硅衬底100例如实施约2分钟的900℃以上且1100℃以下的rta(rapid thermal anneal:快速热退火)。由此,电极层61的至少一部分与碳化硅衬底100所含的硅反应而进行硅化物化。由此,电极层61与第三杂质区13和第六杂质区23

各自进行欧姆接合。优选电极层61与第一接触区14和第二接触区24各自进行欧姆接合。

[0101]

接着,形成源极配线62。源极配线62以横跨第一沟槽8的方式形成。具体而言,源极配线62以与电极层61相接并且覆盖第一绝缘体80的方式形成。源极配线62优选由含al的材料构成。接着,对碳化硅单晶衬底50进行背面研磨。由此,碳化硅单晶衬底50的厚度减少。

[0102]

接着,形成第二电极70。第二电极70与碳化硅衬底100的第二主面2相接而形成。第二电极70例如由含nisi的材料构成。第二电极70的形成优选通过溅射法来实施,但也可以通过蒸镀来实施。在形成第二电极70之后,第二电极70例如通过激光退火而被加热。由此,第二电极70的至少一部分进行硅化物化。如上所述,制造了图1所示的mosfet200。

[0103]

(第五实施方式)接着,对第五实施方式所涉及的碳化硅半导体器件200的制造方法进行说明。第五实施方式所涉及的碳化硅半导体器件200的制造方法主要在对第一沟槽8的第一底面7进行离子注入的工序方面与第四实施方式所涉及的碳化硅半导体器件200的制造方法不同,其它工序与第四实施方式所涉及的碳化硅半导体器件200的制造方法相同。以下,以与第四实施方式所涉及的碳化硅半导体器件200的制造方法不同的工序为中心进行说明。

[0104]

如图15所示,第五实施方式所涉及的碳化硅半导体器件200的形成沟槽8的工序(s20:图7)中的第一沟槽8的深度(第二深度h4)比第四实施方式所涉及的碳化硅半导体器件200的制造方法的形成沟槽8的工序(s20:图7)中的第一沟槽8的深度(第一深度h1)浅。第二深度h4例如为2.5μm以上且29.5μm以下。

[0105]

接着,实施倾斜离子注入工序(s30:图7)。具体而言,在第一主面1上配置有掩模层54的状态下,对第一沟槽8的第一侧面5和第一底面7例如倾斜注入铝等能够赋予p型(第二导电型)的杂质离子。由此,形成在第一侧面5和第一底面7露出的第二区32(参见图16)。接着,对第一沟槽8的第二侧面6和第一底面7例如倾斜注入铝等能够赋予p型的杂质离子。由此,形成在第二侧面6和第一底面7露出的第四区34(参见图17)。

[0106]

如上所述,根据第五实施方式所涉及的碳化硅半导体器件200的制造方法,在形成第二区32的工序和形成第四区34的工序的各自中,对底面7注入能够赋予第二导电型的杂质离子。

[0107]

接着,进行追加的蚀刻。具体而言,通过追加的蚀刻将对第一沟槽8的第一底面7注入的能够赋予p型的杂质离子除去。由此,第一沟槽8的深度从第二深度h4变成第一深度h1(参见图11)。结果,第一沟槽8的第一底面7向n型的第三下部漂移区91露出。如图11所示,在相对于碳化硅单晶衬底50与碳化硅外延层40的边界面45垂直的方向上,第一沟槽8的第一底面7位于第二区32与碳化硅单晶衬底50之间以及第四区34与碳化硅单晶衬底50之间。以后的工序与第四实施方式所涉及的碳化硅半导体器件200的制造方法相同。

[0108]

需要说明的是,在上述中,以第一导电型为n型并且第二导电型为p型的形式进行了说明,但第一导电型可以为p型并且第二导电型可以为n型。另外在上述中,以mosfet为例示对本公开内容所涉及的碳化硅半导体器件200进行了说明,但本公开内容所涉及的碳化硅半导体器件200不限于mosfet。本公开内容所涉及的碳化硅半导体器件200例如可以为igbt(insulated gate bipolar transistor:绝缘栅双极晶体管)等。

[0109]

接着,对上述实施方式所涉及的碳化硅半导体器件200及其制造方法的作用效果进行说明。

[0110]

如图17所示,在第二区32与第一沟槽8的第一底面7相接的情况下,位于比第一底面7更靠第二主面2侧的位置的第二区32的宽度大于位于比第一底面7更靠第一主面1侧的位置的第二区32的宽度。在此情况下,比第一底面7更靠第二主面2侧的第二区32与第一区31的电荷平衡、与比第一底面7更靠第一主面1侧的第二区32与第一区31的电荷平衡不同。同样地,比第一底面7更靠第二主面2侧的第四区34与第三区33的电荷平衡、与比第一底面7更靠第一主面1侧的第四区34与第三区33的电荷平衡不同。因此,第二区32与第一区31的电荷平衡以及第四区34与第三区33的电荷平衡各自变得无法获得平衡。即,难以良好地保持超结部的电荷平衡。

[0111]

另一方面,根据上述实施方式所涉及的碳化硅半导体器件200及其制造方法,在相对于第二主面2垂直的方向上,第一沟槽8的第一底面7位于第二区32的底面(第二端面3)与第二主面2之间,并且位于第四区34的底面(第四端面4)与第二主面2之间。在此情况下,第二区32与第一沟槽8的第一底面7间隔开。因此,与第二区32与第一沟槽8的第一底面7相接的情况不同,第二区32的宽度在相对于第二主面2垂直的方向上大致保持恒定。同样地,第四区34与第一沟槽8的第一底面7间隔开。因此,与第四区34与第一沟槽8的第一底面7相接的情况不同,第四区34的宽度在相对于第二主面2垂直的方向上大致保持恒定。结果,第二区32与第一区31的电荷平衡以及第四区34与第三区33的电荷平衡各自变得无法获得平衡的情形能够得到抑制。即,能够良好地保持超结部的电荷平衡。

[0112]

另外,深的超结部通常通过反复进行外延生长工序和离子注入工序来制造。然而,当使用该制造方法时,制造工序大幅变长,导致成本增加。另外,通过反复进行外延生长工序和离子注入工序,有时各外延层中的杂质浓度大为不同。

[0113]

另一方面,根据本实施方式所涉及的碳化硅半导体器件200的制造方法,在碳化硅外延层40中形成沟槽8,所述沟槽8具有第一侧面5和与第一侧面5相对的第二侧面6。通过对第一侧面5倾斜注入能够赋予第二导电型的杂质离子,形成第二区32。通过对第二侧面6倾斜注入能够赋予第二导电型的杂质离子,形成第四区34。由此,能够通过简易的方法制造深的超结部。因此,能够大幅缩短制造工序。

[0114]

另外,在外延生长工序为1次的情况下,与反复进行2次以上外延生长工序的情况相比,能够降低相对于第二主面2垂直的方向上的杂质浓度的偏差。因此,能够良好地保持超结部的电荷平衡。

[0115]

应该认为本次公开的实施方式在所有方面均为例示,而不是限制性的。本发明的范围不是由上述说明、而是由权利要求书示出,旨在包括与权利要求书等同的含义和范围内的所有变更。符号说明

[0116]

1第一主面,2第二主面,3第二端面,4第四端面,5第一侧面,6第二侧面,7第一底面(底面),8第一沟槽(沟槽),9第二沟槽,10第一台面区,11第一杂质区,12第二杂质区,13第三杂质区,14第一接触区,15第一下部漂移区,16第一超结部,17第一端面,20第二台面区,21第四杂质区,22第五杂质区,23第六杂质区,24第二接触区,25第二下部漂移区,26第二超结部,27第三端面,31第一区,32第二区,33第三区,34第四区,40碳化硅外延层,41第五区,42第六区,43第七区,44第八区,45边界面,50碳化硅单晶衬底,51栅极绝缘膜,52栅电极,53分离绝缘膜,54掩模层,60第一电极,61电极层,62源极配线,70第二电极,71第三侧面,72第

四侧面,73第二底面,74第一栅极沟槽,75第五侧面,76第六侧面,77第三底面,78第二栅极沟槽,80绝缘体(第一绝缘体),90第二绝缘体,91第三下部漂移区,92第一p型杂质区,93第一n型杂质区,94第二p型杂质区,100碳化硅衬底,101第一方向,102第二方向,103第三方向,200碳化硅半导体器件(mosfet),h1第一深度,h2第二厚度,h3第一厚度,h4第二深度,w1第一宽度,w2第二宽度,w3第三宽度,w4第四宽度,w5第五宽度,w6第六宽度,w7第七宽度,w8第八宽度,w9第9宽度。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。