1.本实用新型涉及电源板卡监测技术领域,具体地说是一种电源板卡监测电路。

背景技术:

2.随着科技技术不断进步,所有电子系统中包含的功能,内容,器件数量不断增多,电源系统的设计也变得越来越复杂。在目前的电源系统结构中,分布式电源拓扑(distributed power architecture,dpa)是使用比较广泛的,但是这种分布式电源结构也存在一个弊端,就是需要严格的电源管理。电源管理是指如何将电源有效分配给系统的不同组件,配置各个系统模块的上电时序,检测各个电源模块的输出状态等。

技术实现要素:

3.本实用新型的技术任务是针对以上不足之处,提供一种电源板卡监测电路,采用cpld作为电源管理的主控,并且采用简单的外围电路便实现了电源管理,结构简单,可应用在具备复杂电源系统的领域。

4.本实用新型解决其技术问题所采用的技术方案是:

5.一种电源板卡监测电路,采用cpld为电源管理主控,并设计其外部电路,包括电源上电时序控制电路和电源输出反馈正常电路;

6.所述电源上电时序控制电路包括光耦器件、n型三极管、n型mos管和分压电阻,在cpld控制信号输入端设置光耦器件,光耦器件输出端连接n型三极管,并通过n型三极管连接n型mos管,mos管的输出即为电源模块的输出电压;

7.当cpld控制信号为高电平的时候,光耦器件内部的发光二极管导通,使得光耦导通,进一步,使得n型三极管导通。n型三极管的导通使得n型mos管的栅极电压被下拉到gnd,n型mos管截止,电源模块的输出电压正常输出;当cpld控制信号为低电平的时候,n型mos管的栅极电压被上拉到控制电压vcc,n型mos管导通,电源模块的输出电压则不会有效输出;

8.所述电源输出反馈正常电路包括比较器和分压电阻,参考比较电压经电阻分压后进入比较器的负端;电源模块的输出电压经电阻分压后进入比较器的正端;当电源模块的输出电压的电压分量大于比较电压的电压分量时,比较器输出高电平,当电源模块的输出电压的电压分量小于比较电压的电压分量时,比较器输出低电平。

9.随着系统集成的密度越来越大,要求对电源的管理有更高的要求,其中对电源的上电时序和监测是重中之重。电源的上电顺序是非常之重要的,在调试中被发现出问题的机会很少。因此必须要对系统的电源进行统一管理。

10.cpld(complex programmable logic device)复杂可编程逻辑器件,是从pal和gal器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。因此,在超大规模的电源系统中,cpld的作用可以得以发挥。

11.优选的,所述cpld采用epm1270t144i5n芯片。

12.进一步的,所述比较器输出的高低电平进一步输入到cpld内部做下一步逻辑运算。

13.进一步的,控制电压端与所述n型mos管之间设置有分压电阻r1,cpld控制信号输入端与光耦器件之间设置有分压电阻r2;光耦器件与n型三极管之间设置有分压电阻。

14.优选的,所述r1和r2的阻值均为1kω;

15.所述光耦器件发射集与n型三极管基集之间连接电阻r3,n型三极管的发射集与基集之间连接r4;所述r3和r4的阻值均为2kω。

16.优选的,电源模块的输出电压经电阻r15分压后进入比较器的正端,r15阻值为1kω;

17.电源模块的输出电压经电阻r16分压后接地,r16阻值为4.7kω。

18.进一步的,所述比较器的输出端连接电阻r14,r14阻值为100ω。

19.优选的,电源芯片自身就带有电源使能引脚(enable),电源正常引脚(powergood)以及电源反馈引脚(feedback)时,直接将这三个引脚接在cpld的i/o上面,再进行软件编程配置。

20.本实用新型的一种电源板卡监测电路与现有技术相比,具有以下有益效果:

21.该监测电路采用cpld作为电源管理的主控,并通过对电源上电时序控制电路和电源输出反馈正常电路的设计,实现了通过cpld结合简单的外围电路便可实现电源管理。

22.该电路结构简单,可应用在具备复杂电源系统的领域。

附图说明

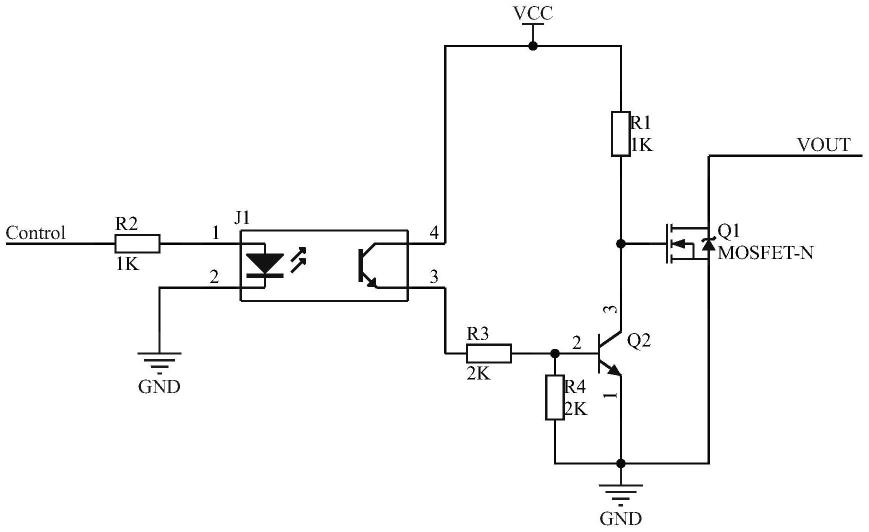

23.图1是本实用新型实施例提供的电源上电时序控制电路图;

24.图2是本实用新型实施例提供的电源输出反馈正常电路图。

具体实施方式

25.下面结合具体实施例对本发明作进一步说明。

26.本实用新型实施例提供一种电源板卡监测电路,采用cpld为电源管理主控,并设计其外部电路,包括电源上电时序控制电路和电源输出反馈正常电路;

27.所述电源上电时序控制电路包括光耦器件、n型三极管、n型mos管和分压电阻,在cpld控制信号输入端设置光耦器件,光耦器件输出端连接n型三极管,并通过n型三极管连接n型mos管,mos管的输出即为电源模块的输出电压;

28.所述电源输出反馈正常电路包括比较器和分压电阻,参考比较电压经电阻分压后进入比较器的负端;电源模块的输出电压经电阻分压后进入比较器的正端;当电源模块的输出电压的电压分量大于比较电压的电压分量时,比较器输出高电平,当电源模块的输出电压的电压分量小于比较电压的电压分量时,比较器输出低电平。比较器输出的高低电平进一步输入到cpld内部做下一步逻辑运算。

29.随着系统集成的密度越来越大,要求对电源的管理有更高的要求,其中对电源的上电时序和监测是重中之重。电源的上电顺序是非常之重要的,在调试中被发现出问题的机会很少。因此必须要对系统的电源进行统一管理。

30.cpld(complex programmable logic device)复杂可编程逻辑器件,是从pal和

gal器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。因此,在超大规模的电源系统中,cpld的作用可以得以发挥。

31.本实施例中,所述cpld采用epm1270t144i5n芯片。

32.如图1所示,为本实施例提供的电源上电时序控制电路:

33.j1为光耦器件,r1、r2、r3、r4为电阻,q1为n型mos管,q2为n型三极管。

34.control为cpld控制信号,vcc为控制电压,vout为电源模块的输出电压。

35.当control信号为高电平的时候,j1光耦内部的发光二极管导通,使得光耦导通,进一步,q2导通。q2的导通使得q1的栅极电压被下拉到gnd,q1截止,vout正常输出;当control信号为低电平的时候,q1的栅极电压被上拉到vcc,q1导通,vout则不会有效输出。

36.如图2所示,为本实施例提供的电源输出反馈正常电路,

37.u2为比较器,vref为参考比较电压,vout是电源模块输出电压,signal2是vref和vout比较后的反馈信号。

38.vref的参考电压经过r12和r13分压后进入比较器的负端,vout经过r15和r16分压后进入比较器的正端,当vout的电压分量大于vref的电压分量时,比较器输出高电平,当vout的电压分量小于vref的电压分量时,比较器输出低电平,输出的高低电平会进一步输入到cpld内部做下一步逻辑运算。

39.电源芯片自身就带有电源使能引脚(enable),电源正常引脚(powergood)以及电源反馈引脚(feedback)的情况,直接将这三个引脚接在cpld的i/o上面,再进行软件编程配置。

40.通过上面具体实施方式,所述技术领域的技术人员可容易的实现本实用新型。但是应当理解,本发明并不限于上述的具体实施方式。在公开的实施方式的基础上,所述技术领域的技术人员可任意组合不同的技术特征,从而实现不同的技术方案。

41.除说明书所述的技术特征外,均为本专业技术人员的已知技术。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。