1.本技术涉及处理器领域,尤其涉及一种基于栈空间特性的缓存处理方法、装置、电子设备及存储介质。

背景技术:

2.在现有技术中,当分配一段栈空间的时候,目前的设计都是等到cpu发起读写操作后才分配缓存。而且如果当前分配的栈空间大小刚好是缓存行对齐的,基于时效性特征,分配时该段空间保存的数据已经失效,但是cpu缓存控制器在数据缺失的情况下,通常仍然会从外部存储器中读取无效值,造成带宽浪费。当释放一段栈空间的时候,基于时效性特征,该段栈空间的数据已经是无效数据,如果该无效数据在缓存中的状态是脏数据,缓存控制器在对其执行替换操作的时候,仍然会将该无效数据写入外部存储器中,浪费外部带宽。

技术实现要素:

3.本技术实施例提供了一种基于栈空间特性的缓存处理方法、装置、电子设备及存储介质,用于在分配栈空间时,利用栈空间的局部性特征,能够提前为栈空间分配缓存,降低之后的访问延迟,利用栈空间的时效性特征,能够减少对外部存储器的带宽需求;在释放栈空间时,再次利用栈空间的时效性特征,提高缓存的利用率,并且由于避免了无效数据向外部存储器的写回操作,减少了对外部存储器的带宽需求。

4.本技术第一方面提供一种基于栈空间特性的缓存处理方法,可以包括:

5.通过中央处理器cpu分配栈空间;

6.在缓存行的数据缺失的情况下,为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充;

7.或,

8.读取多个缓存行的标志位;

9.在确定替换目标缓存行的情况下,若所述标志位无效,则直接无效化所述目标缓存行的数据,所述目标缓存行为所述多个缓存行中的一个。

10.本技术第二方面提供一种基于栈空间特性的缓存处理装置,其特征在于,包括:

11.处理器,用于通过中央处理器cpu分配栈空间;在缓存行的数据缺失的情况下,为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充;

12.或,

13.所述处理器,用于读取多个缓存行的标志位;在确定替换目标缓存行的情况下,若所述标志位无效,则直接无效化所述目标缓存行的数据,所述目标缓存行为所述多个缓存行中的一个。

14.本技术第三方面提供一种电子设备,包括:

15.存储有可执行程序代码的存储器;

16.与所述存储器耦合的处理器;

17.所述处理器用于对应执行如本技术第一方面所述的方法。

18.本技术实施例又一方面提供一种计算机可读存储介质,包括指令,当其在处理器上运行时,使得处理器执行本技术第一方面所述的方法。

19.本技术实施例又一方面公开一种计算机程序产品,当所述计算机程序产品在计算机上运行时,使得所述计算机执行本技术第一方面所述的方法。

20.本技术实施例又一方面公开一种应用发布平台,所述应用发布平台用于发布计算机程序产品,其中,当所述计算机程序产品在计算机上运行时,使得所述计算机执行本技术第一方面所述的方法。

21.从以上技术方案可以看出,本技术实施例具有以下优点:

22.在本技术实施例中,通过中央处理器cpu分配栈空间;在缓存行的数据缺失的情况下,为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充;或,读取多个缓存行的标志位;在确定替换目标缓存行的情况下,若所述标志位无效,则直接无效化所述目标缓存行的数据,所述目标缓存行为所述多个缓存行中的一个。用于在分配栈空间时,利用栈空间的局部性特征,能够提前为栈空间分配缓存,降低之后的访问延迟,利用栈空间的时效性特征,能够减少对外部存储器的带宽需求;在释放栈空间时,再次利用栈空间的时效性特征,提高缓存的利用率,并且由于避免了无效数据向外部存储器的写回操作,减少了对外部存储器的带宽需求。

附图说明

23.为了更清楚地说明本技术实施例技术方案,下面将对实施例和现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,还可以根据这些附图获得其它的附图。

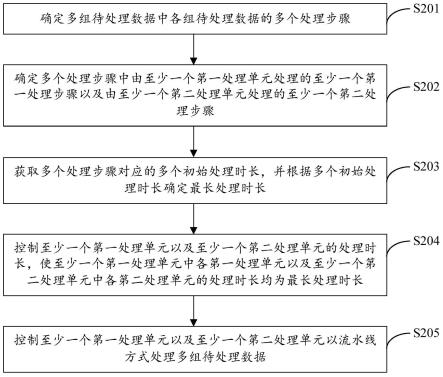

24.图1为一个n核的存储器层次结构的示意图;

25.图2为现有技术中cpu缓存的互斥机制的示意图;

26.图3为本技术实施例中基于栈空间特性的缓存处理方法的一个实施例示意图;

27.图4a为本技术实施例中栈空间分配过程的示意图;

28.图4b为本技术实施例中缓存控制器分配缓冲行过程的一个示意图;

29.图5为本技术实施例中基于栈空间特性的缓存处理方法的另一个实施例示意图;

30.图6a为本技术实施例中栈空间释放过程的示意图;

31.图6b为本技术实施例中缓存控制器替换缓存行的一个示意图;

32.图7为本技术实施例中基于栈空间特性的缓存处理装置的一个示意图;

33.图8为本技术实施例中电子设备的一个实施例示意图

34.图9所示,为本技术实施例中电子设备的另一个实施例示意图。

具体实施方式

35.本技术实施例提供了一种基于栈空间特性的缓存处理方法、装置、电子设备及存储介质,用于在分配栈空间时,利用栈空间的局部性特征,能够提前为栈空间分配缓存,降低之后的访问延迟,利用栈空间的时效性特征,能够减少对外部存储器的带宽需求;在释放栈空间时,再次利用栈空间的时效性特征,提高缓存的利用率,并且由于避免了无效数据向

外部存储器的写回操作,减少了对外部存储器的带宽需求。

36.为了使本技术领域的人员更好地理解本技术方案,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行描述,显然,所描述的实施例仅仅是本技术一部分的实施例,而不是全部的实施例。基于本技术中的实施例,都应当属于本技术保护的范围。

37.下面对本技术所涉及的一些术语做一个简要的说明,如下所示:

38.中央处理器(central processing unit,cpu)作为计算机系统的运算和控制核心,是信息处理、程序运行的最终执行单元。cpu自产生以来,在逻辑结构、运行效率以及功能外延上取得了巨大发展。

39.缓存(cache),原始意义是指访问速度比一般随机存取存储器(random access memory,ram)快的一种高速存储器,通常它不像系统主存那样使用动态随机存取存储器(dynamic random access memory,dram)技术,而使用昂贵但较快速的静态随机存取存储器(static random-access memory,sram)技术。缓存的设置是所有现代计算机系统发挥高性能的重要因素之一。

40.缓存(cache)中的数据是按块读取的,当中央处理器(central processor unit,cpu)访问某个数据时,会假设该数据附近的数据以后会被访问到,因此,第一次访问这一块区域时,会将该数据连同附近区域的数据(共64字节)一起读取进缓存中,那么这一块数据称为一个缓存行(cache line)。缓存系统是以缓存行为单位存储的。目前主流的cpu cache的cache line大小都是64字节。

41.随着处理器的性能越来越高,存储器性能逐渐变成了系统的重要瓶颈之一,为了尽可能地满足处理器的需求,同时为了平衡成本和性能,业界普遍采用一种存储器层次结构的设计方案。该方案利用软件的局部性原理,包含多级存储器。如图1所示,为一个n核的存储器层次结构的示意图。第一级存储器位于整个存储器层次的最高层,通常处于中央处理器(central processor unit,cpu)内部,称为l1缓存。为了区分指令和数据,l1缓存通常又分为l1指令缓存和l1数据缓存;第二级存储器通常也处于cpu内部,称为l2缓存;在多核的场景中为了降低多核对主存的带宽需求,cpu的设计往往会引入第三级缓存,称为l3缓存;除了cpu子系统以外,手机片上系统(system on chip,soc)一般也会包含图像处理器(graphic processor unit,gpu)等对数据带宽同样有着巨大需求的子系统,为了提高整个系统的带宽,第四级存储器也被称为系统缓存,应运而生,逐渐成为了高性能手机soc设计中不可或缺的一部分。第五级存储器和第六级存储器一般分别对应主存和闪存。基于该存储器结构,cpu访问外部存储器空间的时候会先从l1缓存开始寻找该地址的缓存,如果命中,则直接在缓存中对该地址进行相应的读或者写操作,反之如果l1缓存缺失,则向下一层l2缓存寻找,以逐级寻找的方式访问l1到l4,如果l1至l4的缓存都缺失,就需要从主存或者闪存中获得数据并且为该地址分配缓存,这样下次cpu再次访问该地址时就可以在l1至l4的缓存中对该地址直接进行操作,提高访问性能。

42.该存储器层次结构层次越高,性能越高,成本也越高。为了平衡性能和成本以及受限于缓存本身的限制,层次越高,设计能够实现的容量也越小。

43.由于cpu内部缓存所处层次最高,对整个系统的性能提升非常关键,但是受限于成本,频率等因素,容量很小。所以如何能够提高cpu缓存的利用率就显得尤为重要。为了实现该目的,目前的cpu设计中采取了很多方法。

44.1、cpu内部采用一种互斥的缓存策略提高缓存的利用率,采取互斥缓存策略的两个缓存层次间,同一个地址的缓存同一时刻最多只允许存在于一个缓存层次中。例如图2所示,为现有技术中cpu缓存的互斥机制的示意图。当core0发出一笔read a的访问时,在l1,l2,l3缓存都缺失的情况下,读访问会到达cpu外部的l4存储器,从l4返回的数据只会分配core0的l1缓存,而不会同时分配core0的l2缓存以及l3缓存。当然对于某些特殊情况,例如l1指令缓存和l2缓存之间采取的可以是非互斥机制,以及涉及到多核共享数据时,core0内部缓存和l3缓存之间也不再是互斥机制。最终的目的都是为了兼顾不同的场景需求的同时,尽可能地避免对同一地址空间分配多级缓存空间,从而避免缓存的重复率。

45.2、cpu提供了连续写检测机制以及暂时读写属性提高缓存的利用率,连续写检测机制是指当cpu检测到对大量的连续地址的写访问时,即使该类地址的属性允许分配缓存,cpu也不会实际为其分配缓存。因为在真实的应用场景中,软件经常会对连续的一段地址空间进行初始化,但是该段地址空间并不符合局部性原理,因此如果cpu仍然为这段地址空间分配缓存,会导致这些暂时不会用到的数据占用大量的缓存空间,严重降低缓存的利用率;暂时读写属性则是用来表示该地址只会在很短暂的时间内会被用到,缓存在需要进行替换或者清理操作的时候,可以结合该属性决定替换策略以及无效操作,避免无效数据占用缓存的时间,提高缓存的利用率。

46.现有技术为了提高缓存的命中率,采取了很多有效的方法,上文只列举了少数几种方法,仍然存在一些缺点。

47.cpu内部除了指令和普通的数据以外,还有一个特殊的概念—栈,栈表示一段连续的虚拟地址空间,该段虚拟地址空间用来保存中断和函数调用时的现场以及用来为局部变量分配地址。cpu内部的栈寄存器表征着当前栈空间的起始地址。栈空间有两个主要特征,其一是具备一定的局部性,其二是具备一定的时效性。局部性是指栈空间被分配后的一段较短的时间内就会被访问;时效性是指栈空间保存的数据只在其对应的栈空间释放之前的这段时间内才有效,一旦释放后,该段空间保存的数据就变成了无效数据,直到下一次再分配,重新写入新数据。

48.1、当分配一段栈空间的时候,目前的设计都是等到cpu发起读写操作后才分配缓存,并没有考虑栈的局部性特征,为其提前分配缓存。而且如果当前分配的栈空间大小刚好是缓存行对齐的,基于时效性特征,分配时该段空间保存的数据已经失效,但是cpu缓存控制器在数据缺失的情况下,通常仍然会从外部存储器中读取无效值,造成带宽浪费。

49.2、当释放一段栈空间的时候,基于时效性特征,该段栈空间的数据已经是无效数据,如果该无效数据在缓存中的状态是脏数据,缓存控制器在对其执行替换操作的时候,仍然会将该无效数据写入外部存储器中,浪费外部带宽。

50.本技术技术方案主要在对栈空间分配和释放的过程中利用栈空间的局部性特征和时效性特征提出相应的优化方案。其中,cpu对栈空间的分配和释放,都是通过对栈寄存器(stack pointer,sp)执行加减操作来实现的。本技术技术方案在分配栈空间时,利用栈空间的局部性特征,能够提前为栈空间分配缓存,降低之后的访问延迟;利用栈空间的时效性特征,能够减少对外部存储器的带宽需求。在释放栈空间时,再次利用栈空间的时效性特征,提高缓存的利用率,并且由于避免了无效数据向外部存储器的写回操作,减少了对外部存储器的带宽需求。

51.下面以实施例的方式,对本技术技术方案做进一步的说明,如图3所示,为本技术实施例中基于栈空间特性的缓存处理方法的一个实施例示意图,可以包括:

52.301、通过中央处理器cpu分配栈空间。

53.可以理解的是,cpu对栈空间的分配,是通过对栈寄存器(stack pointer,sp)执行加操作来实现的。

54.分配栈空间时的方案为:如图4a所示,为本技术实施例中栈空间分配过程的示意图。由于栈的向下增长性,当对栈寄存器(stack pointer,sp)执行减法操作(subtract,sub)时即为分配过程,被减数(#8)即为当前分配的字节数,栈寄存器指向的地址由执行减法操作前的0x108变为0x100,0x100-0x107即为新分配的栈空间。新分配的栈空间大小,是由编译器决定的,翻译成指令,为8或16。

55.302、在缓存行的数据缺失的情况下,为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充。

56.可选的,所述在缓存行的数据缺失的情况下,电子设备为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充,可以包括:在缓存行的数据缺失的情况下,电子设备通过缓存控制器为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充。

57.可选的,所述方法还可以包括:电子设备获取读/写请求;电子设备根据所述读/写请求在所述缓存行中进行读/写。

58.示例性的,基于局部性特征,本技术采取一种方案,即cpu在分配栈空间的同时,发起对缓存的预取操作,提前从外部存储器读取数据进行缓存行填充,这之后对该栈空间的读写操作就可以直接在缓存中进行了。例如,根据新分配的栈空间0x100-0x107地址,从外部存储器读取数据,对所述缓存行填充。

59.可选的,所述在缓存行的数据缺失的情况下,电子设备为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充,可以包括:在所述缓存行的数据缺失,且所述栈空间不是缓存行对齐的情况下,电子设备为所述栈空间分配缓存行,并从外部存储器读取数据对所述缓存行填充。

60.可选的,所述在所述缓存行的数据缺失,且所述栈空间不是缓存行对齐的情况下,电子设备为所述栈空间分配缓存行,并从外部存储器读取数据对所述缓存行填充,可以包括:在所述缓存行的数据缺失,且所述栈空间不是缓存行对齐的情况下,电子设备通过缓存控制器为所述栈空间分配缓存行,并从外部存储器读取数据对所述缓存行填充。

61.可选的,所述方法还可以包括:在所述缓存行的数据缺失,且所述栈空间是缓存行对齐的情况下,电子设备为所述栈空间分配缓存。

62.可选的,所述在所述缓存行的数据缺失,且所述栈空间是缓存行对齐的情况下,电子设备为所述栈空间分配缓存,可以包括:在所述缓存行的数据缺失,且所述栈空间是缓存行对齐的情况下,电子设备通过缓存控制器为所述栈空间分配缓存。

63.示例性的,如果当前分配的栈空间大小是缓存行对齐的,基于时效性特征,可以将上述方案中的预取操作简化为只分配缓存。如图4b所示,为本技术实施例中缓存控制器分配缓冲行过程的一个示意图。图4b中增加了对栈空间是否是缓存行对齐的条件判断,如果是,则只分配缓存,不再发起一笔读外部存储器的操作,因为此时外部存储器保存的数据都

是无效数据。

64.可选的,上述方案中缓存控制器操作前需要判断分配的栈空间是否是缓存行对齐的。如果对栈空间增加一条限制:分配的栈空间必须是缓存行对齐的,则能够省略这一判断。

65.在本技术实施例中,通过中央处理器cpu分配栈空间;在缓存行的数据缺失的情况下,为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充;用于在分配栈空间时,利用栈空间的局部性特征,能够提前为栈空间分配缓存,降低之后的访问延迟,利用栈空间的时效性特征,能够减少对外部存储器的带宽需求。

66.如图5所示,为本技术实施例中基于栈空间特性的缓存处理方法的另一个实施例示意图,可以包括:

67.501、读取多个缓存行的标志位。

68.可以理解的是,对栈空间的释放,是通过对栈寄存器(stack pointer,sp)执行减操作来实现的。

69.释放栈空间时的方案为:如图6a所示,为本技术实施例中栈空间释放过程的示意图。对sp执行加法操作(add)即为释放过程,如图6a所示,sp指向的地址由0x100变为0x108,原分配的0x100-0x107地址空间被释放,此时地址0x100到地址0x107中保存的数据成为了无效数据。

70.基于时效性特征,本技术技术方案通过在缓存的标记位中增加一位标志位,表征当前的缓存行数据是否是无效数据。本技术中称该标志位为数据无效位,数据无效位设为1,表示数据无效;数据无效位设为0,表示该位不起作用。栈空间释放时,如果释放的空间刚好是缓存行对齐的,就将数据无效位设为1,表示数据无效;栈空间再次被分配时,将数据无效位设为0。

71.502、在确定替换目标缓存行的情况下,若所述标志位无效,则直接无效化所述目标缓存行的数据,所述目标缓存行为所述多个缓存行中的一个。

72.可以理解的是,该多个缓存行中已存满数据,没有多余的存储空间。

73.可选的,所述在确定替换目标缓存行的情况下,若所述标志位无效,则电子设备直接无效化所述目标缓存行的数据,可以包括:在确定替换目标缓存行的情况下,若所述标志位无效,则电子设备通过缓存控制器直接无效化所述目标缓存行的数据。

74.503、若所述标志位有效,则判断所述目标缓存行的数据是否是脏数据。

75.504、若是脏数据,则写回至外部存储器。

76.505、若不是脏数据,则直接无效化所述目标缓存行的数据。

77.可选的,所述若所述标志位有效,则电子设备判断所述目标缓存行的数据是否是脏数据;若是脏数据,则电子设备写回至外部存储器;若不是脏数据,则电子设备直接无效化所述目标缓存行的数据,可以包括:若所述标志位有效,则电子设备通过缓存控制器判断所述目标缓存行的数据是否是脏数据;若是脏数据,则电子设备通过缓存控制器写回至外部存储器;若不是脏数据,则电子设备通过缓存控制器直接无效化所述目标缓存行的数据。

78.可选的,所述方法还可以包括:在栈空间释放时,如果释放的空间是缓冲行对齐,电子设备将数据无效位设为1,表示数据无效。

79.可选的,所述在栈空间释放时,如果释放的空间是缓冲行对齐,电子设备将数据无

效位设为1,表示数据无效,可以包括:在栈空间释放时,如果释放的空间是缓冲行对齐,电子设备通过缓存控制器将数据无效位设为1,表示数据无效。

80.可选的,所述方法还可以包括:在栈空间再次被分配时,电子设备将数据无效位设为0,表示不起作用。

81.可选的,所述在栈空间再次被分配时,电子设备将数据无效位设为0,表示不起作用,可以包括:在栈空间再次被分配时,电子设备通过缓存控制器将数据无效位设为0,表示不起作用。

82.示例性的,增加数据无效位后,如图6b所示,为本技术实施例中缓存控制器替换缓存行的一个示意图。缓存控制器首先读取缓存行的标记位,然后决定当前替换的缓存行,再判断缓存行的数据无效位是否有效,如果为1,则不管该数据是否是脏数据,缓存控制器都不会将其写入外部存储器中,而直接将其无效化,避免了正常流程中额外对外部存储器的写回操作。

83.需要说明的是,步骤503-505为可选的步骤。

84.可选的,上述方案中缓存控制器操作前需要判断释放的栈空间是否是缓存行对齐的。如果对栈空间增加一条限制:分配的栈空间必须是缓存行对齐的,则能够省略这一判断。

85.在本技术实施例中,读取多个缓存行的标记位;在确定替换目标缓存行的情况下,若所述标记位无效,则直接无效化所述目标缓存行的数据,所述目标缓存行为所述多个缓存行中的一个。用于在释放栈空间时,再次利用栈空间的时效性特征,提高缓存的利用率,并且由于避免了无效数据向外部存储器的写回操作,减少了对外部存储器的带宽需求。

86.需要说明的是,图3所示的实施例与图5所示的实施例结合起来的实施例,也在本技术的保护范围内,此处不再赘述。

87.本技术技术方案基于现有技术的特点,创新性地利用栈空间的局部性特征和时效性特征,提前为栈空间分配缓存,降低延时,并且避免了对外部存储器冗余的读取操作;同时通过在缓存行的标记位中增加一位标志位,用来表征栈空间的释放操作,缓存控制器通过该标志位能够将栈释放的数据直接无效化,避免了写外部存储器的操作。

88.如图7所示,为本技术实施例中基于栈空间特性的缓存处理装置的一个示意图,可以包括:

89.处理器701,用于通过中央处理器cpu分配栈空间;在缓存行的数据缺失的情况下,为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充;

90.或,

91.处理器701,用于读取多个缓存行的标志位;在确定替换目标缓存行的情况下,若所述标志位无效,则直接无效化所述目标缓存行的数据,所述目标缓存行为所述多个缓存行中的一个。

92.可选的,处理器701,具体用于在所述缓存行的数据缺失,且所述栈空间不是缓存行对齐的情况下,为所述栈空间分配缓存行,并从外部存储器读取数据对所述缓存行填充。

93.可选的,处理器701,还用于在所述缓存行的数据缺失,且所述栈空间是缓存行对齐的情况下,为所述栈空间分配缓存。

94.可选的,处理器701,还用于获取读/写请求;根据所述读/写请求在所述缓存行中

进行读/写。

95.可选的,处理器701,还用于若所述标志位有效,则判断所述目标缓存行的数据是否是脏数据;若是脏数据,则写回至外部存储器;若不是脏数据,则直接无效化所述目标缓存行的数据。

96.可选的,处理器701,还用于在栈空间释放时,如果释放的空间是缓冲行对齐,将数据无效位设为1,表示数据无效。

97.可选的,处理器701,还用于在栈空间再次被分配时,将数据无效位设为0,表示不起作用。

98.如图8所示,为本技术实施例中电子设备的一个实施例示意图,包括如图7所示的基于栈空间特性的缓存处理装置。

99.如图9所示,为本技术实施例中电子设备的另一个实施例示意图,可以包括:

100.图9示出的是与本技术实施例提供的电子设备相关的手机的部分结构的框图。参考图9,手机包括:射频(radio frequency,rf)电路910、存储器920、输入单元930、显示单元940、传感器950、音频电路960、无线保真(wireless fidelity,wi-fi)模块970、处理器980、以及电源990等部件。本领域技术人员可以理解,图9中示出的手机结构并不构成对手机的限定,可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。

101.下面结合图9对手机的各个构成部件进行具体的介绍:

102.rf电路910可用于收发信息或通话过程中,信号的接收和发送,特别地,将基站的下行信息接收后,给处理器980处理;另外,将设计上行的数据发送给基站。通常,rf电路910包括但不限于天线、至少一个放大器、收发信机、耦合器、低噪声放大器(low noise amplifier,lna)、双工器等。此外,rf电路910还可以通过无线通信与网络和其他设备通信。上述无线通信可以使用任一通信标准或协议,包括但不限于全球移动通讯系统(global system of mobile communication,gsm)、通用分组无线服务(general packet radio service,gprs)、码分多址(code division multiple access,cdma)、宽带码分多址(wideband code division multiple access,wcdma)、长期演进(long term evolution,lte)、电子邮件、短消息服务(short messaging service,sms)等。

103.存储器920可用于存储软件程序以及模块,处理器980通过运行存储在存储器920的软件程序以及模块,从而执行手机的各种功能应用以及数据处理。存储器920可主要包括存储程序区和存储数据区,其中,存储程序区可存储操作系统、至少一个功能所需的应用程序(比如声音播放功能、图像播放功能等)等;存储数据区可存储根据手机的使用所创建的数据(比如音频数据、电话本等)等。此外,存储器920可以包括高速随机存取存储器,还可以包括非易失性存储器,例如至少一个磁盘存储器件、闪存器件、或其他易失性固态存储器件。

104.输入单元930可用于接收输入的数字或字符信息,以及产生与手机的用户设置以及功能控制有关的键信号输入。具体地,输入单元930可包括触控面板931以及其他输入设备932。触控面板931,也称为触摸屏,可收集用户在其上或附近的触摸操作(比如用户使用手指、触笔等任何适合的物体或附件在触控面板931上或在触控面板931附近的操作),并根据预先设定的程式驱动相应的连接装置。可选的,触控面板931可包括触摸检测装置和触摸控制器两个部分。其中,触摸检测装置检测用户的触摸方位,并检测触摸操作带来的信号,

将信号传送给触摸控制器;触摸控制器从触摸检测装置上接收触摸信息,并将它转换成触点坐标,再送给处理器980,并能接收处理器980发来的命令并加以执行。此外,可以采用电阻式、电容式、红外线以及表面声波等多种类型实现触控面板931。除了触控面板931,输入单元930还可以包括其他输入设备932。具体地,其他输入设备932可以包括但不限于物理键盘、功能键(比如音量控制按键、开关按键等)、轨迹球、鼠标、操作杆等中的一种或多种。

105.显示单元940可用于显示由用户输入的信息或提供给用户的信息以及手机的各种菜单。显示单元940可包括显示面板941,可选的,可以采用液晶显示器(liquid crystal display,lcd)、有机发光二极管(organic light-emitting diode,oled)等形式来配置显示面板941。进一步的,触控面板931可覆盖显示面板941,当触控面板931检测到在其上或附近的触摸操作后,传送给处理器980以确定触摸事件的类型,随后处理器980根据触摸事件的类型在显示面板941上提供相应的视觉输出。虽然在图9中,触控面板931与显示面板941是作为两个独立的部件来实现手机的输入和输入功能,但是在某些实施例中,可以将触控面板931与显示面板941集成而实现手机的输入和输出功能。

106.手机还可包括至少一种传感器950,比如光传感器、运动传感器以及其他传感器。具体地,光传感器可包括环境光传感器及接近传感器,其中,环境光传感器可根据环境光线的明暗来调节显示面板941的亮度,接近传感器可在手机移动到耳边时,关闭显示面板941和/或背光。作为运动传感器的一种,加速计传感器可检测各个方向上(一般为三轴)加速度的大小,静止时可检测出重力的大小及方向,可用于识别手机姿态的应用(比如横竖屏切换、相关游戏、磁力计姿态校准)、振动识别相关功能(比如计步器、敲击)等;至于手机还可配置的陀螺仪、气压计、湿度计、温度计、红外线传感器等其他传感器,在此不再赘述。

107.音频电路960、扬声器961,传声器962可提供用户与手机之间的音频接口。音频电路960可将接收到的音频数据转换后的电信号,传输到扬声器961,由扬声器961转换为声音信号输出;另一方面,传声器962将收集的声音信号转换为电信号,由音频电路960接收后转换为音频数据,再将音频数据输出处理器980处理后,经rf电路910以发送给比如另一手机,或者将音频数据输出至存储器920以便进一步处理。

108.wi-fi属于短距离无线传输技术,手机通过wi-fi模块970可以帮助用户收发电子邮件、浏览网页和访问流式媒体等,它为用户提供了无线的宽带互联网访问。虽然图9示出了wi-fi模块970,但是可以理解的是,其并不属于手机的必须构成,完全可以根据需要在不改变申请的本质的范围内而省略。

109.处理器980是手机的控制中心,利用各种接口和线路连接整个手机的各个部分,通过运行或执行存储在存储器920内的软件程序和/或模块,以及调用存储在存储器920内的数据,执行手机的各种功能和处理数据,从而对手机进行整体监控。可选的,处理器980可包括一个或多个处理单元;优选的,处理器980可集成应用处理器和调制解调处理器,其中,应用处理器主要处理操作系统、用户界面和应用程序等,调制解调处理器主要处理无线通信。可以理解的是,上述调制解调处理器也可以不集成到处理器980中。

110.手机还包括给各个部件供电的电源990(比如电池),优选的,电源可以通过电源管理系统与处理器980逻辑相连,从而通过电源管理系统实现管理充电、放电、以及功耗管理等功能。

111.尽管未示出,手机还可以包括摄像头、蓝牙模块等,在此不再赘述。

112.在本技术实施例中,处理器980,用于通过中央处理器cpu分配栈空间;在缓存行的数据缺失的情况下,为所述栈空间分配缓存,并从外部存储器读取数据对所述缓存行填充;

113.或,

114.处理器980,用于读取多个缓存行的标志位;在确定替换目标缓存行的情况下,若所述标志位无效,则直接无效化所述目标缓存行的数据,所述目标缓存行为所述多个缓存行中的一个。

115.可选的,处理器980,具体用于在所述缓存行的数据缺失,且所述栈空间不是缓存行对齐的情况下,为所述栈空间分配缓存行,并从外部存储器读取数据对所述缓存行填充。

116.可选的,处理器980,还用于在所述缓存行的数据缺失,且所述栈空间是缓存行对齐的情况下,为所述栈空间分配缓存。

117.可选的,处理器980,还用于获取读/写请求;根据所述读/写请求在所述缓存行中进行读/写。

118.可选的,处理器980,还用于若所述标志位有效,则判断所述目标缓存行的数据是否是脏数据;若是脏数据,则写回至外部存储器;若不是脏数据,则直接无效化所述目标缓存行的数据。

119.可选的,处理器980,还用于在栈空间释放时,如果释放的空间是缓冲行对齐,将数据无效位设为1,表示数据无效。

120.可选的,处理器980,还用于在栈空间再次被分配时,将数据无效位设为0,表示不起作用。

121.本技术中所涉及的电子设备可以是终端设备,也可以是其他使用射频pa的电子设备。其中,终端设备可称之为用户设备(user equipment,ue)、移动台(mobile station,ms)、移动终端(mobile terminal)、智能终端等,所述终端设备可以经无线接入网(radio access network,ran)与一个或多个核心网进行通信。例如,终端设备可以是移动电话(或称为“蜂窝”电话)、具有移动终端的计算机等,终端设备还可以是便携式、袖珍式、手持式、计算机内置的或者车载的移动装置以及未来新无线(new radio,nr)网络中的终端设备,它们与无线接入网交换语音或数据。对终端设备的说明:本技术中,终端设备还可以包括中继relay,和基站可以进行数据通信的都可以看为终端设备,本技术中将以一般意义上的ue来介绍。

122.在上述实施例中,可以全部或部分地通过软件、硬件、固件或者其任意组合来实现。当使用软件实现时,可以全部或部分地以计算机程序产品的形式实现。所述计算机程序产品包括一个或多个计算机指令。在计算机上加载和执行所述计算机程序指令时,全部或部分地产生按照本发明实施例所述的流程或功能。所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。所述计算机指令可以存储在计算机可读存储介质中,或者从一个计算机可读存储介质向另一计算机可读存储介质传输,例如,所述计算机指令可以从一个网站站点、计算机、服务器或数据中心通过有线(例如同轴电缆、光纤、数字用户线(dsl))或无线(例如红外、无线、微波等)方式向另一个网站站点、计算机、服务器或数据中心进行传输。所述计算机可读存储介质可以是计算机能够存储的任何可用介质或者是包含一个或多个可用介质集成的服务器、数据中心等数据存储设备。所述可用介质可以是磁性介质,(例如,软盘、硬盘、磁带)、光介质(例如,dvd)、或者半导体介质(例如固态硬盘

solid state disk(ssd))等。

123.所属领域的技术人员可以清楚地了解到,为描述的方便和简洁,上述描述的系统,装置和单元的具体工作过程,可以参考前述方法实施例中的对应过程,在此不再赘述。

124.在本技术所提供的几个实施例中,应该理解到,所揭露的系统,装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

125.所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

126.另外,在本技术各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。上述集成的单元既可以采用硬件的形式实现,也可以采用软件功能单元的形式实现。

127.所述集成的单元如果以软件功能单元的形式实现并作为独立的产品销售或使用时,可以存储在一个计算机可读取存储介质中。基于这样的理解,本技术的技术方案本质上或者说对现有技术做出贡献的部分或者该技术方案的全部或部分可以以软件产品的形式体现出来,该计算机软件产品存储在一个存储介质中,包括若干指令用以使得一台计算机设备(可以是个人计算机,服务器,或者网络设备等)执行本技术各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器(rom,read-only memory)、随机存取存储器(ram,random access memory)、磁碟或者光盘等各种可以存储程序代码的介质。

128.以上所述,以上实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。