1.本发明涉及数据处理技术领域,具体涉及一种数据处理方法、装置、电子设备及可读存储介质。

背景技术:

2.随着大数据时代的到来,数据处理的适用场景越来越多,也越来越重要,而数据处理速度是数据处理的关键指标。

3.现有技术中的数据处理方法如图1所示,需要上一组获取的数据处理完成后,才能进行下一组数据的处理,若假设每个数据处理过程耗时分别为t1、t2…

tn,则完成1组数据处理的总耗时为t=t1 t2

…

tn,完成m组数据处理的总耗时tm=(t1 t2

…

tn)*m。由于每次都需要等到上一组获取的数据完成才能进行下一组数据的处理,当数据的组数较多时,数据处理速度慢。并且,由于各个数据处理过程的耗时存在不相同,若后面的步骤耗时较长(即处理的较慢),则前面步骤处理的数据会比后面处理的速度快,可能会造成后面步骤的数据堵塞或者覆盖,造成运算出错。

4.因此,急需提供一种数据处理方法、装置、电子设备及可读存储介质,用以解决现有技术中存在的数据处理速度慢以及各数据处理时长不同,导致某些数据处理步骤易发生数据堵塞或覆盖的问题,进而造成数据处理出错的技术问题。

技术实现要素:

5.有鉴于此,有必要提供一种数据处理方法、装置、电子设备及可读存储介质,用以解决现有技术中存在的数据处理速度慢以及各数据处理时长不同,导致某些数据处理步骤易发生数据堵塞或覆盖的问题,进而造成数据处理出错的技术问题。

6.一方面,本发明提供了一种数据处理方法,用于基于现场可编程门阵列和微处理器对多组待处理数据进行处理,所述现场可编程门阵列包括至少一个第一处理单元,所述微处理器包括至少一个第二处理单元;所述数据处理方法包括:

7.确定多组待处理数据中各组所述待处理数据的多个处理步骤;

8.确定所述多个处理步骤中由所述至少一个第一处理单元处理的至少一个第一处理步骤以及由所述至少一个第二处理单元处理的至少一个第二处理步骤;

9.获取所述多个处理步骤对应的多个初始处理时长,并根据所述多个初始处理时长确定最长处理时长;

10.控制所述至少一个第一处理单元中各第一处理单元以及所述至少一个第二处理单元中各第二处理单元的处理时长,使所述第一处理单元以及所述第二处理单元的处理时长均为所述最长处理时长;

11.控制所述至少一个第一处理单元以及所述至少一个第二处理单元以流水线方式处理所述多组待处理数据。

12.在一些可能的实现方式中,所述确定多组待处理数据中各组所述待处理数据的多

个处理步骤,包括:

13.基于预设的划分规则确定所述待处理数据的多个初始处理步骤;

14.基于预设的合并规则对所述多个初始处理步骤进行合并,获得所述多个处理步骤。

15.在一些可能的实现方式中,所述确定所述多个处理步骤中由所述至少一个第一处理单元处理的至少一个第一处理步骤以及由所述至少一个第二处理单元处理的至少一个第二处理步骤,包括:

16.获取所述多个处理步骤中各处理步骤的步骤特征;

17.基于预设的划分规则以及所述步骤特征确定所述多个处理步骤中由所述至少一个第一处理单元处理的至少一个第一处理步骤以及由所述至少一个第二处理单元处理的至少一个第二处理步骤。

18.在一些可能的实现方式中,所述控制所述至少一个第一处理单元以及所述至少一个第二处理单元的处理时长,使所述至少一个第一处理单元中各第一处理单元以及所述至少一个第二处理单元中各第二处理单元的处理时长均为所述最长处理时长,包括:

19.获取各所述第一处理单元以及各所述第二处理单元的初始处理时长;

20.根据所述初始处理时长和所述最长处理时长确定处理时长差值;

21.根据所述处理时长差值控制各所述第一处理单元以及各所述第二处理单元的开始与停止,使各所述第一处理单元以及各所述第二处理单元的处理时长均为所述最长处理时长。

22.在一些可能的实现方式中,所述多组待处理数据包括第一待处理数据和第二待处理数据,所述第一待处理数据和所述第二待处理数据均包括顺序排布的第一目标处理步骤和第二目标处理步骤,所述至少一个第一处理单元包括处理所述第一目标处理步骤的第一目标处理单元,所述至少一个第二处理单元包括处理所述第二目标处理步骤的第二目标处理单元。

23.在一些可能的实现方式中,所述控制所述至少一个第一处理单元以及所述至少一个第二处理单元以流水线方式处理所述多组待处理数据,包括:

24.获取处理信号,所述第一目标处理单元响应所述处理信号,并处理所述第一待处理数据的第一目标处理步骤,且当所述第一待处理数据的第一目标处理步骤处理完成后,生成第一处理完成信号;

25.所述第二目标处理单元响应所述第一处理完成信号,并处理所述第一待处理数据的第二目标处理步骤,且当所述第一待处理数据的第二目标处理步骤处理完成后,生成第二处理完成信号;

26.所述第一目标处理单元响应所述第一处理完成信号,并处理所述第二待处理数据的第一目标处理步骤;

27.所述第二目标处理单元响应所述第二处理完成信号,并处理所述第二待处理数据的第二目标处理步骤。

28.在一些可能的实现方式中,所述多组待处理数据包括m组待处理数据,所述待处理数据包括n个处理步骤,则所述数据处理方法还包括:

29.构建与n个所述处理步骤一一对应的n个存储区;

30.获取各组所述待处理数据的处理结果;

31.将第i*n j组待处理数据存储至第j个存储区;

32.其中,i=0,1,

…

;j=1,2,

…

n;n=2,3,

…

;m=2,3,

…

。

33.另一方面,本发明还提供了一种数据处理装置,用于基于现场可编程门阵列和微处理器对多组待处理数据进行处理,所述现场可编程门阵列包括至少一个第一处理单元,所述微处理器包括至少一个第二处理单元;所述数据处理装置包括:

34.处理步骤确定模块,用于确定多组待处理数据中各组所述待处理数据的多个处理步骤;

35.处理步骤划分模块,用于确定所述多个处理步骤中由所述至少一个第一处理单元处理的至少一个第一处理步骤以及由所述至少一个第二处理单元处理的至少一个第二处理步骤;

36.处理时长获取模块,用于获取所述多个处理步骤对应的多个初始处理时长,并根据所述多个初始处理时长确定最长处理时长;

37.处理时长控制模块,用于控制所述至少一个第一处理单元以及所述至少一个第二处理单元的处理时长,使所述至少一个第一处理单元中各第一处理单元以及所述至少一个第二处理单元中各第二处理单元的处理时长均为所述最长处理时长;

38.数据处理模块,用于控制所述至少一个第一处理单元以及所述至少一个第二处理单元以流水线方式处理所述多组待处理数据。

39.另一方面,本发明还提供了一种电子设备,包括存储器和处理器,其中,

40.所述存储器,用于存储程序;

41.所述处理器,与所述存储器耦合,用于执行所述存储器中存储的所述程序,以实现上述任意一种实现方式中所述的数据处理方法中的步骤。

42.另一方面,本发明还提供了一种计算机可读存储介质,用于存储计算机可读取的程序或指令,所述程序或指令被处理器执行时能够实现上述任意一种实现方式中所述的数据处理方法中的步骤。

43.采用上述实施例的有益效果是:本发明提供的数据处理方法,通过设置基于现场可编程门阵列和微处理器对多组待处理数据进行处理,提高数据处理方法的串行和并行处理能力,发挥现场可编程门阵列对大量数据进行高速处理的优势以及微处理器编程灵活的特点,提高对多组待处理数据进行处理的处理速度。

44.进一步地,本发明通过控制至少一个第一处理单元以及至少一个第二处理单元的处理时长,使至少一个第一处理单元中各第一处理单元以及至少一个第二处理单元中各第二处理单元的处理时长均为最长处理时长,以实现所有处理单元的处理时长都相等的目的,避免由于数据处理时长不同,导致易发生数据堵塞或覆盖的技术问题,避免数据处理出错,提高数据处理过程的正确性和可靠性。

45.更进一步地,本发明通过控制至少一个第一处理单元以及至少一个第二处理单元以流水线方式处理多组待处理数据,可进一步提高数据处理方法的数据处理速度。

附图说明

46.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使

用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

47.图1为现有技术中数据处理方法的一个实施例结构示意图;

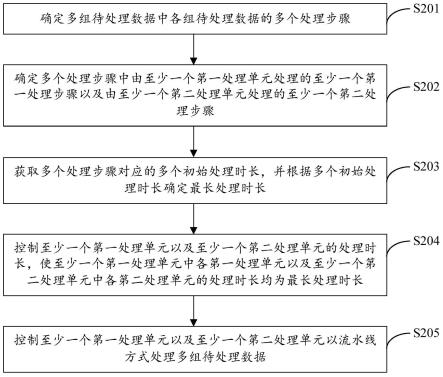

48.图2为本发明提供的数据处理方法的一个实施例流程示意图;

49.图3为本发明提供的数据处理架构的一个实施例结构示意图;

50.图4为本发明图2中s201的一个实施例流程示意图;

51.图5为本发明图2中s202的一个实施例流程示意图;

52.图6为本发明提供的待处理数据为3d相机数据时的数据处理架构的一个实施例结构示意图;

53.图7为本发明图2中s204的一个实施例流程示意图;

54.图8为本发明图2中s205的一个实施例流程示意图;

55.图9为本发明提供的对处理结果进行存储的一个实施例流程示意图;

56.图10为本发明提供的数据处理装置的一个实施例结构示意图;

57.图11为本发明提供的电子设备的一个实施例结构示意图。

具体实施方式

58.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

59.应当理解,示意性的附图并未按实物比例绘制。本发明中使用的流程图示出了根据本发明的一些实施例实现的操作。应当理解,流程图的操作可以不按顺序实现,没有逻辑的上下文关系的步骤可以反转顺序或者同时实施。此外,本领域技术人员在本发明内容的指引下,可以向流程图添加一个或多个其他操作,也可以从流程图中移除一个或多个操作。

60.在本发明实施例的描述中,“和/或”,描述关联对象的关联关系,表示可以存在三种关系,例如:a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。

61.附图中所示的一些方框图是功能实体,不一定必须与物理或逻辑上独立的实体相对应。可以采用软件形式来实现这些功能实体,或在一个或多个硬件模块或集成电路中实现这些功能实体,或在不同网络和/或处理器系统和/或微控制器系统中实现这些功能实体。

62.在本文中提及“实施例”意味着,结合实施例描述的特定特征、结构或特性可以包含在本发明的至少一个实施例中。在说明书中的各个位置出现该短语并不一定均是指相同的实施例,也不是与其它实施例互斥的独立的或备选的实施例。本领域技术人员显式地和隐式地理解的是,本文所描述的实施例可以与其它实施例相结合。

63.本发明实施例提供了一种数据处理方法、装置、电子设备及可读存储介质,以下分别进行说明。

64.图2为本发明提供的数据处理方法的一个实施例流程示意图,图3为本发明提供的数据处理架构的一个实施例结构示意图,如图2和图3所示,数据处理方法用于基于现场可

编程门阵列(field-programmable gate array,fpga)100和微处理器(advanced risc machines,arm)200对多组待处理数据进行处理,现场可编程门阵列100包括至少一个第一处理单元110,微处理器200包括至少一个第二处理单元210;数据处理方法包括:

65.s201、确定多组待处理数据中各组待处理数据的多个处理步骤;

66.s202、确定多个处理步骤中由至少一个第一处理单元110处理的至少一个第一处理步骤以及由至少一个第二处理单元210处理的至少一个第二处理步骤;

67.s203、获取多个处理步骤对应的多个初始处理时长,并根据多个初始处理时长确定最长处理时长;

68.s204、控制至少一个第一处理单元110以及至少一个第二处理单元210的处理时长,使至少一个第一处理单元110中各第一处理单元110以及至少一个第二处理单元210中各第二处理单元210的处理时长均为最长处理时长;

69.s205、控制至少一个第一处理单元110以及至少一个第二处理单元210以流水线方式处理多组待处理数据。

70.与现有技术相比,本发明实施例提供的数据处理方法,通过设置基于现场可编程门阵列100和微处理器200对多组待处理数据进行处理,提高数据处理方法的串行和并行处理能力,发挥现场可编程门阵列100对大量数据进行高速处理的优势以及微处理器200编程灵活的特点,提高对多组待处理数据进行处理的处理速度。

71.进一步地,本发明实施例通过控制至少一个第一处理单元110以及至少一个第二处理单元210的处理时长,使至少一个第一处理单元110中各第一处理单元110以及至少一个第二处理单元210中各第二处理单元210的处理时长均为最长处理时长,以实现所有处理单元的处理时长都相等的目的,避免由于数据处理时长不同,导致易发生数据堵塞或覆盖的技术问题,避免数据处理出错,提高数据处理过程的正确性和可靠性。

72.更进一步地,本发明实施例通过控制至少一个第一处理单元110以及至少一个第二处理单元210以流水线方式处理多组待处理数据,可进一步提高数据处理方法的数据处理速度。

73.在本发明的一些实施例中,现场可编程门阵列100和微处理器200可为一个控制芯片,通过这一控制芯片对多组待处理数据进行处理,相比于使用独立的现场可编程门阵列100和微处理器200,可降低设计难度,并可使现场可编程门阵列100和微处理器200之间的数据传输更加稳定。

74.在本发明的一个具体实施例中,控制芯片可为xczu3eg。

75.在本发明的一些实施例中,如图4所示,步骤s201包括:

76.s401、基于预设的划分规则确定待处理数据的多个初始处理步骤;

77.s402、基于预设的合并规则对多个初始处理步骤进行合并,获得多个处理步骤。

78.本发明实施例通过基于预设的合并规则对多个初始处理步骤进行合并,获得多个处理步骤,可减少现场可编程门阵列100中第一处理单元110和/或微处理器200中第二处理单元210的个数,降低成本。并且,还可减小初始处理时长和最长处理时长的差值,进一步提高数据处理方法的数据处理速度。

79.在本发明的具体实施例中,步骤s401中预设的划分规则可为待处理数据的处理流程。步骤s402中预设的合并规则可为各初始处理步骤的处理时长。

80.需要说明的是:预设的划分规则和预设的合并规则可根据实际情况进行调整,在此不做一一赘述。

81.在本发明的一个具体应用场景中,待处理数据为3d相机数据。初始处理步骤包括数据获取、图像处理、解相位、排序、相位匹配、三维计算以及数据压缩这七个初始处理步骤,考虑到数据获取和图像处理的处理时长较短,将数据获取和图像数据进行合并,合并为第一个处理步骤,则3d相机数据包括六个处理步骤。

82.在本发明的一些实施例中,如图5所示,步骤s202包括:

83.s501、获取多个处理步骤中各处理步骤的步骤特征;

84.s502、基于预设的划分规则以及步骤特征确定多个处理步骤中由至少一个第一处理单元110处理的至少一个第一处理步骤以及由至少一个第二处理单元210处理的至少一个第二处理步骤。

85.本发明实施例通过基于预设的划分规则和步骤特征确定第一处理步骤和第二处理步骤,可进一步地充分利用现场可编程门阵列100对大量数据进行高速处理的优势以及微处理器200编程灵活的特点,进而可进一步提高对多组待处理数据进行处理的处理速度。

86.在本发明的一些实施例中,步骤特征包括但不限于各处理步骤的条件判断数量以及串行运算特性,具体地:当条件判断数量较多且串行运算特性较强时,处理步骤为由第二处理单元210处理的第二处理步骤。

87.在本发明的具体实施例中,如图6所示,当待处理数据为3d相机数据时,由于三维计算这一处理步骤条件判断较多且串行运算特性较强,则微处理器200包括一个第二处理单元210,用于处理三维计算这一处理步骤。现场可编程门阵列100包括五个第一处理单元110,分别用于处理数据获取及图像处理、解相位、排序、相位匹配以及数据压缩这五个处理步骤。

88.在本发明的一些实施例中,如图7所示,步骤s204包括:

89.s701、获取各第一处理单元110以及各第二处理单元210的初始处理时长;

90.s702、根据初始处理时长和最长处理时长确定处理时长差值;

91.s703、根据处理时长差值控制各第一处理单元110以及各第二处理单元210的开始与停止,使各第一处理单元110以及各第二处理单元210的处理时长均为最长处理时长。

92.在本发明的具体实施例中,若其中一个第一处理单元110的初始处理时长比最长处理时长快0.3秒,即:处理时长差值为0.3秒,则可控制这一第一处理单元110在处理过程中暂停0.3秒,以使这一第一处理单元110的处理时长为最长处理时长。

93.在本发明的另一些具体实施例中,若其中一个第一处理单元110的初始处理时长比最长处理时长快0.3秒,即:处理时长差值为0.3秒,则可控制这一第一处理单元110在处理完成后等待0.3秒,以使这一第一处理单元110的总处理时长为最长处理时长。

94.在本发明的一些实施例中,多组待处理数据包括第一待处理数据和第二待处理数据,第一待处理数据和第二待处理数据均包括顺序排布的第一目标处理步骤和第二目标处理步骤,至少一个第一处理单元110包括处理所述第一目标处理步骤的第一目标处理单元,至少一个第二处理单元210包括处理所述第二目标处理步骤的第二目标处理单元。

95.则在本发明的一些实施例中,如图8所示,步骤s205包括:

96.s801、获取处理信号,第一目标处理单元响应处理信号,并处理第一待处理数据的

第一目标处理步骤,且当第一待处理数据的第一目标处理步骤处理完成后,生成第一处理完成信号;

97.s802、第二目标处理单元响应第一处理完成信号,并处理第一待处理数据的第二目标处理步骤,且当第一待处理数据的第二目标处理步骤处理完成后,生成第二处理完成信号;

98.s803、第一目标处理单元响应第一处理完成信号,并处理第二待处理数据的第一目标处理步骤;

99.s804、第二目标处理单元响应第二处理完成信号,并处理第二待处理数据的第二目标处理步骤。

100.由上述过程可知:若每个处理步骤的处理时长为t,一组待处理数据包括n各处理步骤,则完成一组待处理数据的耗时t’=n*t,完成m组待处理数据的总耗时t

m’=(m n-1)*t,当m远大于n(例如n=6,m=1000)时,t

m’≈m*t,相比于现有技术中的tm=(t1 t2

…

tn)*m,大大缩短了数据处理时间,提高了数据处理速度。

101.在本发明的具体实施例中,当待处理数据为3d相机数据时,至少一个第一处理单元包括数据获取及图像处理单元、解相位处理单元、排序处理单元、相位匹配处理单元、三维计算处理单元以及数据压缩处理单元,数据获取及图像处理、解相位、排序、相位匹配、三维计算以及数据压缩这六个处理步骤的耗时分别为ta、tb、tc、td、te、tf,由fpga和arm的特性可知,ta、tb、tc、td、tf是固定值,te会随着数据以及arm运行状态的不同产生差异。实际测试得知,整个过程,三维计算耗时最长,即t

max

(ta、tb、tc、td、te、tf)=te。通过控制各处理单元的处理时长,使得处理时长均为te,则步骤s205具体如下:

102.0时刻,各处理单元均为空闲状态,数据获取及图像处理单元响应处理信号,对第1组待处理数据进行获取和图像处理;

103.te时刻,数据获取及图像处理单元处理完成,生成第一处理完成信号,数据获取及图像处理单元处于空闲状态,其它单元均处于空闲状态,解相位处理单元响应第一处理完成信号,对第1组待处理数据进行处理;同时,数据获取及图像处理单元响应第一处理完成信号,对第2组待处理数据进行获取和图像处理;

104.2倍te时刻,数据获取及图像处理单元和解相位处理单元均处理完成,处于空闲状态,其它处理单元均处于空闲状态,数据获取及图像处理单元对第3组待处理数据进行获取和图像处理,解相位处理单元对第2组待处理数据进行解相位处理,排序处理单元对第1组待处理数据进行排序;

105.3倍te时刻,数据获取及图像处理单元、解相位处理单元、排序处理单元均处理完成,处于空闲状态,数据获取及图像处理单元对第4组待处理数据进行获取和图像处理,解相位处理单元对第3组待处理数据进行解相位处理,排序处理单元对第2组待处理数据进行排序,相位匹配处理单元对第1组待处理数据进行相位匹配;

106.4倍te时刻,数据获取及图像处理单元、解相位处理单元、排序处理单元、相位匹配处理单元均处理完成,处于空闲状态,其它模块均处于空闲状态,数据获取及图像处理单元对第5组待处理数据进行获取和图像处理,解相位处理单元对第4组待处理数据进行解相位处理,排序处理单元对第3组待处理数据进行排序,相位匹配处理单元对第2组待处理数据进行相位匹配,三维计算处理单元对第1组待处理数据进行匹配运算;

107.5倍te时刻,数据获取及图像处理单元、解相位处理单元、排序处理单元、相位匹配处理单元、三维计算处理单元均处理完成,处于空闲状态,数据获取及图像处理单元对第6组待处理数据进行获取和图像处理,解相位处理单元对第5组待处理数据进行解相位处理,排序处理单元对第4组待处理数据进行排序,相位匹配处理单元对第3组待处理数据进行相位匹配,三维计算处理单元对第2组待处理数据进行匹配运算,数据压缩处理单元对第1组待处理数据进行压缩;

108.以此类推,n倍te时刻,数据获取及图像处理单元、解相位处理单元、排序处理单元、相位匹配处理单元、三维计算处理单元、数据压缩处理单元均处理完成,处于空闲状态,数据获取及图像处理单元对第n 1组待处理数据进行获取和图像处理,解相位处理单元对第n组待处理数据进行解相位处理,排序处理单元对第n-1组待处理数据进行排序,相位匹配出来电源对第n-2组待处理数据进行相位匹配,三维计算处理单元对第n-3组待处理数据进行匹配运算,数据压缩处理单元对第n-4组待处理数据进行压缩。

109.综上所述:在n倍te时刻,数据压缩处理单元已经完成te组待处理数据的压缩,即此时已完成te组待处理数据的全流程处理,亦即完成n组待处理数据的全流程耗时为(n 5)*te。

110.为了进一步防止流水线方式处理多组待处理数据的处理过程中数据出错,在本发明的一些实施例中,多组待处理数据包括m组待处理数据,待处理数据包括n个处理步骤,则如图3和图9所示,数据处理方法还包括:

111.s901、构建与n个处理步骤一一对应的n个存储区300;

112.s902、获取各组待处理数据的处理结果;

113.s903、将第i*n j组待处理数据存储至第j个存储区300;

114.其中,i=0,1,

…

;j=1,2,

…

n;n=2,3,

…

;m=2,3,

…

。

115.本发明实施例通过构建与n个处理步骤一一对应的n个存储区300,并将第i*n j组待处理数据存储至第j个存储区300,可实现对每个待处理数据的处理结果的存储,防止流水线方式处理多组待处理数据过程中数据出错的技术问题,进一步提高对待处理数据进行数据处理的准确性和可靠性。

116.在本发明的具体实施例中,当待处理数据为3d相机数据时,存储区300为6个,分别为第一存储区、第二存储区、第三存储区、第四存储区、第五存储区以及第六存储区。

117.第1组待处理数据的处理结果存储在第一存储区;第2组待处理数据的处理结果存储在第二存储区;第3组待处理数据的处理结果存储在第三存储区;第4组待处理数据的处理结果存储在第四存储区;第5组待处理数据的处理结果存储在第五存储区;第6组待处理数据的处理结果存储在第六存储区;第7组待处理数据的处理结果存储在第一存储区;第8组待处理数据的处理结果存储在第二存储区,

…

,以此类推。

118.为了更好实施本发明实施例中的数据处理方法,在数据处理方法基础之上,对应的,本发明实施例还提供了一种数据处理装置,用于基于现场可编程门阵列和微处理器对多组待处理数据进行处理,现场可编程门阵列包括至少一个第一处理单元,微处理器包括至少一个第二处理单元;如图10所示,数据处理装置1000包括:

119.处理步骤确定模块1001,用于确定多组待处理数据中各组待处理数据的多个处理步骤;

120.处理步骤划分模块1002,用于确定多个处理步骤中由至少一个第一处理单元处理的至少一个第一处理步骤以及由至少一个第二处理单元处理的至少一个第二处理步骤;

121.处理时长获取模块1003,用于获取多个处理步骤对应的多个初始处理时长,并根据多个初始处理时长确定最长处理时长;

122.处理时长控制模块1004,用于控制至少一个第一处理单元以及至少一个第二处理单元的处理时长,使至少一个第一处理单元中各第一处理单元以及至少一个第二处理单元中各第二处理单元的处理时长均为最长处理时长;

123.数据处理模块1005,用于控制至少一个第一处理单元以及至少一个第二处理单元以流水线方式处理多组待处理数据。上述实施例提供的数据处理装置1000可实现上述数据处理方法实施例中描述的技术方案,上述各模块或单元具体实现的原理可参见上述数据处理方法实施例中的相应内容,此处不再赘述。

124.如图11所示,本发明还相应提供了一种电子设备1100。该电子设备1100包括处理器1101、存储器1102及显示器1103。图11仅示出了电子设备1100的部分组件,但是应理解的是,并不要求实施所有示出的组件,可以替代的实施更多或者更少的组件。

125.处理器1101在一些实施例中可以是一中央处理器(central processing unit,cpu),微处理器或其他数据处理芯片,用于运行存储器1102中存储的程序代码或处理数据,例如本发明中的数据处理方法。

126.在一些实施例中,处理器1101可以是单个服务器或服务器组。服务器组可为集中式或分布式的。在一些实施例中,处理器1101可为本地的或远程的。在一些实施例中,处理器1101可实施于云平台。在一实施例中,云平台可包括私有云、公共云、混合云、社区云、分布式云、内部间、多重云等,或以上的任意组合。

127.存储器1102在一些实施例中可以是电子设备1100的内部存储单元,例如电子设备1100的硬盘或内存。存储器1102在另一些实施例中也可以是电子设备1100的外部存储设备,例如电子设备1100上配备的插接式硬盘,智能存储卡(smart media card,smc),安全数字(secure digital,sd)卡,闪存卡(flash card)等。

128.进一步地,存储器1102还可既包括电子设备1100的内部储存单元也包括外部存储设备。存储器1102用于存储安装电子设备1100的应用软件及各类数据。

129.显示器1103在一些实施例中可以是led显示器、液晶显示器、触控式液晶显示器以及oled(organic light-emitting diode,有机发光二极管)触摸器等。显示器1103用于显示在电子设备1100的信息以及用于显示可视化的用户界面。电子设备1100的部件1101-1103通过系统总线相互通信。

130.在本发明的一些实施例中,当处理器1101执行存储器1102中的数据处理程序时,可实现以下步骤:

131.确定多组待处理数据中各组待处理数据的多个处理步骤;

132.确定多个处理步骤中由至少一个第一处理单元处理的至少一个第一处理步骤以及由至少一个第二处理单元处理的至少一个第二处理步骤;

133.获取多个处理步骤对应的多个初始处理时长,并根据多个初始处理时长确定最长处理时长;

134.控制至少一个第一处理单元以及至少一个第二处理单元的处理时长,使至少一个

第一处理单元中各第一处理单元以及至少一个第二处理单元中各第二处理单元的处理时长均为最长处理时长;

135.控制至少一个第一处理单元以及至少一个第二处理单元以流水线方式处理多组待处理数据。

136.应当理解的是:处理器1101在执行存储器1102中的数据处理程序时,除了上面的功能之外,还可实现其它功能,具体可参见前面相应方法实施例的描述。

137.进一步地,本发明实施例对提及的电子设备1100的类型不做具体限定,电子设备1100可以为手机、平板电脑、个人数字助理(personal digitalassistant,pda)、可穿戴设备、膝上型计算机(laptop)等便携式电子设备。便携式电子设备的示例性实施例包括但不限于搭载ios、android、microsoft或者其他操作系统的便携式电子设备。上述便携式电子设备也可以是其他便携式电子设备,诸如具有触敏表面(例如触控面板)的膝上型计算机(laptop)等。还应当理解的是,在本发明其他一些实施例中,电子设备1100也可以不是便携式电子设备,而是具有触敏表面(例如触控面板)的台式计算机。

138.相应地,本技术实施例还提供一种计算机可读存储介质,计算机可读存储介质用于存储计算机可读取的程序或指令,程序或指令被处理器执行时,能够实现上述各方法实施例提供的数据处理方法中的步骤或功能。

139.本领域技术人员可以理解,实现上述实施例方法的全部或部分流程,可以通过计算机程序来指令相关的硬件(如处理器,控制器等)来完成,计算机程序可存储于计算机可读存储介质中。其中,计算机可读存储介质为磁盘、光盘、只读存储记忆体或随机存储记忆体等。

140.以上对本发明所提供的数据处理方法、装置、电子设备及可读存储介质进行了详细介绍,本文中应用了具体个例对本发明的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本发明的方法及其核心思想;同时,对于本领域的技术人员,依据本发明的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本发明的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。