1.本发明涉及光电输入、输出器件,是一种基于复合介质栅结构的集光和电输入、输出于一体的新器件。

背景技术:

2.ccd和cmos-aps作为当前最常见的两种成像器件,都具有各自的局限。ccd因其复杂的控制时序和电压要求,导致工作速度较慢,且不易集成;cmos-aps因其采用感光二极管,且结构复杂,导致填充系数低,满阱电荷小。

3.在中国专利cn201210442007中提出了一种双晶体管光敏探测器,该探测器的特点是单个半导体器件即可实现完整的复位、感光以及读出的功能,构成一个完整的像素,可以极大地提高像素的填充因子。这种复合介质栅双晶体管光敏探测器作为新一代的成像器件,其更快的工作速度、更大的填充系数、更多的满阱电荷且能和cmos工艺集成,使其与ccd和cmos-aps相比具有先天优势。

技术实现要素:

4.针对现有大部分光敏探测器都只有光输入的功能,而缺少电输入的能力,本发明旨在为光电联合输入提供一种可能方案,具体提供一种基于复合介质栅结构的光电一体器件和阵列。本发明的另一个目的在于提供上述器件和阵列的操作方法。

5.本发明器件采用的技术方案如下:

6.基于复合介质栅结构的光电一体器件,包括形成在同一p型半导体衬底上方的复合介质栅光敏探测器和复合介质栅晶体管,其中,所述复合介质栅光敏探测器用于收集、存储和读出感光的光电子,其在衬底上方依次设有第一底层绝缘介质层、第一浮栅、第一顶层绝缘介质层和第一控制栅,在衬底内设有第一漏极,不设源极;所述复合介质栅晶体管用于向所述复合介质栅光敏探测器输入或输出电子,其在衬底上方依次设有第二底层绝缘介质层、第二浮栅、第二顶层绝缘介质层和第二控制栅,在衬底内设有源极和第二漏极。

7.本发明还提供一种基于复合介质栅结构的光电一体器件的操作方法,包括如下步骤:

8.(1)电子的输入:调节所述第二控制栅与p型半导体衬底处于正偏状态,在所述第一漏极施加正脉冲,使得电子跃过所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区与所述第一底层绝缘介质层下方p型半导体衬底内沟道之间的势垒,完成电子的输入;

9.或者电子的输出:调节所述第二控制栅与p型半导体衬底处于正偏状态,在所述第一漏极施加负脉冲,使得电子跃过所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区与所述第一底层绝缘介质层下方p型半导体衬底内沟道之间的势垒,完成电子的输出;

10.(2)信号的读出:调节所述第一控制栅与p型半导体衬底处于正偏压状态,所述源极接地,所述第二漏极接正偏信号,读取所述复合介质栅晶体管的输出电流。

11.进一步地,在电子输入或者输出之后,还包括如下步骤:

12.光电子的复位:调节所述第一控制栅与p型半导体衬底处于零偏状态,使得所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区消失,完成光电子的复位;

13.光电子的产生:光电子入射到p型半导体衬底,产生光生电子空穴对;

14.光电子的收集:调节所述第一控制栅与p型半导体衬底处于正偏压状态,使得所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区产生,所述光电子的产生步骤中产生的光生电子空穴对在垂直电场的作用下分离,电子被扫入所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区,空穴被扫出衬底。

15.本发明还提供一种基于复合介质栅结构的光电一体器件阵列,将上述光电一体器件采用nor架构形成阵列:对于n行m列的所述光电一体器件阵列,共有n个第一字线wl1信号,分别连接n个所述光电一体器件的第一控制栅;共有n个第二字线wl2信号,分别连接n个所述光电一体器件的第二控制栅;共有m个源线sl信号,分别连接m个所述源极;共有m个第一位线bl1信号,分别连接m个所述第一漏极;共有m个第二位线bl2信号,分别连接m个所述第二漏极。

16.本发明另外提供一种基于复合介质栅结构的光电一体器件阵列的操作方法,包括如下步骤:

17.(1)电子的输入:调节第二字线wl2与p型半导体衬底处于正偏状态,在第二位线bl2施加正脉冲,使得每个器件中电子跃过所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区与所述第一底层绝缘介质层下方p型半导体衬底内沟道之间的势垒,完成电子的输入;

18.或者电子的输出:调节第二字线wl2与p型半导体衬底处于正偏状态,在第二位线bl2施加负脉冲,使得每个器件中电子跃过所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区与所述第一底层绝缘介质层下方p型半导体衬底内沟道之间的势垒,完成电子的输出;

19.(2)信号的读出:调节第一字线wl1与p型半导体衬底处于正偏状态,源线sl接地,第一位线bl1接正偏信号,读取所述复合介质栅晶体管的输出电流。

20.进一步地,在电子输入或者输出之后,还包括如下步骤:

21.光电子的复位:调节第一字线wl1与p型半导体衬底处于零偏状态,使得每个器件中所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区消失,完成光电子的复位;

22.光电子的产生:光电子入射到p型半导体衬底,产生光生电子空穴对;

23.光电子的收集:调节第一字线wl1与p型半导体衬底处于正偏状态,使得每个器件中所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区产生,所述光电子的产生步骤中产生的光生电子空穴对在垂直电场的作用下分离,电子被分别扫入每个器件中所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区,空穴被扫出衬底

24.本发明的光电一体器件利用光电子进行工作,可以作为图像传感器使用,同时能解决初始信号分布不均匀的问题;利用电子进行工作,可以作为dram使用,提供短期存储功能;这些能力为图像传感器与人工智能相结合的应用提供技术支撑。

附图说明

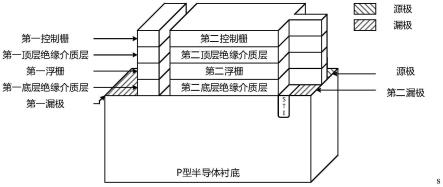

25.图1是本发明的器件结构图;

26.图2是本发明器件的(a)符号图,(b)是(a)图的符号简化图;

27.图3是本发明的阵列结构图。

具体实施方式

28.本实施例提供了一种基于复合介质栅结构的光电一体器件,其结构如图1所示,包括形成在同一p型半导体衬底上方的复合介质栅光敏探测器和复合介质栅晶体管,其中,所述复合介质栅光敏探测器用于收集、存储和读出感光的光电子,其在衬底上方依次设有第一底层绝缘介质层、第一浮栅、第一顶层绝缘介质层和第一控制栅,在衬底内设有第一漏极,不设源极;所述复合介质栅晶体管用于向所述复合介质栅光敏探测器输入或输出电子,其在衬底上方依次设有第二底层绝缘介质层、第二浮栅、第二顶层绝缘介质层和第二控制栅,在衬底内设有源极和第二漏极。复合介质栅晶体管与复合介质栅光敏探测器的横向间距为工艺支持的最小间距,使得复合介质栅晶体管第一漏极的电子可以跃过两个晶体管直接的势垒。

29.基于复合介质栅结构的光电一体器件的符号如图2的(a)图所示,包括第一控制栅、第二控制栅、源极、第一漏极和第二漏极和衬底;考虑到通常采用p型衬底,因此可以将符号简化为图2的(b)图的形式。

30.基于此,图3给出了n行m列的光电一体阵列架构,共有n个第一字线wl1信号,分别连接n个第一控制栅;共有n个第二字线wl2信号,分别连接n个第二控制栅;共有m个源线sl信号,分别连接m个复合介质栅光敏探测器的漏极;共有m个第一位线bl1信号,分别连接m个复合介质栅光敏探测器的第一漏极;共有m个第二位线bl2信号,分别连接m个复合介质栅晶体管的第二漏极。

31.实施例1

32.本实施例给出一种基于上述阵列解决初始信号分布不均匀的方案。假设图3中的阵列尺寸为16

×

16,即n=16、m=16,记阵列中每个基于复合介质栅结构的光电一体器件为m

i,j

,其中i为行、j为列,从左下角开始编号,即左下角所述基于复合介质栅结构的光电一体器件为m

1,1

,右上角基于复合介质栅结构的光电一体器件编号为m

16,16

。假设每个基于复合介质栅结构的光电一体器件中所述复合介质栅光敏探测器原始阈值电压为v

th1,0

,由于工艺偏差导致的初始阈值电压偏移量为光电子导致的阈值电压偏移为v

opt

,即:

[0033][0034]

如若采用常规方案,则采集到图像信号后,并不能消除的影响,导致图像具有标准差:

[0035][0036]

如若采用本发明所述方案,可消除σ的影响。具体方案如下:

[0037]

(1)电子的输入:调节第二字线wl2接3v,p型半导体衬底接-3v,在第二位线bl2施加1khz,3.3v的负脉冲,使得每个器件中电子跃过所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区与所述第一底层绝缘介质层下方p型半导体衬底内沟道之间的势垒,完成

电子的输入,其中第i行、第j列光电一体器件m

i,j

的输入值为

[0038]

(2)电子的输出:在本实施例中,不需要对感光数据进行额外的运算,因此无需此步骤;

[0039]

(3)光电子的复位:调节第一字线wl1接-3v,p型半导体衬底接-3v,使得每个器件中所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区消失,完成光电子的复位;

[0040]

(4)光电子的产生:光电子入射到p型半导体衬底,产生光生电子空穴对;

[0041]

(5)光电子的收集:调节第一字线wl1接0v,p型半导体衬底接-3v,使得每个器件中所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区产生,步骤(4)中产生的光生电子空穴对在垂直电场的作用下分离,电子被分别扫入每个器件中所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区,空穴被扫出衬底;

[0042]

(6)信号的读出:在步骤(5)的正偏压状态下,源线sl接0v,第一位线bl1接0.2v,读取所述复合介质栅晶体管的输出电流,基于复合介质栅结构的光电一体器件中所述复合介质栅光敏探测器阈值电压:

[0043][0044]

即:

[0045][0046]

消除了σ的影响。

[0047]

实施例2

[0048]

本实施例给出另一种区别于实施例1的用于解决初始信号分布不均匀的方案。

[0049]

具体方案如下:

[0050]

(1)电子的输入:在本实施例中,不需要对感光数据进行额外的运算,因此无需此步骤;

[0051]

(2)电子的输出:调节第二字线wl2接3v,p型半导体衬底接-3v,在第二位线bl2施加1khz,3.3v的正脉冲,使得每个器件中电子跃过所述所述第一底层绝缘介质层下方p型半导体衬底内沟道与第一底层绝缘介质层下方p型半导体衬底内的耗尽区之间的势垒,完成电子的输出,其中第i行、第j列光电一体器件m

i,j

的输出值为

[0052]

(3)光电子的复位:调节第一字线wl1接-3v,p型半导体衬底接-3v,使得每个器件中所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区消失,完成光电子的复位;

[0053]

(4)光电子的产生:光电子入射到p型半导体衬底,产生光生电子空穴对;

[0054]

(5)光电子的收集:调节第一字线wl1接0v,p型半导体衬底接-3v,使得每个器件中所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区产生,步骤(4)中产生的光生电子空穴对在垂直电场的作用下分离,电子被分别扫入每个器件中所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区,空穴被扫出衬底;

[0055]

(6)信号的读出:在步骤(5)的正偏压状态下,源线sl接0v,第一位线bl1接0.2v,读取所述复合介质栅晶体管的输出电流,基于复合介质栅结构的光电一体器件中所述复合介质栅光敏探测器阈值电压:

[0056][0057]

即:

[0058][0059]

消除了σ的影响。

[0060]

实施例3

[0061]

本实施例给出一种基于上述阵列作为dram使用,提供短期存储功能的方案。假设图3中的阵列尺寸为16

×

16,即n=16、m=16,记阵列中每个基于复合介质栅结构的光电一体器件为m

i,j

,其中i为行、j为列,从左下角开始编号,即左下角所述基于复合介质栅结构的光电一体器件为m

1,1

,右上角基于复合介质栅结构的光电一体器件编号为m

16,16

。假设每个基于复合介质栅结构的光电一体器件中所述复合介质栅光敏探测器原始阈值电压为v

th1,0

,即:

[0062][0063]

当需要存储数据时:

[0064]

(1)电子的输入:调节第二字线wl2接3v,p型半导体衬底接-3v,在第二位线bl2施加1khz,3.3v的负脉冲,使得每个器件中电子跃过所述第一底层绝缘介质层下方p型半导体衬底内的耗尽区与所述第一底层绝缘介质层下方p型半导体衬底内沟道之间的势垒,完成电子的输入,其中第i行、第j列光电一体器件m

i,j

的输入值为

[0065]

(2)电子的输出:无需此步骤;

[0066]

(3)光电子的复位:无需此步骤;

[0067]

(4)光电子的产生:无需此步骤;

[0068]

(5)光电子的收集:无需此步骤;

[0069]

(6)信号的读出:调节第一字线wl1接0v,p型半导体衬底接-3v,源线sl接0v,第一位线bl1接0.2v,读取所述复合介质栅晶体管的输出电流,基于复合介质栅结构的光电一体器件中所述复合介质栅光敏探测器阈值电压:

[0070][0071]

即:

[0072][0073]

完成了数据的存储与读取,而且该方案相较于现行的dram方案具有读出噪声小、存储时间长、非破坏性读取等优势。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。