∑-δ

模数转换器中的数模转换器线性化技术

技术领域

1.本公开涉及一种∑-δ模数转换器中的数模转换器线性化技术。

背景技术:

2.∑-δ调制是适用于模数转换器(adc)将模拟信号编码成数字信号的技术。∑-δadc可配置有多位量化器以支持用于例如蜂窝电信(例如,第四代(4g)系统、第五代(5g)系统)等各种应用的数据编码。这些应用可能需要宽带宽、高分辨率、高线性、高能效的adc。

3.一些∑-δadc设计在adc的反馈回路中采用多位数模转换器(dac)。然而,多位dac的元件之间的失配可能会造成dac性能的非线性,从而限制adc的精度。此外,现有线性化技术常常会增加反馈回路的延迟,这可能会对整体adc性能产生负面影响。

技术实现要素:

4.描述了一种∑-δ调制器。所述∑-δ调制器可包括多位量化器,所述多位量化器配置有映射引擎以在所述多位量化器内执行排序、映射和切换操作中的一个或多个。在一些实施例中,所述映射引擎嵌入所述多位量化器内。

5.所述∑-δ调制器可另外包括:第一求和节点,其被配置成从接收到的输入模拟信号减去反馈模拟信号并生成第一模拟输出信号;回路滤波器,其被配置成从所述第一求和节点接收所述第一模拟输出信号并对所述第一模拟输出信号进行滤波;以及第二求和节点,其被配置成从第一滤波后模拟输出信号减去所述反馈模拟信号并生成第二模拟输出信号,其中所述多位量化器被配置成从所述映射引擎接收所述第二模拟输出信号和参考信号以产生数字输出信号。

6.在一些实施例中,所述映射引擎耦合在参考信号与所述多位量化器之间。

7.在一些实施例中,所述∑-δ调制器可另外包括额外回路延迟(eld)dac,所述eld dac被配置成:经由反馈回路接收所述数字输出信号;将所述数字输出信号转换成所述反馈模拟信号;并且将所述反馈模拟信号提供到所述第二求和节点。在一些实施例中,所述eld dac另外被配置成将所述数字输出信号转换成所述反馈模拟信号。

8.在一些实施例中,所述∑-δ调制器可另外包括主dac,所述主dac被配置成:经由反馈回路接收所述数字输出信号;将所述数字输出信号转换成所述反馈模拟信号;并且将所述反馈模拟信号提供到所述第一求和节点。

9.在一些实施例中,所述主dac另外被配置成经由所述主dac与失配传感器之间的直接信令路径将所述反馈模拟信号作为输入提供到所述失配传感器。

10.在一些实施例中,所述失配传感器另外被配置成:测量所述主dac的单元元件之间的静态失配;并且将包括测量到的静态失配的测量信息提供到与多位连续时间∑-δ调制器相关联的逻辑。

11.在一些实施例中,所述失配传感器另外被配置成:测量所述主dac的单元元件之间的动态失配;并且将包括测量到的动态失配的测量信息提供到与多位连续时间∑-δ调制

器相关联的逻辑。

12.在一些实施例中,所述逻辑另外配置有排序算法、映射算法或切换算法,或其任何组合。

13.在一些实施例中,所述映射引擎另外被配置成将所述排序算法、所述映射算法或所述切换算法中的一个或多个或其任何组合应用于所述参考。

14.在一些实施例中,所述映射引擎在多位连续时间∑-δ调制器的反馈回路外部,并且另外被配置成提供多位连续时间∑-δ调制器的线性化,而无需来自所述多位量化器的输出。

15.在一些实施例中,多位连续时间∑-δ调制器的反馈回路包括一组每位并行回路,每个回路被配置成提供所述滤波后模拟输出信号的每位信号求和,使得多个每位并行回路的输出是多位量化数字输出信号。

16.描述了一种装置。所述装置包括:第一求和节点,其被配置成从接收到的输入模拟信号减去反馈模拟信号并生成第一模拟输出信号;回路滤波器,其被配置成从所述第一求和节点接收所述第一模拟输出信号并对所述第一模拟输出信号进行滤波;多级量化器,其包括耦合到所述回路滤波器以接收滤波后信号并输出数字输出信号的多个切片,所述多个切片中的每个切片包括耦合到第二求和节点的放大器、耦合到所述第二求和节点的锁存器、耦合到所述第二求和节点的eld dac和耦合到所述第二求和节点的参考dac,其中所述参考dac被配置成从映射引擎接收一组输出参考代码。

17.在一些实施例中,所述映射引擎另外被配置成经由反馈回路接收作为反馈的所述数字输出信号加上一组输入代码,以将一组输出代码提供到所述参考dac。

18.在一些实施例中,所述数字输出信号包括多位量化数字输出信号。

19.在一些实施例中,所述装置的反馈回路包括一组每位并行回路,每个回路被配置成提供滤波后模拟输出信号的每位信号求和,使得多个每位并行回路的输出是多位量化数字输出信号。

20.在一些实施例中,所述装置可另外包括一组相应锁存器,所述一组相应锁存器被配置成提供多个每位并行回路的输出以提供多位量化数字输出信号。

21.在一些实施例中,所述多位量化器是包括1位比较器锁存器和数个重复的eld求和节点的数个切片的多级量化器。

22.在一些实施例中,参考dac被配置成将数个参考代码转换成参考电流,其中映射引擎另外包括数个开关以基于所选择的次序将一组输入代码连接到一组输出参考代码。

23.可描述一种方法。所述方法可包括:经由∑-δ调制器的滤波器对第一模拟输出信号进行滤波;经由所述∑-δ调制器的求和节点从滤波后模拟输出信号减去反馈模拟信号;经由所述∑-δ调制器的所述求和节点的输出生成第二模拟输出信号;以及经由所述∑-δ调制器的多位量化器从映射引擎接收所述第二模拟输出信号和参考信号以产生数字输出信号,其中所述映射引擎耦合在所述参考信号与所述多位量化器之间。

24.在一些实施例中,所述映射引擎另外被配置成经由反馈回路接收作为反馈的所述数字输出信号加上一组输入代码,以将一组输出代码提供到参考dac。

附图说明

25.通过参考附图,可以更好地理解本公开,并且其众多特征和优点对于本领域技术人员来说是显而易见的。在不同的图式中使用相同的参考符号指示类似或相同的项目。

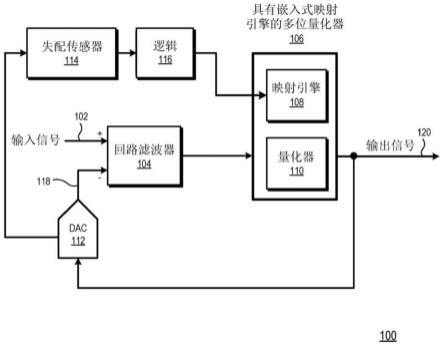

26.图1是根据一些实施例的连续时间∑-δadc的框图。

27.图2是根据一些实施例的连续时间∑-δadc的框图。

28.图3是根据一些实施例的连续时间∑-δadc的框图。

29.图4是根据一些实施例的连续时间∑-δadc的框图。

30.图5是根据一些实施例的连续时间∑-δadc的框图。

具体实施方式

31.本公开的各个方面涉及连续时间∑-δadc中的dac线性化技术。在adc中,可以用采样频率对模拟信号进行采样,然后将所述模拟信号量化成数字信号。在一些实施例中,这可能会引入量化误差噪声。连续时间∑-δadc可执行δ调制,其可对信号的变化(即,δ)而非绝对值进行编码。结果是脉冲流,而不是像脉码调制的情况一样的数字流。在σ-δ调制中,通过使数字输出通过dac并将所得模拟信号添加(σ)到输入信号(即,在δ调制之前的信号),由此减少δ调制所引入的误差,从而提高调制的精度。

32.连续时间∑-δadc包括一个或多个∑-δ调制器(sdm)。sdm是包含回路滤波器、量化器和反馈dac的反馈回路。量化器的功能是采样和量化。量化器的输入信号在时域中连续并且在电压(或电流)域中连续(即,连续时间连续值(模拟信号))。量化器的输出信号可在时域中离散并且在电压域中离散(即,离散时间离散值(数字信号))。主反馈dac的功能是将数字信号转换成模拟信号的零阶保持。

33.利用多位量化的∑-δadc在需要宽带宽、高分辨率、高线性、高能效的adc的许多应用中很受欢迎。为了实现高线性,多位dac的失配常常是一个瓶颈。存在用于高线性dac的一些线性化技术,例如排序、数据加权平均、随机化等。然而,在高速∑-δadc中,dac在反馈回路中。在一些实施例中,dac线性化技术可能会增加反馈回路中的延迟,这是不期望的。本公开的各个方面通过改变多位量化器的参考来改进线性化技术。因此,这减少了∑-δ调制器的反馈回路中的延迟,这对于高速∑-δadc是有利的。

34.举例来说,映射引擎通常在sdm的主反馈回路中,并且更具体地说,映射引擎在量化器与主dac之间。在本公开中,映射引擎不是sdm的主反馈回路的一部分。通过对参考dac的参考代码进行排序、映射和切换,实现了对主dac的单元元件的对应排序、映射和切换。如果映射引擎需要量化器输出作为输入,那么映射引擎在量化器与参考dac之间,但在主反馈回路之外。因为映射引擎不在主反馈回路中,所以映射引擎的延迟也不会引起sdm主反馈回路的总回路延迟。在映射引擎需要量化器输出信息的情况下,sdm主反馈回路和dac线性化回路部分解耦,且因此可以单独优化。

35.图1是根据一些实施例的连续时间∑-δadc 100的框图。连续时间∑-δadc 100可实施前馈或反馈或混合前馈-反馈sdm架构。在连续时间∑-δadc 100的以下描述中,可从连续时间∑-δadc 100添加或省略某些组件。连续时间∑-δadc 100可通过经由连续时间∑-δadc 100的一个或多个组件处理信号来支持信号的模数转换。连续时间∑-δadc100可包括回路滤波器104、多位量化器106、dac 112、失配传感器114和逻辑116。在图1

的例子中,多位量化器106嵌入有映射引擎108。因此,多位量化器106包括映射引擎108和量化器110。

36.连续时间∑-δadc 100的组件中的一个或多个可(例如,以操作方式、以通信方式、在功能上、以电子方式)彼此耦合。连续时间∑-δadc100的组件中的一个或多个可包括一个或多个输入和一个或多个输出。在一些实施例中,回路滤波器104可包括多个输入。举例来说,回路滤波器104可包括被配置成接收输入信号102(例如,模拟信号)的第一输入和耦合到dac 112的输出以接收另一信号(例如,反馈信号118)的第二输入。回路滤波器104还可包括耦合到多位量化器106的第一输入的输出。举例来说,回路滤波器104的输出可耦合到量化器110的输入。

37.多位量化器106可包括被配置成输出信号120(例如,数字信号)的输出。在一些实施例中,多位量化器106的输出可耦合到dac 112的输入。在一些实施例中,dac 112可包括耦合到失配传感器114的输入的第二输出。失配传感器114的输出可耦合到逻辑116的输入。在一些实施例中,失配传感器114可测量dac 112的元件之间的静态失配或动态失配或这两者,如本文所描述。逻辑116可配置有各种算法,包括:排序算法、映射算法或切换算法等等,以支持连续时间∑-δadc 100的线性化。在一些实施例中,逻辑116的输出可耦合到多位量化器106的第二输入。举例来说,逻辑116的输出可耦合到嵌入多位量化器106内的映射引擎108的输入。映射引擎108可耦合到多位量化器106内的量化器110。映射引擎108可配置有一个或多个电路元件,例如用于支持如本文所描述的线性化技术的开关。

38.图2是根据一些实施例的连续时间∑-δadc 200的框图。连续时间∑-δadc 200可实施前馈sdm架构。在连续时间∑-δadc 200的以下描述中,可从连续时间∑-δadc 200添加或省略某些组件。连续时间∑-δadc 200可通过经由连续时间∑-δadc 200的一个或多个组件处理信号来支持信号的模数转换。连续时间∑-δadc 200可包括一组求和节点(例如,求和节点204和求和节点208)、回路滤波器206、与对应延迟214相关联的量化器210、额外回路延迟(eld)补偿dac 220、主dac 224、失配传感器230、逻辑232和映射引擎236。在一些实施例中,连续时间∑-δadc 200可提供反馈回路,所述反馈回路可包括连续时间∑-δadc200的组件中的一个或多个(例如,求和节点204的第二输入、回路滤波器206的输入和输出两者、求和节点208的所有输入、量化器210的第一输入、eld dac 220的输入和输出两者、主dac 224的输入和输出两者,以及映射引擎236的第一输入),如本文所描述。

39.连续时间∑-δadc 200的组件中的一个或多个可(例如,以操作方式、以通信方式、在功能上、以电子方式)彼此耦合。连续时间∑-δadc200的组件中的一个或多个可包括一个或多个输入和一个或多个输出。求和节点204可包括一个或多个输入,例如用以接收信号的第一输入和耦合到主dac 224的第一输出以接收另一信号的第二输入。求和节点204还可包括耦合到回路滤波器206的输入以将信号输出到回路滤波器206的输出。回路滤波器206还可包括耦合到求和节点208的第一输入以从回路滤波器206接收信号的输出。求和节点208还可包括耦合到eld dac 220的输出以从eld dac 220接收信号的第二输入。量化器210可包括一个或多个输入,例如,耦合到求和节点208的输出以从求和节点208接收信号的第一输入,以及耦合到映射引擎236的输出以从映射引擎236接收信号的第二输入。

40.量化器210还可包括耦合到延迟214的输入以将信号输出到延迟214的输出,延迟214可包括一个或多个输出以及到主dac 224的用以将信号输出到主dac 224的输入,所述

输出包括用以提供输出信号216的第一输出、耦合到映射引擎236的第一输入以将信号输出到映射引擎236的第二输出,以及耦合到eld dac 220的输入以将信号输出到eld dac 220的第三输出。主dac 224还可包括耦合到失配传感器230的输入以将信号输出到失配传感器230的第二输出,失配传感器230可包括耦合到逻辑232的输入以将信号输出到逻辑232的输出。逻辑232可包括耦合到映射引擎236的第二输入以将信号输出到映射引擎236的输出。另外,映射引擎236可包括用以接收参考信号234的第三输入。

41.在图2的例子中,求和节点204可经由第一输入接收输入信号202,输入信号202可以是模拟信号。求和节点204还可经由第二输入从主dac 224的输出接收主反馈信号226。求和节点204可被配置成添加或减去信号,例如从主反馈信号226添加或减去输入信号202以产生所得信号。求和节点204可经由求和节点204的输出将所得信号提供到回路滤波器206的输入。回路滤波器206可由一个或多个电路元件构成。举例来说,回路滤波器206可由一个或多个电阻器和电容器构成。回路滤波器206还可与对连续时间∑-δadc 200建模的相应传递函数相关联。

42.回路滤波器206可经由回路滤波器206的输出将滤波后信号提供到求和节点208的第一输入。求和节点208还可经由第二输入从eld dac220的输出接收反馈eld补偿信号222。求和节点208可被配置成添加或减去信号,例如从反馈eld补偿信号222添加或减去滤波后信号以产生所得信号。求和节点208可经由求和节点208的输出将所得信号提供到量化器210的第一输入,量化器210还可在量化器的第二输入处从映射引擎236的输出接收所得信号212。量化器210可将求和节点208的模拟输出转换成数字代码。

43.映射引擎236可被配置成经由第三输入接收参考信号234。映射引擎236还可被配置成经由第二输入从逻辑232的输出接收所得信号。另外,或可替换的是,映射引擎236还可被配置成经由第一输入从延迟214的输出接收反馈信号216。在一些实施例中,失配传感器230可测量主dac 224的元件之间的静态失配或动态失配,或这两者。映射引擎236可配置有一个或多个电路元件,例如用于支持线性化技术的开关。

44.逻辑232可配置有各种算法,包括:排序算法、映射算法或切换算法等等,以支持连续时间∑-δadc 200的线性化。如图2的例子所示,将映射引擎236配置在参考234与量化器210(例如,多位量化器)之间,而不是将映射引擎236配置在量化器210与主dac 224之间。从求和节点208输出的模拟信号和来自映射引擎236的所得信号212可以是到量化器210(例如,多位量化器)的输入和到与量化器210相关联的延迟214的输入(τ1是量化器210的延迟214)。延迟214的输出可以是连续时间∑-δadc 200的输出信号216。

45.在图2的例子中,dac(例如,主dac 224、eld dac 220)具有非线性,并且这些非线性是dac元件(例如,主dac 224、eld dac220)的失配的结果,失配传感器230检测dac元件(例如,主dac 224、eld dac 220)的失配,基于从逻辑232或输出信号216或这两者接收的信息,映射引擎236可被配置成调整(例如,改变)参考连接到量化器210的次序。另外,映射引擎236可生成非线性的映射,并基于所识别的非线性而生成用于量化器210的校正信号。

46.在一些实施例中,量化器210(例如,多位量化器)可实施为闪存子adc。此闪存子adc可被配置成将量化器210的输入信号(其可为求和节点208的输出信号)与一系列参考(例如,参考电压或参考电流)进行比较。闪存子adc(例如,多位量化器210)中的单元1位比较器和主dac 224的单元元件可通过连接电路(例如,采样器、缓冲器、d触发器等)一对一地

318将参考代码(被称为ref代码)转换成参考电流。

52.n 1级量化器320可具有n个参考代码,可以是例如代码1、代码2

……

代码n。在一些实施例中,映射引擎334可配置有一个或多个开关以将输入代码1、代码2

……

代码n连接到输出ref代码1、ref代码2

……

ref代码n。在一些其它实施例中,映射引擎334可配置有一个或多个开关以基于所选择的次序将输入代码1、代码2

……

代码n连接到输出ref代码1、ref代码2

……

ref代码n。因此,可通过从映射引擎334的输入代码到输出代码的连接来实施特定操作,例如排序、映射或切换,或其任何组合。1位比较器(例如,锁存器316)和1位单元dac 318可一对一地连接。通过对量化器320的参考代码进行排序、映射或切换或其任何组合,可有效地实现对dac(例如,eld dac 314、主dac 324)的单元元件的等效排序、映射或切换或其任何组合。

53.连续时间∑-δadc 300可支持可能不需要来自量化器320输出的信息的线性化技术。在一些例子中,连续时间∑-δadc 300可执行排序线性化技术或映射线性化技术,或这两者。在这些例子中,利用关于dac(例如,eld dac 314、ref dac 318、主dac 324)的单元元件的静态失配和动态失配的测量信息,可以通过逻辑332计算dac(例如,eld dac 314、ref dac 318、主dac 324)的单元元件的特定次序。在dac的操作中,此次序可以是固定的。在一些实施例中,映射引擎334可被配置成以特定最优次序在输入代码与输出代码之间实施固定连接。在这种情况下,由于映射引擎334在连续时间∑-δadc 300的操作期间未进行切换,因此其延迟是无害的。

54.一些线性化技术,例如切换线性化技术,可能不需要来自量化器320输出的信息,这些技术例如随机化线性化技术。在此例子中,dac(例如,eld dac 314、ref dac 318、主dac 324)的单元元件的次序被随机切换。在这种情况下,在切换之后,例如,ref dac 318输出电流和比较器输入可在比较器的下一采样时刻之前稳定。因此,在这种情况下,当切换发生时映射引擎334的延迟可以小于连续时间∑-δadc 300的一个采样时钟周期。如图3所示,连续时间∑-δadc 300的主反馈回路和eld反馈回路对速度的要求很苛刻并且对额外延迟很敏感。ref dac 318和映射引擎334被配置成用于dac线性化技术。对于映射引擎334在连续时间∑-δadc 300的操作期间进行切换的情况,在一些实施例中,ref dac 318和映射引擎334具有最多一个采样时钟周期,以在切换发生时稳定。

55.图4是根据一些实施例的连续时间∑-δadc 400的框图。在连续时间∑-δadc 400的以下描述中,可从连续时间∑-δadc 400添加或省略某些组件。连续时间∑-δadc 400可实施如图1所描述的连续时间∑-δadc 100的各方面。举例来说,连续时间∑-δadc 400可实施前馈sdm架构。连续时间∑-δadc 400可包括可被配置成添加或减去信号的求和节点,例如求和节点404和求和节点412。连续时间∑-δadc 400可包括回路滤波器408,回路滤波器408可由一个或多个电路元件(例如,一个或多个电阻器、电容器、电感器等)构成。连续时间∑-δadc 400还可包括放大器410、eld dac 414、ref dac 418、锁存器416、主dac 424、失配传感器430、逻辑432和映射引擎434。连续时间∑-δadc400的组件中的一个或多个可(例如,以操作方式、以通信方式、在功能上、以电子方式)彼此耦合。在一些实施例中,连续时间∑-δadc 400可提供反馈回路,所述反馈回路可包括连续时间∑-δadc 400的组件中的一个或多个,如本文所描述。

56.求和节点404可包括一个或多个输入,例如用以接收信号的第一输入和耦合到主

dac 424的第一输出以接收另一信号的第二输入。求和节点404还可包括耦合到回路滤波器408的输入以将信号输出到回路滤波器408的输出。回路滤波器408还可包括耦合到放大器410的输入以从回路滤波器408接收信号的输出。求和节点412可包括一个或多个输入,包括耦合到放大器410的输出以接收放大后信号的第一输入、耦合到ref dac 418的输出以从ref dac 418接收信号的第二输入,以及耦合到eld dac 414的输出以从eld dac 214接收信号的第三输入。

57.求和节点412可包括耦合到锁存器416的输入的输出。锁存器416可包括用以提供输出信号(例如,输出信号420)的输出。锁存器416的输出可耦合到eld dac 414的输入和到主dac 424的输入。主dac424可包括耦合到失配传感器430的输入的第二输出,失配传感器430可包括耦合到逻辑432的输入的输出。逻辑432可包括耦合到映射引擎434的第一输入的输出。映射引擎434可包括用以接收一组代码的一组第二输入,以及用以将参考代码提供到ref dac 418的输入的一组输出。另外,映射引擎434可包括耦合到锁存器416的输出以接收输出信号420的第三输入。

58.因此,在图4的例子中,输出信号420也是映射引擎434的输入。这些类型的dac线性化技术的一些例子是动态加权平均线性化技术和随机化动态加权平均线性化技术。在图4的例子中,σ-δ调制器的主反馈回路以及dac线性化回路(部分)解耦。dac线性化回路可包括比较器(即,锁存器416)、映射引擎434、ref dac 418和eld求和节点412。sdm主反馈回路可包括比较器(即,锁存器416)、主dac 424、回路滤波器408、gm单元(即,放大器410)和eld求和节点412。因此,sdm主反馈回路和dac线性化回路可分别针对其不同的要求进行优化。

59.在一些实施例中,例如,主dac 424可具有噪声和匹配要求。因此,主dac 424的单元元件可在相对大的电流(例如,针对更低的热噪声)和相对大的区域(针对更好的匹配和更低的闪烁噪声)内。在一些实施例中,多位量化器中的ref dac 418可具有比主dac 424更宽松的噪声和匹配要求,因为ref dac 418贡献的噪声和非线性由sdm进行噪声整形。因此,与可将映射引擎配置在比较器与主dac 424之间的一些方法相比,将映射引擎434配置在比较器和ref dac 418之间可能是有益的。

60.如图4所示,连续时间∑-δadc 400可包括sdm的主反馈回路、eld反馈回路和dac线性化回路。在一些实施例中,dac线性化回路的总延迟可以是最多一个采样时钟周期。在一些实施例中,主反馈回路的总延迟也可以是最多一个采样时钟周期。在一些实施例中,可不基于量化器输出的当前样本而选择主dac 424的单元元件。实际上,可基于量化器输出的先前样本而选择要使用的主dac 424的单元元件的次序。

61.图5是根据一些实施例的连续时间∑-δadc 500的晶体管级实施方案的框图。在连续时间∑-δadc 500的以下描述中,可从连续时间∑-δadc 500添加或省略某些组件。连续时间∑-δadc 500可支持一种或多种线性化技术,例如dac线性化技术。在一些实施例中,连续时间∑-δadc 500可支持不需要量化器输出的线性化技术。

62.在示例晶体管级实施方案中,gm单元、eld dac 510、相关联参考电流528、锁存器530、采样保持(s&h)电路538和缓冲器540构成eld补偿的量化器的切片。所提出的连续时间∑-δadc 500的晶体管级电路实施方案详细示出复制的求和节点和1位比较器的第m个切片。在图5的例子中,sdm使用(n 1)级量化。因此,sdm具有复制的求和节点和1位比较器的共计n个切片。

63.在一些实施例中,回路滤波器506具有差分电压输出vi

和vi-。这些差分电压信号利用源退化跨导(gm)级516转换成差分电流信号。在一些实施例中,gm单元可实施为源退化pmos跨导放大器,所述源退化pmos跨导放大器由电流源i

s 506、源退化电阻器r

s 508、电容器cs510和薄氧化物pmos晶体管m1、m

2 518构成。在一些实施例中,源退化可用于改善gm单元在

±

250mv的大输入摆幅下的线性。可在m1、m

2 518的源极处添加电容器cs以在gm级516(v/i转换器)的传递函数中生成零并补偿gm级516的相移/延迟。电流源i

s 506可以例如实施为级联pmos电流源。

64.在一些实施例中,gm单元的带宽可能会影响外部反馈回路的稳定性,但不会影响快速反馈回路的稳定性。eld dac 510可实施为电流舵型dac。nmos开关m3、m

4 514和电流源i

dac,u 512可构成单元eld dac。nmos晶体管m5、m

6 522和电流源i

ref,u 524可构建单元参考dac(ref dac)。在一些实施例中,对于n 1级量化,可能需要创建n个参考级,并且因此,每个切片可能需要n-1个参考电流单元。参考dac将数字输入代码(即,参考代码)转换成输出电流。图5所示的n 1级量化器具有n个参考代码,即ref代码1、ref代码2

……

ref代码n。这n个参考代码可以是n个输入代码{代码1、代码2

……

代码n}的排列。映射引擎550在从输入代码{代码1、代码2

……

代码n}到其输出代码{ref代码1、ref代码2

……

ref代码n}的连接上应用特定的排序操作、映射操作和/或切换操作。

65.eld dac可以是由nmos晶体管m

3-m

4 514和电流源i

dac,u 512构成的n 1级电流舵型dac。eld dac的实施方式与参考dac类似,但eld dac的开关由n 1级量化器的数字输出控制。参考dac和eld dac中的电流源可以例如实施为级联nmos电流源。

66.在锁存器块之后,使用具有互补采样时钟(clkp

sh 536和clkn

sh 532)的传输门(m7、m

8 534)对锁存器530的末端处的锁存器输出进行采样。在一些实施例中,在采样后锁存器输出与eld dac的输入之间插入两个缓冲器540。对缓冲器数量的选择是最小化锁存器的负载电容与减少缓冲器延迟之间的权衡。第一缓冲器(m9、m

10 542-1)是具有pmos负载的nmos缓冲器,而第二缓冲器(m

11

、m

12 542-2)是cmos缓冲器。在一些实施例中,nmos缓冲器的输入电容可低于cmos缓冲器的输入电容,但nmos缓冲器消耗更多功率。cmos缓冲器供轨对轨驱动能力。对于n 1级量化,一个采样后锁存器输出节点应在两个缓冲器之后驱动n个单元eld dac。因此,s&h电路(通过门m

7-m8)使用采样时钟clk

sh

对锁存器输出进行采样。在此之后,采样后量化器输出经过由m

9-m

12

构成的两个缓冲器。由m

9-m

10

构成的第一缓冲器是具有pmos负载的nmos缓冲器。由m

11-m

12

构成的第二缓冲器是cmos缓冲器(cmos反相器)。第二缓冲器输出d

、d-是sdm的数字输出v,并且所述第二缓冲器输出d

、d-还驱动主dac和eld dac。由于1位锁存器通过s&h电路和缓冲器一对一地连接到dac单元元件,因此通过对参考dac的参考代码进行排序、映射、切换,可以有效地实现dac单元元件的对应排序、映射、切换。

67.在一些实施例中,参考电流可被设计成对于每个切片具有相同的共模电流(即,i

refp,1

i

refn,1

=i

refp,2

i

refn,2

=

……

=i

refpn

i

refn,n

)。差分参考电流信号i

refp,m-i

refn,m

对于每个切片可能不同。在一些实施例中,源退化gm级、连接电路、锁存器和采样器对于这n个切片完全相同。第m个eld dac可以是n 1级电流舵型dac。

68.在一些实施例中,可通过执行软件的处理系统的一个或多个处理器实施上文所描述的技术的某些方面。软件包括存储或以其它方式有形地体现在非暂时性计算机可读存储介质上的一组或多组可执行指令。软件可包括指令和某些数据,这些指令和数据在由一个

或多个处理器执行时,操控所述一个或多个处理器以执行上文所描述的技术的一个或多个方面。非暂时性计算机可读存储介质可包括例如磁盘或光盘存储装置、例如闪存器等固态存储装置、高速缓冲存储器、随机存取存储器(ram)或其它一个或多个非易失性存储器装置等等。存储在非暂时性计算机可读存储介质上的可执行指令可以呈源代码、汇编语言代码、目标代码的形式,或呈可通过一个或多个处理器解译或以其它方式执行的其它指令格式的形式。

69.计算机可读存储介质可以包括在使用期间可由计算机系统存取以将指令和/或数据提供到计算机系统的任何存储介质或存储介质的组合。此类存储介质可包括但不限于光学介质(例如,压缩光盘(cd)、数字多功能光盘(dvd)、蓝光光盘)、磁性介质(例如,软盘、磁带,或磁性硬盘驱动器)、易失性存储器(例如,随机存取存储器(ram)或高速缓冲存储器)、非易失性存储器(例如,只读存储器(rom)或闪存器),或基于微机电系统(mems)的存储介质。计算机可读存储介质可嵌入计算系统(例如,系统ram或rom)中、固定地附接到计算系统(例如,磁性硬盘驱动器)、以可移除方式附接到计算系统(例如,光学光盘或基于通用串行总线(usb)的闪存器),或经由有线或无线网络(例如,网络可存取存储装置(nas))耦合到计算机系统。

70.应注意,上文在总体描述中所描述的活动或元素并非全部是需要的,可能不需要特定活动或装置的一部分,并且除所描述的那些活动或元素之外,可执行一个或多个另外的活动或包括一个或多个另外的元素。举例来说,对于一些dac线性化技术,例如随机化,不需要关于dac单元元件失配的信息。在这种情况下,不需要失配传感器114、230、330、430、546。另外,列出活动的次序未必是执行活动的次序。另外,已经参考特定实施例描述了概念。然而,本领域的技术人员了解,可以在不脱离如所附权利要求书中所阐述的本公开的范围的情况下进行各种修改和改变。尽管在图1-5中作为例子示出了前馈sdm架构,但本公开还可以用于其它sdm架构,例如反馈架构和混合前馈-反馈架构。尽管在图1-5中作为例子示出了单回路sdm架构,但本公开还可以用于其它sdm架构,例如多级噪声整形(mash)架构。因此,应在说明性而非限制性意义上看待本说明书和图式,并且预期所有这些修改都包括在本公开的范围内。

71.上文已关于特定实施例描述了益处、其它优点和问题的解决方案。然而,所述益处、优点、问题的解决方案以及可以使任何益处、优点或解决方案出现或变得更显著的任何特征不应解释为任何或所有权利要求的关键,必需或必要特征。此外,上文所公开的特定实施例仅是说明性的,因为所公开的主题可按得益于本文中的教示的本领域的技术人员显而易见的不同但等效的方式修改和实践。除了如所附权利要求书中所描述的内容以外,并不意图限制本文中所示的构造或设计的细节。因此,显而易见的是,可更改或修改上文公开的特定实施例,并且所有这些变化被视为在所公开的主题的范围内。因此,本文寻求的保护如所附权利要求中所阐述。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。