1.本发明与显示装置有关,尤其是关于一种应用于显示面板的源极驱动电路。

背景技术:

2.一般而言,外界的静电放电(electrostatic discharge,esd)干扰通常会造成车用源极驱动集成电路的运作在短时间内出现异常,因而导致车用显示面板的显示画面会有短时间的闪屏或闪线等画面异常发生,导致观看显示画面的人的视觉感受不佳。

3.目前业界所采用的最高等级(class a)的静电放电防护规范为:在静电放电干扰下,车用显示面板所显示的画面不能出现闪屏及闪线等画面异常。虽然车用源极驱动集成电路已有针对静电放电干扰的现有电路对策,然而,该些电路对策仍可能因为显示面板的液晶特性及电路信号搭配错位等因素而失效,导致车用显示面板的显示画面仍出现闪屏及闪线等画面异常,亟待进一步加以改善。

4.此外,现有的电路对策并不适用于包括线缓冲器(line buffer)或帧缓冲器(frame buffer)的车用源极驱动集成电路,故仍需进一步提出相对应的电路对策,以改善上述显示画面异常的现象。

技术实现要素:

5.有鉴于此,本发明提出一种应用于显示面板的源极驱动电路,以有效解决现有技术所遭遇到的上述问题。

6.依据本发明的一具体实施例为一种源极驱动电路。于此实施例中,源极驱动电路耦接显示面板及栅极驱动电路。源极驱动电路包括数据输出单元、输出致能单元及时序控制单元。数据输出单元耦接显示面板,用以提供数据信号给显示面板。静电放电侦测单元用以于侦测到静电放电事件发生时提供静电放电侦测信号。输出致能单元耦接静电放电侦测单元及栅极驱动电路,用以根据静电放电侦测信号提供输出致能信号给栅极驱动电路,致使栅极驱动电路发出给显示面板的栅极驱动信号处于低电位。时序控制单元耦接静电放电侦测单元及栅极驱动电路,用以于静电放电侦测信号启动时将原本提供给栅极驱动电路的第一时脉信号(ckva)切换为第二时脉信号(ckvb)并且于静电放电侦测信号结束时切换回第一时脉信号,致使显示面板所显示的画面符合特定规范。

7.于一实施例中,该显示面板为车用显示面板且该源极驱动电路为车用源极驱动电路。

8.于一实施例中,该特定规范为在该静电放电事件发生时,该显示面板所显示的画面不能出现闪屏或闪线的现象。

9.于一实施例中,当该静电放电侦测信号未启动时,该栅极驱动电路接收到该第一时脉信号且当该静电放电侦测信号启动时,该栅极驱动电路仍能接收到该第二时脉信号,由以避免该栅极驱动电路所输出的栅极输出信号对应于错误的数据信号而造成该显示面板所显示的画面出现抖动。

10.于一实施例中,该时序控制单元包括:一第一时脉提供单元,用以提供该第一时脉信号;一第二时脉提供单元,用以提供该第二时脉信号;以及一多工输出单元,分别耦接该静电放电侦测单元、该第一时脉提供单元及该第二时脉提供单元,用以根据该静电放电侦测信号选择性地输出该第一时脉信号或该第二时脉信号。

11.于一实施例中,该时序控制单元还包括一振荡器(osc),耦接该第二时脉提供单元,用以模拟该第一时脉信号(ckva)产生该第二时脉信号(ckvb)给该第二时脉提供单元。

12.于一实施例中,该源极驱动电路包括k条线的线缓冲器(line buffer),若该静电放电事件发生于一显示帧的第n条线,则该输出致能信号于该显示帧的第(n k)条线才开始让该栅极驱动信号处于低电位,其中n与k为正整数。

13.相较于现有技术,本发明的源极驱动电路可在侦测到静电放电事件发生时输出具有高阻抗(hiz)的数据信号给显示面板或输出模拟的时脉信号给栅极驱动器,由以有效避免传统上由于显示面板的液晶特性或电路信号搭配错位等因素而导致其显示画面出现闪屏及闪线等异常。此外,本发明亦有考量到源极驱动电路具有线缓冲器(line buffer)或帧缓冲器(frame buffer)的情况提出相对应的电路对策,故亦可适用之。

14.关于本发明的优点与精神可以通过以下的发明详述及附图得到进一步的了解。

附图说明

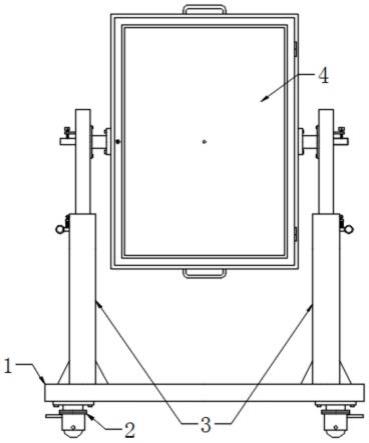

15.图1为显示装置包括显示面板、源极驱动电路及栅极驱动电路的示意图。

16.图2为根据本发明的一较佳具体实施例中的源极驱动电路的功能方块图。

17.图3为当侦测到静电放电事件发生时源极驱动电路输出具有高阻抗(hiz)的数据信号并提供输出致能信号使栅极驱动电路发出低电位的栅极驱动信号的时序图。

18.图4为通过高阻抗(hiz)的数据信号及低电位的栅极驱动信号消除显示面板中的漏电路径的示意图。

19.图5为根据本发明的另一较佳具体实施例中的源极驱动电路的功能方块图。

20.图6a为传统上由于在侦测到静电放电事件发生期间无时脉信号存在导致电路信号搭配错位的时序图。

21.图6b为本发明即使在侦测到静电放电事件发生期间亦有模拟的时脉信号存在以有效避免电路信号搭配错位的时序图。

22.图7为于源极驱动电路具有6条线的线缓冲器的情况下,输出致能信号遮蔽起点会比侦测到esd事件发生晚6条线的示意图。

23.图8a及图8b为于源极驱动电路具有帧缓冲器的情况下,输出致能信号遮蔽起点会在侦测到esd事件发生的下一帧的示意图。

24.主要元件符号说明:

25.1...显示装置

26.da...显示面板

27.sic...源极驱动电路

28.gic...栅极驱动电路

29.sda...源极数据信号

30.gp...栅极驱动信号

31.oe...输出致能信号

32.ckv...时脉信号

33.2...源极驱动电路

34.20...静电放电侦测单元

35.22...输出致能单元

36.24...数据输出单元

37.gd...栅极驱动电路

38.pl...显示面板

39.esds...静电放电侦测信号

40.t1~t19...时间

41.din...输入数据

42.vs...场同步信号

43.de...有效显示数据选通信号

44.bk...空白区间

45.fn~f(n 4)...帧

46.hiz...高阻抗

47.gl1~gl2...栅极驱动线

48.sl1~sl2...源极驱动线

49.vcom...共同电压

50.vgl...低电位

51.m11、m12、m21、m22...晶体管开关

52.cs...电容

53.4...源极驱动电路

54.40...介面单元

55.42...时序控制单元

56.420...第一时脉提供单元

57.422...第二时脉提供单元

58.424...振荡器

59.428...多工输出单元

60.ckva...第一时脉信号

61.ckvb...第二时脉信号

62.sda1~sda7...源极数据信号

63.g(n)~g(n 3)...栅极输出信号

64.6...显示装置

65.ln...第n条线

66.l(n 6)...第(n 6)条线

67.sp...遮蔽起点

具体实施方式

68.现在将详细参考本发明的示范性实施例,并在附图中说明所述示范性实施例的实例。在附图及实施方式中所使用相同或类似标号的元件/构件是用来代表相同或类似部分。

69.依据本发明的一具体实施例为一种显示面板的源极驱动电路。于此实施例中,显示面板可以是车用显示面板且源极驱动电路可以是车用源极驱动电路,但不以此为限。

70.请参照图1,图1为显示装置包括显示面板、源极驱动电路及栅极驱动电路的示意图。

71.如图1所示,显示装置1包括显示面板da、源极驱动电路sic及栅极驱动电路gic。栅极驱动电路gic提供栅极驱动信号gp给显示面板da。源极驱动电路sic提供源极数据信号sda给显示面板da。此外,源极驱动电路sic还会提供输出致能信号oe及时脉信号ckv给栅极驱动电路gic。

72.接着,请参照图2,图2为此实施例中的源极驱动电路的功能方块图。

73.如图2所示,源极驱动电路2耦接显示面板pl及栅极驱动电路gd。源极驱动电路2包括静电放电侦测单元20、输出致能单元22及数据输出单元24。静电放电侦测单元20用以于侦测到静电放电事件发生时提供静电放电侦测信号esds。输出致能单元22耦接静电放电侦测单元20及栅极驱动电路gd,用以根据静电放电侦测信号esds提供输出致能信号oe给栅极驱动电路gd,致使栅极驱动电路gd提供给显示面板pl的栅极驱动信号gp处于低电位(vgl)。数据输出单元24耦接静电放电侦测单元20及显示面板pl,用以根据静电放电侦测信号esds提供具有高阻抗(hiz)的数据信号sda给显示面板pl,致使显示面板pl所显示的画面能够符合特定规范。于实际应用中,上述的特定规范是指在静电放电事件发生时,显示面板pl所显示的画面不能出现闪屏或闪线等异常现象,但不以此为限。

74.举例而言,如图3所示,在第n帧fn及第(n 1)帧f(n 1)期间,由于并无任何静电放电事件发生,所以静电放电侦测信号esds均未启动而维持于低电位,并且源极驱动电路sic提供给栅极驱动电路gic的输出致能信号oe及时脉信号ckv、源极驱动电路sic提供给显示面板pl的数据信号sda以及栅极驱动电路gd提供给显示面板pl的栅极驱动信号gp均维持正常。

75.于时间t5进入第(n 2)帧f(n 2)后,尚无任何静电放电事件发生,故一切仍维持正常。直至时间t6,由于静电放电侦测单元20侦测到静电放电事件发生时,所以静电放电侦测信号esds会由低电位变为高电位,以指示静电放电事件的发生。

76.此时,输出致能单元22提供高电位的输出致能信号oe给栅极驱动电路gd,致使栅极驱动电路gd提供低电位(vgl)的栅极驱动信号gp给显示面板pl。数据输出单元24同时提供具有高阻抗(hiz)的数据信号sda给显示面板pl。由此,显示面板pl的各画素中的漏电路径可被消除,故能避免显示面板pl的显示画面在静电放电事件发生时出现闪屏或闪线等异常现象。

77.需说明的是,上述运作可持续至第(n 2)帧f(n 2)结束为止,或是视实际需求延续至第(n 3)帧f(n 3),甚至第(n 4)帧f(n 4)或更多帧,并无特定的限制。

78.接着,请参照图4,显示面板3包括多个画素且每一个画素分别包括晶体管开关及电容。若以左上角的画素为例,其晶体管开关m11的栅极耦接用以传送处于低电位(vgl)的栅极驱动信号的栅极驱动线gl1,电容cs耦接晶体管开关m11的一端且晶体管开关m11的另

一端耦接具有高阻抗(hiz)的数据信号sda,由以消除电容cs所储存的电荷的漏电路径。至于其他画素亦可依此类推,于此不另行赘述。由此,由于显示面板pl的所有画素中的可能的漏电路径均已被消除,故可有效避免显示面板pl所显示的画面出现闪屏现象。

79.于另一实施例中,源极驱动电路还可包括时序控制单元,用以产生时脉信号ckv给栅极驱动电路。请参照图5,图5为此实施例中的源极驱动电路的功能方块图。

80.于源极驱动电路4中,时序控制单元42耦接介面单元40。介面单元40提供第一时脉信号ckva给时序控制单元42。时序控制单元42包括第一时脉提供单元420、第二时脉提供单元422、振荡器424及多工输出单元428。第一时脉提供单元420及第二时脉提供单元422均耦接至多工输出单元428。第一时脉提供单元420还耦接介面单元40。第二时脉提供单元422还耦接振荡器424。

81.第一时脉提供单元420用以提供介面单元40的第一时脉信号ckva给多工输出单元428。振荡器424用以模拟第一时脉信号ckva而产生第二时脉信号ckvb至第二时脉提供单元422,并由第二时脉提供单元422提供给多工输出单元428。

82.当多工输出单元428接收到静电放电侦测信号esds时,多工输出单元428根据静电放电侦测信号esds是否启动选择性地输出第一时脉信号ckva或第二时脉信号ckvb。举例而言,当静电放电侦测信号esds启动时,代表有侦测到静电放电事件发生,此时,多工输出单元428即会从原本提供第一时脉信号ckva切换为提供第二时脉信号ckvb。当静电放电侦测信号esds结束时,代表静电放电事件已结束,此时,多工输出单元428即会再从提供第二时脉信号ckvb切换回提供第一时脉信号ckva。

83.需说明的是,由于第二时脉信号ckvb是由振荡器424用拟第一时脉信号ckva而得,所以第二时脉信号ckvb应相同于第一时脉信号ckva,但不以此为限。

84.如图6a所示,传统上由于源极驱动电路在侦测到静电放电事件发生期间会停止传送时脉信号ckv给栅极驱动电路,容易造成电路信号搭配错位(例如栅极驱动电路所输出的栅极输出信号g(n 1)~g(n 3)分别对应于错误的数据信号)而导致显示面板的显示画面抖动。

85.相反地,如图6b所示,由于本发明的源极驱动电路4在侦测到静电放电事件发生期间仍会输出模拟的第二时脉信号ckvb给栅极驱动电路,故能有效避免电路信号搭配错位的情况发生,使得栅极驱动电路所输出的栅极输出信号能对应于正确的数据信号,使得显示面板的显示画面不会出现抖动。

86.此外,由于源极驱动电路亦可设置有线缓冲器(line buffer)或帧缓冲器(frame buffer),因此,本发明针对上述情况分别提出相对应的电路对策如下。

87.请参照图7,于一实施例中,假设源极驱动电路sic包括6条线的线缓冲器,因此,在考量到线缓冲器的情况下,输出致能信号oe的遮蔽起点sp将会比侦测到esd事件发生时的第n条线ln还延后6条线,亦即此实施例中的输出致能信号oe的遮蔽起点sp将会是第(n 6)条线l(n 6),但不以此为限。

88.接着,请参照图8a及图8b,于另一实施例中,假设源极驱动电路sic包括帧缓冲器,因此,在考量到帧缓冲器的情况下,当在第n帧fn侦测到esd事件发生时,此实施例中的输出致能信号oe的遮蔽起点sp将会从下一帧开始,亦即从第(n 1)帧f(n 1)开始,但不以此为限。

89.相较于现有技术,本发明的源极驱动电路可在侦测到静电放电事件发生时输出具有高阻抗(hiz)的数据信号给显示面板或输出模拟的时脉信号给栅极驱动器,由以有效避免传统上由于显示面板的液晶特性或电路信号搭配错位等因素而导致其显示画面出现闪屏及闪线等异常。此外,本发明亦有考量到源极驱动电路具有线缓冲器(line buffer)或帧缓冲器(frame buffer)的情况提出相对应的电路对策,故亦可适用之。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。