无漂移相变存储器

发明领域

1.本发明总体上涉及相变存储器,并且更具体地涉及无漂移的相变(phase-change)存储器的制造。

背景技术:

2.相变存储器(pcm)是一种类型的非易失性随机存取存储器(nvram)。相变存储器可被称为pcm或pcram。pcm使用相变材料的独特性质来存储非晶相和结晶相两者中的信息。该材料可以在相之间快速且重复地切换。这种切换经常通过经由光脉冲加热或电加热来完成。

3.信息或数据存储在材料的相中。可以通过测量pcm单元的电阻来读取该数据。pcm可以提供更快的ram速度,但是以低功率需求存储数据。

4.pcm使用特殊合金,包括碲锗锑(germanium antimony tellurium)(gst)。可以用热改变gst以具有两种不同的状态或“相”(结晶的和无定形的)。

技术实现要素:

5.本发明的实施例包括一种用于制造相变存储器(pcm)的方法。在实施例中,底部电极沉积在衬底的顶部上。介电材料层沉积在底部电极的顶部上。在介电材料层中产生孔。在介电材料层上旋涂(spun)并烘烤剥离层。在剥离层上旋涂并烘烤光致抗蚀剂层。执行uv光刻以在介电材料层中的孔上方产生开口。ag层沉积在剩余的图案化的介电材料层和光致抗蚀剂层的顶部上。在ag层的顶部上沉积碲锗锑(gst)层。顶部电极沉积在gst层的顶部上。去除ag层、gst层和位于光致抗蚀剂层顶部上的顶部电极以及光致抗蚀剂层和剥离层。

附图说明

6.图1a、1b、1c、1d、1e、1f和1g是描绘根据本发明的第一实施例的包括ag和gst层的结构的示意图(通过截面图);

7.图2a、2b、2c、2d、2e、2f、2g和2h是描绘根据本发明的第二实施例的包括两个ag层和gst层的结构的示意图(通过截面图);

8.图3a、3b、3c、3d、3e、3f和3g是描绘根据本发明的第三实施例的包括ag和gst层的结构的示意图(通过截面图);以及

9.图4a、图4b、图4c、图4d、图4e和图4f是描绘根据本发明的第四实施例的包括ag掺杂gst层的结构的示意图(通过截面图)。

具体实施方式

10.本发明的实施例大体上提供一种用于制造相变存储器(pcm)的方法。具体地,本发明的实施例通过包括蒸发和溅射的物理沉积技术来提供ag和碲锗锑(gst)的多层叠置体,以使相变存储器结构中的复位电阻漂移最小化。

11.本发明的实施例认识到,在相变材料中存在有害电阻漂移。通常,相变材料的电阻应当随时间保持恒定。不幸的是,这种电阻漂移破坏相变存储器的稳定性并且限制发展。具体地,本发明的实施例通过在顶部电极与底部电极之间沉积ag和gst的不同层来减小相变材料中的电阻漂移。

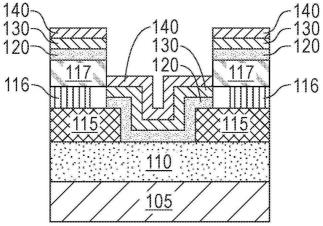

12.本技术的申请人已经出乎意料地确定,与其中使用非ag掺杂的gst合金层的等效pcm单元相比,银(ag)和ge2sb2te5(gst)的多层结构作为pcm材料的存在可以减少pcm单元的复位状态电阻漂移。贯穿本技术使用术语“ag和ge2sb2te5(gst)的多层结构”表示gst合金,其中ag作为有意添加的杂质存在。在沉积期间以及在设定和复位操作期间gst中的ag的迁移使复位状态中的电阻漂移最小化。

13.本文公开了要求保护的结构和方法的实施例的详细描述;然而,应当理解的是,所公开的实施例仅仅是可以以各种形式体现要求保护的结构和方法的说明。此外,结合各种实施方式给出的每个实例旨在是说明性的而非限制性的。此外,附图不一定按比例绘制,可以放大一些特征以示出特定部件的细节。因此,本文所公开的具体结构和功能细节不应被解释为限制性的,而仅仅是用于教导本领域技术人员以不同方式采用本发明的方法和结构的代表性基础。

14.说明书中对“一个实施方式”、“实施方式”、“示例性实施方式”等的引用表示所描述的实施方式可包括特定的特征、结构或特性,但是每个实施方式可能不一定包括特定的特征、结构或特性。此外,这样的短语不一定指相同的实施方式。进一步,当结合实施例描述特定特征、结构或特性时,认为结合其他实施例(无论是否明确描述)影响这样的特征、结构或特性在本领域技术人员的知识范围内。

15.出于下文描述的目的,术语“上”、“下”、“右”、“左”、“竖直”、“水平”、“顶部”、“底部”及其派生词应涉及如在附图中定向的所披露的结构和方法。术语“覆盖”、“顶部”、“定位在

…

上”或“定位在

…

顶部”是指第一元件(如第一结构)存在于第二元件(如第二结构)上,其中插入元件(如界面结构)可以存在于第一元件与第二元件之间。术语“直接接触”是指诸如第一结构的第一元件和诸如第二结构的第二元件在两个元件的界面处没有任何中间导电、绝缘或半导体层的情况下连接。术语非晶体是指非晶体、纳米晶体或微晶体。术语结晶是指单晶(即,单晶)或多晶(即,多晶)。

16.典型的pcm单元包括第一电极、呈现原子序变化(从晶体到非晶体,或反之亦然)的pcm材料以及第二电极的材料堆叠。例如,由碲锗锑(ge2sb2te5或gst)合金构成的pcm材料在结晶状态下呈现低电阻(即,置位状态),而在非晶态下gst合金呈现高电阻(即,复位状态)。在典型的pcm单元中,第一和第二电极由诸如氮化钛(tin)或钨(w)的导电材料构成,而pcm材料由硫族化物(即,包括来自元素周期表第16族的元素和更正电的元素的材料)构成。典型地,提供pcm材料的硫族化物是gst。

17.现在参见图1a-1g,图1a-1g示出了根据本发明的第一实施例的形成相变存储器的第一方法。在第一方法中,首先沉积ag层,接着在顶部电极与底部电极之间的图案化介电材料层中沉积gst层。参见图1a-1f,存在描绘存储器结构的示意图(通过截面图),该存储器结构包括衬底105、底部电极110、图案化的电介质层115、ag层120、gst层130和顶部电极140。

18.在第一实施例中,图1a示出存储器结构的第一层,衬底105具有位于衬底105顶部上的底部电极110。在第一实施例中,衬底105由导电、非导电或半导体材料(例如,硅)构成。

底部电极110由第一导电材料构成。提供底部电极110的第一导电材料可以是导电金属或导电金属氮化物。在本技术的一个实施例中,底部电极110可以由氮化钛(tin)、氮化钽(tan)或钨(w)组成。底部电极110可以具有从10nm至100nm的厚度;尽管底部电极110的其他厚度是预期的并且可以在本技术中采用。底部电极110可以通过包括例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)、溅射、化学溶液沉积或电镀的沉积工艺形成。

19.在第一实施例中,图1b示出了毯状介电材料层115,例如二氧化硅或氮化硅。毯状介电材料层115可具有10nm至100nm的厚度;尽管在本技术中设想并可采用毯状介电材料层115的其他厚度。毯状介电材料层115可通过沉积工艺形成,沉积工艺包括例如化学气相沉积

20.(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射。

21.在第一实施例中,图1c描绘了图1b的介电材料层115,该介电材料层115包括1微米或更小的横向尺寸的孔,该孔现在被称为图案化的介电材料层115,该图案化的介电材料层115允许层被放置在图案化的介电材料层115的顶部上,并且放置在顶部上的该层可以与底电极110接触。在实施例中,在图案化的介电材料层115中可以存在单个孔。在替代实施例中,在图案化的介电材料层115中可存在一个以上的孔。在又一替代实施例中,任何孔可位于图案化介电材料层115的任何位置。在实施例中,通过光学或电子束光刻来产生孔,并且通过反应性等离子体蚀刻或离子束溅射来蚀刻孔。

22.在第一实施例中,图1d首先通过光刻曝光和显影产生剥离图案(层116和117)。图1d的结构示出了ag层120,ag层120沉积在图案化的介电材料层115和底部电极110的暴露层的顶部上并且与底部电极110直接接触。在实施例中,ag层120具有小于20纳米(nm)的厚度。在替代实施例中,ag层120具有在5nm与10nm之间的厚度。在实施例中,使用热蒸发在图案化的介电材料层115上沉积ag层120。在实施方式中,使用剥离层116和光致抗蚀剂层117以覆盖图案化的介电材料层115,但是将图案化的介电材料层115中的孔和孔周围的区域暴露于ag层120,但是不允许整个剩余的图案化的介电材料层115被覆盖在ag层120中。在实施例中,剥离层116和光致抗蚀剂层117被旋涂和烘烤。在实施例中,通过穿过掩模曝光uv光来制成或多个孔,其中图案与图案化电介质层中的或多个孔对准,并且剥离层116被显影剂底切(undercut)。

23.在第一实施例中,在图1e中,gst层130沉积在ag层120的顶部上并且直接接触。在实施例中,gst层130具有小于200nm的厚度。在替代实施例中,gst层130具有在20nm与50nm之间的厚度。在实施例中,使用物理溅射并且更具体地射频(rf)溅射将gst层130沉积在ag层120上。在实施例中,使用剥离层116和光致抗蚀剂层117,以便覆盖图案化的介电材料层115,但是将图案化的介电材料层115中的孔和孔周围的区域暴露于ag层120,但是不允许gst层130中覆盖整个剩余的图案化的介电材料层115。在实施例中,gst层130覆盖ag层120但不覆盖任何其他层。在实施例中,当沉积gst层130时,gst层130与ag层120混合,在不同层的沉积期间并且由于热混合形成单层(未示出),

24.在第一实施例中,在图1f中,顶部电极140沉积在gst层130的顶部上并且直接接触。在实施例中,使用剥离层116和光致抗蚀剂层117以便覆盖图案化的介电材料层115但是

暴露孔和孔周围的区域到顶部电极140。顶部电极140由第二导电材料构成。提供顶部电极140的第二导电材料可为导电金属或导电金属氮化物。在本技术的一个实施例中,顶部电极140可由氮化钛(tin)、氮化钽(tan)或钨(w)组成。在一些实施例中,第二导电材料是与第一导电材料在组成上相同的导电材料。在一个示例中,底部电极110和顶部电极140两者都由氮化钛(tin)组成。在其他实施例中,第二导电材料是与第一导电材料在组成上不同的导电材料。在一个示例中,底部电极110由氮化钛(tin)组成,并且顶部电极140由氮化钽(tan)组成。顶部电极140可具有从10nm至100nm的厚度;尽管在本技术中设想并可采用顶部电极140的其他厚度。顶部电极140可通过包括例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射的沉积工艺形成。

25.在第一实施例中,在图1g中,在完成ag层120、gst层130和顶部电极140的沉积时,通过化学去除器去除过量的ag层120、gst层130和顶部电极140来溶解剥离层116和光致抗蚀剂层117。

26.现在参见图2a-2e,图2a-2e图示了根据本发明的第二实施例的形成相变存储器的第二方法。在该方法中,分别邻近顶部电极和底部电极沉积两个ag层,在这两个ag层之间沉积掺杂的碲锗锑(gst)层,并且在底部ag层与第一电极之间的顶部电极与底部电极之间沉积图案化的介电材料层。参见图2a-2e,存在描绘存储器结构的示意图(通过截面图),该存储器结构包括底部电极210、图案化的介电层215、ag层220、gst层230、ag层240和顶部电极250。

27.在第二实施例中,图2a描绘了存储器结构的第一层,衬底205具有位于衬底205的顶部上的底部电极210。在第二实施例中,衬底205由导电、非导电或半导体材料(例如,硅)组成。底部电极210由第一导电材料构成。提供底部电极210的第一导电材料可以是导电金属或导电金属氮化物。在本技术的一个实施例中,底部电极210可以由氮化钛(tin)、氮化钽(tan)或钨(w)组成。底部电极210可以具有从10nm至100nm的厚度;尽管底部电极210的其他厚度是预期的并且可以在本技术中采用。底部电极210可以通过包括例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射、化学溶液或电镀的沉积工艺形成。

28.在第二实施例中,图2b描绘了诸如例如二氧化硅或氮化硅的覆盖介电材料层215。毯状介电材料层215可具有10nm至100nm的厚度;尽管在本技术中设想并可采用毯状介电材料层215的其他厚度。毯状介电材料层215可通过沉积工艺形成,沉积工艺包括例如化学气相沉积

29.(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射。

30.在第二实施例中,图2c描绘了图2b的介电材料层215,该介电材料层包括横向尺寸为1微米或更小的孔,该孔现在被称为图案化的介电材料层215,该图案化的介电材料层215允许层被放置在图案化的介电材料层215的顶部上,并且放置在顶部上的该层可以与底部电极210接触。在实施例中,在图案化的介电材料层215中可以存在单个孔。在替代实施例中,在图案化的介电材料层215中可存在一个以上的孔。在又一替代实施例中,任何孔可位于图案化介电材料层215的任何位置。在实施例中,通过光或电子束光刻和/或反应性等离子体蚀刻来形成孔。

31.在第二实施例中,图2d描绘了ag层220,所述ag层220沉积在经图案化的介电材料层215和底部电极210的暴露层的顶部上并且与底部电极直接接触。在实施例中,ag层220具有小于20nm的厚度。在替代实施例中,ag层220具有在5nm和10nm之间的厚度。在实施例中,使用热蒸发在图案化的介电材料层215上沉积ag层220。在实施方式中,使用剥离层216和光致抗蚀剂层217以覆盖图案化的介电材料层215,但是将图案化的介电材料层215中的孔和孔周围的区域暴露于ag层120,但是不允许整个剩余的图案化的介电材料层215覆盖在ag层220中。在实施例中,剥离层216和光致抗蚀剂层217被旋涂和烘烤。在实施例中,通过利用掩模曝光uv光来制成或多个孔,其中光刻图案与图案化介电材料层中的或多个孔对准,并且剥离层216被显影剂底切。

32.在第二实施例中,图2e,gst层230沉积在ag层220的顶部上并且直接接触。在实施例中,gst层230具有小于200nm的厚度。在替代实施例中,gst层230具有20nm与50nm之间的厚度。在实施例中,使用物理溅射并且更具体地射频(rf)溅射将gst层230沉积在ag层220上。在实施例中,使用剥离层216和光致抗蚀剂层217以便覆盖经图案化的介电材料层215,但是将经图案化的介电材料层215中的孔和孔周围的区域暴露于ag层220,但是不允许gst层230中覆盖整个剩余的经图案化的介电材料层215。在实施例中,gst层230覆盖ag层220但不覆盖任何其他层。在实施例中,当沉积gst层230时,gst层230与ag层220混和,从而在各个层的沉积期间并且由于热混合而形成单层(未示出),

33.在第二实施例中,图2f,ag层240沉积在gst层230的顶部上并且直接接触。在实施例中,ag层240具有小于20nm的厚度。在替代实施例中,ag层240具有在5nm和10nm之间的厚度。在实施例中,使用热蒸发在gst层230上沉积ag层240。在实施例中,使用剥离层216和光致抗蚀剂层217以便覆盖图案化的介电材料层115但是暴露gst层230。在实施例中,当沉积ag层240时,ag层240与gst层230混和,从而在各个层的沉积期间并且由于热混合而形成单层(未示出)。

34.在第二实施例中,图2g,在由ag220、gst230和直接在底部电极上的ag240层构成的分层结构的顶部上沉积顶部电极250。在实施例中,使用剥离层216和光致抗蚀剂层217以便覆盖经图案化的介电材料层215。顶部电极250由第二导电材料构成。提供顶部电极250的第二导电材料可以是导电金属或导电金属氮化物。在本技术的一个实施例中,顶部电极250可以由氮化钛(tin)、氮化钽(tan)或钨(w)组成。在一些实施例中,第二导电材料是与第一导电材料在组成上相同的导电材料。在一个示例中,底部电极210和顶部电极250两者由氮化钛(tin)构成。在其他实施例中,第二导电材料是与第一导电材料在组成上不同的导电材料。在一个示例中,底部电极210由氮化钛(tin)组成,并且顶部电极250由氮化钽(tan)组成。顶部电极250可以具有从10nm至100nm的厚度;尽管用于顶部电极250的其他厚度是预期的并且可以在本技术中采用。顶部电极250可通过包括例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射的沉积工艺形成。

35.在第二实施例中,在图2e中,在完成ag层220、gst层230、ag层240和顶部电极250的沉积之后,通过化学去除器去除过量的ag层220、gst层230、ag层240和顶部电极250来溶解剥离层216和光致抗蚀剂层217。

36.现在参见图3a-3g,其示出了根据本发明第三实施例的形成相变存储器的第三方

法。在第三方法中,首先沉积碲锗锑(gst)层,随后沉积ag层和顶部电极层。参见图3a-3f,存在描绘包括底部电极310、图案化电介质层315、gst层320、ag层330和顶部电极340的存储器结构的示意图(通过截面图)。

37.在第三实施例中,图3a描绘了存储器结构的第一层,衬底305具有位于衬底305顶部上的底部电极310。在第一实施例中,衬底305由导电、非导电或半导体材料(例如,硅)组成。底部电极310由第一导电材料构成。提供底部电极310的第一导电材料可以是导电金属或导电金属氮化物。在本技术的一个实施例中,底部电极310可以由氮化钛(tin)、氮化钽(tan)或钨(w)组成。底部电极310可具有从10nm到100nm的厚度;尽管底部电极310的其他厚度是预期的并且在本技术中可被采用。底部电极110可以通过包括例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射、化学溶液或电镀的沉积工艺形成。

38.在第三实施例中,图3b描绘了毯状介电材料层315,例如二氧化硅或氮化硅。毯状介电材料层315可具有10nm至100nm的厚度;尽管在本技术中设想并可采用毯状介电材料层315的其他厚度。毯状介电材料层315可通过沉积工艺形成,沉积工艺包括例如化学气相沉积

39.(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射。

40.在第三实施例中,图3c描绘了图3b的介电材料层315,该介电材料层包括横向尺寸为1微米或更小的孔,该孔现在被称为图案化的介电材料层315,该图案化的介电材料层315允许层被放置在图案化的介电材料层315的顶部上,并且放置在顶部上的该层可以与底部电极310接触。在实施例中,在图案化的介电材料层315中可以存在单个孔。在替代实施例中,在图案化介电材料层315中可存在一个以上孔。在又一替代实施例中,任何孔可位于图案化介电材料层315的任何位置。在实施例中,通过光或电子束光刻和反应等离子体蚀刻或离子束溅射来产生孔。

41.在第三实施例(图3d)中,gst层330沉积在图案化介电材料层315的顶部及底部电极310的暴露层上,且gst层330直接接触。在实施例中,gst层330具有小于200nm的厚度。在替代实施例中,gst层330具有20nm与50nm之间的厚度。在实施例中,使用物理溅射并且更具体地射频(rf)溅射将gst层330沉积在图案化的介电材料层315和底部电极310的暴露层上。在实施例中,使用剥离层316和光致抗蚀剂层317以便覆盖图案化的介电材料层315,但是将图案化的介电材料层315中的孔和孔周围的区域暴露于gst层330,但是不允许整个剩余的图案化的介电材料层315被覆盖在gst层330中。在实施例中,将剥离层316和光致抗蚀剂层317旋涂并烘烤。在实施例中,通过利用掩模曝光uv光来制成或多个孔,其中光刻图案与图案化介电材料层中的或多个孔对准,并且剥离层316被显影剂底切。

42.在第三实施例(图3e)中,ag层320沉积在gst层330上并且直接接触。在实施例中,ag层320具有小于20nm的厚度。在替代实施例中,ag层320具有在5nm和10nm之间的厚度。在实施例中,使用热蒸发在gst层330上沉积ag层320。在实施方式中,使用剥离层316和光致抗蚀剂层317以覆盖图案化的介电材料层315,但是将图案化的介电材料层315中的孔和孔周围的区域暴露于gst层330,但是不允许整个剩余的图案化的介电材料层315覆盖在ag层320中。在实施例中,ag层320覆盖gst层330但不覆盖任何其他层。在实施例中,当沉积gst层330

时,gst层130与ag层320混和,从而在各个层的沉积期间并且由于热混合而形成单层(未示出),

43.在第三实施例(图3f)中,顶部电极340直接沉积在ag层320的顶部上。在实施例中,使用剥离层316和光致抗蚀剂层317以覆盖图案化的介电材料层315,但暴露孔和孔周围的区域至顶部电极340。顶部电极340由第二导电材料构成。提供顶部电极340的第二导电材料可以是导电金属或导电金属氮化物。在本技术的一个实施例中,顶部电极340可以由氮化钛(tin)、氮化钽(tan)或钨(w)组成。在一些实施例中,第二导电材料是与第一导电材料在组成上相同的导电材料。在一个实例中,底部电极310和顶部电极340两者由氮化钛(tin)组成。在其他实施例中,第二导电材料是与第一导电材料在组成上不同的导电材料。在一个实例中,底部电极310由氮化钛(tin)组成,并且顶部电极340由氮化钽(tan)组成。顶部电极340可具有从10nm到100nm的厚度;尽管用于顶部电极340的其他厚度被考虑并且在本技术中可被采用。顶部电极340可通过包括例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射的沉积工艺形成。

44.在第三实施例中,在图3g中,在完成gst层330、ag层320和顶部电极340的沉积时,通过化学去除器去除过量的gst层330、ag层320和顶部电极340来溶解剥离层316和光致抗蚀剂层317。

45.现在参考图4a至图4f,其示出了根据本发明的第四实施例的形成相变存储器的第四方法。在该方法中,ag掺杂的碲锗锑(gst)层沉积在顶部电极与底部电极之间。参见图4a-4e,存在描绘包括底部电极410、图案化电介质层415、ag掺杂gst层420和顶部电极440的存储器结构的示意图(通过截面图)。

46.尽管这里没有实践,但是本发明设想第四实施例,其中将ag掺杂的gst用作pcm材料以解决复位电阻漂移,而不是上述的ag和gst的多层结构。图4a示出存储器结构的第一层,衬底405具有位于衬底405顶部上的底部电极410。在第四实施方式中,衬底405由导电、非导电或者半导体材料(例如,硅)构成。底部电极410由第一导电材料构成。提供底部电极410的第一导电材料可以是导电金属或导电金属氮化物。在本技术的一个实施例中,底部电极410可以由氮化钛(tin)、氮化钽(tan)或钨(w)组成。底部电极410可以具有从10nm至100nm的厚度;尽管底部电极410的其他厚度是预期的并且可以在本技术中采用。底部电极410可以通过包括例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射、化学溶液或电镀的沉积工艺形成。

47.在第四实施例中,图4b示出毯状介电材料层415,例如二氧化硅或氮化硅。毯状介电材料层415可具有10nm至100nm的厚度;尽管毯状介电材料层415的其他厚度被设想且可在本技术中采用。毯状介电材料层415可通过沉积工艺形成,沉积工艺包括例如化学气相沉积

48.(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射。

49.在第四实施例中,图4c描绘了图4b的介电材料层415,该介电材料层415包括横向尺寸为1微米或更小的孔,该孔现在被称为图案化介电材料层415,该图案化介电材料层415允许层放置在图案化介电材料层415的顶部上,并且放置在顶部上的该层可以与底部电极410接触。在实施例中,在图案化的介电材料层415中可以存在单个孔。在替代实施例中,在

图案化介电材料层415中可存在一个以上孔。在又一替代实施例中,任何孔可位于图案化介电材料层415中的任何位置。在实施例中,通过光或电子束光刻和/或反应性等离子体蚀刻来形成孔。

50.在第四实施例(图4d)中,ag掺杂gst合金层420沉积于底部电极410的顶部上且直接接触。在实施例中,ag掺杂gst层420具有小于200nm的厚度。ag掺杂gst合金层420由包含(ag)作为杂质(即,掺杂剂)元素的gst合金构成。杂质以足以引起pcm单元的复位状态电阻漂移减小的量存在于gst合金中。在本技术的一个实施例中,ag掺杂gst合金层420具有从5原子百分比到15原子百分比的掺杂剂浓度。在本技术的另一实施例中,ag掺杂gst合金层420具有10原子百分比至45原子百分比的掺杂浓度。gst合金中5原子百分比至45原子百分比的ag掺杂剂浓度导致pcm单元的复位状态电阻漂移的减少。

51.在一些实施例中,ag掺杂gst合金层420具有从ag掺杂gst合金层420的一个表面到ag掺杂gst合金层420的相对表面的均匀掺杂剂浓度。在其他实施例中,ag掺杂gst合金层420具有渐变的掺杂剂浓度。在一些实施例中,渐变的掺杂剂浓度从在底部电极410与ag掺杂gst合金层420之间形成的界面以及从在顶部电极440与ag掺杂gst合金层420之间形成的界面两者向内减小。

52.在一个实施例中,可以通过首先形成非ag掺杂gst合金层来形成ag掺杂gst合金层420。可利用例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积

53.(ald)或物理气相沉积(pvd)的沉积工艺形成非ag掺杂gst合金层。接下来,可利用来自牺牲材料层的离子注入、气相掺杂或掺杂剂扩散将ag离子引入到非ag掺杂的gst合金层中。

54.在另一实施例中,可利用沉积工艺形成ag掺杂gst合金层420,其中在沉积工艺本身期间引入ag离子或原子。

55.在又一实施例中,可以通过首先沉积ag的第一层,然后沉积非ag掺杂gst合金层,然后沉积ag的第二层来形成ag掺杂gst合金层420。在各个层的沉积期间并且由于热混合,形成ag掺杂的gst合金层;没有留下单独的ag层,如上所示和讨论的。在一些实施方式中,可以省去ag的第一层。在其他实施例中,可以省略ag的第二层。可以利用包括例如化学气相沉积

56.(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积

57.(pvd)、溅射、化学溶液沉积或电镀的沉积工艺来形成第一ag层和/或第二ag层。可利用例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)或物理气相沉积(pvd)的沉积工艺形成非ag掺杂gst合金层。在一个实施例中并且当采用第一和第二ag层时,第一层ag和第二层ag的厚度可以是从3nm至15nm,而非ag掺杂的gst合金层的厚度可以是从20nm至150nm。

58.在第四实施例(图4d)中,ag掺杂gst层420沉积在经图案化的介电材料层415的顶部及底部电极410的暴露层上,且ag掺杂gst层420直接接触。在实施例中,ag掺杂gst层420具有小于200nm的厚度。在替代实施例中,gst层420具有20nm与50nm之间的厚度。在实施例中,使用剥离层416和光致抗蚀剂层417以便覆盖图案化的介电材料层415,但是将图案化的介电材料层415中的孔和孔周围的区域暴露于ag掺杂的gst合金层420,但是不允许整个剩余的图案化的介电材料层415覆盖在ag掺杂的gst合金层420中。在实施例中,剥离层416和

光致抗蚀剂层417被旋涂并烘烤。在实施例中,通过利用掩模曝光uv光来制成或多个孔,其中光刻图案与图案化电介质材料中的或多个孔对准,并且剥离层416被显影剂底切。

59.在第四实施例中,图4e,在掺杂ag的gst合金层420的顶部上沉积顶部电极440。在实施例中,使用剥离层416和光致抗蚀剂层417,以便覆盖图案化的介电材料层415,但是暴露孔和孔周围的区域到顶部电极440。顶部电极440由第二导电材料构成。提供顶部电极440的第二导电材料可以是导电金属或导电金属氮化物。在本技术的一个实施例中,顶部电极440可以由氮化钛(tin)、氮化钽(tan)或钨(w)组成。在一些实施例中,第二导电材料是与第一导电材料在组成上相同的导电材料。在一个示例中,底部电极410和顶部电极440两者由氮化钛(tin)组成。在其他实施例中,第二导电材料是与第一导电材料在组成上不同的导电材料。在一个实例中,底部电极410由氮化钛(tin)组成,并且顶部电极440由氮化钽(tan)组成。顶部电极440可以具有从10nm至100nm的厚度;尽管用于顶部电极440的其他厚度是预期的并且可以在本技术中采用。顶部电极440可以通过包括例如化学气相沉积(cvd)、等离子体增强化学气相沉积(pecvd)、原子层沉积(ald)、物理气相沉积(pvd)或溅射的沉积工艺形成。

60.在第四实施例中,在图4f中,在完成ag掺杂gst合金层420和顶部电极440的沉积时,通过化学去除器去除过量的ag掺杂gst合金层420和顶部电极440来溶解剥离层416和光致抗蚀剂层417。

61.在以上描述的四个实施例中的任何实施例中,pcm结构可以形成为pcm材料堆叠阵列,pcm材料堆叠阵列位于形成最终结构的第一和第二导电含金属结构之间。在此,该第一导电含金属结构可以位于一个衬底上,该衬底可以包括一个前端线(feol)层级,该前端线层级包含位于一个半导体衬底上或其中的一个或多个半导体器件。或者,衬底可以包括位于feol层上的后段制程(beol)层。beol层包括一个或多个互连级,该一个或多个互连级包含具有嵌入在其中的一个或多个导电结构的互连介电材料。

62.在一些实施例中,最终结构还可以包括位于每个第一导电含金属结构和每个pcm堆叠之间的含选择器层。每个包含选择器的层包括例如二极管或阈值开关器件。或者,也可以从结构中省略含有选择器的层。最终结构可以利用本领域技术人员公知的处理技术来形成,除了pcm材料结构之外,pcm材料结构如上所述在四个实施例中使用ag、gst和/或ag掺杂的gst作为pcm材料来形成。尽管未示出,但最终结构可嵌入在形成于衬底上的一个或多个互连介电材料层中。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。