pll电路及其控制方法

技术领域

1.本公开涉及一种pll(phase locked loop:锁相环)电路。

背景技术:

2.对于各种ic(integrated circuit:集成电路),利用了频率合成器,该频率合成器根据基准时钟来生成任意频率的时钟。作为这样的频率合成器,广泛使用pll电路。图1的(a)~图1的(c)是对pll电路的基本架构进行说明的框图。

3.在图1的(a)中,示出了模拟pll电路1。模拟pll电路1包括相位比较器(pfd:phase frequency detector;相位频率检测器)10、电荷泵电路12、低通滤波器14、电压控制振荡器(vco:voltage controlled oscillator)16、以及分频器18。vco16以与模拟的控制电压v

ctrl

相应的频率来振荡。vco16的输出时钟clk_vco由分频器18进行1/n分频。相位比较器10对分频后的时钟clk_div与基准时钟clk_ref的相位差进行检测,对电荷泵电路12进行控制。低通滤波器14为使电荷泵电路12的输出电压平滑化的环路滤波器,生成控制电压v

ctrl

。

4.图1的(a)的模拟pll电路1长久以来在各种应用中被使用,可靠性较高,但会存在如下这样的问题:芯片尺寸因环路滤波器而变大。此外,为了发挥足够的性能,电路设计者需要优化电路的布局。

5.在图1的(b)中,示出了全数字pll电路(adpll:all digital pll)2。adpll电路2接收fcw(frequency control word:频率控制字)及基准时钟clk_ref,并生成输出时钟clk_dco,该输出时钟clk_dco为根据fcw对基准时钟clk_ref进行倍增而得到。adpll电路2包括频率相位比较器20、数字滤波器22、以及数字控制振荡器(dco:digital controlled oscillator)24。dco24以与被输入的控制代码d

ctrl

相应的频率来振荡。频率相位比较器20具有相当于图1的相位比较器10、电荷泵电路12及分频器18的功能,由tdc(时间-数字转换器)、加法器及计数器等构成。频率相位比较器20所生成的数字信号由数字滤波器22进行滤波,并被输入到dco24。

6.图1的(b)的adpll电路2能够以cmos工艺来构成,因此会存在微细化容易,且能够使芯片面积变小这样的优点。另一方面,即使为全数字,针对频率相位比较器20及dco24,为了满足所期望的规格,电路设计者也需要优化电路的布局。

7.在图1的(c)中,示出了注入同步型pll电路3(也称il-pll(injection locked pll:注入锁定pll))。il-pll电路3能够以模拟电路或数字电路的架构来设计,但在此,仅说明以数字电路来构成的情况。il-pll电路3包括反馈电路30、dco32、以及边沿注入电路34。il-pll电路3被理解为反馈控制与前馈控制的混合,通过相当于图1的(b)的频率相位比较器20、数字滤波器22的反馈电路30的反馈控制来使dco32的振荡频率稳定化。边沿注入电路34切出基准时钟clk_ref的边沿,并将切出的边沿注入到dco32,对输出时钟clk_dco的相位进行重新对准。根据边沿的注入方法,il-pll电路有时也会被称为mdll(multiplying delay locked loop:倍数延迟锁相环)电路。

8.il-pll电路具有如下这样的优点:(i)因为环路带宽因注入同步而被宽带化,所

circuits and systems conference(newcas),paris,2013,pp.1-4

22.非专利文献10:k.j.shen et al.,"a 0.17-to-3.5mw 0.15-to-5ghz soc pll with 15db built-in supply noise rejection and self-bandwidth control in 14nm cmos",2016 ieee international solid-state circuits conference(isscc),san francisco,ca,2016,pp.330-331

23.非专利文献11:f.ahmad et al."a 0.5-9.5-ghz,1.2-us lock-time fractional-n dpll with

±

1.25%ui period jitter in 16-nm cmos for dynamic frequency and core-count scaling",ieee journal of solid-state circuits,vol.52,no.1,pp.21-32,jan.2017

技术实现要素:

24.[发明要解决的课题]

[0025]

图1的(a)、图1的(b)的pll电路具有环路滤波器,因此会存在从起动开始到相位同步的时间(称为起动时间)较长这样的问题。为了缩短起动时间,提出了各种技术。

[0026]

以往的高速起动技术中,主流的是根据频率引入状态来动态地控制环路滤波器的特性(例如非专利文献2、5、8、9、10、11),但因为利用了反馈控制,所以在频率引入之前,依然存在无法忽视的延迟。此外,会存在如下这样的问题:到相位同步为止的时间根据此时的条件而变动。

[0027]

在非专利文献1、3、4、6、7中,在刚起动后,当通过前馈来使针对可变频率振荡器的控制信号变化,并进行锁定判定时,切换到反馈控制。在该方式中,能够缩短频率引入的时间,但在频率引入完成后,反馈控制会被进行到相位同步为止,因此会存在延迟,且相位同步所需的时间会根据此时的条件而变动。

[0028]

本公开鉴于上述问题而完成,其一个方案的例示性目的之一在于提供一种能够以预定时间高速地起动的注入同步型pll电路。

[0029]

[用于解决技术课题的技术方案]

[0030]

本公开的一个方案涉及一种注入同步型的pll(phase locked loop)电路。pll电路包括:数字控制振荡器,其被构成为能够在选择信号被置于有效的期间,形成环形振荡器,并以与控制代码相应的频率来振荡,在选择信号被置于无效的期间,注入基于基准时钟的注入沿;以及控制器,其对数字控制振荡器进行控制。控制器(a)在pll电路的起动期间成为第1模式,重复进行包含以下步骤的循环:(i)使选择信号有效,使数字控制振荡器振荡,并进行数字控制振荡器所产生的振荡器时钟与基准时钟的相位比较的步骤;以及(ii)使选择信号无效并停止数字控制振荡器,通过基于相位比较的结果的二分法查找来更新控制代码的步骤。

[0031]

本公开的另一方案涉及一种pll电路的控制方法。pll电路包含数字控制振荡器,该数字控制振荡器被构成为:能够在选择信号被置于有效的期间,形成环形振荡器,并以与控制代码相应的频率来振荡,在选择信号被置于无效的期间,注入基于基准时钟的注入沿。控制方法包括:在pll电路的第1次起动时,重复包含(i)使数字控制振荡器振荡,并进行数字控制振荡器所产生的振荡器时钟与基准时钟的相位比较的步骤、以及(ii)停止数字控制振荡器,并通过基于相位比较的结果的二分法查找来更新控制代码的步骤的循环的步骤;

以及在二分法查找完成后,使数字控制振荡器连续动作,并使控制代码变化,使得振荡器时钟的相位接近基准时钟的相位的步骤。

[0032]

另外,将以上构成要素任意地组合后得到的结果,或将本公开的表达方式在方法、装置等之间转换后的结果,作为本发明的方案也是有效的。

[0033]

发明效果

[0034]

根据本公开的一个方案,能够以预定时间高速起动pll电路。

附图说明

[0035]

图1的(a)~图1的(c)是对pll电路的基本架构进行说明的框图。

[0036]

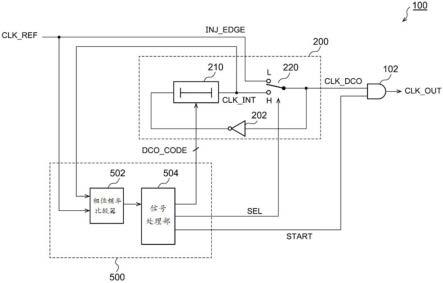

图2是表示实施方式的pll电路的基本构成的框图。

[0037]

图3是图2的pll电路的动作波形图。

[0038]

图4是对基于二分法查找的控制代码的转变进行说明的图。

[0039]

图5是表示pll电路的构成例的图。

[0040]

图6是图5的pll电路的动作波形图。

[0041]

图7是表示基于二分法查找的频率的转变的图。

[0042]

图8是对pll电路的第2次以后的起动进行说明的时序图。

[0043]

图9是表示图5的窗口产生器的构成例的电路图。

[0044]

图10是图9的pll电路的动作波形图。

[0045]

图11是图9的pll电路的动作波形图。

[0046]

图12是表示pll电路的具体的构成例的电路图。

具体实施方式

[0047]

(实施方式的概要)

[0048]

以下,对本公开的几个例示性的实施方式的概要进行说明。该概要作为后述的详细说明的前置,以实施方式的基本理解为目的,将一个或多个实施方式中的几个概念简化并对其进行说明,并不会限定发明或公开的广度。此外,该概要并非可考虑的全部实施方式的概括性的概要,并不对实施方式的不可或缺的构成要素进行限定。方便起见,“一个实施方式”有时用于指代本说明书所公开的一个实施方式(实施例或变形例)或多个实施方式(实施例或变形例)。

[0049]

本说明书所公开的一个实施方式涉及一种pll(phase locked loop:锁相环)电路。pll电路包括:数字控制振荡器;以及控制器,其对数字控制振荡器进行控制。数字控制振荡器被构成为:能够在选择信号被置于有效的期间,形成环形振荡器,并以与控制代码相应的频率来振荡,在选择信号被置于无效的期间,注入基于基准时钟的注入沿。控制器重复进行包含以下步骤的循环:(a)在pll电路的起动期间成为第1模式,(i)使选择信号有效并使数字控制振荡器振荡,进行数字控制振荡器所产生的振荡器时钟与基准时钟的相位比较的步骤;以及(ii)使选择信号无效并停止数字控制振荡器,通过基于相位比较的结果的二分法查找来更新控制代码的步骤。

[0050]

在数字控制振荡器的控制代码为m位时,在从起动开始起m个循环后,控制代码成为最优值,频率引入完成。然后,因为是注入同步型,所以在下一循环中,能够以与注入沿相

位同步的状态来开始振荡。即,基于反馈的相位同步的延迟时间为零,此外,起动时间为m个循环的时间,是不变的。

[0051]

也可以是,在一个实施方式中,控制器在第1模式下,在基准时钟的每个周期,对选择信号的有效与无效进行切换。在该情况下,1个循环为基准时钟的2个周期,起动时间为2

×m×

t

ref

。

[0052]

也可以是,在一个实施方式中,控制器响应pll电路的停止指示,保持此时的控制代码,并在下一个pll电路的起动指示时,以保持的控制代码为初始值,立即开始控制代码的反馈控制。由此,能够从取入了使能信号的基准时钟的第1个循环起,以相位同步的状态来重启。即,在具备该pll电路的系统中,能够积极地对pll电路的动作、停止进行切换,并能够大幅地削减耗电。

[0053]

也可以是,在一个实施方式中,控制器在(b)二分法查找完成后成为第2模式,使数字控制振荡器连续动作,并使控制代码变化,使得振荡器时钟的相位接近基准时钟的相位,并且周期性地使选择信号无效。

[0054]

也可以是,在一个实施方式中,控制器还包括窗口产生器,该窗口产生器接收数字控制振荡器的内部时钟,将1个脉冲切出并生成窗口信号。也可以是,在通常动作期间中,选择信号与窗口信号对应。窗口信号所规定的窗打开(有效)的定时、窗关闭的(无效)定时不取决于基准时钟。因此,在数字控制振荡器振荡的期间,无论有无基准时钟,都能够可靠地使窗开闭。此外,能够进行定时调整,使得在窗打开的期间中,可靠地包含基准时钟的注入沿,因此不会产生来源于窗口信号的毛刺(glitch)或谐波振荡。若在窗打开的期间不发生基准时钟的转变(产生边沿)的情况下,则内部时钟的周期会以每预定循环(倍增数)1次的比例变长,但振荡不会停止。

[0055]

也可以是,在一个实施方式中,窗口产生器在内部时钟的每n个循环(n≥2)生成1次在内部时钟的半个循环期间被置于有效的脉冲信号,并使脉冲信号延迟内部时钟的周期的k倍时间(0<k<1),从而生成窗口信号。由此,能够对窗口信号的定时进行调节,使得在窗口信号的有效期间中存在注入沿。

[0056]

也可以是,在一个实施方式中,设k=1/4。由此,能够对窗口信号的定时进行调节,使得在窗口信号的有效期间的实质上中央存在注入沿。另外,k不需要严格为1/4。

[0057]

也可以是,在一个实施方式中,窗口产生器包括:计数器,其对内部时钟进行计数,并每n个循环在内部时钟的1个周期间,使输出有效;逻辑门,其对计数器的输出与内部时钟进行逻辑合成,生成脉冲信号;以及延迟线,其使脉冲信号延迟内部时钟的周期的1/4的延迟量。

[0058]

也可以是,在一个实施方式中,数字控制振荡器包含可变延迟电路。也可以是,延迟线为与可变延迟电路相同电路形式的复制。

[0059]

也可以是,在一个实施方式中,延迟线赋予可变延迟电路的1/2倍的延迟。在环形振荡器中,可变延迟电路的延迟量相当于内部时钟的实质上半个周期。因此,可变延迟电路的1/2倍的延迟为内部时钟的1/4周期。

[0060]

也可以是,在一个实施方式中,数字控制振荡器包含:可变延迟电路;以及复用器,其在一个输入接收可变延迟电路的输出即内部时钟,在另一个输入接收注入沿,且其输出与可变延迟电路的输入连接,并选择与窗口信号相应的一者。

[0061]

也可以是,在一个实施方式中,窗口产生器包含窗口信号所通过的复用器的复制。由此,能够降低因复用器导致的定时偏差的影响。

[0062]

也可以是,在一个实施方式中,复用器包含:第1nand门,其在第1输入接收内部时钟,在第2输入接收窗口信号;第2nand门,其在第1输入接收基准时钟,在第2输入接收被反相的窗口信号;第3nand门,其在第1输入接收第1nand门的输出,在第2输入接收第2nand门的输出;以及第4nand门,其在第1输入接收第1nand门的输出,在第2输入接收第2nand门的输出,且输出与第3nand门的输出连接。一般的复用器包含初级的2个nand门的“对”、以及后级的1个nand门。nand门存在来源于其构成的非对称性的2个输入信号的延迟差,因此在一般的复用器中,在输出级的nand门中,复用器的2个输入信号会产生延迟差。因此,能够通过成“对”地配置2个该输出级的nad门,并交换各自的输入地进行连接,从而抵消2个输入信号的延迟差。

[0063]

也可以是,在一个实施方式中,可变延迟电路包含:第1延迟电路,其赋予较粗的延迟控制量;以及第2延迟电路,其赋予足够短的延迟控制量,该延迟控制量以满刻度(full scale)来满足相当于第1延迟电路的控制量1lsb的延迟量。也可以是,延迟线包含第1延迟电路的复制,并赋予第2控制代码,该第2控制代码具有赋予到第1延迟电路的第1控制代码的1/2的值。在该情况下,可变延迟电路的延迟量中,基于第1延迟电路的延迟为主导,因此能够通过使用该部分的复制来生成内部时钟的1/4周期的延迟。

[0064]

也可以是,在一个实施方式中,作为注入沿,直接注入基准时钟。由此,基准时钟不会通过延迟电路或逻辑门,因此能够降低电源噪声给注入沿带来的相位噪声。

[0065]

也可以是,在一个实施方式中,反馈电路包含:对称型相位检测器,其在窗口信号被置于有效的期间,成为使能状态,并将数字控制振荡器所生成的时钟信号与基准时钟的相位进行比较,生成表示比较结果的升降信号;以及数字滤波器,其生成与升降信号相应的控制代码。通过使对称型相位检测器在窗口信号被置于有效的期间成为使能,从而能够将相位引入范围扩大到基准时钟的1个周期的范围。

[0066]

也可以是,在一个实施方式中,反馈电路包含:相位频率检测器,其在窗口信号被置于有效的期间,成为使能状态,并将数字控制振荡器所生成的时钟信号与基准时钟的相位及频率进行比较,生成表示比较结果的上升脉冲及下降脉冲;以及数字滤波器,其生成与基于上升脉冲及下降脉冲的升降信号相应的控制代码。通过采用原本具有较大相位引入范围,并具有频率引入功能的相位频率检测器,进而使相位频率检测器在使能窗口信号被置于有效的期间成为使能,从而能够实质上无限地扩大相位引入范围。

[0067]

尽管窗口打开,但当不产生注入沿时,数字控制振荡器的频率每基准时钟的周期会短期地变动。因此,也可以是,窗口产生器在无法检测到基准时钟的边沿时,维持窗口信号的无效。由此,即使在基准时钟停止时,也能够继续基于pll电路的时钟生成。此外,数字控制振荡器的频率仅会在基准时钟刚缺失之后发生变动,而之后能够保持一定。

[0068]

也可以是,在一个实施方式中,pll电路还包括时钟监视电路,该时钟监视电路生成在基准时钟被正常输入时被置于有效、在基准时钟停止时被置于无效的时钟使能信号。也可以是,根据时钟使能信号来对计数器的输出进行屏蔽。

[0069]

(实施方式)

[0070]

以下,参照附图,针对实施方式进行说明。对于各附图所示的相同或等同的构成要

素、构件、以及处理,标注相同的附图标记,并适当省略重复的说明。此外,实施方式并不对发明进行限定,仅为例示,实施方式所记述的一切特征或其组合并非都是发明的实质性内容。

[0071]

在本说明书中,所谓“构件a与构件b连接的状态”,除包含构件a与构件b物理性地直接连接的情况之外,还包含构件a与构件b经由不对其电连接状态产生实质影响,或者不会损害其结合所起到的功能或效果的其它构件间接地连接的情况。

[0072]

同样,所谓“构件c被设置在构件a与构件b之间的状态”,除包含构件a与构件c、或者构件b与构件c直接连接的情况之外,还包含经由不对其电连接状态产生实质影响,或者不会损害通过其结合而起到的功能或效果的其它构件间接地连接的情况。

[0073]

图2是表示实施方式的pll电路100的基本构成的框图。pll电路100为注入同步型,包括数字控制振荡器(dco:digital controlled oscillator)200、控制器500及输出门102。

[0074]

dco200被构成为:在选择信号sel被置于有效(例如高=1)期间,形成环形振荡器,并以与m位的控制代码dco_code[m-1:0]相应的频率来振荡,在选择信号sel被置于无效(例如低=0)期间,能够注入基于基准时钟clk_ref的注入沿。

[0075]

dco200主要包含逆变器202、可变延迟电路210、以及复用器(选择器)220。复用器220接收基于可变延迟电路210的输出信号(内部时钟)clk_int、基准时钟clk_ref的注入沿inj_edge,并选择与控制信号sel相应的一者。复用器220的输出clk_dco被逆变器202反相,并被反馈到可变延迟电路210的输入。另外,该逆变器202的插入位置不被限定,既可以设置在可变延迟电路的输入侧,也可以设置在输出侧,还可以组装到可变延迟电路或复用器中。

[0076]

在该构成中,基准时钟clk_ref被作为注入沿inj_edge而直接注入。由此,基准时钟clk_ref不会通过延迟电路或逻辑门,因此能够降低来自该路径的电源噪声给注入沿带来的相位噪声。

[0077]

控制器500对dco200进行控制。具体而言,生成针对可变延迟电路210的控制代码dco_code、针对复用器220的选择信号sel、以及针对输出门102的开始信号start。

[0078]

控制器50能够在第1模式与第2模式间进行切换,并在ic的电源接通时,在pll电路100的起动期间成为第1模式在起动完成后成为第2模式在此,也将第1模式称为二分法查找模式。

[0079]

在第1模式下,控制器500重复执行包含2个处理(i)、(ii)的循环。

[0080]

第1处理:使选择信号sel有效,并使dco200振荡,进行dco200所产生的振荡器时钟即内部时钟clk_int(或输出时钟clk_dco)与基准时钟clk_ref的相位比较。

[0081]

第2处理:使选择信号sel无效并停止dco200,通过基于步骤(i)相位比较的结果的二分法查找来对控制代码dco_code进行更新。

[0082]

例如,也可以是,控制器500在第1模式下,在基准时钟clk_ref的每个周期,对选择信号sel的有效与无效进行切换。即,在第1模式下,每基准时钟clk_ref的周期,dco200交替地重复振荡与停止,其振荡频率被更新。

[0083]

在第2模式下,控制器500使dco200连续动作,并使控制代码dco_code变化,使得振荡器时钟clk_int的相位及频率与基准时钟clk_ref的相位及频率接近。此外,控制器500周期性地使选择信号sel无效,将基于基准时钟clk_ref的注入沿注入到dco200,并施加相

位同步。

[0084]

控制器500在第1模式下将开始信号start置于无效(低),在第2模式下将start信号置于有效(高)。输出门102接收dco200所产生的时钟clk_dco和start信号,在start信号被置于无效的期间,即,pll电路100的起动期间中,阻断时钟clk_dco,在start信号被置于有效的期间,即,pll电路100的起动完成后,使时钟clk_dco通过,并将输出时钟clk_out输出。

[0085]

与第1模式相关联地,控制器500包括相位频率比较器(相位频率检测器)502及信号处理部504。相位频率比较器502对基准时钟clk_ref与dco200的内部时钟clk_int的频率及相位进行比较。另外,相位频率比较器502也可以由相位比较器(相位检测器)与频率比较器(频率检测器)的组合来构成。信号处理部504在第1模式下,基于相位频率比较器502的输出,通过二分法查找来使控制代码dco_code变化。此外,信号处理部504在第2模式下,对相位频率比较器502的输出进行积分(使其平滑化),生成控制代码dco_code。与第2模式相关联的信号处理部504的构成可以采用公知技术,典型地,包含数字滤波器。此外,也可以是,信号处理部504包含状态机,该状态机用于对第1模式和第2模式进行控制。

[0086]

以上是pll电路100的构成。接着,是对其动作进行说明的图。图3是图2的pll电路100的动作波形图。在时刻t0,pll电路100起动,成为第1模式

[0087]

在第1模式期间,以进行第1处理的第1期间t1和进行第2处理的第2期间t2为1个循环,对其重复执行,并基于二分法查找来对针对dco200的控制代码dco_code[m-1:0]进行更新。然后,在m个循环的重复后,即,在经过基准时钟clk_ref的(2

×

m)个周期后的时刻t1,以查找到的最优的控制代码dco_code来转换到第2模式在第2模式下,start信号被置于有效,输出时钟clk_out被供给到pll电路100的外部的块,控制代码dco_code被相位同步环优化,输出时钟clk_out的频率被稳定化在基准时钟clk_ref的n倍。

[0088]

图4是对基于二分法查找的控制代码的转变进行说明的图。在此,为控制代码dco_code的位数m为4的情况,目标代码表示[1011](在10进制下为11的情况)。

[0089]

以上是pll电路100的动作。根据该pll电路100,在dco200的控制代码dco_code为m位时,在从起动开始起m个循环后,控制代码dco_code会成为最优的值,频率引入会完成。并且,因为是注入同步型,所以在下个循环中,能够以与注入沿相位同步的状态来开始振荡。即,基于反馈的相位同步的延迟时间为零,能够进行高速起动。此外,起动时间为m个循环的时间,是不变的。

[0090]

图5是表示pll电路100的构成例(100a)的图。控制器500中的、除相位频率比较器502外的部分对应于图2的信号处理部504。控制器500接收指示pll电路100的起动、停止的使能信号en,并以使能信号en的有效(高)为触发而成为第1模式开始起动。

[0091]

触发器530及逆变器532在基准时钟clk_ref的边沿(在该例中,为负边沿)对使能信号en进行重定时(retiming),并生成enreg信号。

[0092]

and门534在energ信号为“高”的期间,将基准时钟clk_ref作为动作时钟来供给到二分法查找部512及环路滤波器514。

[0093]

窗口产生器400在enreg信号有效(高)时成为激活。窗口产生器400通过接收dco200的内部时钟clk_int,按每n个中切出1个的比例来切出脉冲,并使其延迟内部时钟

clk_int的1/4周期,从而生成窗口信号inj_windb。n为pll电路100的倍增比。窗口信号inj_windb在第2模式下由选择器522来选择,并作为选择信号sel被供给到复用器220。

[0094]

此外,窗口信号inj_windb被供给到相位频率比较器502。相位频率比较器502在窗口信号inj_windb所指定的定时(期间),对2个时钟信号clk_ref与clk_int的相位进行比较,并输出表示比较结果的信号up_down。

[0095]

二分法查找部512在pll电路100刚起动后的第1模式下成为激活,并基于相位频率比较器502的输出up_down,通过二分法查找来使控制代码dco_code变化。二分法查找部512在第1模式期间,将查找使能信号saren置于有效(高),当二分法查找完成时,将saren信号置于无效(低),并转换到第2模式

[0096]

在第1模式期间,二分法查找部512所生成的代码code_bs介由选择器516,作为控制代码dco_code而被供给到可变延迟电路210。此外,当第1模式结束时,代码code_bs被设定为环路滤波器514的初始值。

[0097]

此外,二分法查找部512在基准时钟clk_ref的每1个周期,生成电平反相的选择信号sel_bs。在第1模式期间,sel_bs信号由选择器522来选择,并作为选择信号sel而被供给到复用器220。

[0098]

环路滤波器514在第2模式下成为激活,并基于相位频率比较器502的输出up_down来生成控制代码code_fb。在第2模式期间,环路滤波器514所生成的代码code_fb介由选择器516,作为控制代码dco_code而被供给到可变延迟电路210。

[0099]

saren信号由逆变器518进行反相,作为start信号而被供给到输出门102。

[0100]

以上是pll电路100a的构成。接着,对其动作进行说明。图6是图5的pll电路100a的动作波形图。在此,控制代码dco_code的位数为m=4。图7是表示基于二分法查找的频率的转变的图。

[0101]

接着,参照图6。在时刻t0,使能信号en成为“高”,在时刻t1,使能信号en响应于基准时钟clk_ref的负边沿而被取入,enreg信号成为“高”,并成为第1模式sel_bs信号在基准时钟clk_ref的每个周期反相,成为sel信号。

[0102]

每当时刻t2、t4、t6、t8和sel信号成为“高”时,基准时钟clk_ref的正边沿会被注入到dco200,dco200会振荡。此外,当时刻t3、t5、t7、t9和sel信号成为低时,会进行相位比较。作为相位比较的结果,在up_down信号为“高”时,控制代码dco_code(code_bs)会増加,在up_down信号为“低”时,控制代码dco_code(code_bs)会减少。针对每1次相位比较,从控制代码dco_code的最上位比特msb向最下位比特lsb,值逐渐确定。state_count为指定二分法查找中的目标位的计数值。

[0103]

在时刻t

10

,当所有位的查找完成时,saren信号成为“低”,并转换为第2模式通过二分法查找得到的控制代码code_bs被设置为环路滤波器514的初始值。在后续的时刻t

11

,当基准时钟clk_ref的边沿被注入时,dco200开始振荡,控制代码code_fb由环路滤波器514来调整。此时,通过二分法查找,环路滤波器514与已经施加了频率锁定的状态是等价的。因此,pll电路100a具有如下这样的优点:在基准时钟clk_ref被输入的时刻t

11

的瞬间,

从与相位锁定等价的状态开始。此外,包含基准时钟clk_ref的正边沿那样的窗口信号inj_windb被生成,基准时钟clk_ref被注入到dco200,相位锁定被维持。

[0104]

以上是pll电路100a的通常的起动动作。接着,针对pll电路100(100a)的高速起动进行说明。

[0105]

控制器500在初次起动时基于第1模式会通过二分法查找来探索最优的控制代码dco_code,而在第2次以后的起动时,会不经由第1模式地,立即开始振荡。具体而言,控制器500响应于pll电路100的停止指示(使能信号en

の

的“低”),保持此时的控制代码dco_code,并在下一个pll电路100的起动指示(使能信号en的“高”)时,以保持的控制代码为初始值,立即转变为第2模式。

[0106]

图8是对pll电路100的第2次以后的起动进行说明的时序图。在时刻t0,使能信号en成为“低”,在时刻t1,当enreg信号成为“低”时,pll电路100停止。在pll电路100停止后,控制代码dco_code的值也被保持。在时刻t2,使能信号en成为“高”,在时刻t3,enreg信号成为“高”。在时刻t4,当基准时钟clk_ref的边沿被注入时,pll电路100开始振荡。如此,针对第2次以后,能够在1个循环内从相位同步的状态进行重启。

[0107]

即,在具备该注入同步型的pll电路100的系统中,能够积极地对pll电路的动作、停止进行切换,在供给时钟clk_out的负载停止的期间,能够通过将使能信号en设为“低”,从而大幅地削减pll电路100的耗电。

[0108]

图9是表示图5的窗口产生器400的构成例的电路图。在图9中,省略了图5的选择器522及二分法查找部512等。

[0109]

可变延迟电路210能够构成为第1延迟电路212与第2延迟电路214的串联连接,第1延迟电路212赋予相对较粗的分辨率的延迟,第2延迟电路214赋予相对较高的分辨率的延迟。可变延迟电路210的输出作为内部时钟clk_int而被引出到可变频率振荡器200的外部。作为环形振荡器的可变频率振荡器200包含用于逻辑反相的逆变器,但逆变器的插入位置不被限定,既可以设置于可变延迟电路的输入侧,也可以设置于输出侧,还可以组装在可变延迟电路或复用器中。

[0110]

复用器220在一个输入(1)接收内部时钟clk_int,在另一个输入(0)接收注入沿inj_edge,并选择与选择信号sel(窗口信号inj_windb)相应的一者。具体而言,在窗口信号inj_windb有效(在本实施方式中,为负逻辑系,低=0)时选择注入沿inj_edge,在窗口信号inj_windb无效(高=1)时选择内部时钟clk_int。复用器220的输出被返回到可变延迟电路210的输入。

[0111]

反馈电路300与图5的相位频率比较器502及环路滤波器514对应。可变频率振荡器200的振荡频率f

dco

对赋予可变延迟电路210的控制代码进行反馈控制,使其接近基于基准时钟clk_ref的频率f

ref

的目标频率。例如,将规定目标频率f

tgt

的fcw(frequency control word:频率控制字)输入到反馈电路300,并以f

ref

×

fcw为目标频率,使内部时钟clk_int(即输出时钟clk_dco)的频率f

dco

稳定化。

[0112]

反馈电路300的构成或控制方式不被特别地限定,能够使用fll(frequency locked loop:锁频环)方式或pll(phase locked loop:锁相环)方式中的任意一个,或者兼用它们。例如,也可以是,通过fll方式来控制第1延迟电路212的延迟量,通过pll方式来控制第2延迟电路214的延迟量。或者,也可以是,通过pll方式来控制第1延迟电路212与第2延

迟电路214这两者的延迟量。

[0113]

窗口产生器400通过接收内部时钟clk_int,并切出1个脉冲,从而生成窗口信号inj_windb。即,在本实施方式中,窗口信号inj_windb被与基准时钟clk_ref无关地生成。

[0114]

以上是pll电路100的基本构成。接着,对其动作进行说明。图10是图9的pll电路100的动作波形图。可变频率振荡器200所生成的内部时钟clk_int及输出时钟clk_dco为对基准时钟clk_ref进行n倍增的信号。窗口信号inj_windb通过将内部时钟clk_int的脉冲(半周期)切出,并适当地配合定时来生成,因此,窗口信号inj_windb能够在其有效期间(低区间),包含基准时钟clk_ref的边沿。该注入沿inj_edge被注入到可变频率振荡器200,可变频率振荡器200所生成的内部时钟clk_int(及输出时钟clk_dco)由注入沿inj_edge进行重定时。

[0115]

以上是pll电路100的动作。根据该pll电路100,窗口信号inj_windb所规定的窗打开(有效)的定时、以及窗关闭(无效)的定时不取决于基准时钟clk_ref。因此,在可变频率振荡器200振荡的期间,无论有无基准时钟clk_ref,都能够可靠地使窗开闭。

[0116]

此外,能够进行定时调整,使得在窗打开的期间可靠地包含基准时钟clk_ref的注入沿inj_edge,因此不会产生因窗口信号导致的毛刺或谐波振荡。若是在窗打开的期间不发生基准时钟的转变(边沿),则内部时钟clk_int(及输出时钟clk_dco)的周期会以每预定循环(倍增数n)1次的比例变长,但振荡不会停止。根据图9的pll电路100,能够解决以往的问题点中的一些。

[0117]

接着,回到图9。窗口产生器400按内部时钟clk_int的每n个循环(n≥2)1次地、在内部时钟clk_int的半个循环(即内部时钟的高区间或低区间)期间,生成被置于有效的脉冲信号injwb,并使脉冲信号injwb延迟内部时钟clk_int的周期的k倍(0<k<1)时间,从而生成窗口信号inj_windb。n优选为pll电路100的倍增数。

[0118]

在设k=1/4的情况下,能够对窗口信号inj_windb的定时进行调节,使得在窗口信号inj_windb的有效期间(低)的中央,存在注入沿inj_edge。

[0119]

窗口产生器400包含计数器402、逻辑门404、以及延迟线406。计数器402对内部时钟clk_int进行计数,并每n个周期地在1个周期期间,使其输出injw_en有效。逻辑门404对计数器402的输出injw_en和内部时钟clk_int进行逻辑运算,生成脉冲信号injwb。例如,也可以是,逻辑门404包含nand门,该nand门生成内部时钟clk_int的反相信号与计数器402的输出injw_en的否定逻辑积。

[0120]

以上是pll电路100的基本构成。接着,对其动作进行说明。图11是图9的pll电路100的动作波形图。在此,示出n=16的情况。计数器402由4位构成,进位信号被设为injw_en。clk_intb为内部时钟clk_int的反相信号,通过injw_en信号与doc_intb信号的nand运算来生成脉冲信号injwb。通过向该脉冲信号injwb赋予相当于内部时钟clk_int的周期的约1/4(clk_int的脉冲宽度的1/2)的延迟,从而生成窗口信号inj_windb。基准时钟clk_ref的正边沿(注入沿)会位于inj_windb信号的实质上的中心,因此即使在抖动被重叠于基准时钟clk_ref的情况下,只要为内部时钟clk_int的脉冲宽度(clk_int的1/4周期)的范围,就也能够通过注入沿来开始重定时。

[0121]

图12是表示pll电路100的具体的构成例的电路图。接着,针对可变频率振荡器200进行说明。第1延迟电路212和第2延迟电路214如上所述,分辨率是不同的,前者具有适于赋

予低分辨率的延迟的构成,后者具有适于赋予高分辨率的延迟的电路构成。也可以是,第2延迟电路214包含分辨率不同的2个延迟电路214m、214f。

[0122]

复用器220包含第1nand门222~第4nand门228及逆变器230。一般地,复用器220由2个nand门的“对”构成,因此有时会存在如下情况:2个输入信号的延迟因元件偏差的影响而产生差。因此,能够通过对称地配置2个该“对”来减少2个输入信号的延迟差。

[0123]

接着,针对窗口产生器400进行说明。如上所述,延迟线406所赋予的延迟为内部时钟clk_int的周期的约1/4。在可变频率振荡器200中,可变延迟电路210所赋予的延迟相当于内部时钟clk_int(clk_dco)的周期的1/2。因此,可变延迟电路210所赋予的延迟的一半会成为应赋予给injwb信号的延迟。

[0124]

内部时钟clk_int的半个周期的长度中,基于第1延迟电路212的是主导的。因此,延迟线406被构成为:忽略第2延迟电路214所赋予的延迟,并将第1延迟电路212的延迟的1/2倍的延迟赋予injwb信号。

[0125]

被赋予第1延迟电路212的控制代码为温度计码code_c[62:0],并被构成为能够产生将温度计码code_c[62:0]的值(标有“1”的位数)乘以单位延迟得到的延迟。在该例中,温度计码为63位。

[0126]

延迟线406为具有与第1延迟电路212相同电路形式的复制,单位延迟被设计为与第1延迟电路212相同,级数为第1延迟电路212的级数的1/2。因此,赋予延迟线406的温度计码code_d[31:0]的位数为赋予第1延迟电路212的温度计码的位数的1/2。code_d[31:0]能够通过每隔1位对code_c[62:0]进行间隔剔除来生成。

[0127]

在图12中,图8的逻辑门404被以分解为逆变器404a和nand门404b的方式示出。在窗口产生器400,还设置有虚拟的复用器410。

[0128]

复用器410用于消除可变频率振荡器200中的复用器220的影响。复用器410为复用器220的复制,通过向延迟线406的输出injwb_dly赋予与复用器220相同的延迟的方式来消除复用器220的影响。

[0129]

本领域技术人员应理解的是,实施方式仅为例示,在它们的各构成要素或各处理过程的组合中能够存在各种变形例,且那样的变形例也在本发明的范围之内。以下,对这样的变形例进行说明。

[0130]

在实施方式中,作为注入沿,使用了基准时钟clk_ref的边沿,但不限于此,也可以是,对基准时钟clk_ref进行倍增,并将其作为倍增后的时钟的注入沿来使用。

[0131]

虽然基于实施方式,用具体的语句来对本发明进行了说明,但实施方式仅表示本发明的原理及应用,对于实施方式,在不脱离权利要求书所规定的本发明的思想的范围内,允许许多变形例或配置的变更。

[0132]

[工业可利用性]

[0133]

本公开能够利用于pll(phase locked loop:锁相环)电路。

[0134]

[附图标记说明]

[0135]

100 pll电路

[0136]

102 输出门

[0137]

200 dco

[0138]

210 可变延迟电路

[0139]

212 第1延迟电路

[0140]

214 第2延迟电路

[0141]

220 复用器

[0142]

222 第1nand门

[0143]

224 第2nand门

[0144]

226 第3nand门

[0145]

228 第4nand门

[0146]

230 逆变器

[0147]

500 控制器

[0148]

502 相位频率比较器

[0149]

504 信号处理部

[0150]

512 二分法查找部

[0151]

514 环路滤波器

[0152]

516 选择器

[0153]

522 选择器

[0154]

530 触发器

[0155]

532 逆变器

[0156]

300 反馈电路

[0157]

310 pfd

[0158]

312 门控电路

[0159]

314、316 锁存电路

[0160]

318 数字滤波器

[0161]

320 对称型pd

[0162]

400 窗口产生器

[0163]

402 计数器

[0164]

404 逻辑门

[0165]

406 延迟线

[0166]

410 复用器

[0167]

412 屏蔽电路

[0168]

420 时钟监视电路

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。