改进稳定性的电阻性pcb迹线

1.相关申请案的交叉引用

2.本技术案主张2019年10月3日申请的第62/909,921号美国临时专利申请案及2020年3月30日申请的第16/834,309号美国专利申请案的权益及优先权,其全部内容以引用的方式并入本文中。

技术领域

3.本发明大体上涉及使用电阻性印刷电路板(pcb)迹线以改进集成电路性能、稳定性及制造。

背景技术:

4.随着集成电路在大小上减小及在复杂性上增加,高频电路中出现新的问题。

5.集成电路的电源网络具有相关联的阻抗。随着电路演进,存在对低阻抗的更大需要,且存在对更宽频率范围的需要,以便集成电路更快地操作及获得更快的数据速率。然而,如果集成电路具有随电容器谐振的电感,那么现代陶瓷电容器在用作解耦或旁路电容器时可能是不稳定的。

6.一个替代方案是使用钽电容器。然而,生产此类电容器所需的材料来自不稳定地区。因此,出于社会及经济原因两者,使用钽电容器是非期望的。

7.另一方法是使用电阻器来抑制陶瓷电容器的谐振,从而减小集成电路的阻抗峰值。然而,最近已存在电阻器的全球性短缺,这具有增加交付周期及价格的效应。

8.因此,存在对在不诉诸于使用电阻器的情况下避免使用钽电容器的解决方案的未满足需求。

技术实现要素:

9.本发明的某些方面涉及一种在pcb上延伸pcb迹线的方法。所述pcb包括多个pcb层。所述方法包括在所述多个pcb层中的至少一者上形成导电迹线;将所述导电迹线的第一部分耦合到在所述多个pcb层中的至少一者上形成的电容器;将不同于所述导电迹线的所述第一部分的第二部分耦合到在延伸穿过所述多个pcb层中的两者或更多者的第一通孔内形成的导电材料;及根据预定阻抗可配置地设置所述导电迹线的导电路径的长度。在平面图中所述电容器与所述第一通孔以第一距离横向分离。在所述平面图中所述导电迹线的所述长度大于所述第一距离。所述长度的所述导电迹线的所述导电路径具有所述预定阻抗。

10.根据本发明的某些实施例,所述方法进一步包含选择性地切割多个迹线段中的至少一者以形成具有所述长度的所述导电迹线的所述导电路径。

11.根据本发明的其它实施例,所述方法进一步包含在所述平面图中在第一区域及第二区域中形成彼此平行的所述多个迹线段中的两者或更多者。所述第一区域中的所述两个或更多个多个迹线段之间的第一横向距离大于所述第二区域中的所述两个或更多个多个迹线段之间的第二横向距离。

12.根据本发明的又其它实施例,所述方法进一步包含选择性地电连接多个断开连接的迹线段中的两者或更多者,以形成具有所述长度的所述导电迹线的所述导电路径。

13.在某些其它实施例中,所述方法进一步包含在第一区域及第二区域中形成彼此平行的所述多个断开连接的迹线段中的两者或更多者,其中所述第一区域中的所述两个或更多个多个断开连接的迹线段之间的第一横向距离大于所述第二区域中的所述两个或更多个多个断开连接的迹线段之间的第二横向距离。

14.根据本发明的一些实施例,所述方法进一步包含用桥电连接所述导电迹线上的两个或更多个位置,其中所述导电迹线的所述导电路径的所述长度包含所述桥的长度。

15.根据本发明的某些其它实施例,所述方法进一步包含切割所述导电迹线的一部分。

16.根据本发明的又其它实施例,所述方法进一步包含形成延伸穿过所述多个pcb层中的两者或更多者的第二通孔,其中,当电流流过所述第一通孔及所述第二通孔时,所述第一通孔具有具第一极性的第一电场,且所述第二通孔具有具与所述第一极性相反的第二极性的第二电场,使得所述第一电场与所述第二电场彼此抵消。

17.根据本发明的一些实施例,所述方法也包含形成第二通孔,在所述平面图中所述第二通孔延伸穿过所述多个pcb层中的两者或更多者,与所述第一通孔相距介于0.2mm与4mm之间。

附图说明

18.图1是根据某些现有技术方法的pcb上的电路的一部分的框图。

19.图2展示根据本发明的某些实施例的一个电路配置的一部分。

20.图3a展示根据本发明的某些实施例的一个可能的pcb迹线设计。

21.图3b展示根据本发明的某些实施例的另一可能的pcb迹线设计。

22.图3c展示根据本发明的某些实施例的又另一可能的pcb迹线设计。

23.图4展示根据本发明的某些实施例的一个集成电路配置的一部分。

24.图5展示根据本发明的某些方面的电源及接地通孔的紧邻定位。

具体实施方式

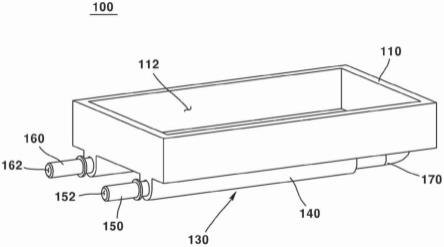

25.图1说明用于设计向集成电路(未展示)供应电力的印刷电路板(pcb)100上的电源电路的一部分的某些现有技术方法。pcb 100的大部分是接地平面110。大接地平面的一些优点是使电路布局更容易,从而允许设计者在不需要延伸额外迹线的情况下将任何组件接地。接地平面110不必唯一地位于pcb 100的表面上,或甚至根本不必位于所述表面上。一种可能性是接地平面110位于或部分位于pcb 100的单独层中。所属领域的一般技术人员将理解,接地平面110的不同配置及放置是可能的。

26.在多层pcb(例如pcb 100)的情况下,其中接地平面也可占用pcb的特定层,通孔120用作指向较低接地平面层的接地。这允许迹线(例如迹线130c)连接到集中接地点。

27.接地平面110传导来自许多组件的大返回电流,而无显著的电压降,从而确保所有组件的接地连接处于相同的参考电势。在pcb 100的情况下,返回点(例如,电源通孔,未说明)将把电路连接到电源平面以完成电路。然而,由于组件(例如电容器150及电阻器160)所

需的空间,可能难以将接地点及电源点放置为彼此靠近。这部分与电容器150及电阻器160的大小有关。然而,基板面(real estate)需求还必须考虑多个安装垫140,以及迹线130b及130a,其将这些组件连接到包含集成电路的更大电路内的其它组件。返回路径越长,串扰风险越高,因为更长的返回路径产生大的电感场,这会干扰pcb 100上的信号。串扰及信号降级风险随着更长的返回路径而增加,这至少部分因为存在一个大的风险,即路径将靠近另一路径延伸,使得其磁场/电感场可导致非所要的电压/信号(即,噪声)被由于磁耦合或电容耦合而流入另一路径的电流感应到一个路径上。

28.例如,在电阻器160是0402英制电阻器(1005公制电阻器)的情况下,这不是微不足道量的基板面。明确来说,即使在试图降低最小化真实状态影响的设计中,电阻器160、其相关联的垫140及其专用迹线130b(将电阻器160连接到电容器150)及130c(将电阻器160连接到接地通孔120)也可能占据2.42平方毫米的空间。随着集成电路大小的不断缩小,这可能是大量的空间。

29.这并没有考虑到电阻器160也占据大约0.35毫米的垂直空间(不考虑垫140)。除了占据垂直空间外,电阻器160的存在还要求将集成电路上的电流上拉,且然后下推,以流过座落在pcb 100的表面上方的电阻器160。当电流移动通过电阻器160时,其被有效地从pcb 100的表面提离。这增加返回路径的长度。如上文所提及,这可能导致串扰及信号降级。

30.然而,在传统设计中,需要电阻器160来抑制电容器150的谐振,以便减小阻抗峰值的量值,这在现代高频低阻抗集成电路中是非期望的。

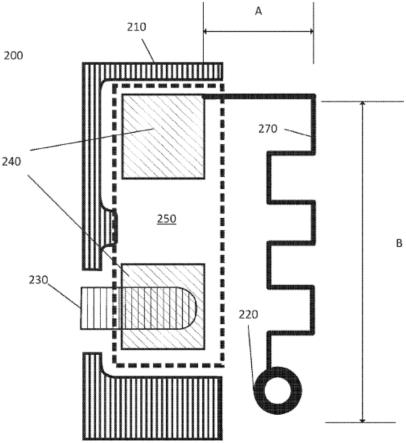

31.图2说明根据本文所描述的某些实施例在pcb 200上设计集成电路的类似部分的方法。与图1中所说明的集成电路的部分类似,图2的集成电路在具有接地平面210的pcb 200上实施。此外,图2的集成电路也具有电容器250,所述电容器250使用垫240连接到pcb 200,并使用迹线230连接到其它组件(例如集成电路)。

32.然而,与图1的电路不同,不存在物理表面安装电阻器或相关联的垫。确切来说,电容器直接通过迹线270连接到接地通孔220。为了便于理解,pcb迹线270被说明为与迹线230不同。然而,所属领域的一般技术人员将理解,可使用若干材料及方法来实施pcb上的迹线,且迹线230及270可相似或完全不同,这取决于集成电路设计的需要。

33.pcb迹线270经设计以具有一定长度以产生类似于电阻器140的等效串联电阻(esr)。所需的长度可取决于pcb迹线270的宽度而变化。pcb迹线270的宽度可随用于制造迹线导线的工艺或抑制电容器250的谐振形式以及连接到迹线230的集成电路引脚(未展示)的电感的需要而变化。例如,典型的生产工艺能够容易地生产80微米宽的pcb迹线。更先进工艺能够制作具有50微米的宽度的pcb迹线。所属领域的一般技术人员将理解,这些仅为实例,且根据需要生产具有任意数量的宽度的pcb迹线是可能的。

34.为了节省基板面,pcb迹线270可具有若干图案,例如图2中所说明的“z字形”图案。可实施各种图案以实现所期望的esr,同时将电容器250定位为紧邻接地通孔220。pcb迹线270的整体长度通常将长于电容器250与接地通孔220之间的距离,以便实现最大的空间节省。

35.选择适当的设计以匹配集成电路的esr需求,使得pcb迹线270能够产生足够的esr,以抑制电容器250的谐振及连接到迹线230的集成电路引脚(未展示)的电感。这消除对单独的电阻器,以及额外的项目,例如将单独的电阻器连接到集成电路所需的垫及其它迹

线的需要。这允许电路具有较小的基板面,同时减小成本。

36.空间节省可为显著的。例如,pcb迹线270及接地通孔220可占用具有0.4毫米的宽度a及仅2.5毫米的长度b的区域,以实现与0402英制电阻器相同的esr。也就是说,与在使用具有相当的esr的电阻器时需要超过2平方毫米相比,esr效应可通过仅占据1平方毫米来实现。这是基板面的显著减小,而同时消除电阻器。

37.在某些例子中,所需的esr是预先知道的,例如,在pcb将仅用于特定的集成电路的情况下。针对此类情况,图3a说明连接到接地通孔320的固定pcb迹线310。虽然固定pcb迹线310仅具有一个可能的长度及esr值,但其生产更便宜且更简单。

38.然而,存在其中固定pcb迹线310不够的许多情况。例如,当进行测试以确定特定esr值的pcb迹线的适当长度时或在pcb可用于不同电路设计的情况下,在pcb制造之前可能不知道确切的所需esr。在此类例子中,实施灵活的pcb迹线设计可能是有益的。

39.灵活的pcb迹线设计的一个实例在图3b中说明。pcb迹线330具有两个分支330a及330b,以及断开连接的分支330c。pcb迹线330的最终阻抗不是固定的。确切来说,取决于用于抑制由旁路/解耦电容器(未展示)形成的电路的谐振,及由集成电路(未展示)的电源引脚呈现的电感的电路esr值的配置的需要,可设置pcb迹线330的不同的最终长度。这可使用若干方法实现。此外,尽管申请案通篇,许多pcb迹线被说明为直线或组合或直线及90度角,但这不是必需的。pcb迹线可以曲线或任意角延伸。所属领域的一般技术人员将理解,存在若干方法来延伸pcb迹线。

40.分支330a及330b可在切割点340a及340b处切割,这将修改迹线330的阻抗,其中迹线330a、330b及330c等效于并联的电阻器。切割迹线将断开所述分支上的电路,并防止电流沿所述分支流动。剩余的未切割分支将形成最终长度,并确定pcb迹线330的阻抗,电流通过所述pcb迹线330流到接地通孔320。切割点340a及340b为说明性目的而展示,但所属领域的一般技术人员将理解,pcb迹线330,或由单独迹线330a、330b及330c并联形成的任何pcb迹线可具有具切口的可变数量的组成迹线340a、340b及340c,且切割点不唯一地限于沿pcb迹线330的固定点或预定点。在一些实施方案中,具有切口的迹线可用焊桥修复,以便复原迹线。切割点的位置还可经选择以最小化迹线330a、b、c的任何寄生电容或电感。然而,某些方面可使pcb迹线330的某些部分更适合于切割点。

41.例如,改变不同分支330a及330b与电容器(未说明)同接地通孔320之间的断开连接的分支330c之间的距离可能是有益的。这不仅可在布线及esr值选择的变化、寄生电容或电感的减小及/或变化方面形成一定的灵活性,而且可形成更有利的切割点。

42.切割平行的迹线分支并非为pcb迹线330增加变化及灵活性的唯一方法。pcb迹线330可含有断开连接的分支,例如断开连接的分支330c。断开连接的分支可在一端或两端上断开连接。断开连接的分支330c可通过将端点焊接到pcb迹线330或通过在断开连接的分支330c与pcb迹线330的端之间形成电连接的其它技术重新连接到pcb迹线330。可使用任何数量的分支、断开连接的分支或其组合来实施灵活的pcb迹线330。

43.对分支330a及330b以及任何断开连接的分支(例如断开连接的分支330c)进行布线,使得每一者在接地通孔320与电容器之间提供不同的并联阻抗,以便在布线及所产生的esr的变化方面提供最大的灵活性是有益的。然而,可能存在具有冗余长度的路径可能有益的时刻。例如,以便在错误的分支被切割时提供备份。

44.切割分支或连接断开连接的分支并非增加灵活性及esr变化的唯一方法。另一可能的方法在图3c中说明。pcb迹线350类似于图3a的固定pcb迹线310。然而,其经设计以具有靠近在一起延伸的部分,例如到电容器的连接附近的部分及到接地通孔320的连接附近的部分。这允许在这些部分之间形成桥370,缩短电流流过的pcb迹线350的整体长度,并从而减小esr值。

45.桥370可为焊桥,或通过布线新的迹线。所属领域的一般技术人员将理解,存在若干技术可用于桥接pcb迹线350的不同部分,以形成缩短电流在其上流动的路径的长度的电连接。

46.pcb迹线350可具有多于一个可能的桥接点,桥370被放置于所述桥接点处。不同的桥接点每一者将导致pcb迹线350的不同esr值,从而增加选择针对特定集成电路设计的期望esr值需求的额外灵活性。此外,另外切割或以其它方式断开连接pcb迹线350中呈现为冗余或未被桥370使用的部分可能是有益的。

47.所属领域的一般技术人员将理解,存在若干方法来实施灵活的pcb迹线以实现所期望的esr值,且图仅用于帮助更好地理解概念,且不包含所有可能的设计。

48.考虑到图4,使用pcb迹线来替换电源电路中的电阻器的另一优点变得显而易见。图4说明具有接地平面410的pcb 400上的电源电路的一部分。电源电路具有安装在垫440上的电容器450,所述垫440将电容器450连接到pcb 400。迹线430将电容器450连接到电源电路的其它组件,例如集成电路(未展示)的电源引脚。

49.根据本发明的某些方面,pcb迹线470提供足够的esr值,以抑制由电容器450形成的电路的谐振及由集成电路(未展示)的电源引脚呈现的电感,并将电容器连接到接地通孔420。与先前实例不同,pcb 400另外具有紧邻接地通孔420的电源通孔480。这因为pcb迹线470的空间节省使用,及抑制电容器谐振原本所需的电阻器的消除而是可能的。

50.将接地通孔420紧邻电源通孔480放置可产生若干有利的结果。例如,将接地通孔420靠近电源通孔480放置缩短电流返回路径,并减小由电容器450及电阻性迹线470形成的电源解耦电路所围封的面积。如上文所讨论的,由于减少的磁场/电感场及电容耦合,较短的返回路径比较长的返回路径提供更好的信号完整性。

51.图5说明根据本发明的某些实施例在多层pcb上将通孔彼此紧邻放置。如参考图4所描述的,用pcb迹线替换电阻器允许将不同的通孔(例如电源通孔580及接地通孔520)紧邻放置。这具有缩短电流的返回路径,从而导致改进的信号可靠性的直接好处。然而,也可从靠近地放置电源通孔580及接地通孔520实现其它优势。

52.一个此类优势源自于电源通孔580及接地通孔520的操作。作为返回路径590的部分,电流从电源层被上拉,并流过安装在pcb的表面上的组件。电流也被下推穿过接地通孔520到接地层。随着电流沿返回路径590流动,电源通孔580及接地通孔520两者产生电场。然而,电源通孔580及接地通孔520的电场将具有彼此相反的极性。

53.当电源通孔580及接地通孔520被分隔开放置时,电场可能干扰环绕的迹线上的信号或干扰集成电路的其它组件。减轻这些风险的一个方法是,以pcb基板面为代价将电源通孔580及接地通孔520远离其它迹线及组件放置。

54.然而,由于pcb迹线的使用允许将电源通孔580及接地通孔520紧邻放置,因此电源通孔580及接地通孔520可足够靠近在一起,以使相反极性的电场相互抑制或抵消。这减小

电源通孔580及接地通孔520的电场将干扰集成电路的操作的风险。

55.在本发明的某些实施例中,所属领域的一般技术人员将理解,相反极性的两个通孔应尽可能彼此靠近放置。例如,在某些实施例中,通孔在平面图中可被放置为彼此相距近至0.4mm,且在平面图中也可被放置为与垫相距近至0.2mm。然而,所属领域的一般技术人员将知道,制造商、客户或可能甚至制造技术/技术将规定并排通孔放置的最小距离。因此,所属领域的一般技术人员将理解,通孔之间的最小可能距离可在不脱离本发明的精神的情况下变化。

56.进一步来说,所属领域的一般技术人员将理解,磁场强度与穿过导体的电流成正比,且与距导体的距离成反比。例如,在距离导体1mm处,场强度为导体处的场强度的1/10。在距离导体2mm处,场强度为导体处初始场强度的1/20。在本发明的某些实施例中,将具有相反极性的两个通孔放置为分开超过4mm将展现几乎没有的场消除效应。

57.本发明的各个方面的其它目的、优点及实施例对于本发明领域的技术人员来说是显而易见的,且在描述及附图的范围内。例如,但非限制,结构或功能元件可依据本发明重新布置。类似地,根据本发明的原理可应用于其它实例,即使此处未具体详细描述,所述实例仍将在本发明的范围内。

58.此外,本发明通篇的元件引用可被划分为某些子元件、组合或复制,而不脱离本发明的精神。进一步来说,在不脱离本发明的精神的情况下,上文所讨论的一些特定组件(例如电容器)可为各种大小及实施方案。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。