1.本发明涉及光声技术领域,尤其涉及一种微型穿戴式光声信号采集系统。

背景技术:

2.光声效应是用脉冲激光作为激励,当脉冲激光照射组织时,组织吸收光能并将其转换为热能,随之产生热膨胀,最终以超声波的形式向外传播信号,即光声信号;光声信号通过超声耦合剂量被超声换能器接受,经过高速采集卡将模拟信号转变为数字信号并存储到计算机上;由于在光声效应中,厘米量级的吸收体产生的光声信号的频带约为20-300khz,毫米量级的吸收体产生的光声信号频带约为70khz-2.5mhz,微米量级的吸收体产生的光声信号的频带约为400khz-20mhz,人体的血管组织属于微米级的吸收体,因此吸收所激发的光声信号频率一般在几百khz到几十mhz之间,另外信号幅值一般为微伏级别,一个信号脉冲持续的时间为毫秒级甚至微秒级,产生的光声信号幅值较低,容易被噪声淹没,而现有的光声信号采集系统无法对微小的光声信号进行放大,采集效果不足。

技术实现要素:

3.本发明的目的在于提供一种微型穿戴式光声信号采集系统,能够在采集光声信号时对光声信号进行放大,提高光声信号幅值。

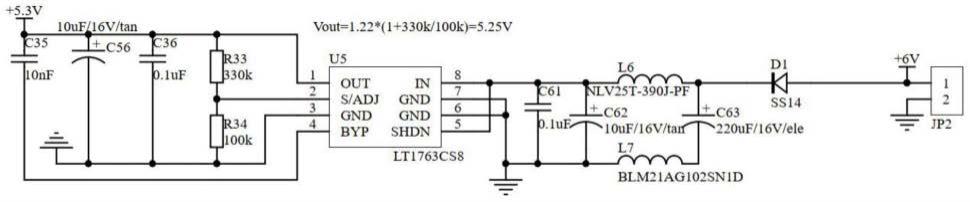

4.为实现上述目的,本发明提供了一种微型穿戴式光声信号采集系统,包括第一稳压电路、放大电路、第二稳压电路、模数转换电路、fpga主控电路、第三稳压电路和串口输出电路;所述放大电路和所述第一稳压电路电连接,所述模数转换电路和所述放大电路电连接,所述第二稳压电路和所述模数转换电路电连接,所述fpga主控电路和所述模数转换电路电连接,所述第三稳压电路和所述fpga主控电路电连接,所述串口输出电路和所述fpga主控电路电连接。

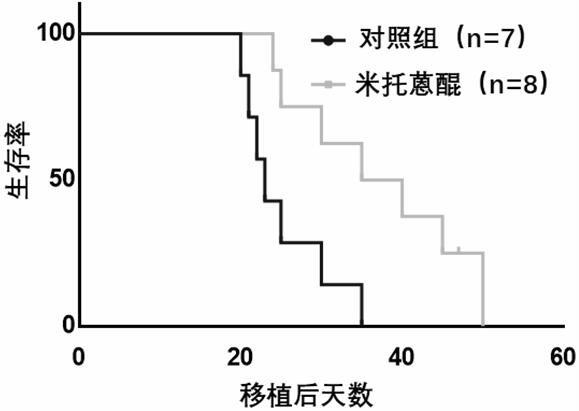

5.其中,所述第一稳压电路包括芯片u5、电阻r33、电容c36、电容r56、电容c35、电阻r34、电容c61、电感l6、二极管d1、插接件jp2、电容c62、电感l7和电容c63;

6.所述电阻r33一端和所述芯片u5的out端连接,另一端与所述芯片u5的s/adj端连接;所述电容c36一端与所述电阻r33连接;所述电容r56正极与所述电容c36连接,负极接地;所述电容c35一端与所述电容r56正极连接,另一端与所述芯片u5的byp端连接;所述电阻r34一端与所述电阻r33连接,另一端与所述芯片u5的gnd端连接;所述电容c61一端与所述芯片u5的in端连接,另一端接地;所述电感l6一端与所述电容c61连接;所述二极管d1负极与所述电感l6连接;所述插接件jp2一端与所述二极管d1正极连接,另一端接地;所述电容c62正极与所述电感l6连接,负极接地;所述电感l7一端与所述电容c62负极连接;所述电容c63正极与所述电感l6连接,负极与所述电感l7连接。

7.其中,所述放大电路包括射频连接器p1、电阻r19、电容c14、电阻r30、电阻r29、电阻r28、电感l5、电容c29、电容c27、电容c26、电容c23、电阻r32、运算放大器u4、电阻r12、电容c10、电阻r14、电容c16、电阻r16、电容c12、电阻r17、电容c13、电阻r27、电阻r25、电阻

r20、电感l4、电容c28、电容c25、电容c22、电容c17、电阻r31、运算放大器u3、电容c15、电阻r11、电容c9、电阻r13、电容c2、电阻r15和电容c11;

8.所述电阻r19一端与所述射频连接器p1连接;所述电容c14一端与所述电阻r19连接;所述电阻r30一端与所述电容c14连接;所述电阻r29一端与所述电阻r30连接;所述电阻r28一端与所述电阻r29连接;所述电感l5一端与所述电阻r28连接;所述电容c29一端与所述电感l5连接,另一端接地;所述电容c27正极和所述电阻r30连接,负极接地;所述电容c26一端与所述电阻r30连接,另一端接地;所述电容c23正极和所述电阻r29连接,负极接地;所述电阻r32一端与所述电阻r29连接,另一端接地;所述运算放大器u4一端同相输入端和所述电容c14连接;所述电阻r12一端与所述运算放大器u4反向输入端连接;所述电容c10一端与所述电阻r12连接,另一端接地;所述电阻r14一端与所述运算放大器u4反向输入端连接;所述电容c16一端与所述运算放大器u4同向输入端连接,另一端接地;所述电阻r16一端与所述运算放大器u4输出端连接;所述电容c12一端与所述电阻r16一端连接;所述电阻r17一端与所述电容c12一端连接;所述电容c13一端与所述电阻r17一端连接;所述电阻r27一端与所述电容c13连接;所述电阻r25一端与所述电阻r27连接;所述电阻r20一端与所述电阻r25连接;所述电感l4一端与所述电阻r20连接;所述电容c28一端与所述电感l4连接,另一端接地;所述电容c25正极和所述电阻r27连接,负极接地;所述电容c22一端与所述电阻r27连接,另一端接地;所述电容c17正极和所述电阻r25连接,负极接地;所述电阻r31一端与所述电阻r25连接,另一端接地;所述运算放大器u3同相输入端和所述电容c13连接;所述电容c15一端与所述运算放大器u3同相输入端连接,另一端接地;所述电阻r11一端和所述运算放大器u3反相输入端连接;所述电容c9一端和所述电阻r11连接,另一端接地;所述电阻r13一端和所述运算放大器u3反相输入端连接;所述电容c2一端和所述运算放大器u3反相输入端连接,另一端和所述电阻r13连接;所述电阻r15一端和所述运算放大器u3输出端连接;所述电容c11一端和所述电阻r15连接,另一端和所述模数转换电路连接。

9.其中,所述第二稳压电路包括芯片usb2、电容c125、电容c126、电容e1、电阻r48、稳压芯片u10、电阻r49、指示灯led1、电容e2和电容c80;

10.所述电容c125一端和所述芯片usb2的vbus端连接,另一端接地;所述电容c126一端和所述芯片usb2的vbus端连接,另一端接地;所述电容e1负极接地;所述电阻r48一端和所述电容e1正极连接;所述稳压芯片u10的vin端和所述电阻r48连接;所述电阻r49和所述稳压芯片u10的vout端连接;所述指示灯led1正极和所述电阻r49连接,负极接地;所述电容e2正极和所述电阻r48连接,负极接地;所述电容c80一端和所述稳压芯片u10的vout端连接,另一端接地。

11.其中,所述模数转换电路包括芯片u6、电阻r36、排阻rp1、排阻rp2、排阻rp3、电容c64、电容c65、电阻r41、电阻r42、芯片u7、电阻r35、电阻r38、电阻r37、电阻r39、电阻r40、电阻r43、电阻r44、电阻r47、电容c27、电阻r45、电阻r46、电容c68、电容c69、电容c70、电容c73、电容c74、电容c75、电容c77和电容c78;

12.所述电阻r36一端和所述芯片u6的clk端连接;所述排阻rp1一端分别与所述芯片u6的d8端、d9端、d10端、d11端连接;所述排阻rp2一端分别与所述芯片u6的d4端、d5端、d6端、d7端连接;所述排阻rp3一端分别与所述芯片u6的d0端、d1端、d2端、d3端连接;所述电容c64一端和所述芯片u6的drvdd端连接,另一端接地;所述电容c65一端和所述芯片u6的

avdd1端连接,另一端接地;所述电阻r41一端和所述芯片u6的vinb端连接;所述电阻r一端和所述芯片u6的vina端连接;所述芯片u7的 out端和所述电阻r42连接,-out端和所述电阻r41连接;所述电阻r35一端和所述电阻r41连接,另一端和所述芯片u7的 in端连接;所述电阻r38一端和所述电阻r35连接;所述电阻r37一端和所述电阻r38连接,另一端接地;所述电阻r39一端和所述电阻r38连接;所述电阻r40一端和所述电阻r39连接,另一端和所述电容c11连接;所述电阻r43一端和所述电阻r40连接,另一端接地;所述电阻r44一端和所述电阻r40连接,另一端接地;所述电阻r47一端和所述电阻r42连接,另一端和所述芯片u7的-in端连接;所述电容c27一端和所述芯片u7的v 端连接,另一端接地;所述电阻r一端和所述电阻r47连接;所述电阻r46一端和所述电阻r45连接,另一端接地;所述电容c68一端和所述芯片u6的cpat端连接,另一端接地;所述电容c69一端和所述芯片u6的cpat端连接,另一端和所述电容c73连接;所述电容c70一端和所述芯片u6的cpat端连接,另一端和所述电容c73连接;所述电容c73一端和所述电容c70、所述电容c69连接,另一端接地;所述电容c74一端和所述芯片u6的avdd2端连接,另一端接地;所述电容c75一端和所述芯片u6的vref端连接,另一端接地;所述电容c77一端和所述芯片u6的vref端连接,另一端接地;所述电容c78一端和所述芯片u6的vref端连接,另一端接地。

13.其中,所述第三稳压电路包括芯片u2、电感l1、电阻r21、电容c54、电阻r132、电容c18、电容c19、电感l3、电阻r26、电容c71、电阻r24、电容c67、电容c5、电感l2、电阻r10、电容c202、电阻r6、电容c57、电容c58、电阻r5、电容c20、电容c4、电容c21、电容c66、电容c24、电容c76、电容c72、电容c201、电阻r1、电阻r2、电阻r3和电阻r7;

14.所述电感l1一端和所述芯片u2的lx1端连接;所述电阻r21一端和所述芯片u2的fb1端连接,另一端接地;所述电容c54一端和所述电感l1连接,另一端和所述芯片u2的fb1端连接;所述电阻r132一端和所述电容c54连接,另一端和所述芯片u2的fb1端连接;所述电容c18一端和所述电感l1连接,另一端接地;所述电容c19一端和所述电感l1连接,另一端接地;所述电感l3一端和所述芯片u2的lx3端连接;所述电阻r26一端和所述芯片u2的fb3端连接,另一端接地;所述电容c71一端和所述电感l3连接,另一端和所述芯片u2的fb3端连接;所述电阻r24一端和所述电容c71连接,另一端和所述芯片u2的fb3端连接;所述电容c67一端和所述电感l3连接,另一端接地;所述电容c5一端和所述电感l3连接,另一端接地;所述电感l2一端和所述芯片u2的lx4端连接;所述电阻r10一端和所述芯片u2的fb4端连接,另一端接地;所述电容c202一端和所述电感l2连接,另一端和所述芯片u2的fb4端连接;所述电阻r6一端和所述电容c202连接,另一端和所述芯片u2的fb4端连接;所述电容c57一端和所述电感l2连接,另一端接地;所述电容c58一端和所述电感l2连接,另一端接地;所述电阻r5一端和所述芯片u2的fb2端连接,另一端接地;所述电容c20一端和所述芯片u2的vin1端连接,另一端接地;所述电容c4一端和所述电容c20连接,另一端和所述芯片u2的vcc端连接;所述电容c21一端和所述芯片u2的vin1端连接,另一端接地;所述电容c66一端和所述电容c21连接,另一端和所述芯片u2的vcc端连接;所述电容c24一端和所述芯片u2的vin1端连接,另一端接地;所述电容c76一端和所述电容c24连接,另一端和所述芯片u2的vcc端连接;所述电容c72一端和所述芯片u2的vin1端连接,另一端接地;所述电容c201一端和所述电容c72连接,另一端和所述芯片u2的vcc端连接;所述电阻r1一端和所述芯片u2的en1端连接;所述电阻r2一端和所述芯片u2的en2端连接;所述电阻r3一端和所述芯片u2的en3端连接;

所述电阻r7一端和所述芯片u2的en4端连接。

15.其中,所述串口输出电路包括芯片ic2、电容c1和电容c3;

16.所述芯片ic2的ud 端和所述芯片usb2的dp2端连接,所述芯片ic2的ud-端和所述芯片usb2的dn2端连接;所述电容c1一端和所述芯片ic2的vcc端连接,另一端接地;所述电容c3一端和所述芯片ic2的vcc端连接,另一端接地。

17.本发明的一种微型穿戴式光声信号采集系统,超声探头的超声脉冲信号经过所述放大电路放大后,经过所述模数转换电路转换为12位的数字信号,所述fpga主控电路每次提供一个65mhz的时钟上升沿,所述模数转换电路进行一次数据转化,得到一次信号,持续提供65mhz的时钟就可以持续对放大的模拟信号进行模数转化,随后数据经所述串口输出电路输出,能够在采集光声信号时对光声信号进行放大,提高光声信号幅值。

附图说明

18.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

19.图1是本发明的第一稳压电路的电路图。

20.图2是本发明的放大电路的电路图。

21.图3是本发明的第二稳压电路的部分电路图。

22.图4是本发明的第二稳压电路的另一部分电路图。

23.图5是本发明的第三稳压电路的电路图。

24.图6是本发明的模数转换电路的电路图。

25.图7是本发明的串口输出电路的电路图。

26.图8是采集正弦信号的波形图。

27.图9是采集方波的波形图。

28.图10是本发明收发模式下波形图。

29.图11是数字示波器收发模式下波形图。

30.图12是有黑胶布时本发明采集的波形图。

31.图13是无黑胶布时本发明采集的波形图。

32.图14是有黑胶布时数字示波器采集的波形图。

33.图15是无黑胶布时数字示波器采集的波形图。

34.图16是本发明的一种微型穿戴式光声信号采集系统的结构示意图。

35.1-第一稳压电路、2-放大电路、3-第二稳压电路、4-模数转换电路、5-fpga主控电路、6-串口输出电路、7-第三稳压电路。

具体实施方式

36.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

37.在本发明的描述中,需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

38.请参阅图1~图16,本发明提供一种微型穿戴式光声信号采集系统:包括第一稳压电路1、放大电路2、第二稳压电路3、模数转换电路4、fpga主控电路5、第三稳压电路7和串口输出电路6;所述放大电路2和所述第一稳压电路1电连接,所述模数转换电路4和所述放大电路2电连接,所述第二稳压电路3和所述模数转换电路4电连接,所述fpga主控电路5和所述模数转换电路4电连接,所述第三稳压电路7和所述fpga主控电路5电连接,所述串口输出电路6和所述fpga主控电路5电连接。

39.在本实施方式中,超声探头的超声脉冲信号经过所述放大电路2放大后,经过所述模数转换电路4转换为12位的数字信号,所述fpga主控电路5每次提供一个65mhz的时钟上升沿,所述模数转换电路4进行一次数据转化,得到一次信号,持续提供65mhz的时钟就可以持续对放大的模拟信号进行模数转化,随后数据经所述串口输出电路6输出,能够在采集光声信号时对光声信号进行放大,提高光声信号幅值。

40.进一步的,所述第一稳压电路1包括芯片u5、电阻r33、电容c36、电容r56、电容c35、电阻r34、电容c61、电感l6、二极管d1、插接件jp2、电容c62、电感l7和电容c63;

41.所述电阻r33一端和所述芯片u5的out端连接,另一端与所述芯片u5的s/adj端连接;所述电容c36一端与所述电阻r33连接;所述电容r56正极与所述电容c36连接,负极接地;所述电容c35一端与所述电容r56正极连接,另一端与所述芯片u5的byp端连接;所述电阻r34一端与所述电阻r33连接,另一端与所述芯片u5的gnd端连接;所述电容c61一端与所述芯片u5的in端连接,另一端接地;所述电感l6一端与所述电容c61连接;所述二极管d1负极与所述电感l6连接;所述插接件jp2一端与所述二极管d1正极连接,另一端接地;所述电容c62正极与所述电感l6连接,负极接地;所述电感l7一端与所述电容c62负极连接;所述电容c63正极与所述电感l6连接,负极与所述电感l7连接。

42.在本实施方式中,所述芯片u5采用lt1763正线性稳压器芯片,低噪声且输出可调,用于作为放大器的稳压电路,通过lt1763的芯片控制所述电阻r33和所述电阻r34的比例关系使得输出的电压为5.25v作为放大的正向输入电压。

43.进一步的,所述放大电路2包括射频连接器p1、电阻r19、电容c14、电阻r30、电阻r29、电阻r28、电感l5、电容c29、电容c27、电容c26、电容c23、电阻r32、运算放大器u4、电阻r12、电容c10、电阻r14、电容c16、电阻r16、电容c12、电阻r17、电容c13、电阻r27、电阻r25、电阻r20、电感l4、电容c28、电容c25、电容c22、电容c17、电阻r31、运算放大器u3、电容c15、电阻r11、电容c9、电阻r13、电容c2、电阻r15和电容c11;

44.所述电阻r19一端与所述射频连接器p1连接;所述电容c14一端与所述电阻r19连接;所述电阻r30一端与所述电容c14连接;所述电阻r29一端与所述电阻r30连接;所述电阻r28一端与所述电阻r29连接;所述电感l5一端与所述电阻r28连接;所述电容c29一端与所述电感l5连接,另一端接地;所述电容c27正极和所述电阻r30连接,负极接地;所述电容c26一端与所述电阻r30连接,另一端接地;所述电容c23正极和所述电阻r29连接,负极接地;所

述电阻r32一端与所述电阻r29连接,另一端接地;所述运算放大器u4一端同相输入端和所述电容c14连接;所述电阻r12一端与所述运算放大器u4反向输入端连接;所述电容c10一端与所述电阻r12连接,另一端接地;所述电阻r14一端与所述运算放大器u4反向输入端连接;所述电容c16一端与所述运算放大器u4同向输入端连接,另一端接地;所述电阻r16一端与所述运算放大器u4输出端连接;所述电容c12一端与所述电阻r16一端连接;所述电阻r17一端与所述电容c12一端连接;所述电容c13一端与所述电阻r17一端连接;所述电阻r27一端与所述电容c13连接;所述电阻r25一端与所述电阻r27连接;所述电阻r20一端与所述电阻r25连接;所述电感l4一端与所述电阻r20连接;所述电容c28一端与所述电感l4连接,另一端接地;所述电容c25正极和所述电阻r27连接,负极接地;所述电容c22一端与所述电阻r27连接,另一端接地;所述电容c17正极和所述电阻r25连接,负极接地;所述电阻r31一端与所述电阻r25连接,另一端接地;所述运算放大器u3同相输入端和所述电容c13连接;所述电容c15一端与所述运算放大器u3同相输入端连接,另一端接地;所述电阻r11一端和所述运算放大器u3反相输入端连接;所述电容c9一端和所述电阻r11连接,另一端接地;所述电阻r13一端和所述运算放大器u3反相输入端连接;所述电容c2一端和所述运算放大器u3反相输入端连接,另一端和所述电阻r13连接;所述电阻r15一端和所述运算放大器u3输出端连接;所述电容c11一端和所述电阻r15连接,另一端和所述模数转换电路4连接。

45.在本实施方式中,lt1763正线性,考虑到产生的光声信号幅值为微伏级别,因此需要至少60db级别的放大,同时,需要性能稳定,噪声系数低的放大电路2,两级放大,所述运算放大器u3和所述运算放大器u4采用lmh6629,经测试中心频率为5.5mhz,实测增益72db,满足要求。

46.进一步的,所述第二稳压电路包括芯片usb2、电容c125、电容c126、电容e1、电阻r48、稳压芯片u10、电阻r49、指示灯led1、电容e2和电容c80;

47.所述电容c125一端和所述芯片usb2的vbus端连接,另一端接地;所述电容c126一端和所述芯片usb2的vbus端连接,另一端接地;所述电容e1负极接地;所述电阻r48一端和所述电容e1正极连接;所述稳压芯片u10的vin端和所述电阻r48连接;所述电阻r49和所述稳压芯片u10的vout端连接;所述指示灯led1正极和所述电阻r49连接,负极接地;所述电容e2正极和所述电阻r48连接,负极接地;所述电容c80一端和所述稳压芯片u10的vout端连接,另一端接地。

48.在本实施方式中,所述第二稳压电路3为所述模数转换电路4提供稳压电源,以所述芯片usb2,即typc-c为输入源,typc-c电压提供5v的外部输入电压,另外还提供ch340的串口输出口用于与计算机的数据传输;所述稳压芯片u10选用ams1117-3v3,5v输入电压通过ams1117-3v3输出3.3v作为所述模数转换电路4部分的正电源输入端;。

49.进一步的,所述模数转换电路4包括芯片u6、电阻r36、排阻rp1、排阻rp2、排阻rp3、电容c64、电容c65、电阻r41、电阻r42、芯片u7、电阻r35、电阻r38、电阻r37、电阻r39、电阻r40、电阻r43、电阻r44、电阻r47、电容c27、电阻r45、电阻r46、电容c68、电容c69、电容c70、电容c73、电容c74、电容c75、电容c77和电容c78;

50.所述电阻r36一端和所述芯片u6的clk端连接;所述排阻rp1一端分别与所述芯片u6的d8端、d9端、d10端、d11端连接;所述排阻rp2一端分别与所述芯片u6的d4端、d5端、d6端、d7端连接;所述排阻rp3一端分别与所述芯片u6的d0端、d1端、d2端、d3端连接;所述电容

c64一端和所述芯片u6的drvdd端连接,另一端接地;所述电容c65一端和所述芯片u6的avdd1端连接,另一端接地;所述电阻r41一端和所述芯片u6的vinb端连接;所述电阻r一端和所述芯片u6的vina端连接;所述芯片u7的 out端和所述电阻r42连接,-out端和所述电阻r41连接;所述电阻r35一端和所述电阻r41连接,另一端和所述芯片u7的 in端连接;所述电阻r38一端和所述电阻r35连接;所述电阻r37一端和所述电阻r38连接,另一端接地;所述电阻r39一端和所述电阻r38连接;所述电阻r40一端和所述电阻r39连接,另一端和所述电容c11连接;所述电阻r43一端和所述电阻r40连接,另一端接地;所述电阻r44一端和所述电阻r40连接,另一端接地;所述电阻r47一端和所述电阻r42连接,另一端和所述芯片u7的-in端连接;所述电容c27一端和所述芯片u7的v 端连接,另一端接地;所述电阻r一端和所述电阻r47连接;所述电阻r46一端和所述电阻r45连接,另一端接地;所述电容c68一端和所述芯片u6的cpat端连接,另一端接地;所述电容c69一端和所述芯片u6的cpat端连接,另一端和所述电容c73连接;所述电容c70一端和所述芯片u6的cpat端连接,另一端和所述电容c73连接;所述电容c73一端和所述电容c70、所述电容c69连接,另一端接地;所述电容c74一端和所述芯片u6的avdd2端连接,另一端接地;所述电容c75一端和所述芯片u6的vref端连接,另一端接地;所述电容c77一端和所述芯片u6的vref端连接,另一端接地;所述电容c78一端和所述芯片u6的vref端连接,另一端接地。

51.在本实施方式中,理论上,采样速率需要符合奈奎斯特定理才能保证采样之后的数字信号可以完整的保留原来的模拟信号的信息,但是实际采用过程,由于外部噪声的干扰,采样速率至少要到信号最高频率的4到5倍才能保证信号不失真,因此所述芯片u6选用ad公司的ad9226,需要 3.3v作为电源电压,功耗为475mw,采样率65msp,精度为12bit,ad9226的为差分输入,因此从放大的模拟信号到数模转换之前还需要通过ad8138进行单端转差分,得到差分信号作为ad9226的输入;要驱动ad9226,要提供一个65mhz的同步时钟,针对高采样率和高速数据处理能力的要求,所述fpga主控电路5采用altera公司的ep4ce10e22c8n作为主控芯片,具有低成本低功耗的特点,具有10320个逻辑单元、414kb的ram、645逻辑块以及144个引脚,可以实现单口和双口ram和异步fifo。ep4ce10e22c8n需要完成的任务包括:控制ad9226完成数字化处理,通过控制多个fifo与外部sram芯片完成输出传输和存储,以及控制串口输出存储的数据;fpga主控芯片的控制代码断电或者复位后,运行的代码是失效,因此需要flash芯片做代码的持久化。

52.进一步的,所述第三稳压电路7包括芯片u2、电感l1、电阻r21、电容c54、电阻r132、电容c18、电容c19、电感l3、电阻r26、电容c71、电阻r24、电容c67、电容c5、电感l2、电阻r10、电容c202、电阻r6、电容c57、电容c58、电阻r5、电容c20、电容c4、电容c21、电容c66、电容c24、电容c76、电容c72、电容c201、电阻r1、电阻r2、电阻r3和电阻r7;

53.所述电感l1一端和所述芯片u2的lx1端连接;所述电阻r21一端和所述芯片u2的fb1端连接,另一端接地;所述电容c54一端和所述电感l1连接,另一端和所述芯片u2的fb1端连接;所述电阻r132一端和所述电容c54连接,另一端和所述芯片u2的fb1端连接;所述电容c18一端和所述电感l1连接,另一端接地;所述电容c19一端和所述电感l1连接,另一端接地;所述电感l3一端和所述芯片u2的lx3端连接;所述电阻r26一端和所述芯片u2的fb3端连接,另一端接地;所述电容c71一端和所述电感l3连接,另一端和所述芯片u2的fb3端连接;所述电阻r24一端和所述电容c71连接,另一端和所述芯片u2的fb3端连接;所述电容c67一

端和所述电感l3连接,另一端接地;所述电容c5一端和所述电感l3连接,另一端接地;所述电感l2一端和所述芯片u2的lx4端连接;所述电阻r10一端和所述芯片u2的fb4端连接,另一端接地;所述电容c202一端和所述电感l2连接,另一端和所述芯片u2的fb4端连接;所述电阻r6一端和所述电容c202连接,另一端和所述芯片u2的fb4端连接;所述电容c57一端和所述电感l2连接,另一端接地;所述电容c58一端和所述电感l2连接,另一端接地;所述电阻r5一端和所述芯片u2的fb2端连接,另一端接地;所述电容c20一端和所述芯片u2的vin1端连接,另一端接地;所述电容c4一端和所述电容c20连接,另一端和所述芯片u2的vcc端连接;所述电容c21一端和所述芯片u2的vin1端连接,另一端接地;所述电容c66一端和所述电容c21连接,另一端和所述芯片u2的vcc端连接;所述电容c24一端和所述芯片u2的vin1端连接,另一端接地;所述电容c76一端和所述电容c24连接,另一端和所述芯片u2的vcc端连接;所述电容c72一端和所述芯片u2的vin1端连接,另一端接地;所述电容c201一端和所述电容c72连接,另一端和所述芯片u2的vcc端连接;所述电阻r1一端和所述芯片u2的en1端连接;所述电阻r2一端和所述芯片u2的en2端连接;所述电阻r3一端和所述芯片u2的en3端连接;所述电阻r7一端和所述芯片u2的en4端连接。

54.在本实施方式中,所述第三稳压电路7为所述fpga主控电路5提供稳压电源,以所述芯片usb2,即typc-c为输入源,所述fpga主控电路5需要三种电压的作为电源输入,分别是1.2v,2.5v,3.3v,所述芯片u2选取ea3059,最多支持4种电压的转换输出。

55.进一步的,所述串口输出电路6包括芯片ic2、电容c1和电容c3;

56.所述芯片ic2的ud 端和所述芯片usb2的dp2端连接,所述芯片ic2的ud-端和所述芯片usb2的dn2端连接;所述电容c1一端和所述芯片ic2的vcc端连接,另一端接地;所述电容c3一端和所述芯片ic2的vcc端连接,另一端接地。

57.在本实施方式中,所述串口输出电路6采用所述芯片usb2的typc-c口作为数字电路部分的电源输入口,同时也兼顾据传输的功能,使用所述芯片ic2采用ch340g芯片实现usb转串口。

58.本发明的一种微型穿戴式光声信号采集系统,超声探头的超声脉冲信号经过放大器放大后,经过所述模数转换电路4转换为12位的数字信号,所述fpga主控电路5每次提供一个65mhz的时钟上升沿,所述模数转换电路4(ad)进行一次数据转化,得到一次信号,持续提供65mhz的时钟就可以持续对放大的模拟信号进行模数转化,区别于普通的信号采集,光声信号的产生需要激光器的驱动,激光器工作则产生光声信号,因此进行模数转换时,激光器的触发时钟需与采集系统的时钟做同步,相当于一个外部时钟作为本采集系统的一个时钟触发源。fpga控制外部sdram进行数据交互时,sdram与fpga的数据传输速度存在较大的速度差异,也需要时钟的同步。此外,由于fpga直接控制sdram数据从串口输出,串口传输速率与sdram数据传输速率也相差较大;总而言之,fpga需要针对激光器触发时钟,模数转换时钟,sdram传输速率,串口传输,做时钟同步和数据同步方案;针对于上述需求,本发明采用一种多计数器 双fifo的解决方案,整个控制状态分为8个状态,分别为idle(初态)、delay(延时态)、write(写入态)、wait(等待态)、read(读取态)、wait_uart(等待串口态)、rd_done_512(读取512个点)和stop(终止态),因为ad采集的时钟频率为65mhz,因此为方便操作,fpga的运行时钟为65mhz。使用altera公司自带的pll锁相环ip核,将板载50mhz通过一定的倍频分频,产生两路时钟,一个是整个fpga以及ad的运行时钟65mhz,一个是sdram的

运行时钟100mhz;下面展开说明每一个状态的逻辑和转移逻辑。

59.idle态:初始态,就是整个采集系统上电之后的初始状态,在stop之后会自动恢复到初始状态。当复位信号触发时,采集系统会重置进入idle态。

60.delay态:捕捉到触发信号上升沿后,进入delay状态。一通道信号(图中的黄色线)为示波器采集到的光声信号,刚触发时,光声信号脉冲会有一个较大的脉冲信号,这个信号并非真正的由目标产生的信号,而是又探头激励产生的幅值较大的脉冲。考虑到采集深度的问题,当捕捉到触发电平时,先延时一段时间,ad不工作,等过一定的时间之后ad进行工作采集,就能采集到后面的信号了,而具体的实现,就是进入delay态时,开启一个计数器用于计算延迟的时钟数,满足300个时钟后进入下一状态write态。

61.write态:sdram的时钟为100mhz,读写相对于fpga运行时钟而言较快,因此sdram的读写都需要fifo支持。需要两个fifo,一个写fifo,一个读fifo。即用65mhz时钟的速率写入到写fifo中,然后sdram用100mhz的时钟从写fifo读出数据写入到sdram中。同理,需要从sdram读取数据时,先读到读fifo中,再从读fifo中读出数据,而sdram芯片支持并发读模式,可以从一次性从fifo读入大量数据到sdram中,利用这一特性设计了write状态。在delay之后,在write状态中开始进行数据采集并写入到fifo中,采集完512个点,即对应了一次外部触发,这512个点的数据通过数据并发写从fifo写入到sdram中,并且回到idle态,等待下一次外部触发的来临。sdram不是无限存储的,有一定的容量限制,例如限制100组512个点存完之后,sdram会返回一个sdram_wr_done的信号,标志着sdram不再接受写入数据,采集系统从write进入wait状态。

62.wait态:wait态就是等待态,等待按键的输入,这里是指,当存完一定组数的数据之后,采集系统不再接受新的数据写入。而如果要写入新的数据,必需把sdram写入的数据读取出来,才能继续采集新数据,写入新数据。这时候需要一个按键进行状态的切换,捕捉到某个按键的输入,采集系统从wait状态转换到read状态。

63.read态:read这个状态,是读状态,主要是把sdram的数据读取出来。前文提过,由于sdram的读写时钟与fpga的运行时钟频率不同,要用到读fifo。在读fifo类似并发写的逻辑,设置一定深度的限制,例如512深度,fifo不足512时自动从sdram里面读数据到fifo。而read这个状态就是为了使读fifo的读使能端置1。然后进入wait_uart的状态。

64.wait_uart态:这个状态是等待uart串口发送完毕的状态,这个状态解决了两个问题,一是数据位数不一致的问题,二是uart传输速率过慢的问题。ad采集的数据位数是12位,sdram的数据位宽是16位,不够的补0处理,而uart则是一次发送8位数据,就意味着一次读取数据要串口发送两次数据,一次高8位,一次低8位,uart每次发送完一次数据,都返回一个tx_done的信号。因此,这里设置了一个寄存器通过0和1判断是高8位还是低8位,当读完高低8位之后再回到read状态继续从读fifo读取数据。为满足512个点数据对齐需要,读完512个16位数据之后,进入rd_done_512态。

65.rd_done_512态:这个状态标志着读取完512个数据,意味着一组数据读完,此时给uart发送一个全1的数据即0xff,接受到从uart发送的tx_done之后,判断sdram的数据是否完全读空,若读空了则进入stop,若仍未读空,则进入read状态继续读取fifo的数据。

66.stop态:进入stop态后采集系统结束工作,直到有重置信号触发再次进入idle状态。

67.整体的采集逻辑如下:首先激光器的触发信号作为采集的触发标志,每次触发,采集512个信号写入到sdram中,采集一定数量的512点后等待按键触发数据输出。数据输出时,每次读取一次数据,uart输出两次,读完512次数据标志着一组,输出一组的数据的结束标志,然后继续读数据输出直至sdram的数据读空,读空sdram之后进入stop待机状态。

68.经测试,采集普通波形、超声波形、黑胶布产生的光声信号以及铅笔芯产生的光声信号均不失真,以下是本采集系统跟tektronix泰克dpo3012数字示波器的采集波形对比:1、(参考图8)函数发生器提供burst信号,一次触发有内有20个周期的正弦信号,vpp为3.3v,正弦信号频率为1mhz。2、(参考图9)函数发生器提供burst信号,一次触发有内有20个周期的方波信号,vpp为3.3v,正弦信号频率为2mhz,信号频率幅值均与函数发生器提供的相同。3、(参考图10、图11)测试采集信噪比较高的超声信号,采用olympus公司的型号为5073r的超声波脉冲发生器作为发射端,olympus的v311探头作为超声探头接收超声信号,下面给出采集系统采集的信号与dpo3012数字示波器采集的波形对比。采集系统是延迟300个时钟之后进行采集的,因此对应的是数字示波器的第二个脉冲,信号不失真,基本相似。4、(参考图12-15)测试光声信号的波形对比;激光脉冲照射黑胶布,olympus的v311探头作为超声探头接收超声信号,经对照可知,虽然看着波形和杂乱,但其实是幅值较小的噪声,并非采集的信号。

69.经上述验证,可以看出信号波形基本相同,通过普通信号,超声脉冲器的的信号,以及黑胶布的光声信号验证,本采集系统可以不失真的采集到微小电信号,能达到有益效果。本发明的一种微型穿戴式光声信号采集系统电路设计紧凑,可以微型化,功耗低,可实现穿戴化,性能稳定。

70.以上所揭露的仅为本发明一种较佳实施例而已,当然不能以此来限定本发明之权利范围,本领域普通技术人员可以理解实现上述实施例的全部或部分流程,并依本发明权利要求所作的等同变化,仍属于发明所涵盖的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。