1.根据本发明的实施方案的一个或多个方面涉及一种光调制器,并且更具体地涉及一种mos电容器型光调制器。

背景技术:

2.硅mos电容器型调制器可能具有高损耗。iii-v si mos电容器型调制器是更高效但可能不太适合大批量制造的混合结构。

3.可通过在硅晶片上粘结iii-v材料片来制造iii-v si mos电容器型调制器。除了不适合大批量制造外,粘结制造过程还会限制调制器的可能的几何配置。

4.一些iii-v si mos电容器型调制器使用专门的过渡层,诸如外延生长的晶体稀土氧化物(reo)。尽管这些调制器是单片式的并且因此不适合大批量制造,但是制作调制器所需的制造步骤很复杂。此外,该过程要求si(111)器件层定向,这与诸如si(100)器件层的其他si器件层相比不太理想。具体地,si(111)不如si(100)常见且更昂贵,并且一些蚀刻技术无法在si(111)上重复。

技术实现要素:

5.本发明的实施方案旨在通过根据第一方面提供一种mos电容器型光调制器来解决上述问题,所述mos电容器型光调制器包括:绝缘体上硅soi衬底;第一掺杂区,所述第一掺杂区在所述soi衬底的硅器件层中;以及第二掺杂区,所述第二掺杂区与所述第一掺杂区由竖直地延伸的绝缘体层横向地分离以形成横向mos电容器区,其中所述第一掺杂区、所述第二掺杂区和所述绝缘体层由不同的材料形成。

6.以此方式,调制器是单片的,而不要求soi衬底的硅器件层具有si(111)器件层定向。此外,不要求专门的过渡层,诸如晶体reo层。

7.光调制器可具有下面阐述的任选特征中的任一者或任何组合(只要它们相容)。

8.soi衬底可包括硅基部、在硅基部的顶部上的掩埋氧化物(box)层,以及在box层的顶部上的硅器件层(即,顶部硅层)。

9.如本文所使用,术语“竖直地”和“水平地”应当理解为相对于box层而言,使得“竖直地”是垂直于box层的上表面,并且“水平地”涉及位于与沿着box层的上表面的平面平行的任何平面内的方向。如本文所使用,横向可被理解为意指沿着水平平面。

10.如本文所使用,横向mos电容器区可以是器件的光模传播的区,并且由p-i-n结形成,其中p-i-n结包括第一掺杂区、绝缘体层和第二掺杂区。绝缘体层可竖直地延伸,从而横向地分离第一掺杂区和第二掺杂区,使得横向mos电容器区的p-i-n结垂直于box层延伸。绝缘体层可相对于衬底以倾斜角度延伸,以便将第二掺杂区与第一掺杂区横向地分离。例如,绝缘体层可以大于0

°

且小于90

°

的角度延伸。

11.第一掺杂区可包含与第二掺杂区不同种类的掺杂剂。具体地,第一掺杂区可具有与第二掺杂区相反的掺杂类型。例如,第一掺杂区可以是p掺杂区并且第二掺杂区可以是n掺杂区。替代地,第一掺杂区可以是n掺杂区并且第二掺杂区可以是p掺杂区。

12.第二掺杂区可形成在半导体区中,并且更特别地在iii-v型半导体区、ii-vi型半导体区或iv型半导体区中。半导体区可从soi衬底的硅器件层外延生长。

13.在一些实施方案中,半导体区可在硅器件层的从mos电容器区横向地偏移的区处从硅器件层延伸。

14.在半导体区是iii-v型半导体区的实施方案中,半导体区可以是inp、gaas、ingaas或ingaasp半导体区。

15.绝缘体层可包括氮化硅。

16.soi衬底的硅器件层可具有(100)晶体定向。

17.任选地,绝缘体层的一部分可在硅器件层的第一掺杂区的顶部上水平地延伸。绝缘体层的另一部分可在半导体区的第二掺杂区的下方水平地延伸。因此,绝缘体层可形成“z”形状,其中绝缘体层的“z”形状的竖直地延伸的部分在第一掺杂区和第二掺杂区之间形成mos电容器区的p-i-n结的绝缘体。

18.在一些实施方案中,硅器件层的一部分可背离box层竖直地延伸。具体地,硅器件层中的第一掺杂区可背离box层竖直地延伸。半导体区的一部分也可竖直地延伸。具体地,半导体区的第二掺杂区可竖直地延伸。因此,竖直地延伸的绝缘体层可横向地分离竖直地延伸的第一掺杂区和竖直地延伸的第二掺杂区。

19.在一些实施方案中,半导体区的上部水平部分可在绝缘体层的水平地延伸的部分的上方水平地延伸,该水平地延伸的部分本身在硅器件层的第一掺杂区的上方水平地延伸。因此,半导体区可形成“z”形状,使得“z”形绝缘体区段的竖直部分和上部水平部分两者在第一掺杂区和第二掺杂区之间形成mos电容器区的p-i-n结的绝缘体。在这些实施方案中,p-i-n结与box层垂直地且平行地延伸。

20.mos电容器型光调制器的结构可通过截面成像(诸如fib或sem)来识别。

21.根据本发明的第二方面的实施方案,提供了一种制造第一方面的mos电容器型光调制器的方法。

22.具体地,根据第二方面,提供了一种制造mos电容器型光调制器的方法,所述mos电容器型光调制器具有横向mos电容器区,所述横向mos电容器区包括将第一掺杂区和第二掺杂区横向地分离的竖直地延伸的绝缘体层,其中所述方法包括以下步骤:在绝缘体上硅soi衬底的硅器件层中提供第一掺杂区;以及使半导体区从所述soi衬底的所述硅器件层外延生长,其中所述半导体区包括所述第二掺杂区,并且所述第一掺杂区、所述第二掺杂区和所述绝缘体层各自由不同的材料形成。

23.该方法可具有下面阐述的任选特征中的任一者或任何组合(只要它们相容)。

24.在一些实施方案中,半导体区可从硅器件层的与mos电容器区横向地偏移的区外延生长。

25.以此方式,半导体区从硅器件层的背离mos电容器区的区生长。因此,生长的半导体区中的任何缺陷被限制于与硅器件的从中发起半导体区的生长的区紧密接近的区。因

此,半导体区中的任何缺陷被定位成背离mos电容器区,使得它们对调制器的性能的影响减小。此外,在一些实施方案中,可选择性地蚀刻半导体区的与硅器件层的使半导体区从中外延生长的区相邻的区,而无需移除mos电容器区中的半导体区的区,使得整个半导体区具有高晶体质量。

26.在一些实施方案中,半导体区是iii-v型半导体区。在其他实施方案中,半导体区可以是inp、gaas、ingaas或ingaasp半导体区。然而,在其他实施方案中,半导体区可以是ii-vi型半导体区或iv型半导体区。

27.在一些实施方案中,绝缘体层可包括介电材料,例如,诸如氮化硅。

28.任选地,soi衬底的硅器件层具有(100)晶体定向。

29.在一些实施方只中,该方法还可包括以下步骤:在上掩模层的下方形成腔;以及在该腔中使半导体区从soi衬底的硅器件层外延生长。

30.以此方式,半导体区的生长可被上掩模层容纳在腔中,使得得到的调制器是单片的而不要求专门的过渡层,诸如晶体reo。 因此,soi衬底的硅器件层(即,顶部硅层)不要求si(111)器件层定向,并且实现器件设计方面的更大灵活性。

31.通过在上掩模层的下方形成腔,在上掩模层和soi衬底的硅器件层之间形成腔。

32.任选地,上掩模层可包括介电材料。例如,上掩模层可包括氮化硅。

33.任选地,形成腔的步骤可包括:提供牺牲层;将上掩模层沉积在牺牲层的顶部上;以及选择性地蚀刻牺牲层以形成腔。

34.例如,可通过沉积牺牲层来提供牺牲层。

35.因此,牺牲层用于形成腔的形状,由此在从上掩模层的下方选择性地蚀刻牺牲层以形成腔之前,将上掩模层层叠在牺牲层的上方。通过选择性地蚀刻牺牲层,去除牺牲层但保留上掩模层,从而在上掩模层的下方形成腔。

36.该方法还可包括以下步骤:在soi衬底的硅器件层中蚀刻沟槽;将下掩模层沉积在硅器件层的顶部上且在沟槽中;在下掩模层中蚀刻在硅器件层的从mos电容器区横向地偏移的区处到达硅器件层的开口;以及将牺牲层沉积在下掩模层上且在下掩模层中的开口中。

37.在一些实施方案中,下掩模层可由与上掩模层相同的材料形成。因此,下掩模层可包括介电材料,诸如氮化硅。

38.上掩模层和下掩模层可共同限定腔。具体地,可在下掩模层的上方且在上掩模层的下方形成腔。

39.任选地,该方法还可包括以下步骤:在沉积上掩模层之前,蚀刻牺牲层的一部分以到达下掩模层。

40.因此,当将上掩模层沉积在牺牲层的顶部上时,上掩模层和下掩模层可包围牺牲层。因此,当从上掩模层和下掩模层之间选择性地蚀刻牺牲层时,上掩模层和下掩模层保

留,并且在上掩模层的下方形成腔。

41.根据一些实施方案,该方法还可包括以下步骤:通过化学机械平坦化(cmp)对牺牲层进行平坦化。

42.具体地,可在沉积上掩模层之前对牺牲层进行平坦化。因此,当将上掩模层沉积在牺牲层的顶部上时,上掩模层和下掩模层可包围牺牲层,使得当从上掩模层和下掩模层之间选择性地蚀刻牺牲层时,上掩模层和下掩模层保留,并且在上掩模层的下方形成腔。

43.任选地,牺牲层可包括氧化铝或非晶硅。

44.在一些实施方案中,该方法还可包括以下步骤:在选择性地蚀刻牺牲层以形成腔之前,在上掩模层中蚀刻到达牺牲层的开口。

45.任选地,该方法还可包括以下步骤:蚀刻半导体区的一部分以形成波导结构,该波导结构包括mos电容器区。

46.在该步骤中,还可蚀刻上掩模层和下掩模层的部分以及任选地硅器件层的一部分,以形成波导结构。波导结构可包括剩余的半导体区以及上掩模层和下掩模层的剩余部分。

47.上掩模层和下掩模层的剩余部分可形成mos电容器区的p-i-n结的绝缘体区,并且剩余的半导体区可形成第二掺杂区。

48.在一些实施方案中,蚀刻半导体区的一部分以形成波导结构的步骤包括在硅器件层的与mos电容器区横向地偏移的区处蚀刻半导体区的在下掩模层中的开口中和/或与该开口相邻的部分。由于半导体区中的任何缺陷被限制在半导体的这个区,因此可通过该蚀刻来去除缺陷而不会影响mos电容器区。因此,整个剩余的半导体区可具有高晶体质量。

49.该方法还可包括以下步骤:将隔离层沉积在波导结构上;穿过隔离层将第一电触点施加到硅器件层(即,第一掺杂区);以及穿过隔离层将第二电触点施加到半导体区(即,第二掺杂区)。

50.任选地,隔离层可以是隔离氧化物,诸如二氧化硅。可将电触点施加到硅器件层和半导体区的从mos电容器区横向地偏移的区。

51.任选地,该方法可包括以下步骤:通过cmp对半导体区进行平坦化。

52.根据本发明的第三方面的实施方案,提供了一种制造mos电容器型光调制器的方法,所述mos电容器型光调制器具有mos电容器区,所述mos电容器区包括半导体区,所述方法包括以下步骤:在上掩模层的下方形成腔;以及在所述腔中使所述半导体区从绝缘体上硅soi衬底的硅器件层外延生长。

53.应当注意,第三方面的方法不限于制造具有横向mos电容器区的mos电容器型光调制器,该横向mos电容器区具有竖直地延伸的绝缘体层。事实上,在第三方面的方法中,可使用干法蚀刻或选择性湿法蚀刻来有意地使腔蚀刻倾斜(即,不竖直或水平)。

54.以此方式,半导体区的生长可被上掩模层容纳在腔中,使得得到的调制器是单片的而不要求专门的过渡层,诸如晶体reo。 因此,soi衬底的硅器件层不要求si(111)器件层定向,并且实现器件设计方面的更大灵活性。

55.通过在上掩模层的下方形成腔,在上掩模层和soi衬底的硅器件层之间形成腔。

56.本公开包括上述方面和任选特征的组合,除非这种组合是明显不允许的或明确避免的。

附图说明

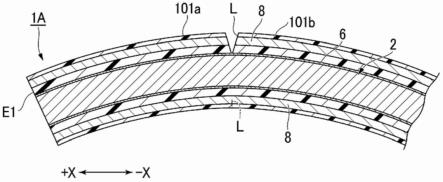

57.现在将参考附图通过示例的方式来描述本发明的实施方案,在附图中:图1是根据本发明的第一实施方案的mos电容器型光调制器的示意性截面;图2是根据本发明的第二实施方案的mos电容器型光调制器的示意性截面;图3a至图3l描绘了制造图1的调制器的方法的步骤;图4a至图4l描绘了制造图2的调制器的方法的步骤;并且图5a至图5g描绘了制造图2的调制器的变体方法的步骤。

具体实施方式

58.下面结合附图阐明的详细描述意图作为根据本发明提供的mos电容器型光调制器及其制造方法的示例性实施方案的描述,而不意图表示其中可构建或利用本发明的唯一形式。该描述结合所示的实施方案阐明本发明的特征。然而,应当理解,相同或等效的功能和结构可由也意图涵盖在本发明的精神和范围内的不同实施方案实现。如本文中其他地方指示,相似的元件编号意图指示相似的元件或特征。

59.下面参考图1和图3a至图3l描述根据第一实施方案的mos电容器型光调制器1及其制造方法。调制器1包括soi衬底20。

60.如图3a所示,最初提供绝缘体上硅衬底20,所述绝缘体上硅衬底包括硅基层23、掩埋二氧化硅(box)层22和硅器件层21。硅器件层21具有si(100)晶体结构。在硅器件层21中蚀刻到达box层22的沟槽24。使用标准图案化和蚀刻技术来蚀刻该沟槽。尽管图3a中未示出,但是在第一硅器件层21中使用标准注入技术来形成第一掺杂区。

61.接下来,如图3b所示,将包括氮化硅的下掩模层25沉积在硅器件层21的顶部上并且沉积在沟槽24中。

62.然后在下掩模层25中蚀刻到达硅器件层21的开口26 (例如,参见图3c)。同样,使用标准图案化和蚀刻技术来蚀刻开口26。该开口26提供暴露硅的点,iii-v型半导体层稍后将从该点生长。在下掩模层25中的将从具有调制器1的p-i-n结的mos电容器区横向地偏移的区中蚀刻开口26。

63.如图3d所示,然后将牺牲层27沉积在下掩模层25的顶部上和开口26中。例如,牺牲层27可包括氧化铝或非晶硅。

64.接下来,蚀刻牺牲层27的一部分到达下掩模层25。具体地,如图3e所示,蚀刻牺牲层27的每一侧的一部分以显露下面的下掩模层25。此外,蚀刻定位在下掩模层25中的开口26中的牺牲层27的一部分以显露硅器件层21的一部分。在替代实施方案中,不蚀刻定位在下掩模层25中的开口26中的牺牲层27的该部分,使得牺牲层27延伸跨过开口26并且不暴露硅器件层21。同样,使用标准图案化和蚀刻技术。

65.如图3f所示,然后将上掩模层28沉积在牺牲层27的顶部上并且沉积在开口26中。因此,上掩模层28和下掩模层25包围牺牲层27。

66.接下来,在上掩模层28中蚀刻到达牺牲层27的开口29 (例如,参见图3g)。同样,使

用标准图案化和蚀刻技术。

67.然后选择性地蚀刻牺牲层27,同时维持上掩模层28和下掩模层25。因此,在上掩模层28和下掩模层25之间、在上掩模层28下方且在下掩模层25上方形成腔30 (例如,参见图3h)。腔30在下掩模层25中的开口26处从硅器件层21在上掩模层28和下掩模层25之间延伸到上掩模层28中的开口29。

68.如图3i所示,然后在腔30中使iii-v型半导体区31在下掩模层25中的开口26处从暴露的硅器件层21外延生长。使用标准外延生长技术。iii-v型半导体区31生长以填充腔30的形状并且因此被上掩模层28和下掩模层25限制。在该示例实施方案中,iii-v型半导体区31是inp、gaas、ingaas或ingaasp,但是也可使用其他iii-v型材料。

69.通过使用标准掺杂技术在原位掺杂来形成iii-v型半导体区31的第二掺杂区。在替代实施方案中,可使用标准注入和/或扩散技术来形成iii-v型半导体区31的第二掺杂区。如果第一掺杂区是n掺杂的,则第二掺杂区是p掺杂的,反之亦然。

70.接下来,通过蚀刻不需要的iii-v型半导体区31的一部分、上掩模层28和下掩模层25的一部分来形成波导结构32。波导结构32包括具有p-i-n结的mos电容器区。同样,使用标准蚀刻技术。如图3j所示,在该步骤中,蚀刻iii-v型半导体区31的在开口26处与硅器件层21相邻的部分。因此,去除了ii-v型半导体区31中的任何缺陷。

71.然后将隔离层33沉积在波导结构32的顶部上。在图3k所示的示例实施方案中,隔离层33是隔离氧化物,诸如二氧化硅。

72.最后,在分别到达硅器件层21和iii-v型半导体区31的两个开口处蚀刻隔离层33,并且穿过隔离层33沉积电触点34 (例如,参见图3l)。将电触点34施加到硅器件层21和iii-v型半导体区31的从波导结构32的mos电容器区横向地偏移的区。 下掩模层25的剩余部分形成mos电容器区中的p-i-n结的绝缘体层。

73.在图1中示出得到的调制器1。soi衬底20的硅器件层21与box层22平行且邻接地水平地延伸。绝缘体层25 (由下掩模层形成)具有由第一上部水平地延伸的部分25a、第二竖直地延伸的部分25b和第三下部水平地延伸的部分25c形成的“z”形状。有利地,该“z”形状增加了电荷可积累的表面区域。这对应地增加了调制效率,而不会影响光模的大小。

74.绝缘体层25的第一水平地延伸的部分25a在硅器件层21上方且与该硅器件层邻接地延伸,并且特别是在硅器件层21的第一掺杂区上方延伸。绝缘体层25的第二竖直地延伸的部分25b背离box层22竖直地延伸到绝缘体层25的第一上部水平地延伸的部分25a。因此,绝缘体层25与硅器件层21并且特别是硅器件层21的第一掺杂区形成竖直结(即,在第二竖直地延伸的部分25b处)和水平结(即在第一上部水平地延伸的部分25a处)两者。在未示出的变型中,绝缘体层25倾斜地延伸跨过波导结构32。例如,绝缘体层25可以大于0

°

且小于90

°

的角度延伸。与图1所示的“z”形绝缘体层相比,这种延伸可能是线性的一。

75.绝缘体层25的第三下部水平地延伸的部分25c从绝缘体层25的第二竖直地延伸的部分25b的下端在box层22的顶部上且与该box层邻接地水平地延伸。

76.类似于绝缘体层25,iii-v型半导体区31也具有由第一上部水平地延伸的部分31a、第二竖直地延伸的部分31b和第三水平地延伸的部分31c形成的“z”形状。

77.iii-v型半导体区31的第一上部水平地延伸的部分31a在绝缘体层25的第一上部水平地延伸的部分25a的顶部上且与该第一上部水平地延伸的部分邻接地延伸。iii-v型半

导体区31的第三下部水平地延伸的部分31c在绝缘体层25的第三下部水平地延伸的部分25c的顶部上且与该第三下部水平地延伸的部分邻接地延伸。iii-v型半导体区31的第二竖直地延伸的部分31b在iii-v型半导体区31的第一上部水平地延伸的部分31a与第三下部水平地延伸的部分31c之间竖直地延伸。

78.因此,硅器件层21的第一掺杂区与iii-v型半导体区31的第二竖直地延伸的部分31b由绝缘体层25的第二竖直地延伸的部分25b横向地(即,水平地)间隔开。这形成横向mos电容器区。

79.硅器件层21的第一掺杂区还与iii-v型半导体区31的第一上部水平地延伸的部分31a由绝缘体层25的第一上部水平地延伸的部分25a竖直地间隔开。因此,调制器1具有与box层垂直地且平行地延伸的p-i-n结。

80.在图1所示的示例实施方案中,绝缘体层25、硅器件层21的第一掺杂区和iii-v型半导体区31的第二掺杂区由不同的材料形成。具体地,绝缘体层25包括氮化硅,硅器件层21具有si(100)结晶定向,并且iii-v型半导体区31包括inp或ingaasp。

81.下面参考图2、图4a至图4l和图5a至图5g描述根据第二实施方案的mos电容器型光调制器100及其制造方法。调制器100包括soi衬底120。

82.根据制造mos电容器型光调制器的第一方法,并且如图4a所示,最初提供绝缘体上硅衬底120,所述绝缘体上硅衬底包括硅基层123、掩埋二氧化硅(box)层122和硅器件层121。硅器件层121具有si(100)晶体结构。在硅器件层121中蚀刻到达box层122的沟槽124。使用标准图案化和蚀刻技术来蚀刻该沟槽。尽管图4a中未示出,但是在第一硅器件层121内使用标准注入技术来形成第一掺杂区。

83.接下来,如图4b所示(并且类似于参考第一实施方案在图3b中示出的步骤),将包括氮化硅的下掩模层125沉积在硅器件层121的顶部上并且沉积在沟槽124中。

84.然后在下掩模层125中蚀刻开口126。然而,与第一实施方案中的对应步骤相比,下掩模层125中的开口126在沟槽124中延伸到硅器件层121和box层122。同样,使用标准图案化和蚀刻技术来蚀刻开口126。该开口126提供暴露硅的点,iii-v型层随后将从该点生长。在下掩模层125中的将从具有调制器100的p-i-n结的mos电容器区横向地偏移的区中蚀刻开口126。

85.如图4d所示,然后将牺牲层127沉积在下掩模层125的顶部上、在沟槽124中并且在开口126中。牺牲层127可包括氧化铝或非晶硅。

86.接下来,通过化学机械平坦化(cmp)对牺牲层127进行平坦化,使得牺牲层127仅存在于沟槽124中(例如,参见图4e)。因此,使沟槽124中的牺牲层127与下掩模层125齐平。

87.如图4f所示,然后将上掩模层128沉积在牺牲层127的顶部上,使得上掩模层128和下掩模层125包围牺牲层127。

88.类似于参考第一实施方案在图3g中示出的步骤,在上掩模层128中蚀刻到达牺牲层127的开口129。同样,使用标准图案化和蚀刻技术。

89.然后选择性地蚀刻牺牲层127,同时维持上掩模层128和下掩模层125。因此,在上掩模层128和下掩模层125之间在沟槽124中形成腔130。腔130在上掩模层128的下方形成。

90.如图4i所示,然后在腔130中使iii-v型半导体区131在下掩模层125中的开口126处从暴露的硅器件层121外延生长。使用标准外延生长技术。iii-v型半导体区131生长以填

充腔130的形状并且因此被上掩模层128和下掩模层125限制。在该示例实施方案中,iii-v型半导体区131是inp或ingaasp。通过使用标准掺杂技术在原位掺杂来形成iii-v型半导体区131的第二掺杂区。如果第一掺杂区是n掺杂的,则第二掺杂区是p掺杂的,反之亦然。

91.接下来,通过蚀刻不需要的iii-v型半导体区131的一部分、上掩模层128和下掩模层125的一部分来形成波导结构132。波导结构132包括具有p-i-n结的mos电容器区。使用标准蚀刻技术。将iii-v型半导体区131的在开口126处与硅器件层121相邻的部分定位成背离mos电容器区的p-i-n结。因此,iii-v型半导体区131中的任何缺陷定位成背离p-i-n结,并且因此对mos电容器区的影响减少。

92.类似于参考第一实施方案在图3k中示出的步骤,然后将隔离层133沉积在波导结构132的顶部上。在图4k所示的示例实施方案中,隔离层133是隔离氧化物,诸如二氧化硅。

93.最后,在分别到达硅器件层121和iii-v型半导体区131的两个开口处蚀刻隔离层133,并且穿过隔离层133沉积电触点134 (例如,参见图4l)。将电触点134施加到硅器件层121和iii-v型半导体区131的从波导结构132的mos电容器区横向地偏移的区。下掩模层125的剩余部分形成mos电容器区中的p-i-n结的绝缘体层。

94.在图2中示出得到的调制器100。类似于图1所示的第一实施方案,调制器2的绝缘体层125 (由下掩模层形成)具有由第一上部水平地延伸的部分125a、第二竖直地延伸的部分125b和第三下部水平地延伸的部分125c形成的“z”形状。

95.不同于图1所示的第一实施方案,图2所示的soi衬底120的硅器件层121包括第一水平地延伸的部分121a和第二竖直地延伸的部分121b。第一水平地延伸的部分121与box层122平行且在该box层的顶部上延伸,并且第二竖直地延伸的部分121b背离box层122竖直地延伸。

96.绝缘体层125的第一水平地延伸的部分125a在硅器件层121的竖直地延伸的部分121b上方水平地延伸。绝缘体层125的第二竖直地延伸层125b竖直地且与硅器件层121的竖直地延伸的部分121b邻接地延伸。绝缘体层125的第三下部水平地延伸的部分125c从绝缘体层125的第二竖直地延伸的部分125b的下端在box层122的顶部上水平地延伸。

97.不同于图1所示的第一实施方案,iii-v型半导体区131不具有“z”形状。相反,iiiv型半导体区131包括第一竖直地延伸的部分131a、第二水平地延伸的部分131b和第三竖直地延伸的部分131c。iii-v型半导体区131a的第一竖直地延伸的部分131a竖直地且与绝缘体层125的竖直地延伸的部分125b邻接地延伸。因此,绝缘体层125的第二竖直地延伸的部分125b横向地(即,水平地)隔开硅器件层121的第二竖直地延伸的部分121b和iii-v型半导体区131的第一竖直地延伸的部分131a。在硅器件层121的第二竖直地延伸的部分121b中形成第一掺杂区,并且在iii-v型半导体区131的第一竖直地延伸的部分131a中形成第二掺杂区,以形成具有平行于box层延伸的p-i-n结的横向mos电容器区。

98.在图2所示的示例实施方案中,绝缘体层125、硅器件层121的第一掺杂区和iii-v型半导体区131的第二掺杂区由不同的材料形成。具体地,绝缘体层125包括氮化硅,硅器件层具有si(100)结晶定向,并且iii-v型半导体区131包括inp、gaas、ingaas或ingaasp。

99.下面参考图5a至图5g描述图2所示的mos电容器型光调制器100的替代制造方法。

100.如图5a所示,最初提供绝缘体上硅衬底120,所述绝缘体上硅衬底包括硅基层123、掩埋二氧化硅(box)层122和硅器件层121。硅器件层121具有si(100)晶体结构。在硅器件层

121中蚀刻到达box层122的沟槽124。使用标准图案化和蚀刻技术来蚀刻该沟槽。尽管图5a中未示出,但是在第一硅器件层121内使用标准注入技术来形成第一掺杂区。

101.接下来,如图5b所示,将包括氮化硅的下掩模层125沉积在硅器件层121的顶部上并且沉积在沟槽124中。下掩模层125将形成mos电容器型光调制器100的绝缘体层125 (在图2中示出)。

102.然后在下掩模层125中蚀刻开口126。类似于图4c所示的步骤,下掩模层125中的开口126在沟槽124中延伸到硅器件层121和box层122。同样,使用标准图案化和蚀刻技术来蚀刻开口126。该开口126提供暴露硅的点,iii-v型层随后将从该点生长。在下掩模层125中的将从具有调制器100的p-i-n结的mos电容器区横向地偏移的区中蚀刻开口126。

103.与图4d所示的其中沉积牺牲层的方法步骤相比,在图5d中,在开口126中使iii-v型半导体区131从暴露的硅器件层121选择性地且外延生长。iii-v型半导体区131从开口126向外生长以至少填充沟槽124。

104.然后,通过cmp对iii-v型半导体区131进行平坦化,使得半导体区131仅存在于沟槽124中(例如,参见图5e)。以此方式,使沟槽124中的半导体区131与下掩模层125齐平。

105.通过蚀刻不需要的iii-v型半导体区131的一部分、上掩模层125的一部分和硅器件层121的一部分来形成波导结构132。将隔离层133沉积在波导结构132的顶部上(图5f)。

106.最后,在分别到达硅器件层121和iii-v型半导体区131的两个开口处蚀刻隔离层133,并且穿过隔离层沉积电触点134 (图5g)。

107.尽管已经结合上述示例性实施方案描述了本发明,但在给出本公开时,许多等效修改和变化对于本领域技术人员将是显而易见的。 因此,上面阐明的本发明的示例性实施方案应被认为是说明性的,而不是限制性的。在不脱离本发明的精神和范围的情况下,可对所描述的实施方案进行各种变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。