1.本揭示内容是关于一种延迟电路及延迟方法。

背景技术:

2.延迟锁定回路电路常常包括于诸如记忆体系统的数字系统中,且用以对准多个数字信号的边缘。举例而言,延迟锁定回路电路可用以基于参考时脉信号来对准时脉信号的上升边缘及/或下降边缘以产生经同步化的输出时脉信号。

技术实现要素:

3.本揭示内容包含一种延迟电路。延迟电路包括相位侦测器、相位累加器电路、解码器及延迟元件。相位侦测器用以(i)接收第一时脉信号及第二时脉信号,及(ii)产生一数字信号,数字信号指示第一时脉信号的一相位与第二时脉信号的一相位之间的一关系。相位累加器电路用以接收数字信号并基于数字信号在多个时脉循环上的值而产生一相位信号。解码器用以接收相位信号,且基于相位信号产生一数字控制字元。延迟元件用以接收数字控制字元,且通过根据数字控制字元修改第二时脉信号的相位来改变第一时脉信号的相位与第二时脉信号的相位之间的关系。

4.本揭示内容包含一种延迟电路。延迟电路包括相位侦测器、数字控制区块及延迟元件。相位侦测器用以接收一第一时脉信号及一第二时脉信号,及产生一数字信号,该数字信号指示该第一时脉信号的一相位与该第二时脉信号的一相位之间的一关系。数字控制区块用以接收该数字信号,并基于该数字信号在多个时脉循环上的多个值而产生一数字控制字元。延迟元件用以(i)接收该数字控制字元,且用以(ii)通过根据该数字控制字元修改该第二时脉信号的该相位而改变该第一时脉信号的该相位与该第二时脉信号的该相位之间的该关系。

5.本揭示内容包含一种延迟方法,包含:接收一第一时脉信号及一第二时脉信号;产生一数字信号,该数字信号指示该第一时脉信号的一相位与该第二时脉信号的一相位之间的一关系;基于该数字信号在多个时脉循环上累加的多个值而产生一相位信号;基于该相位信号产生一数字控制字元;及通过根据该数字控制字元修改该第二时脉信号的该相位来改变该第一时脉信号的该相位与该第二时脉信号的该相位之间的该关系。

附图说明

6.本揭露的态样在与随附附图一起研读时自以下详细描述内容来最佳地理解。应注意,根据行业中的标准惯例,各种特征未按比例绘制。实际上,各种特征的尺寸可为了论述清楚经任意地增大或减小。

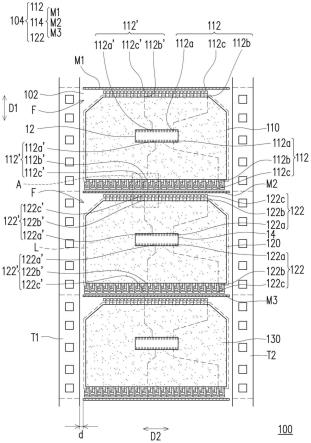

7.图1为根据一些实施例的延迟锁定回路(delay lock loop;dll)电路的方块图;

8.图2为根据一些实施例的绘示在相位电路与解码器之间交换的信号的方块图;

9.图3为根据一些实施例的描绘解码器的细节的方块图;

10.图4为根据一些实施例的描绘延迟元件的细节的方块图;

11.图5a为根据一些实施例的dll电路的实例实施的示意图;

12.图5b为根据一些实施例的通过目标延迟产生器使用的信号的时序图;

13.图5c为根据一些实施例的计时元件电路的实例实施的示意图;

14.图6描绘根据一些实施例的具有精细调谐部分及粗略调谐部分的解码器的细节;

15.图7a及图7b描绘根据一些实施例的锁定侦测器的细节;

16.图8描绘根据本揭露的一些实施例实施的dll电路的时序图;

17.图9描绘根据一些实施例的用以移位选通时脉的相位的时脉树的使用;

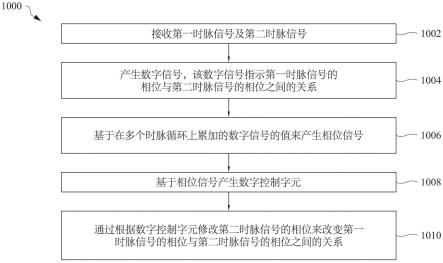

18.图10描绘根据一些实施例的实例方法的操作。

19.不同诸图中的对应数字及符号通常指对应部分,除非以其他方式指示。诸图经绘制以清楚地图示实施例的相关态样,且不必按比例绘制。

20.【符号说明】

21.100:相位电路

22.101:相位信号

23.102:数字控制字元

24.103:第二时脉信号/第二控制信号

25.104:数字信号

26.105:第一时脉信号

27.110:解码器

28.120:延迟元件

29.130:相位侦测器

30.200:相位电路

31.201:相位信号

32.203:重设累加器信号

33.204:模式切换信号

34.205:时脉信号

35.206:数字信号

36.207:时脉信号

37.210:脉冲产生器

38.220:模式切换元件

39.230:解码器

40.240:相位侦测器

41.300:相位电路

42.301:相位信号

43.302:模式切换信号

44.303:重设累加器信号

45.304:精细延迟控制字元

46.305:粗略延迟控制字元

47.310:脉冲产生器

48.315:模式切换元件

49.320:解码器

50.321:精细解码器部分

51.322:粗略解码器部分

52.323:粗略移动器

53.330:延迟元件

54.400:解码器

55.401:精细解码器部分

56.402:粗略解码器部分

57.403:粗略移动器

58.404:精细延迟控制字元

59.405:粗略延迟控制字元

60.406:信号

61.407:第二时脉信号

62.408:相位比较信号

63.409:第一时脉信号/输入周期性信号

64.410:延迟元件

65.411:精细调谐部分

66.412:粗略调谐部分

67.413:目标延迟信号

68.420:目标延迟产生器

69.430:相位侦测器

70.502:延迟量值信号

71.503:数字低通滤波器

72.504:解码器

73.505:精细一元转换器

74.506:控制字元

75.507:锁定侦测器

76.508:相位电路

77.508a:d型正反器

78.508b:多工器

79.508c:二进位加法器元件

80.508d:d型正反器

81.508e:逻辑and门

82.510:模式切换信号

83.511:粗略调谐

84.512:锁定侦测信号

85.513:相移信号

86.514:脉冲产生器

87.515:模式切换电路

88.516:粗略移动器

89.517:粗略一元转换器

90.518:输入周期性信号

91.519:第一d型正反器

92.520:第二d型正反器

93.522:相位侦测器

94.523:输出信号/周期性信号

95.524:一元精细延迟控制字元

96.525:目标延迟信号

97.527:一元粗略延迟控制字元/温度计码

98.529:粗略调谐部分/粗略调谐区块

99.530:经预延迟的信号

100.531:相位比较信号

101.535:精细调谐部分/精细调谐区块

102.536:延迟元件

103.537:目标延迟产生器

104.538:经预延迟的周期性信号

105.540:延迟元件

106.541:粗略调谐部分

107.542:精细调谐部分

108.543:单位单元

109.544:传输门

110.545:示意图

111.546:输入周期性信号

112.547:启用引脚

113.548:温度计码粗略调谐字元

114.549:单位单元

115.550:图表

116.551:单元

117.552:三状态反相器单位单元的阵列

118.553:温度计码精细调谐字元

119.600:解码器

120.610:精细调谐部分

121.620:粗略调谐部分

122.700:锁定侦测器

123.704:比较结果

124.705:值

125.706:信号

126.707:周期性输入信号

127.740:正反器

128.1220:远端延迟串

129.1230:时脉树

130.1000:方法

131.1002:操作

132.1004:操作

133.1006:操作

134.1008:操作

135.1010:操作

具体实施方式

136.以下揭示内容提供用于实施所提供标的物的不同特征的许多不同实施例或实例。下文描述组件及配置的特定实例以简化本揭露。当然,这些组件及配置仅为实例且并非意欲为限制性的。举例而言,在以下描述中第一特征于第二特征上方或上的形成可包括第一及第二特征直接接触地形成的实施例,且亦可包括额外特征可形成于第一特征与第二特征之间使得第一特征及第二特征可不直接接触的实施例。此外,本揭露在一些各种实例中可重复参考数字及/或字母。此重复是出于简单及清楚的目的,且本身并不指明所论述的一些各种实施例及/或组态之间的关系。

137.另外,空间相对术语,诸如

“……

下面”、“下方”、“下部”、

“……

上方”、“上部”及类似者本文中可出于易于描述而使用以描述如诸图中图示的一个元素或特征与另一(些)元素或特征的关系。空间相对术语意欲涵盖装置的使用或操作中的除了诸图中描绘的定向外的不同定向。设备可以其他方式定向(旋转90度或处于其他定向),且本文中使用的空间相对描述词可同样经因此解译。

138.描述本揭露的一些实施例。在这些实施例中描述的阶段之前、期间及/或之后可提供额外操作。经描述的阶段中的一些对于不同实施例可被替换或消除。额外特征可被添加至半导体装置。下文描述的特征中的一些对于不同实施例可被替换或消除。尽管一些实施例参看按特定次序执行的操作予以论述,但这些操作可以另一逻辑次序执行。

139.延迟锁定回路(delay lock loop;dll)电路用于数字系统中以使多个数字信号的边缘对准。dll电路可用以例如基于参考时脉信号来对准时脉信号的上升边缘及/或下降边缘以产生经同步化的输出时脉信号。已知dll电路经由模拟电路实施,且通常包括相位侦测器、电荷泵、滤波器及延迟串。此类已知dll电路具有如下缺点:易受在参考时脉信号与输出时脉信号之间引入的非必要延迟(latencies)影响。非必要延迟可为模拟电路固有的特性,包括通过环境因素(例如,暴露于高温等)引起的电流失配的结果。在较高频率(例如,7ghz或以上的频率)下且当使用较小特征大小(例如,5nm特征大小等)时,这些延迟可能变得特别显著。

140.本揭露的方法提供dll电路及用于操作dll电路的方法,这些dll电路消除或减轻已知dll电路的非必要延迟及其他缺陷。在一些实施例中,本揭露的方法通过使用数字技术控制dll电路来达成这些优势。本揭露的数字控制dll电路较不容易受到引入至输出中的误

差以及参考时脉信号与输出时脉信号之间的目标相位延迟的失真影响。因此,相较于已知模拟dll方法,本揭露的方法赋予更高准确度、可预测性、弹性及可靠性。另外,经由使用数字控制dll减轻误差赋予数字控制dll在高频应用中且在具有小的特征大小的实施方式中的使用。

141.图1为根据一些实施例的dll电路的方块图。如在此图中所示,dll电路包括接收第一时脉信号105及第二时脉信号103的相位侦测器130。基于接收到的时脉信号,相位侦测器130产生数字信号104,该数字信号指示第一时脉信号105的相位与第二时脉信号103的相位之间的关系。相位侦测器130用以比较第一时脉信号105与第二时脉信号103以判定两个信号之间的相对相位差。在一些实施例中,第一时脉信号105为通过dll电路接收的参考时脉信号,且第二时脉信号103为通过dll电路产生的输出时脉信号。图1的dll电路可用以对准第二时脉信号103的边缘(例如,上升边缘及/或下降边缘)与第一时脉信号105的边缘以产生经同步的输出时脉信号。

142.通过相位侦测器130产生的数字信号104通过相位电路100接收。在一些实施例中,相位电路100为基于所接收数字信号104产生相位信号101的相位累加器电路。在此类实施例中,相位电路100用以累加数字信号104在多个循环上的值以计算对准第一时脉信号105的相位与第二时脉信号103的相位需要的总相移延迟。此信息通过相位电路100输出为相位信号101。

143.在一些实施例中,通过相位电路100接收到的数字信号104包括数字值(例如,为“1”的逻辑位准高值、为“0”的逻辑位准低值),这些数字值指示第二时脉信号103落后于或领先于第一时脉信号105。举例而言,在一些实施例中,具有“1”值的数字信号104指示第二时脉信号103落后于第一时脉信号105,且具有“0”值的数字信号104指示第二时脉信号103领先于第一时脉信号105,或反之亦然。

144.在一些实施例中,相位电路100基于数字信号104具有第一值(例如,为“1”的逻辑位准高值)而增大相位信号101的值,且基于数字信号104具有第二值(例如,为“0”的逻辑位准低值)减低相位信号101的值。通过相位电路100产生的相位信号101通过解码器110接收,该解码器基于相位信号101产生数字控制字元102。在一些实施例中,解码器110执行一或多个解码功能以解码相位信号101,且借此产生数字控制字元102。

145.延迟元件120自解码器110接收数字控制字元102。在一些实施例中,延迟元件120用以通过根据数字控制字元102修改第二时脉信号103的相位来改变第一时脉信号105的相位与第二时脉信号103的相位之间的关系。相移信号接着通过延迟元件120输出为第二控制信号103,第二控制信号103作为反馈信号而反馈至相位侦测器130以重复上述程序。

146.如下文参看图2至图10进一步解释,本揭露的实施例利用组合数字电路与模拟电路以对已知模拟dll电路进行改良的方法。在一些实施例中,数字电路包括相位电路100及解码器110,相位电路100及解码器110一起构成dll电路的数字核心的部分。依据本揭露的方法使用的数字信号包括通过相位侦测器130产生的前述数字信号104及通过解码器110产生的数字控制字元102。使用此类数字组件及数字信号赋予优于已知dll电路的改良,这些已知dll电路主要基于模拟技术。此类改良贯穿本揭露予以描述。构成数字核心的组件的结构及功能性在下文进一步详细地描述。

147.与数字核心一起,本揭露的dll电路包括与数字组件相互作用的模拟组件。这些模

拟组件包括一起构成dll电路的模拟核心的部分的延迟元件120及相位侦测器130。构成模拟核心的组件的结构及功能性在下文进一步详细地描述。本文中所描述的模拟组件与数字组件的组合用以提供dll电路及用以操作dll电路的方法,这些dll电路有利地消除已知模拟dll电路的非必要延迟及误差。

148.图2为根据一些实施例的描绘在相位电路200与解码器230之间交换的信号的方块图。相位电路200、解码器230及相位侦测器240提供上文分别关于图1的相位电路100、解码器110及相位侦测器130描述的功能性。如本文中所描述,本揭露的一些实施例包括基于精细调谐模式及粗略调谐模式两者提供延迟的延迟元件(例如,图1的延迟元件120、图4的延迟元件410等)。在一些实施例中,精细调谐模式及粗略调谐模式使用通过解码器230的不同部分产生的独特延迟控制字元来达成。图2描绘用于在精细调谐模式与粗略调谐模式之间进行选择并切换的控制机制的态样。

149.更具体而言,在一些实施例中,在待达成的相位差具有通过延迟元件的粗略调谐模式不可达成的精度之后,粗略调谐模式与精细调谐模式之间的切换自动地发生。此事件通过相位侦测器240来侦测,相位侦测器240输出具有第一逻辑值(例如,为“1”的逻辑位准高值)的数字信号206,该第一逻辑值指示对待施加至第二时脉信号207的额外相移的需要。数字信号206及第二时脉信号207分别对应于如上文关于图1所描述的数字信号104及第二时脉信号103。相位侦测器240输出具有第一逻辑值的数字信号206,直至第二时脉信号207的相位已被延迟移位超过目标相位,从而指示第一时脉信号205及第二时脉信号207的相位经对准达小于可通过延迟元件的粗略调谐模式提供的延迟量的程度。在此处,相位侦测器240产生具有第二逻辑值(例如,为“0”的逻辑位准低值)的数字信号206,该第二逻辑值指示切换至精细调谐模式以进一步对准时脉信号205、207的相位的需要。

150.相位电路200自相位侦测器240接收数字信号206,且基于所接收信号206产生相位信号201。相位信号201对应于图1的相位信号101,且提供与上文针对相位信号101描述的功能性相同或类似的功能性。在一些实施例中,相位电路200用以针对每一时脉循环使相位信号201的数值输出增大一个位元,在每一时脉循环中,该相位电路接收具有第一逻辑值(例如,为“1”的逻辑位准高值)的数字信号206,因此增大待施加至第二时脉信号207的总延迟。

151.当相位电路200接收具有第二逻辑值(例如,为“0”的逻辑位准低值)的数字信号206时,此情形指示第二时脉信号207的相位被延迟超过先前循环中的目标相位。基于此输入,相位电路200使相位信号201的数值输出减低一个位元,前述情形使得延迟元件(例如,图1的延迟元件120、图4的延迟元件410等)的粗略调谐模式使时脉信号207延迟,使得时脉信号的相位尽可能紧密地与粗略调谐模式可允许的目标相位对准而不会使时脉信号207落后于目标相位。

152.在一些实施例中,模式切换元件220用以接收相位信号201。在侦测到相位信号201的值的减低之后,模式切换元件220便将模式切换信号204的值自第一逻辑位准值(例如,“0”)改变至第二逻辑位准值(例如,“1”)。解码器230用以接收相位信号201及模式切换信号204。当模式切换信号204自第一逻辑位准值改变至第二逻辑位准值时,解码器230冻结相位信号201的当前值,且启动解码器230的精细解码模式。

153.在一些实施例中,脉冲产生器210亦用以接收模式切换信号204。在接收到具有第二逻辑位准值(例如,“1”)的模式切换信号204之后,脉冲产生器210在重设累加器信号203

上输出重设脉冲,该重设脉冲通过相位电路200来接收。在接收到重设累加器信号203之后,相位电路200便经重设,该相位电路重设相位信号201为初始值(例如,零)。相位信号201的重设经执行,使得相位信号201可接着用以计算将在延迟元件的精细调谐模式中施加的相位延迟。

154.图3为根据一些实施例的描绘解码器320的额外细节的方块图。图3的相位电路300、脉冲产生器310、模式切换元件315、解码器320及延迟元件330提供上文关于图1及图2的对应元件描述的一些或所有功能性。同样,图3的相位信号301、模式切换信号302及重设累加器信号303以类似于上文参看图1及图2描述的对应信号的方式来使用。

155.在一些实施例中,解码器320含有精细解码器部分321及粗略解码器部分322。如图2中一般,解码器320用以接收相位信号301及模式切换信号302,该模式切换信号可经初始化为第一值(例如,“0”)。在模式切换信号302具有第一值时,粗略解码器部分322启动,且精细解码器部分321停用。启动时,粗略解码器部分322用以接收相位信号301且将相位信号301自二元值转换为对应的一元粗略延迟控制字元305以控制待通过延迟元件330施加的延迟量。在一些实施例中,粗略延迟控制字元305为32位元一元数,该32位元一元数经初始化为第一值(例如,“0”)。在转换为一元数之前,等同于相位信号301的二进位数经由粗略移动器323馈入,粗略移动器323用以连续地输出粗略移动器323已接收到的上一非零二进位数。在一些实施例中,粗略移动器323经建置至解码器320中以受到保护而免受温度及电压的变化影响。

156.在一些实施例中,当模式切换信号302自第一值(例如,“0”)改变至第二值(例如,“1”)时,解码器320接收此第二值。基于接收到的第二值,解码器320锁定粗略解码器部分322且启动精细解码器部分321。锁定粗略解码器部分322防止相位信号301进入粗略解码器部分322,从而使得特定值(例如,“0”)传播至粗略移动器323的输入端。粗略移动器323继续输出其接收到的等同于相位信号301的二进位数,使得延迟元件330的粗略调谐部分继续施加相同延迟量。当解码器320的精细解码器部分321经启动时,精细解码器部分321接收相位信号301作为输入且输出精细延迟控制字元304。在一些实施例中,精细延迟控制字元304对应于相位信号301的一元值加上相位信号301的初始化值,该初始化值等同于延迟元件330的精细调谐部分的最大延迟输出的一半。在一些实施例中,精细延迟控制字元304为32位元一元数。

157.图4为根据一些实施例的描绘延迟元件410的细节的方块图。图4的解码器400、精细解码器部分401、粗略解码器部分402、粗略移动器403、延迟元件410及相位侦测器430提供上文关于图1至图3的对应元件描述的一些或所有功能性。同样,图4的精细延迟控制字元404、粗略延迟控制字元405及第二时脉信号407以类似于上文参看图1至图3描述的对应信号的方式来使用。

158.在一些实施例中,延迟元件410用以接受粗略延迟控制字元405及精细延迟控制字元404的一元输入以及经预移位周期性信号406。一元粗略延迟控制字元405通过延迟元件410的粗略调谐部分412接受,延迟元件410启动粗略调谐部分412中对应于一元粗略延迟控制字元405的数个粗略延迟元件。类似地,一元精细延迟控制字元404通过延迟元件410的精细调谐部分411接受,延迟元件410启动精细调谐部分411中对应于一元精细延迟控制字元404的数个精细延迟元件。延迟元件410接着通过以下操作使预延迟的周期性信号406延迟:

馈入预延迟的周期性信号通过粗略调谐部分412及精细调谐部分411两者的数个经启动的延迟单元,输出经预移位的周期性信号406的经相位延迟移位版本作为第二时脉信号407。

159.如图4中所绘示,目标延迟产生器420用以接受第一时脉信号409及目标延迟信号413。第一时脉信号409对应于上文参看图1至图3描述的第一时脉信号(例如,第一时脉信号105、第一时脉信号205)。在一些实施例中,目标延迟信号413为周期性信号,该信号具有对应于待施加至第一时脉信号409的所欲相移的周期大小。在一些实施例中,目标延迟产生器420以等同于所欲相位延迟的长度的倒数的速率对第一时脉信号409进行取样。

160.在目标延迟信号413为具有一周期大小的周期性信号的一些实施例中,该周期大小对应于待施加至具有与第一时脉信号409相同的频率的信号的所欲相移,此情形通过使用目标延迟信号413的频率对输入周期性信号409进行取样来实现。此情形导致目标延迟产生器420按所欲相位延迟长度的解析度来输出预延迟周期性信号406且预延迟周期性信号406的周期为所欲相位延迟的整数倍数。目标延迟产生器420亦输出相位比较信号408。在一些实施例中,相位比较信号408通过使等同于预延迟信号406的经取样周期性信号通过额外d型正反器来产生,其中d型正反器的时脉(clock,clk)通过用以对输入周期性信号409进行取样以产生预延迟的周期性信号406的相同周期性信号驱动。此导致相位比较信号408亦具有所欲相位延迟的解析度及等同于所欲相位延迟的完整数的整数倍数的周期。然而,因为相位比较信号408已经过额外d型正反器,所以相位比较信号408具有落后于预延迟周期性信号406准确地一个目标相位延迟的长度的相位。

161.相位侦测器430用以接受相位比较信号408及第二时脉信号407,在第二时脉信号407被延迟移位延迟元件410经程序化已执行的时间量之后,第二时脉信号407等同于经预延迟的周期性信号406。相位侦测器430接着比较这两个信号以判定通过延迟元件410施加的延迟量应增大或减低以使相位比较信号408及第二时脉信号407的相位对准。因为相位比较信号408的相位落后于预延迟周期性信号406准确的目标延迟长度,所以通过延迟元件410施加至预延迟周期性信号406的延迟必须等同于目标延迟,延迟元件410使预延迟周期性信号406的相位与相位比较信号408的相位对准。

162.图5a为根据一些实施例的dll电路的实例实施方式的示意图。在一些实施例中,图5a的dll电路用以产生相位延迟,从而使输入周期性信号518延迟通过目标延迟信号525的周期长度指示的目标延迟量。在图5a中,目标延迟产生器537用以接受输入周期性信号518及目标延迟信号525,输入周期性信号518及目标延迟信号525具有等同于待施加至周期性信号的所欲相移的周期长度,该周期性信号具有等同于输入周期性信号518的频率的频率。目标延迟产生器537首先通过发送输入周期性信号518通过第一d型正反器(d flip flop,df)519以目标延迟信号525的频率对输入周期性信号518进行取样,第一d型正反器519接受目标延迟信号525作为其时脉值。

163.第一d型正反器519输出经预延迟的信号530,经预延迟的信号530等同于以目标相位延迟大小的解析度表示的输入周期性信号518,其中经预延迟的信号530的周期为目标相位延迟的完整数的整数倍数。第二d型正反器520接受经预延迟的信号530作为输入且接受目标延迟信号525作为其时脉,第二d型正反器520产生相位比较信号531作为输出。目标延迟产生器537输出待接受的经预延迟的信号530作为至延迟元件536的输入,且输出待接受的相位比较信号531作为相位侦测器522的输入。图5b为根据一些实施例的通过目标延迟产

生器537使用的信号的时序图。

164.再次参看图5a,在一些实施例中,相位侦测器522包括单一d型正反器,该单一d型正反器用以接受输出信号523作为其输入且接受相位比较信号531作为其时脉(clock,clk)。相位比较信号531等同于经预延迟的信号538,但通过第二d型正反器520在经预延迟的信号538之后准确地向后相移一个目标延迟。输出信号523等同于经预延迟的信号加上通过延迟元件536施加至输出信号523的延迟。修改通过延迟元件536施加至输出周期性信号523的延迟用以使输出周期性信号523的相位量值上等同于目标延迟。因此,在一些实施例中,包含相位侦测器522的d型正反器用以输出逻辑1信号至相移信号513,而相位比较信号531的相位落后于输出周期性信号523的相位,从而指示通过延迟元件536施加的延迟需要增大延迟的量值以与目标延迟匹配。相反,若输出周期性信号523的相位落后于相位比较信号531,则包含相位侦测器522的d型正反器输出逻辑0至相移信号513,从而指示通过延迟元件536施加的延迟需要减低延迟的量值以与目标延迟匹配。

165.相位电路508通过用以每时脉循环一次地接受相移信号513作为输入而充当相位累加器,该时脉同步至输入周期性信号518。相移信号513的值通过接受相移信号513作为至d型正反器508a的输入而每时脉循环读取一次,其中时脉同步至输入周期性信号518。d型正反器508a的输出充当用于多工器508b的控制位元,多工器508b在其控制位元为1时输出二进位值1,且在控制位元为0时输出二进位值-1。此二进位值通过二进位加法器元件508c接受,二进位加法器元件508c亦通过发送其输出通过d型正反器508d而每时脉循环接收延迟量值信号502作为输入一次,其中时脉在返回接收延迟量值信号502作为输入之前而同步至输入周期性信号518。作为延迟量值信号502累加的值通过相位电路508输出,且指示待通过相位延迟元件536施加的相位延迟的量值。

166.在一些实施例中,延迟量值信号发送通过数字低通滤波器503以在发送至解码器504之前减轻信号中的杂讯。解码器504接受延迟量值信号502作为输入,以将延迟量值信号502转换为一元控制字元,从而控制通过延迟元件536施加的延迟量。在电路的一些实施例中,延迟元件536包含多个功能模式,诸如粗略调谐部分529及精细调谐部分535,解码器504出于进行通过延迟元件536施加至输出周期性信号523的粗略延迟改变或精细调谐延迟调整的目的而具有多个操作模式。在一些实施例中,解码器用以接收模式切换信号510作为输出。在模式切换信号510设定为逻辑0的初始值时,解码器以粗略模式操作,此情形使得延迟量值信号通过粗略一元转换器517最终转换为一元粗略延迟控制字元527,从而控制通过延迟元件536的粗略调谐部分529施加至输出周期性信号523的粗略延迟的量。在到达粗略一元转换器517之前,实施粗略移动器516,在解码器504处于粗略模式时,此情形通过由解码器504连续地输出上一非零值输出用于粗略调谐511来确保发送至延迟元件536的粗略调谐部分529的控制信号的连续性。

167.在一些实施例中,模式切换电路515用以接收延迟量值信号502,且在接收到延迟量值信号502的值的下降之后,便输出逻辑1信号至模式切换信号510,模式切换信号510最初经初始化至逻辑0。脉冲产生器514用以接收模式切换信号510且输出相位累加器重设信号509,相位累加器重设信号509在到达d型正反器508d之前通过逻辑and门508e而与二进位加法器元件508c的和组合,相位累加器重设信号509重设延迟量值信号502的值为0以开始累加通过延迟元件536的精细调谐部分535待施加至输出信号523的延迟的值。

168.在自模式切换信号510接收逻辑1信号作为输入之后,解码器504自粗略切换模式切换至精细调谐模式。一元粗略控制字元527锁定于其当前值,使得经实施的粗略延迟在精细调谐延迟调整期间且之后继续。解码器504输出延迟量值信号至精细一元转换器505,精细一元转换器505输出一元精细延迟控制字元524以控制通过延迟元件536的精细调谐部分535施加至输出周期性信号523的延迟量。

169.在一些实施例中,锁定侦测器507用以通过解码器504接受二元延迟控制字元506及等同于输入周期性信号518的周期性输入信号。在一些实施例中,控制字元506对应于精细调谐调整的延迟控制字元。锁定侦测器507每时脉循环接受控制字元506一次,且比较控制字元506与设定的临限值。若控制字元506并未超出临限值历时预定数目个循环,则控制字元506在锁定侦测信号512上输出逻辑1信号,锁定侦测信号512先前经初始化为逻辑0。

170.延迟元件536用以接受经预延迟的周期性信号538作为输入。在一些实施例中,延迟元件536包含粗略调谐部分529及精细调谐部分535。粗略调谐部分529接受一元粗略延迟控制字元527,该一元粗略延迟控制字元控制通过延迟元件536施加的粗略延迟增量的量。精细调谐部分535接受一元精细延迟控制字元524,其中位元中的最高有效位元的一半经反相以使初始预设延迟移位达总精细调谐延迟容量的50%以在必要时允许在两个方向上移位。经预延迟的周期性信号538接着馈送通过所有延迟元件,这些延迟元件通过接收的一元控制码的部分接收逻辑1位元来启动且输出输出周期性信号523,这些延迟元件自延迟元件536的粗略调谐部分及精细调谐部分两者中接收一元控制码的部分。

171.在一些实施例中,延迟元件536具有单位单元(unit cell)结构,该单位单元结构用以减小粗略调谐区块529与精细调谐区块535之间的延迟变化且亦减小电路复杂性。在一些实施例中,延迟元件536的单位单元结构通过具有受控引脚(controlled pin)(en)的三状态反相器来实施。在图5a的实例中,粗略调谐区块529为通过温度计码527控制的32级延迟串。粗略调谐区块的每一级可通过2个单位单元及一传输门实施。在一些实施例中,精细调谐区块535通过使用八个单位单元的具有延迟范围的相位插入器实施。在一些实施例中,精细调谐区块包括三十二(32)个步阶以产生更精细解析度。

172.图5c描绘根据一些实施例的延迟元件540。在一些实施例中,延迟元件540具有粗略调谐部分541及精细调谐部分542。延迟元件540的两个部分组态有单位单元结构。实例的粗略单位单元通过粗略单位单元543描绘。粗略单位单元543运用两个三状态反相器单位单元549及一传输门544来实施。三状态反相器单位单元549的实例晶体管位准示意图545通过示意图545绘示。在图5c的实例中,粗略调谐部分541为通过温度计码粗略调谐字元548控制的32级延迟串。粗略调谐区块的每一级可实施为粗略单位单元543。

173.每一单元具有待延迟的输入周期性信号546及启用引脚547。启用引脚547电耦接至温度计码粗略单位单元543的单一位元。每一单位单元543具有如下两者:三状态反相器单位单元自温度计码粗略调谐字元548接收同一位元,且每一单位单元543相较于其他单元接收温度计码粗略调谐字元548的不同于位元作为启用引脚547的启用信号。以此方式,温度计码粗略调谐字元548通过接收逻辑1输入以启用引脚547来控制启动的粗略单位单元543的数目,或通过设定启用引脚为逻辑低来断开数个单位单元543,从而致使单位单元549具有高阻抗且自粗略调谐部分541断开延迟部分。

174.精细调谐部分542以含有相位插入器的单位单元实施,该相位插入器在一些实施

例中具有八(8)个位元单元551的延迟范围及用于精细解析度的三十二(32)步阶。如图表550中所描绘,八(8)个单位单元中的每一者实施有四个步阶用于精细解析度。八(8)个单位单元551中的每一者通过具有三状态反相器单位单元的阵列552来达成此精细解析度,这些三状态反相器单位单元中的每一者根据温度计码精细调谐字元553来接通或关断延迟步阶,三状态反相器单位单元以与如在粗略调谐部分541情况下进行的方式相同的方式在启用引脚547上接收该温度计码精细调谐字元。

175.图6描绘根据一些实施例的具有精细调谐部分610及粗略调谐部分620的解码器600的细节。如本文中所描述,解码器600将数字滤波器的相位信息转换为通过延迟元件使用的操作调谐字元。通过精细调谐部分610产生的精细调谐字元在启动粗略调谐部分620时固定于中间值。同样,通过粗略调谐部分620产生的粗略调谐字元在启动精细调谐部分610时固定于一值。

176.如图6中所绘示,解码器600的实施例包括溢位/欠位侦测器(标记为“ov_ud侦测”),该溢位/欠位侦测器嵌入于精细调谐部分610及粗略调谐部分620两者中。当粗略调谐字元及精细调谐字元的溢位/欠位被触发时,精细调谐部分610及粗略调谐部分620两者的调谐字元锁定于先前值。除了溢位/欠位侦测器外,精细调谐部分610及粗略调谐部分620的实施例亦包括用于提供所接收phe及tpk信号的精细及粗略解码的逻辑组件及粗略移动器。这些组件及粗略移动器在全文以引用的方式并入本文中的美国专利申请案第10,439,794号中进一步详细地描述。

177.图7a及图7b描绘根据一些实施例的锁定侦测器700的细节。如上文所描述,锁定侦测器700用以接受通过解码器输出的二元延迟控制字元及等同于周期性输入信号的周期性输入信号707。锁定侦测器700每时脉循环接受控制字元一次,且比较该控制字元与设定的临限值,且若控制字元并不超出临限值历时预定数目个循环,则锁定侦测器700在锁定侦测信号上输出逻辑1信号,该锁定侦测信号先前初始化为逻辑0。

178.另外,如图7a及图7b中所绘示,锁定侦测器700在信号trk变高之后每256个参考时脉循环对精细调谐字元(fine_bin)取样一次。锁定侦测器700比较fine_bin的差以检查确认差是否是在

±

7个码内。若比较结果704是在此准则内,则3位元计数器经触发以对值705进行累加。正反器740输出的ld信号706变高,直至3位元计数器的数字为3,此情形指示dll电路为锁定的。在一些实施例中,总等待时段为768个参考循环,如图7b中所绘示。

179.图8描绘根据本揭露的一些实施例实施的dll电路的时序图。如此图中所绘示,当dll电路是处于初始条件时,粗略调谐字元及精细调谐字元的状态分别为0及16的中间值。d型正反器1(例如,df1)的时脉为输入时脉,且d型正反器2(例如,df2)的时脉为延迟时脉。开始时,粗略调谐字元增大以遵循目标延迟,且精细调谐字元锁定于中间值。粗略调谐至精细调谐的切换通过swover区块来判定,如本文中所判定。swover区块在全文以引用的方式并入本文中的美国专利申请案第10,644,869号中进一步详细地描述。

180.本揭露的方法可用于时脉树中以将选通时脉(例如,取样时脉)的相位移位至资料的中央。图9绘示此情形的实例。模拟顶部部分的延迟串通过数字信号来控制,且因此此区块可经复制为远端延迟串1220从而嵌入于晶片的时脉树内。此架构的益处为,远端延迟串1220具有紧凑型尺寸,且可应用于多个时脉树1230中。更一般而言,本揭露的方法可用以替换已知模拟dll电路且借此移除归因于电流及装置失配的变化,如上文所描述。

181.图10描绘根据一些实施例的实例方法1000的操作。为易于理解图10,请参看以上图1以描述。但图10的程序又适用于其他电路。在操作1002处,接收第一时脉信号及第二时脉信号(例如,第一时脉信号105、第二时脉信号103)。在操作1004处,产生一数字信号(例如,数字信号104),该数字信号指示第一时脉信号的相位与第二时脉信号的相位之间的关系。在图1的实例中,第一时脉信号及第二时脉信号通过相位侦测器130接收,且相位侦测器130产生数字信号。在操作1006处,基于数字信号在多个时脉循环上累加的值而产生一相位信号(例如,相位信号101)。在图1的实例中,相位信号通过相位电路100产生,相位电路100可使用相位累加器电路来实施。在操作1008处,数字控制字元(例如,数字控制字元102)基于相位信号来产生。在图1的实例中,数字控制字元通过解码器110产生。在操作1010处,通过根据数字控制字元修改第二时脉信号的相位来改变第一时脉信号的相位与第二时脉信号的相位之间的关系。在图1的实例中,该关系通过延迟元件120改变。

182.本揭露是针对数字延迟锁定电路,及用于操作数字延迟锁定电路的方法。一实例延迟电路包括一相位侦测器,相位侦测器用以(i)接收第一时脉信号及第二时脉信号,及(ii)产生一数字信号,数字信号指示第一时脉信号的一相位与第二时脉信号的一相位之间的一关系。一相位累加器电路用以接收数字信号并基于数字信号在多个时脉循环上的值而产生一相位信号。一解码器用以接收相位信号,且基于相位信号产生一数字控制字元。一延迟元件用以接收数字控制字元,且通过根据数字控制字元修改第二时脉信号的相位来改变第一时脉信号的相位与第二时脉信号的相位之间的关系。在一些实施例中,延迟元件包括一粗略调谐元件及一精细调谐元件,精细调谐元件相较于粗略调谐元件具有一较短可程序化延迟增量。在一些实施例中,解码器包含一粗略解码器元件及一精细解码器元件,粗略解码器元件产生一粗略控制字元以控制粗略调谐元件,且精细解码器元件产生一精细控制字元以控制精细调谐元件。在一些实施例中,电路进一步包含切换模式元件。切换模式元件用以接收相位信号,且用以在相位信号指示第一时脉信号的相位与第二时脉信号的相位之间的一差小于可通过粗略调谐元件施加的一延迟改变量之后,自修改通过粗略调谐元件施加的一延迟量切换至修改通过精细调谐元件施加的一延迟量。在一些实施例中,电路进一步包含延迟产生器。延迟产生器用以接收(i)一输入周期性信号,输入周期性信号具有等同于第一时脉信号及第二时脉信号的一所欲频率的一频率;且用以接收(ii)一目标相位周期性信号,目标相位周期性信号具有等同于第一时脉信号与第二时脉信号之间的一目标相位延迟的一周期。在一些实施例中,延迟产生器进一步用以产生(i)一预移位周期性信号,预移位周期性信号为通过目标相位周期性信号取样的输入周期性信号;且用以产生(ii)一相位比较信号,相位比较信号为通过目标相位周期性信号取样的预移位周期性信号。在一些实施例中,电路进一步包含延迟产生器。延迟产生器用以接收第一时脉信号及表示对第一时脉信号的一目标相位延迟改变的一目标延迟信号,延迟产生器用以通过以与目标相位延迟改变成反比的一频率对第一时脉信号进行取样来产生第二时脉信号。在一些实施例中,目标延迟信号为具有一周期的一周期性信号,周期指示目标相位延迟改变。在一些实施例中,电路进一步包含锁定侦测器。锁定侦测器用以(i)接收一数字延迟控制字元及一参考时脉,且用以(ii)在数字延迟控制字元保持低于一临限值历时一预定数目个时脉循环之后产生一相位锁定信号。在一些实施例中,相位累加器电路用以在时脉循环累加数字信号的值。

183.另一实例电路包括一相位侦测器,相位侦测器用以接收第一时脉信号及第二时脉

信号,及产生一数字信号,数字信号指示第一时脉信号的一相位与第二时脉信号的一相位之间的一关系。实例电路进一步包括一数字控制区块,数字控制区块用以接收数字信号,并基于数字信号在多个时脉循环上的值而产生一数字控制字元。一延迟元件用以(i)接收数字控制字元,且(ii)通过根据数字控制字元修改第二时脉信号的相位而改变第一时脉信号的相位与第二时脉信号的相位之间的关系。在一些实施例中,延迟元件包含一粗略调谐元件及一精细调谐元件,精细调谐元件相较于粗略调谐元件具有一较短可程序化延迟增量。在一些实施例中,数字控制区块包括一粗略解码器元件及一精细解码器元件,粗略解码器元件产生一粗略控制字元以控制粗略调谐元件,且精细解码器元件产生一精细控制字元以控制精细调谐元件。在一些实施例中,电路进一步包含切换模式元件。切换模式元件用以在第一时脉信号的相位与第二时脉信号的相位之间的一差小于可通过粗略调谐元件施加的一延迟改变量时,自修改通过粗略调谐元件施加的一延迟量切换至修改通过精细调谐元件施加的一延迟量。在一些实施例中,电路进一步包含延迟产生器。延迟产生器用以接收(i)一输入周期性信号,输入周期性信号具有等同于第一时脉信号及第二时脉信号的一所欲频率的一频率;及用以接收(ii)一目标相位周期性信号,目标相位周期性信号具有等同于第一时脉信号与第二时脉信号之间的一目标相位延迟的一周期。在一些实施例中,延迟产生器进一步用以产生(i)一预移位周期性信号,预移位周期性信号为通过目标相位周期性信号取样的输入周期性信号;及用以产生(ii)一相位比较信号,相位比较信号为通过目标相位周期性信号取样的预移位周期性信号。在一些实施例中,电路进一步包含延迟产生器。延迟产生器用以接收第一时脉信号及表示对第一时脉信号的一目标相位延迟改变的一目标延迟信号,延迟产生器用以通过以与目标相位延迟改变成反比的一频率对第一时脉信号进行取样来产生第二时脉信号。在一些实施例中,目标延迟信号为具有一周期的一周期性信号,周期指示目标相位延迟改变。在一些实施例中,电路进一步包含锁定侦测器。锁定侦测器用以(i)接收一数字控制字元及一参考时脉,及用以(ii)在数字控制字元保持低于一临限值历时一预定数目个时脉循环之后产生一相位锁定信号。

184.在用于操作一延迟锁定回路电路的实例方法中,接收第一时脉信号及第二时脉信号。产生一数字信号,数字信号指示第一时脉信号的一相位与第二时脉信号的一相位之间的一关系。基于数字信号在多个时脉循环上累加的值而产生一相位信号。基于相位信号产生一数字控制字元。通过根据数字控制字元修改第二时脉信号的相位来改变第一时脉信号的相位与第二时脉信号的相位之间的关系。

185.前述内容概述若干实施例的特征,使得熟悉此项技术者可更佳地理解本揭露的态样。熟悉此项技术者应了解,其可易于使用本揭露作为用于设计或修改用于实施本文中引入的实施例的相同目的及/或达成相同优势的其他制程及结构的基础。熟悉此项技术者亦应认识到,此类等同构造并不偏离本揭露的精神及范畴,且此类等同构造可在本文中进行各种改变、取代及替代而不偏离本揭露的精神及范畴。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。