1.本发明涉及一种线路基板,尤其涉及一种可挠性线路基板。

背景技术:

2.薄膜覆晶(chip on film,cof)封装与卷带承载封装(tape carrier package,tcp)等半导体产品是以卷带式传输进行封装作业。进一步而言,卷带式传输是通过传动齿轮或滚轮来带动可挠性薄膜以进行各种封装工艺,在此过程中,传动齿轮或滚轮会与可挠性线路基板的传输区所设置的金属层(例如铜箔)接触以将静电(即绝缘的可挠性薄膜在传输作业中不断重复的摩擦、剥离等动作而累积的大量静电荷)导出。然而,在传动齿轮的齿部或滚轮与金属层接触的过程中,金属层可能受摩擦而被刮除并产生金属微粒,而金属微粒可能污染作业环境并造成芯片电性问题(如短路、漏电或电性异常等)。因此,如何能避免金属微粒污染又可达到静电防护功效实为业界亟欲克服的问题。

技术实现要素:

3.本发明提供一种可挠性线路基板,其可以在提供静电防护的同时降低金属微粒污染作业环境且造成芯片电性问题(如短路、漏电或电性异常等)的机率。

4.本发明的一种可挠性线路基板,用以承载并电性连接多个芯片,其包括可挠性薄膜以及图案化金属层。可挠性薄膜具有二个传输区、多个装置区与一个无效区,其中二个传输区位于可挠性薄膜两侧并沿着第一方向延伸。多个装置区位于二个传输区之间并沿着第一方向排列。无效区位于二个传输区之间及多个装置区之外。图案化金属层设置于可挠性薄膜上且暴露出二个传输区,并且包括多个引脚与线路图案。多个引脚分别位于多个装置区内,并与分别设置于多个装置区内的多个芯片电性连接。线路图案位于无效区内,且线路图案内缩于二个传输区之间,以与二个传输区维持距离。此外,线路图案包括多个第一金属线,沿着垂直第一方向的第二方向延伸,且分别位于相邻两装置区之间的无效区内,其中每一装置区内的多个引脚具有至少一第一引脚延伸至相邻的无效区内并电性连接至第一金属线。

5.在本发明的一实施例中,上述的至少一第一引脚为接地线。

6.在本发明的一实施例中,上述的多个装置区通过每一装置区内的至少一第一引脚、多个第一金属线与多个芯片而彼此电性导通。

7.在本发明的一实施例中,上述的多个装置区与无效区间以裁切线为界。

8.在本发明的一实施例中,上述的每一装置区内的至少一第一引脚的数量为二个,二个第一引脚分别延伸至位于每一装置区相对两侧的无效区内并电性连接至第一金属线。

9.在本发明的一实施例中,上述的二个第一引脚分别为输入引脚与输出引脚。

10.在本发明的一实施例中,上述的线路图案包括对应环绕于每一装置区外的金属环以及连接相邻金属环的至少一第二金属线,其中每一金属环包括位于对应的装置区相对两侧的无效区的第一金属线。

11.在本发明的一实施例中,上述的相邻两金属环包括位于相同无效区内的二个第一金属线,且二个第一金属线以至少一第二金属线连接。

12.在本发明的一实施例中,上述的金属环为封闭环型轮廓。

13.在本发明的一实施例中,上述的可挠性线路基板还包括防焊层。防焊层设置于可挠性薄膜上,防焊层位于多个装置区内并局部覆盖多个引脚。

14.基于上述,本发明的可挠性线路基板可以通过线路图案(包括第一金属线)的设计提供静电防护,且线路图案(包括第一金属线)可以内缩于二个传输区之间,以与二个传输区维持距离,如此一来,线路图案(包括第一金属线)可以避免于可挠性线路基板传输运送时受到齿轮或滚轮等传动机构的摩擦而被刮除并产生金属微粒的情况,因此本发明的可挠性线路基板可以在提供静电防护的同时降低金属微粒污染作业环境且造成芯片电性问题(如短路、漏电或电性异常等)的机率。进一步而言,装置区内的第一引脚电性连接至第一金属线,因此只要作业环境中具有可导电物体(如机台上的构件)接触到第一金属线或包括第一金属线的金属环,装置区内的静电便会经由第一金属线或金属环与前述可导电物体导出,或者,在进行封装结构的最终测试时,由于所有装置区通过每一装置区内的第一引脚、第一金属线与芯片的连接而彼此电性导通,当测试装置探触一个装置区内的第一引脚的第一测试垫即可以一次性将所有装置区内的静电导出,因此通过线路图案(第一金属线或金属环)的设计可以提供整个可挠性线路基板静电防护的功效。

15.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合附图作详细说明如下。

附图说明

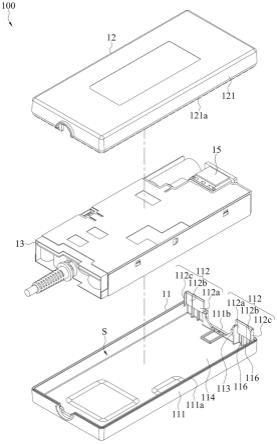

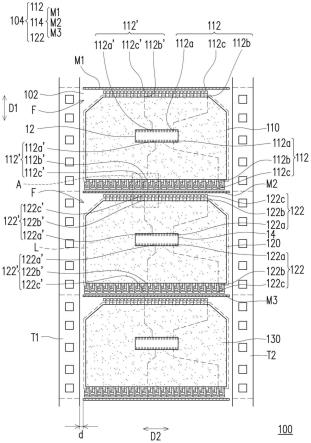

16.应说明的是,图1a与图2a中芯片采透视绘法且省略示出凸块,填充于芯片下与周围的封装胶体亦省略示出。

17.图1a是本发明一实施例的可挠性线路基板的局部俯视示意图;

18.图1b是图1a的区域a的放大示意图;

19.图2a是本发明另一实施例的可挠性线路基板的局部俯视示意图;

20.图2b是图2a的区域b的放大示意图;

具体实施方式

21.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

22.参照本实施例之附图以更全面地阐述本发明。然而,本发明亦可以各种不同的形式体现,而不应限于本文中所述之实施例。附图中的层或区域的厚度、尺寸或大小会为了清楚起见而放大。

23.图1a是本发明一实施例的可挠性线路基板的局部俯视示意图。图1b是图1a的区域a的放大示意图。首先,应说明的是,图1a中的可挠性线路基板100为包括多个接序排列且相同的封装单元(示意地示出三个)的卷带结构,各封装单元用以承载至少一芯片以形成薄膜覆晶封装结构。而为了简洁的说明,以下仅说明二相邻封装单元与其相邻金属线的配置方式,其他封装单元之间可以以类似的方式进行配置,不再赘述。

24.请参考图1a与图1b,在本实施例中,可挠性线路基板100用以承载并电性连接多个芯片12、14,且可挠性线路基板100包括可挠性薄膜102与图案化金属层104。在此,可以依照实际产品需求选择芯片种类,且可挠性薄膜102的材质例如是聚乙烯对苯二甲酸酯(polyethylene terephthalate,pet)、聚酰亚胺(polyimide,pi)、聚醚(polyethersulfone,pes)、碳酸脂(polycarbonate,pc)或其他适合的可挠性材料。

25.进一步而言,可挠性薄膜102可以具有二个传输区t1、t2、多个装置区110、120与一个无效区f,而图案化金属层104包括多个引脚112、122以及线路图案114,其中线路图案114包括多个第一金属线m1、m2、m3。

26.在本实施例中,传输区t1、t2位于可挠性薄膜102两侧并沿着第一方向d1延伸,装置区110、120位于传输区t1、t2之间并沿着第一方向d1排列,无效区f位于传输区t1、t2之间及装置区110、120之外,且图案化金属层104设置于可挠性薄膜102上且暴露出传输区t1、t2。也就是说,可挠性薄膜102在传输区t1、t2处系未设置有图案化金属层104而为裸露状。进一步而言,图案化金属层104的引脚112与引脚122分别位于装置区110与装置区120内,并与分别设置于装置区110与装置区120内的芯片12与芯片14电性连接,而线路图案114(包括第一金属线m1、m2、m3)位于无效区f内且内缩于传输区t1、t2之间,以与传输区t1、t2维持距离d。

27.此外,第一金属线m1、m2、m3沿着垂直第一方向d1的第二方向d2延伸,第一金属线m1位于相邻两装置区(相邻装置区110的装置区(未示出)与装置区110)之间的无效区f内,第一金属线m2位于相邻两装置区110、120之间的无效区f内,第一金属线m3位于相邻两装置区(装置区120与相邻装置区120的装置区(未标示))之间的无效区f内。

28.另一方面,装置区110内的引脚112可以具有至少一第一引脚112’,至少一第一引脚112’延伸至相邻的无效区f内并电性连接至第一金属线m1或m2。装置区120内的引脚122可以具有至少一第一引脚122’,至少一第一引脚122’延伸至相邻的无效区f内并电性连接至第一金属线m2或m3。在本实施例中,装置区110内的至少一第一引脚112’的数量为二个,二个第一引脚112’分别延伸至相邻于装置区110相对两侧的无效区f内并分别电性连接至第一金属线m1、m2。相同地,装置区120内的至少一第一引脚122’的数量为二个,二个第一引脚122’分别延伸至相邻于装置区120相对两侧的无效区f内并分别电性连接至第一金属线m2、m3。此外,装置区110、120的相对两侧分别为输入端与输出端。二个第一引脚112’分别为输入引脚与输出引脚,二个第一引脚122’也分别为输入引脚与输出引脚。而第一金属线m1是位于相邻于装置区110的输入端的无效区f内,第一金属线m2是位于装置区110的输出端与装置区120的输入端之间的无效区f内,第一金属线m3是位于相邻于装置区120的输出端的无效区f内。

29.更具体而言,引脚112包括内引脚112a、外引脚112b与测试垫112c,引脚122包括内引脚122a、外引脚122b与测试垫122c。相同地,第一引脚112’亦包括第一内引脚112a’、第一外引脚112b’与第一测试垫112c’,第一引脚122’亦包括第一内引脚122a’、第一外引脚122b’与第一测试垫122c’。引脚112是以内引脚112a电性连接芯片12,并且向外延伸连接外引脚112b以及测试垫112c。引脚122是以内引脚122a电性连接芯片14,并且向外延伸连接外引脚122b以及测试垫122c。而第一引脚112’是以第一内引脚112a’电性连接芯片12,且向外延伸连接第一外引脚112b’以及第一测试垫112c’,并进一步延伸连接至第一金属线m1、m2,

第一引脚122’是以第一内引脚122a’电性连接芯片14,且向外延伸连接第一外引脚122b’以及第一测试垫122c’,并进一步延伸连接至第一金属线m2、m3。在本实施例中,第一引脚112’可为装置区110的接地线,第一引脚122’可为装置区120的接地线。因此,当可挠性线路基板10的多个装置区皆以相同的方式进行配置时,多个装置区(如装置区110、120)通过每一装置区(如装置区110、120)内的至少一第一引脚(如第一引脚112’、122’)、多个第一金属线(如第一金属线m1、m2、m3)与多个芯片(如芯片12、14)而彼此电性导通。

30.此外,第一金属线m1、m2、m3的长度可以大于沿着相邻的装置区110、120的边缘排列的测试垫112c、122c的总长度,举例而言,第一金属线m1的长度大于沿着相邻的装置区110的边缘(图1a中装置区110的上侧边缘)排列的测试垫112c的总长度,第一金属线m2的长度大于沿着相邻的装置区110的边缘排列的测试垫112c及沿着相邻的装置区120的边缘排列的测试垫122c的总长度,第一金属线m3的长度大于沿着相邻的装置区120的边缘排列的测试垫122c的总长度,但本发明不限于此。

31.据此,本实施例的可挠性线路基板可以通过线路图案(包括第一金属线)的设计提供静电防护,且线路图案(包括第一金属线)可以内缩于二个传输区之间,以与二个传输区维持距离,如此一来,线路图案(包括第一金属线)可以避免于可挠性线路基板传输运送时受到齿轮或滚轮等传动机构的摩擦而被刮除并产生金属微粒的情况,因此,本实施例的可挠性线路基板可以在提供静电防护的同时降低金属微粒污染作业环境且造成芯片电性问题(如短路、漏电或电性异常等)的机率。进一步而言,装置区内的第一引脚可以电性连接至第一金属线,因此只要作业环境中具有可导电物体(如机台上的构件)接触到第一金属线,装置区内的静电便会经由第一金属线与前述可导电物体导出,或者,在进行封装结构的最终测试(final test,ft)时,由于所有装置区通过每一装置区内的第一引脚、第一金属线与芯片的连接而彼此电性导通,当测试装置探触一个装置区内的第一引脚的第一测试垫即可以一次性将所有装置区内的静电导出,因此通过第一金属线的设计可以提供整个可挠性线路基板静电防护的功效。

32.在一实施例中,装置区110、120与无效区f间以裁切线l为界,裁切线l例如是后续用于将装置区110、120裁切单离形成所需封装结构的辅助线。此外,前述测试垫可以皆位于裁切线l之外。

33.在一实施例中,可挠性线路基板100还包括防焊层130,其中防焊层130设置于可挠性薄膜102上且位于装置区110、120内并局部覆盖所述多个引脚112、122。

34.在此必须说明的是,以下实施例沿用上述实施例的元件标号与部分内容,其中采用相同或近似的标号来表示相同或近似的元件,并且省略了相同技术内容的说明,关于省略部分的说明可参考前述实施例,下述实施例不再重复赘述。

35.图2a是本发明另一实施例的可挠性线路基板的局部俯视示意图。图2b是图2a的区域b的放大示意图。请参考图2a与图2b,本实施例的可挠性线路基板100a类似于上述实施例的可挠性线路基板100,而其差别在于:线路图案114包括对应环绕于每一装置区(如图2a中的装置区110、120)外的金属环(如图2a中的金属环mr1、mr2)。在此,金属环的数量会对应装置区的数量。

36.进一步而言,在本实施例中,线路图案114还包括连接相邻金属环mr1、mr2的至少一第二金属线(如图2a中的第二金属线140a、140b),其中金属环mr1包括位于对应的装置区

110相对两侧的无效区f的第一金属线m11、m12,金属环mr2包括位于对应的装置区120相对两侧的无效区f的第一金属线m21、m22,因此本实施例的线路图案通过金属环的设计可以提供更大的金属接触面积增加导电机率,因此可以更有效地提供静电防护。

37.应说明的是,本发明不限制第二金属线的数量,只要具有至少一第二金属线可以连接相邻的金属环皆属于本发明的保护范围。

38.在一实施例中,相邻金属环mr1、mr2包括位于相同无效区f内的第一金属线m12、m21,且第一金属线m12、m21以第二金属线140a、140b连接,使整个可挠性线路基板的所有装置区可以全面导通,以达到更佳的静电防护效果。

39.在一实施例中,金属环mr1、mr2皆为封闭环型轮廓,以将装置区110、120限定于金属环mr1、mr2内,但本发明不限于此,金属环mr1、mr2可以皆为非封闭环型轮廓。

40.综上所述,本发明的可挠性线路基板可以通过线路图案(包括第一金属线)的设计提供静电防护,且线路图案(包括第一金属线)可以内缩于二个传输区之间,以与二个传输区维持距离,如此一来,线路图案(包括第一金属线)可以避免于可挠性线路基板传输运送时受到齿轮或滚轮等传动机构的摩擦而被刮除并产生金属微粒的情况,因此本发明的可挠性线路基板可以在提供静电防护的同时降低金属微粒污染作业环境且造成芯片电性问题(如短路、漏电或电性异常等)的机率。进一步而言,装置区内的第一引脚电性连接至第一金属线,因此只要作业环境中具有可导电物体(如机台上的构件)接触到第一金属线或包括第一金属线的金属环,装置区内的静电便会经由第一金属线或金属环与前述可导电物体导出,或者,在进行封装结构的最终测试时,由于所有装置区通过每一装置区内的第一引脚、第一金属线与芯片的连接而彼此电性导通,当测试装置探触一个装置区内的第一引脚的第一测试垫即可以一次性将所有装置区内的静电导出,因此通过线路图案(第一金属线或金属环)的设计可以提供整个可挠性线路基板静电防护的功效。

41.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。