1.本发明有关于半导体曝光机校正方法以及半导体结构制造方法。

背景技术:

2.对于半导体晶圆的工艺来说,由于面积上的限制,只能针对主要相关层设计量测用的标记(mark),以供上下两层直接叠对的图案作确认。然而,当形成的层数为四层或以上,则将存在无法设计量测用标记的情况。由于是对于使用不同半导体曝光机来形成的两个次相关半导体层,在缺乏量测用标记,将难以确认两个次相关半导体层的图案之间是否叠对正确,对应也难以确认半导体晶圆上的线路是否符合预期。

3.因此,如何改善上述问题,是所属领域技术人员所欲解决的问题之一。

技术实现要素:

4.本发明的一目的有关于一种半导体曝光机校正方法,其能够修正次相关图案因无法对齐而导致形成结构非预期的短路问题。。

5.根据本发明的一实施方式,一种半导体曝光机校正方法包括以下流程。第一半导体曝光机通过第一光罩图形与第二光罩图形分别形成依序堆叠的第一测试层以及第二测试层。第一测试层与第二测试层分别具有第一图案与第二图案。第二半导体曝光机通过第三光罩图形在第二测试层上堆叠第三测试层。第三测试层具有第三图案。通过电子显微镜量测第一测试层上的第一图案与第三测试层上的第三图案之间的叠对误差。根据叠对误差校准第一半导体曝光机以及第二半导体曝光机。

6.在本发明一或多个实施方式,叠对误差包括第一图案与第三图案之间的水平偏移。

7.在一些实施方式中,在根据叠对误差校准第一半导体曝光机以及第二半导体曝光机的流程中,第二半导体曝光机根据叠对误差向多个光罩图形提供同一个补偿相差,光罩图形包括形成第三图案的第三图案光罩图形。

8.在本发明一或多个实施方式,第一图案与第二图案设置使通道穿过第一测试层以及第二测试层。第三测试层延伸至通道内。

9.在一些实施方式中,前述的半导体曝光机校正方法进一步包括以下流程。第二半导体曝光机通过第四光罩图形在第三测试层上堆叠第四测试层。第四测试层包括第四图案。通过电子显微镜量测第二测试层上的第二图案与第四测试层上的第四图案之间的叠对误差。

10.在本发明一或多个实施方式,第四测试层延伸至第二测试层。

11.在本发明一或多个实施方式,前述的半导体曝光机校正方法进一步包括以下流程。在第四测试层形成后,量测第二测试层上多个导电图案中任意两个导电图案是否短路。

12.在一些实施方式中,电子显微镜包括扫描式电子显微镜(sem)。

13.本发明的一目的有关于一种半导体结构制造方法。

14.根据本发明的一实施方式,一种半导体结构制造方法包括以下流程。提供通过如前所述的半导体曝光机校正方法校准的第一半导体曝光机与第二半导体曝光机。通过第一半导体曝光机以第一光罩图形与第二光罩图形分别形成依序堆叠第一半导体图案层以及第二半导体图案层。通过第二半导体曝光机以第三光罩图形与第四光罩图形分别形成依序堆叠第二半导体图案层的第三半导体图案层以及第四半导体图案层,以形成半导体结构。

15.在本发明一或多个实施方式,前述的半导体结构制造方法进一步包括以下流程。切割半导体结构为多个裸片。量测这些裸片的良率。

16.综上所述,本发明提供的半导体曝光机校正方法,能够修正次相关图案因无法对齐而导致非预期的短路问题。

17.应理解到,以上的一般说明与以下的详细描述都是通过示例做进一步说明,旨在为本发明提供做进一步的解释。

附图说明

18.本发明的优点与附图,应由接下来列举的实施方式,并参考附图,以获得更好的理解。这些附图的说明仅仅是列举的实施方式,因此不该认为是限制了个别实施方式,或是限制了权利要求的范围。

19.图1根据本发明的一实施方式绘示一半导体曝光机校正方法的一流程图;

20.图2根据本发明的一实施方式绘示一半导体结构制造方法的一流程图;

21.图3至图4根据本发明的一实施方式绘示半导体曝光机校正方法不同流程的结构的剖面图;

22.图5a至图5c绘示测试半导体结构不同图案叠对的多个俯视示意图;

23.图6至图7根据本发明的一实施方式绘示半导体结构制造方法不同流程的结构的剖面图;以及

24.图8a至图8c绘示形成的半导体结构不同图案叠对的多个俯视示意图。

25.主要附图标记说明:

26.100-半导体曝光机校正方法;110~140-流程;200-半导体结构制造方法;210~230-流程;310-第一测试层;310a-第一图案部分;315-通道;330-第二测试层;330a,330b-导电图案;335-通道;340-间隔;345-总成通道;350-第三测试层;350a,350b,350c,350d,350e,350f-第三图案部分;350g-第三图案部分;370-第四测试层;370a,370b-第四图案部分;400-半导体结构;410-第一半导体图案层;410a-第一图案部分;415-通道;430-第二半导体图案层;430a,430b-导电图案;435-通道;440-间隔;445-总成通道;450-第三半导体图案层;450a,450b,450c,450d,450e,450f-第三图案部分;450g-第三图案部分;470-第四半导体图案层;470a,470b-第四图案部分;w1,w2-宽度;d-偏移;d1,d2,d3,d4-距离。

具体实施方式

27.下文列举实施例配合所附附图进行详细说明,但所提供的实施例并非用以限制本发明所涵盖的范围,而结构运作的描述非用以限制其执行的顺序,任何由元件重新组合的结构,所产生具有均等功效的装置,皆为本发明所涵盖的范围。另外,附图仅以说明为目的,并未依照原尺寸作图。为使便于理解,下述说明中相同元件或相似元件将以相同的符号标

示来说明。

28.除非另有定义,本文所使用的所有词汇(包括技术和科学术语)具有其通常的意涵,其意涵是能够被熟悉此领域的技术人员所理解。更进一步的说,上述的词汇在普遍常用的字典中的定义,在本说明书的内容中应被解读为与本发明相关领域一致的意涵。除非有特别明确定义,这些词汇将不被解释为理想化的或过于正式的意涵。

29.关于本文中所使用的“第一”、“第二”、

…

等,并非特别指称次序或顺位的意思,亦非用以限定本发明,其仅仅是为了区别以相同技术用语描述的元件或操作而已。

30.其次,在本文中所使用的用词“包含”、“包括”、“具有”、“含有”等等,均为开放性的用语,即意指包含但不限于。

31.再者,在本文中,除非内文中对于冠词有所特别限定,否则“一”与“该”可泛指单一个或多个。将进一步理解的是,本文中所使用的“包含”、“包括”、“具有”及相似词汇,指明其所记载的特征、区域、整数、步骤、操作、元件与/或组件,但不排除其所述或额外的其一个或多个其它特征、区域、整数、步骤、操作、元件、组件,与/或其中的群组。

32.为解决次相关半导体叠层难以量测图案之间叠对误差问题,本发明提供半导体曝光机校正方法,以及基于本发明半导体曝光机校正方法结果来进行的半导体结构制造方法。

33.请依序参照图1、图2。图1根据本发明的一实施方式绘示的半导体曝光机校正方法100的流程图。图2根据本发明的一实施方式绘示的半导体结构制造方法200的流程图。图2所绘示的半导体结构制造方法200,能够基于半导体曝光机校正方法100的校正结果来进行。

34.为进一步说明本发明的一半导体曝光机校正方法100,请先依序参照图3与图4。图3至图4根据本发明的一实施方式绘示半导体曝光机校正方法100不同流程的结构的剖面图。应留意到,图3至图4仅示例地绘示叠对部分的局部,而不应以此限制本发明。

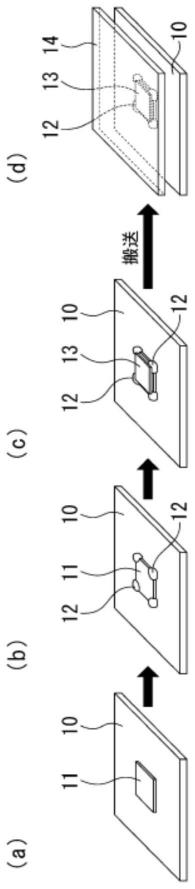

35.在本实施方式中,使用的半导体曝光机包括曝光机,因此后述的第一半导体曝光机与第二半导体曝光机例如分别为第一曝光机与第二曝光机。第一曝光机与第二曝光机能够通过设计的光罩图形来形成图案化的半导体层。但本发明并不以此限制半导体曝光机的类型。

36.在一些实施方式中,图案化的半导体层是形成于半导体晶圆或是半导体基板上,多个叠对的图案化半导体层形成半导体结构,形成的半导体结构经切割能够形成多个裸片。为了简单说明的目的,半导体晶圆或是半导体基板被省略而未绘示。

37.请同时参照图1与图3。在流程110,通过第一半导体曝光机形成依序堆叠的第一测试层310以及第二测试层330。

38.在本实施方式中,如前所述,第一半导体曝光机通过第一光罩图形形成图案化的第一测试层310,第一测试层310具有第一图案。如图3所示,在本实施方式中,图案化的第一测试层310包括通道315。

39.在图3中,通过第二光罩图形,第一半导体曝光机形成图案化的第二测试层330。第二测试层330堆叠在第一测试层310上。第二测试层330具有第二图案。在本实施方式中,第二测试层330也包括通道335,并且图案化的第二测试层330还包括间隔340。间隔340具有宽度w1。

40.在本实施方式中,第二测试层330的第二图案在通道335之间包括两个分离的导电图案330a与导电图案330b,并且导电图案330a与导电图案330b之间存在间隔340。

41.请回到图1,并同时参照图4。在流程120,通过第二半导体曝光机形成依序堆叠于第二测试层330的第三测试层350。在本实施方式中,如图4所示,在第三测试层350上,可以进一步堆叠第四测试层370。

42.如前所述,第二半导体曝光机通过第三光罩图形与第四光罩图形来分别形成图案化的第三测试层350以及第四测试层370。第三测试层350与第四测试层370分别具有第三图案与第四图案。

43.如图4所示,第三测试层350对准第一测试层310的通道315以及第二测试层330的通道335设置。换言之,通道315与通道335形成一个穿过第一测试层310与第二测试层330的总成通道345,而第三测试层350设置形成延伸于总成通道345上,从而在总成通道345内相邻于第一测试层310。在图3与图4中,通道315与通道335形成的总成通道345以虚线呈现。于总成通道345上,第四测试层370堆叠于第三测试层350上。

44.然而,如图4所示,一旦第一半导体曝光机与第二半导体曝光机之间存在非预期的偏差/机差,将使得图案化的第三测试层350相对于第一测试层310存在非预期的偏移。如图4所示,虽然图案化的第三测试层350设计上对准通道315与通道335,但由于第一半导体曝光机与第二半导体曝光机之间存在非预期的偏差/机差,使得第三测试层350相对总成通道345具有水平偏移d,以致于部分的第三测试层350重叠到图案化的第一测试层310与第二测试层330。

45.此外,如图4所示,在本实施方式中,图案化的第四测试层370形成堆叠于第三测试层350上,第四测试层370的第四图案部分370a设计连接第二测试层330上以间隔340分离的导电图案330a与导电图案330b其中之一。然而,由于第一半导体曝光机与第二半导体曝光机之间非预期的偏差/机差,使得第四测试层370同时连接到第二测试层330的两个应电性分离的导电图案330a与导电图案330b。如此一来,将可能会产生非预期的短路。

46.如图4所示第四测试层370于总成通道345外具有与第二测试层330相连的部分,第四测试层370与第二测试层330相连的部分具有宽度w2,宽度w2大于宽度w1。因此,一旦发生偏离,第四测试层370将可能同时连接第二测试层330上两个应分离的导电图案330a与导电图案330b,产生非预期的短路。

47.在一些实施方式中,也可以通过测试第二测试层330上应分离的导电图案330a与导电图案330b之间是否短路,来确认第二测试层330与第四测试层370之间是否存在叠对误差。

48.在图4中,在第三测试层350与第四测试层370形成后,依序堆叠的第一测试层310、第二测试层330、第三测试层350以及第四测试层370能够参照作为一个测试半导体结构。通过确认第一测试层310、第二测试层330、第三测试层350以及第四测试层370之间的叠对情况,将能够获得第一半导体曝光机与第二半导体曝光机之间存在的非预期的偏差/机差。

49.请回到图1。在流程130,通过电子显微镜量测第一测试层310的第一图案与第三测试层350的第三图案之间的叠对误差。在本实施方式中,所使用的电子显微镜包括扫描式电子显微镜(scanning electron microscope)。

50.图5a至图5c绘示的第一测试层310、第二测试层330、第三测试层350以及第四测试

层370形成的测试半导体结构不同图案叠对的多个俯视示意图。

51.同时参照图1与图5a。图5a绘示电子显微镜下,第一测试层310与第三测试层350叠对的一局部。由于直接通过电子显微镜来观察,将能够确认光罩模拟软体上未能呈现到的第一半导体曝光机与第二半导体曝光机之间的叠对机差。在图5a绘示的局部中,第一测试层310包括类方形的第一图案部分310a,第三测试层350包括第三图案部分350a、第三图案部分350b、位于第一图案部分310a上的长条第三图案部分350c与第三图案部分350d、第三图案部分350e以及第三图案部分350f。第三图案部分350a于第三图案部分350b设置于类方形的第一图案部分310a左侧。第三图案部分350e于第三图案部分350f设置于类方形的第一图案部分310a右侧。

52.在预定的设计与光罩软体的模拟中,在图5a绘示的局部,第三测试层350应对称叠对于第一测试层310上,意即,第三图案部分350a~350f相对类方形的第一图案部分310a,应是对称分布的。相对于第一图案部分310a,第三图案部分350a、350b与第三图案部分350e、350f应设置为对称地相对,长条的第三图案部分350c对第一图案部分310a右边缘的距离应设计等同于第三图案部分350d对第一图案部分310a左边缘的距离。然而,由于第一测试层310与第三测试层350非预期的叠对误差,使得第三测试层350相对第一测试层310偏移。如图5a所示,对于第三测试层350的第三图案来说,中间的二长条的第三图案部分350c与第三图案部分350d相对第一测试层310的类方形的第一图案部分310a相对二边缘的距离并不相等。第三测试层350左边的长条第三图案部分350d相对类方形第一图案部分310a左边缘距离d1,第三测试层350右边的长条第三图案部分350c相对类方形右边缘距离d2,而距离d2大于距离d1,说明第三测试层350相对第一测试层310是向左偏移。

53.图4的水平偏移d,对应为二分之一的距离d2减去二分之一的距离d1。

54.图5b绘示通过电子显微镜获得的第三测试层350与第四测试层370叠对的局部。由于第三测试层350与第四测试层370同为第二半导体曝光机所形成,因此第三测试层350与第四测试层370之间不会有叠对误差。如图5b所示,第三测试层350的椭圆第三图案部分350g设置于第四测试层370的第四图案部分370b的椭圆孔的中心,符合预期设计。若第三测试层350与第四测试层370在叠对上存在错位或偏移,由于第三测试层350与第四测试层370同为第二半导体曝光机所形成,第二半导体曝光机的光罩模拟软体应当即时反映。一般而言,同为第二半导体曝光机形成的第三测试层350与第四测试层370,之间应不会有叠对误差。

55.图5c绘示通过电子显微镜获得的第二测试层330与第四测试层370叠对的一局部。其中第二测试层330的第四测试层370之间为次相关的叠对关系,因此并无设计用以量测对准的测量标记。此时,通过电子显微镜,来确认叠对是否对准。

56.如图5c所示,第二测试层330包括多个长条的导电图案330a与330b,其中两个长条为一组作为彼此应以间隔340隔开的导电图案330a与330b。然而,由于第一半导体曝光机与第二半导体曝光机之间的叠对机差,致使由第一半导体曝光机形成的第二测试层330与第二半导体曝光机形成的第四测试层370的第四图案部分370a之间存在叠对误差,从而使得图案化的第四测试层370的第四图案部分370a连接第二测试层330的两个应分离的长条导电图案330a与330b,产生非预期的短路。

57.从图5a至图5c可知,首先,由于不同的第一半导体曝光机与第二半导体曝光机之

间的叠对机差,使得第一测试层310与第二测试层330相对第三测试层350与第四测试层370存在叠对误差。再者,由于第一半导体曝光机与第二半导体曝光机为不同机台,因此各自的光罩模拟软体无法反映第一半导体曝光机与第二半导体曝光机之间的叠对机差,因此第一测试层310与第二测试层330相对第三测试层350与第四测试层370存在叠对误差。而对于同一半导体曝光机的叠对,通常是能够符合预期设计的,如图5b所示的第三测试层350以及第四测试层370,第四测试层370的椭圆第四图案部分370b能够符合设计地设置于第三测试层350的第三图案部分350g的椭圆孔的中心。

58.因此,回到图1。在流程140,在根据流程130得出的叠对误差后,根据叠对误差来校准第一半导体曝光机与第二半导体曝光机。举例而言,以第一半导体曝光机为基准来校准第二半导体曝光机。具体而言,第二半导体曝光机的校正,可以通过提供用于修正的补偿相差来实现。意即,在后续的制造流程中,在第一半导体曝光机的光罩与第二半导体曝光机的光罩都设计完后,在第二半导体曝光机执行时,第二半导体曝光机于形成的图案都加上一个额外的补偿相差。

59.例如,在本实施方式中,在后续通过第三光罩图形与第四光罩图形来形成具第三图案与第四图案的半导体层时,对第三光罩图形与第四光罩图形都提供一个补偿相差,使得第三图案与第四图案的位置都能够获得一个补偿的水平偏移d。如此一来,以图5a的第三测试层350为例,将能够使得第三测试层350的第三图案与第一测试层310的第一图案回到设计的对称关系,即第三图案对准第一图案,而这对应到图5c中第四测试层370的第四图案部分370a亦能被修正,使第二测试层330邻近的导电图案330a与导电图案330b不再电性相接。

60.基于第一测试层310与第三测试层350之间的叠对误差,能够使第一半导体曝光机与第二半导体曝光机之间的叠对机差能够通过补偿相差偏移的方式获得校准。在根据叠对误差校准第二半导体曝光机的流程中,第二半导体曝光机根据叠对误差向多个光罩图形提供同一个补偿相差,光罩图形包括形成第三图案的第三图案光罩图形。如此一来,由于第一测试层310的第一图案与第三测试层350的第三图案叠对能够对准,次相关的第二测试层330的第二图案与第四测试层370的第四图案也将能够对准。

61.请回到图2。在半导体结构制造方法200的流程210中,提供校准的第一半导体曝光机以及第二半导体曝光机。流程210的校准,即通过本发明的一实施方式的半导体曝光机校正方法100来实现。

62.图6至图7根据本发明的一实施方式绘示半导体结构制造方法200不同流程的结构的剖面图。请参照图2,并依序参照图6与图7,以进一步说明半导体结构制造方法200。

63.在流程220,通过第一半导体基台形成依序堆叠的第一半导体图案层410与第二半导体图案层430。第一半导体图案层410具有第一图案,因此与第一测试层310相近而具有通道415。第二半导体图案层430具有第二图案,因此也具有通道435以及间隔440,间隔440分离第二半导体图案层430的导电图案430a与导电图案430b,如图6所示。

64.进入流程230,通过第二半导体曝光机形成依序堆叠于第二半导体图案层430的第三半导体图案层450以及第四半导体图案层470。

65.如图7所示,第三半导体图案层450以及第四半导体图案层470也分别具有第三图案以及第四图案,因此分别相似于第三测试层350与第四测试层370。然而,通过流程210的

校正后,第三半导体图案层450能够对准通道415与通道435形成的总成通道445做设置,并且第四半导体图案层470的第四图案部分470a不会横跨第二半导体图案层430位于总成通道445外以间隔440分离的导电图案430a与导电图案430b。

66.如此一来,经历半导体结构制造方法200的流程210至流程230,半导体结构400成形。

67.图8a至图8c绘示形成的半导体结构400不同图案叠对的多个俯视示意图。

68.图8a绘示第一半导体图案层410与第三半导体图案层450的叠对的局部。如图8a所示,第一半导体图案层410包括第一图案部分410a,第三半导体图案层450包括第三图案部分450a、第三图案部分450b、长条的第三图案部分450c与第三图案部分450d、第三图案部分450e以及第三图案部分450f。对于第三半导体图案层450的第三图案来说,中间的二长条第三图案部分450c与第三图案部分450d相对第一半导体图案层410的类方形的第一图案部分410a的相对二边的距离相等。第三半导体图案层450左边的长条第三图案部分450d相对类方形第一图案部分410a左边距离d3,第三半导体图案层450右边的长条第三图案部分450c相对类方形第一图案部分410a右边距离d4,而距离d3等于距离d4。这对应到,第三图案部分450a、450b以及第三图案部分450e、450f相对于类方形第一图案部分410a是对称地相对的,例如第三图案部分450a到第一图案部分410a右边的距离等同第三图案部分450e到第一图案部分410a左边的距离,说明第一半导体图案层410与第三半导体图案层450符合预期的对称叠对设计。

69.图8b绘示通过电子显微镜获得的第三半导体图案层450与第四半导体图案层470叠对的局部。由于第三半导体图案层450与第四半导体图案层470同为第二半导体曝光机所形成,因此第三半导体图案层450与第四半导体图案层470之间不会有叠对误差。如图8b所示,第四半导体图案层470的椭圆第四图案部分470b设置于第三半导体图案层450的第三图案部分450g的椭圆孔的中心,符合预期设计。

70.图8c绘示通过电子显微镜获得的第二测试层330与第四半导体图案层470叠对的局部。如图8c所示,由于第二半导体曝光机已校准,第四半导体图案层470的第四图案部分470a不会同时连接到第二半导体图案层430的两个分离的导电图案430a与430b。

71.在一些实施方式中,于半导体结构400成形后,能够切割半导体结构400为多个裸片。量测这些裸片的良率。如此,也能够确认半导体图案层叠层是否还存在偏移。若有,则能够记录下来,以供后续制造工艺参考。

72.综上所述,本发明提供的半导体曝光机校正方法,能够修正次相关图案因无法对齐而导致非预期的短路问题。基于上述的校正,制造出的半导体结构次相关的图案彼此之间能够对准。揭露提供的半导体曝光机校正方法以及半导体结构制造方法,能够应用在两个或以上半导体曝光机形成的多层叠对结构上。半导体曝光机例如是黄光曝光机。

73.虽然本发明已以实施例公开如上,然其并不用以限定本发明,任何所属领域的技术人员,在不脱离本发明的精神和范围内,当可作各种的更动与润饰,因此本发明的保护范围当视权利要求所界定的为准。

74.对于本领域技术人员将显而易见的是,在不脱离本公开的范围或精神的情况下,可以对本发明实施例的结构进行各种修改和变化。鉴于前述内容,本发明旨在覆盖各种的修改与变形,只要它们落入权利要求的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。