1.本发明涉及一种导线架,尤其涉及一种导线架及其运用于半导体封装结构的制作方法。

背景技术:

2.目前的无引脚小尺寸封装(small outline no-lead,son),由于该种封装型态侧边填充有封装胶材,其仅通过封装结构底部外露的局部引脚与外部电路板接触做为电性连接的途径。因此,于接合于外部电路板之后,由于电性连接的引脚位于封装结构底部,无法通过外观检查来确认其与电路板的连接状况,不利于后续的电性及品质检查。此外,无引脚小尺寸封装的封装结构在进行切割程序时,由于刀具需切割掉并排的导线架形成单体化封装结构。倘若刀具需切割的金属部分较多时,基于金属材质的导线架的材料特性因素,将使得导线架的切割边缘易因刀具的旋转带动而于边缘形成金属毛边,如此一来,将存在着电性短路的潜在风险。

技术实现要素:

3.本发明是针对一种导线架及其运用于半导体封装结构的制作方法,其可达到减少毛边的产生与改善封装结构与外部的结合以利于后续的品质检查。

4.根据本发明的实施例,导线架包括多个封装区域以及连接封装区域的多个连接部。每一封装区域包括承载座以及环绕承载座的外引脚部。外引脚部包括朝周边延伸的多个引脚。每一连接部连接相邻两外引脚部的引脚且与两相邻的引脚定义出第一凹槽与第二凹槽。第二凹槽位于第一凹槽与对应的连接部之间,且第二凹槽的槽宽小于第一凹槽的槽宽。

5.在根据本发明的实施例的导线架中,上述的每一引脚具有彼此相对的顶面与底面,第一凹槽由底面往顶面的方向延伸,且每一引脚的高度等于第一凹槽的深度、第二凹槽的深度与对应的连接部的厚度的总和。

6.在根据本发明的实施例的导线架中,上述的第一凹槽的深度大于等于每一引脚的高度的1/2。

7.在根据本发明的实施例的导线架中,上述的第二凹槽的深度小于等于第一凹槽的深度的1/3。

8.在根据本发明的实施例的导线架中,上述的每一连接部具有彼此相对的外表面与内表面,外表面切齐于每一引脚的顶面,而内表面为第二凹槽的底部。

9.在根据本发明的实施例的导线架中,上述的每一引脚的底面与承载座的第一下表面切齐于封装胶体的第二下表面。

10.在根据本发明的实施例的导线架中,上述的第二凹槽的槽宽小于等于对应的连接部的长度。

11.在根据本发明的实施例的导线架中,上述的第一凹槽的槽宽大于对应的连接部的

长度。

12.根据本发明的实施例,导线架运用于半导体封装结构的制作方法,其包括以下步骤。提供导线架。导线架包括多个封装区域以及连接封装区域的多个延伸部。每一封装区域包括承载座以及环绕承载座的外引脚部。外引脚部包括朝周边延伸的多个引脚。每一延伸部连接相邻两外引脚部的引脚,且两引脚与对应的延伸部定义出第一凹槽。对延伸部进行蚀刻程序,而形成多个连接部,并于两引脚之间形成第二凹槽。每一连接部连接相邻两引脚,且第二凹槽位于第一凹槽与对应的连接部之间。第二凹槽的槽宽小于第一凹槽的槽宽。配置至少一芯片于导线架的至少一承载座上并电性连接于多个引脚。形成封装胶体以包覆导线架与芯片。封装胶体填满第一凹槽与第二凹槽。

13.在根据本发明的实施例的导线架用于半导体封装结构的制作方法中,上述的两引脚与对应的连接部上形成有第一切割道与第二切割道。第一切割道的宽度大于等于第一凹槽的槽宽,而第二切割道的宽度大于等于第二凹槽的槽宽。于形成封装胶体以包覆导线架与芯片之后,还包括以下步骤。沿着第一切割道进行第一切割程序,以移除第一凹槽内的封装胶体。沿着第二切割道进行第二切割程序,以移除第二凹槽内的封装胶体及对应的连接部,而分开引脚。形成单体化的半导体结构。

14.基于上述,在本发明的导线架的设计中,导线架的连接部与相邻两引脚定义出第一凹槽与第二凹槽,除了可在后续二阶段的切割程序时减少金属毛边的产生及避免短路之外,亦可通过所形成的凹陷来提高与焊料的接触面积,进而可提升半导体结构与外部端子的结合良率且有利于后续检查。

附图说明

15.图1a至图1e是依照本发明的一实施例的一种导线架运用于半导体封装结构的制作方法的剖面示意图。

16.附图标记说明

17.10:半导体封装结构;

18.100、100’:导线架;

19.110:承载座;

20.110a:第一上表面;

21.110b:第一下表面;

22.120:外引脚部;

23.122:引脚;

24.122a:顶面;

25.122b:底面;

26.122c:侧面;

27.126:第一凹槽;

28.128:第二凹槽;

29.200:芯片;

30.210:打线;

31.300:封装胶体;

32.300a:侧表面;

33.300b:第二下表面;

34.b1、b2:槽宽;

35.c:连接部;

36.c1:第一切割道;

37.c2:第二切割道;

38.d1、d2:深度;

39.e:延伸部;

40.e1、s2:内表面;

41.g:凹陷;

42.h:高度;

43.l:长度;

44.r:封装区域;

45.s1:外表面;

46.t:厚度。

具体实施方式

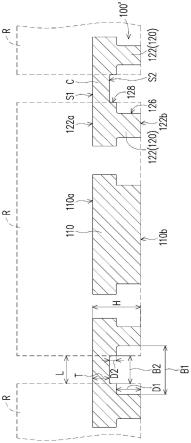

47.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

48.以下将参考附图来全面地描述本发明的例示性实施例,但本发明还可按照多种不同形式来实施,且不应解释为限于本文所述的实施例。在附图中,为了清楚起见,各区域、部位及层的大小与厚度可不按实际比例绘制。为了方便理解,下述说明中相同的元件将以相同的符号标示来说明。

49.图1a至图1e是依照本发明的一实施例的一种导线架运用于半导体封装结构的制作方法的剖面示意图。本实施例的导线架运用于半导体封装结构的制作方法包括下列步骤,首先,请参照图1a,提供导线架100(leadframe strip)。详细来说,本实施例的导线架100包括多个封装区域(示意地示出三个封装区域r)以及连接封装区域r的多个延伸部(示意地示出二个延伸部e)。每一封装区域r包括承载座110以及外引脚部120。外引脚部120环绕承载座110,且包括朝周边延伸的多个引脚122。此处,每一延伸部e连接相邻两外引脚部120的引脚122。相邻两引脚122与对应的延伸部e共同定义出第一凹槽126。如图1a所示,承载座110受到外引脚部120的围绕,由剖面图看来,承载座110位于两个引脚122之间。此处,承载座110、外引脚120以及延伸部e的材质例如是相同,例如金属或金属合金,如铜或铜合金,但不以此为限。特别是,外引脚部120的多个引脚122围绕承载座110不以四边为限,于某些可行的实施例中,引脚122亦可并列围绕于承载座110的两边。

50.请同时参照图1a与图1b,对延伸部e的内表面e1更进行蚀刻程序后,而形成多个连接部c,并于两引脚122之间形成第二凹槽128。此蚀刻程序仅移除部分的延伸部e,而形成与导线架100的顶部距离更短,意即厚度较薄的连接部c及两引脚122之间的第二凹槽128。如图1b所示,在本实施例中,每一连接部c连接相邻两外引脚部120的引脚122,而第二凹槽128位于第一凹槽126与对应的连接部c之间。特别是,第二凹槽128的槽宽b2小于第一凹槽126

的槽宽b1。至此,已完成导线架100’的制作。

51.在结构上,请再参考图1b,本实施例的导线架100’包括封装区域r以及连接封装区域r的连接部c。封装区域r包括承载座110以及外引脚部120。外引脚部120环绕承载座110,且包括朝周边延伸的引脚122。承载座110具有第一下表面110b与相对第一下表面110b的第一上表面110a。每一引脚122具有彼此相对的顶面122a与底面122b,其中承载座110的第一下表面110b实质上切齐于引脚122的底面122b。每一连接部c具有彼此相对的外表面s1与内表面s2,且每一连接部c的外表面s1切齐于每一引脚122的顶面122a。特别是,每一连接部c连接两相邻封装区域r中的两外引脚部120的引脚122,且与两相邻引脚122共同定义出第一凹槽126与第二凹槽128。第一凹槽126由引脚122的底面122b往引脚122的顶面122a方向延伸。第二凹槽128位于第一凹槽126与对应的连接部c之间,其中连接部c的内表面s2为第二凹槽128的底部。

52.请再参考图1b,在本实施例中,每一引脚122的高度h例如是等于第一凹槽126的深度d1、第二凹槽128的深度d2与对应的连接部c的厚度t的总和。第一凹槽126的深度d1例如是大于等于每一引脚122的高度h的1/2,而第二凹槽128的深度d2例如是小于等于第一凹槽126的深度d1的1/3。第二凹槽128的槽宽b2小于第一凹槽126的槽宽b1。第二凹槽128的槽宽b2例如是小于等于对应的连接部c的长度l,而第一凹槽126的槽宽b1大于对应的连接部c的长度l。此处,第二凹槽128的槽宽b2是以等于对应的连接部c的长度l作为举例说明。值得一提的是,由于连接部c的长度l是为后续切割制程中被刀具去除的部分,因此,连接部c的长度l可与第二凹槽128的槽宽相同,或亦可依据后续切割制程中的第二次切割刀具的刀宽或切割道来决定连接部c的长度l。一般业界常见的导线架100厚度约为150微米至210微米左右。每一引脚122的高度h例如是约为152微米,而第一凹槽126的深度d1例如是约为100微米,且第二凹槽128的深度d2例如是约为25微米。于另一可行的实施例中,每一引脚122的高度h例如是203微米,而第一凹槽126的深度d1例如是约为134微米左右,且第二凹槽128的深度d2例如是约为34微米,但不限于此。于另一较佳的实施例中,第一凹槽126与第二凹槽128的槽面上亦可进一步地实施电镀制程,使这些凹槽的表面具有一层电镀金属层(未示出)例如锡或锡合金,以利于后续焊接上板。

53.在应用上,请参照图1c,配置至少一芯片(示意地示出一个芯片200)于导线架100’上,其中芯片200位于导线架100’的承载座110的第一上表面110a上,且以打线210连接的方式电性连接外引脚部120。此处,芯片200可借由黏着层(未示出)而固定于承载座110上,但不限于此。

54.之后,请同时参考图1c与图1d,形成封装胶体300以包覆导线架100’、芯片200以及打线210,且填满外引脚部120的第一凹槽126与第二凹槽128。此处,封装胶体300的材质例如是环氧树脂或其他适合的封装材料,但不限于此。如图1d所示,每一引脚122的底面122b与承载座110的第一下表面110b切齐于封装胶体300的第二下表面300b。意即,封装胶体300的第二下表面300b与每一引脚122的底面122b以及承载座110的第一下表面110b实质上共平面。

55.最后,请同时参考图1d与图1e,在两相邻的封装区域r的两相邻引脚122与对应的连接部c上形成第一切割道c1与第二切割道c2。此处,第一切割道c1的宽度大于等于第一凹槽126的槽宽b1,而第二切割道c2的宽度大于等于第二凹槽128的槽宽b2。值得注意的是,第

一切割道c1与第二切割道c2的宽度尺寸依据是参考所采用的切割刀具的刀宽为主。

56.紧接着,沿着第一切割道c1进行第一切割程序,以移除外引脚部120的第一凹槽126内的封装胶体300。意即,第一切割程序并未完全将引脚122分开,而是进行半切制程移除第一凹槽126内的封装胶体300。之后,沿着第二切割道c2进行第二切割程序,以移除外引脚部120的第二凹槽128内的封装胶体300、第二凹槽128对应的连接部c以及连接部c的外表面s1上的封装胶体300,而分开引脚122以形成单体化的半导体封装结构10。此时,封装胶体300的侧表面300a切齐于引脚122的侧面122c,且引脚122于底面122b与侧面122c之间形成有凹陷g,以露出引脚122的侧表面,增加后续焊料的接触面积、提升接合良率及相关的可靠度检查。至此,已完成本实施例的导线架100’运用于半导体封装结构10的制作。

57.简言之,在本实施例的导线架100’中,连接部c连接相邻两外引脚部120的引脚122且与两相邻引脚122定义出第一凹槽126与第二凹槽128。第一凹槽126与第二凹槽128的设计,在后续进行二阶段的切割程序时,由于被刀具切割的金属部分减少,因而可减少金属毛边的产生且可避免产生短路风险。此外,第一凹槽126与第二凹槽128的设计,在后续进行二阶段的切割程序之后,可在引脚122的底面122b与侧面122c处形成凹陷g,可提高与焊料的接触面积,进而可提升半导体结构10与外部端子的结合良率且有利于后续检查。

58.综上所述,在本发明的导线架的设计中,导线架的连接部与相邻两引脚共同定义出重迭的第一凹槽与第二凹槽,除了可在后续二阶段的切割程序时减少金属毛边的产生及避免产生短路之外,亦可通过所形成的凹陷来提高与焊料的接触面积,进而可提升半导体结构与外部端子的结合良率且有利于后续检查。

59.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。