1.本技术涉及显示设备技术领域,尤其涉及一种阵列基板母板及其制备方法、显示面板母板。

背景技术:

2.请参阅图1、图2和图3,图1是不合格的阵列基板母板示意图,图2是传统的焊盘剖面结构示意图,图3为传统的洗边标识设计。在阵列基板母板的制备过程中,由于传统工艺中仅设置了第一洗边标识41和第二洗边标识61,分别对第一金属层和第二金属层进行洗边,因此在阵列基板区域的周边仍留下大量的透明导电膜,由于膜层边缘的成膜质量不佳,尤其是阵列基板区域周边焊盘位置的透明导电膜层面积较大,因此在清洗过程中焊盘位置的透明导电膜层容易从焊盘脱落,产生透明导电膜碎屑(如图1中黑点所示)。脱落的透明导电膜碎屑在清洗过程中被毛刷和水流带进阵列基板区域内,导致阵列基板母板的成品合格率降低。

技术实现要素:

3.本技术实施例提供一种不容易产生透明导电膜碎屑,成品合格率较高的阵列基板母板。

4.第一方面,本技术提供一种阵列基板母板。阵列基板母板包括阵列基板区域和测试区域,测试区域位于阵列基板区域周边,测试区域电连接阵列基板区域,其特征在于。

5.测试区域包括虚拟焊盘。虚拟焊盘包括阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘。阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘均电连接阵列基板区域。

6.阵列基板母板包括透明导电膜层。透明导电膜层在基准面的投影与阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘两者中至少一个在基准面的投影错开。基准面为阵列基板母板的所在平面。

7.在一种可能实现的方式中,测试区域还包括测试焊盘。测试焊盘包括阵列基板测试焊盘和细缝垂直对准焊盘,阵列基板测试焊盘电连接阵列基板区域,细缝垂直对准焊盘电连接阵列基板区域。透明导电膜层在基准面的投影与阵列基板测试焊盘和细缝垂直对准焊盘两者中至少一个在基准面的投影错开。

8.在一种可能实现的方式中,透明导电膜层在所述基准面的投影与测试区域在所述基准面的投影错开。

9.在一种可能实现的方式中,阵列基板母板包括钝化保护层和基板,钝化保护层和基板从测试区域延伸至阵列基板区域,钝化保护层位于基板和透明导电膜层之间。虚拟焊盘在基板的投影与钝化保护层在基板的投影错开,钝化保护层围绕焊盘设置。

10.第二方面,本技术提供一种显示面板母板。一种显示面板母板包括彩膜基板母板、液晶层以及阵列基板母板,液晶层位于阵列基板母板和彩膜基板母板之间。

11.第三方面,本技术提供一种阵列基板母板的制备方法。阵列基板母板的制备方法

包括:

12.在基板的第一区域内形成阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘,以及在基板的第二区域形成薄膜晶体管。

13.在薄膜晶体管上形成透明导电膜层,透明导电膜层在基准面的投影与阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘两者中至少一个在基准面的投影错开,基准面为基板的所在平面。

14.在一种可能实现的方式中,在基板的第一区域内形成阵列基板测试焊盘和细缝垂直对准焊盘。透明导电膜层在基准面的投影与阵列基板测试焊盘和细缝垂直对准焊盘两者中至少一个在基准面的投影错开。

15.在一种可能实现的方式中,在薄膜晶体管上形成透明导电膜层,透明导电膜层在基准面的投影与阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘两者中至少一个在基准面的投影错开,基准面为基板的所在平面的步骤中包括:

16.形成待处理透明导电膜层,待处理透明导电膜层覆盖阵列基板测试虚拟焊盘、细缝垂直对准虚拟焊盘以及薄膜晶体管。

17.去除阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘上的处理透明导电膜层。

18.在一种可能实现的方式中,待处理透明导电膜层包括第三洗边标识。部分第三洗边标识在基准面的投影与阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘两者中至少一个在基准面的投影重合,第三洗边标识用于去除阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘两者中至少一个上的处理透明导电膜层。

19.在一种可能实现的方式中,部分第三洗边标识在基准面的投影与阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘两者中至少一个在基准面的投影重合,第三洗边标识用于去除阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘两者中至少一个上的处理透明导电膜层。

20.可以理解的是,设置透明导电膜层时绕开测试区域的虚拟焊盘,减少了测试区域的透明导电膜层面积。降低了由于透明导电膜成膜边缘质量不佳容易产生碎屑,从而导致阵列基板母板的良率降低的发生概率。

附图说明

21.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

22.图1是不合格的阵列基板母板示意图;

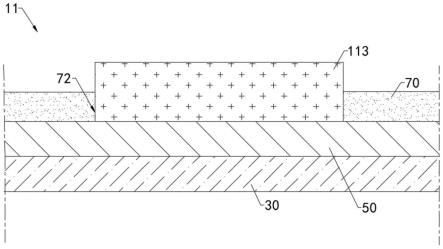

23.图2是传统的焊盘剖面结构示意图;

24.图3为传统的洗边标识一种实施方式示意图;

25.图4是本技术实施例提供的显示面板母板的分解示意图;

26.图5是本技术实施例提供的的阵列基板母板的结构示意图;

27.图6是本技术实施例提供的阵列基板母板的部分结构示意图;

28.图7是本技术实施例提供的阵列基板母板部分剖面结构示意图;

29.图8是本技术实施例提供的薄膜晶体管的一种剖面结构示意图;

30.图9是本技术实施例一提供的阵列基板母板部分剖面结构示意图;

31.图10是本技术实施例二提供的阵列基板母板部分剖面结构示意图;

32.图11是本技术实施例提供的阵列基板母板的制备方法流程图;

33.图12是本技术实施例提供的洗边标识的一种实施方式示意图;

34.图13是本技术实施例三提供的阵列基板母板部分剖面结构示意图;

35.图14是本技术实施例三中的的钝化保护层的一种剖面示意图;

36.图15是本技术实施例三中的钝化保护层的另一种剖面示意图。

37.附图标记说明

38.1000-显示面板母板;301-液晶模块;300-液晶层;200-彩膜基板母板;100-阵列基板母板;214-硅岛;213-像素电极;212-源/漏电极;211-栅极;123-虚拟焊盘的金属电极;122-细缝垂直对准虚拟焊盘;121-阵列基板测试虚拟焊盘;113-测试焊盘的金属电极;112-细缝垂直对准焊盘;111-阵列基板测试焊盘;91-欧姆接触层;90-半导体层;81-第三洗边标识;80-透明导电膜层;72-第二贯穿孔;71-第一贯穿孔;70-钝化保护层;61-第二洗边标识;60-第二金属层;50-第一金属绝缘层;41-第一洗边标识;40-第一金属层;30-基板;21-薄膜晶体管;20-阵列基板区域;12-虚拟焊盘;11-测试焊盘;10-测试区域;1-焊盘。

具体实施方式

39.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

40.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

41.请参阅图4,图4是本实施例提供的显示面板母板1000的分解示意图。显示面板可以是有机发光二极管(organic light-emitting diode,oled)显示面板,也可以是液晶显示面板(liquid crystal display,lcd),或者微发光二极管(micro-led)等显示面板。图4所示实施例的显示面板母板1000以液晶显示面板母板为例进行示意。

42.请再次参阅图4,显示面板母板1000包括阵列基板母板100,彩膜基板母板200和液晶层300。液晶层300位于阵列基板母板100和彩膜基板母板200之间。在本实施方式中,液晶层300中具有六个液晶模块301,液晶模块301之间同层间隔设置。在其他实施方式中,液晶模块301也可以只有一个。

43.下面结合附图,对本技术的具体实施方式进行详细描述。

44.实施例一:请参阅图5,图5是本技术实施例提供的的阵列基板母板的结构示意图。阵列基板母板100包括测试区域10和阵列基板区域20。测试区域10位于阵列基板区域20周边,测试区域10电连接阵列基板区域20。

45.阵列基板区域20与液晶层300的液晶模块301相对设置,阵列基板区域20中设有多个薄膜晶体管21(图未示),可以控制液晶模块301中的液晶分子转动。

46.本实施方式中,测试区域10和阵列基板区域20为矩形,测试区域10位于阵列基板区域20的短边(短边为矩形长度较短的那一条边)。在其他实施方式中,测试区域10也可以位于阵列基板的长边(长边为矩形长度较长的那一条边)。

47.阵列基板母板100的形状也为矩形,矩形的长为2250mm,宽为2600mm。在其他实施方式中,阵列基板母板100也可以为其他尺寸的矩形,或者其他的形状。

48.在本实施方式中,测试区域10数量与阵列基板区域20数量相等,一个测试区域10对应电连接一个阵列基板区域20。在其他实施方式中,测试区域10和阵列基板区域20数量也可以不相等。

49.请参阅图6,图6是本技术实施例提供的阵列基板母板100的部分结构示意图。测试区域10设有焊盘1和传输走线(图未示)。焊盘1通过传输走线电连接阵列基板区域20。在对阵列基板母板100施加外部信号时,焊盘1用于传导外界信号。在一种实施方式中,使用探针对阵列基板母板100施加电压信号,探针的针头与焊盘1接触,电压信号依次经过焊盘1、传输走线,最后到达阵列基板区域20。

50.焊盘1包括测试焊盘11与虚拟焊盘12。虚拟焊盘12为测试焊盘11的备用焊盘。即虚拟焊盘12的功能与测试焊盘11功能一致,只是在焊盘1传导外界信号时,虚拟焊盘12无外界信号接入,但给信号的探针针头仍与虚拟焊盘12接触。这样可以保持在给信号时,在垂直阵列基板母板100的方向,针头的活动范围基本一致,虚拟焊盘12无信号的针头不会过度靠近阵列基板母板100,以至于针头损坏或者测试区域10的结构被损坏。

51.测试焊盘11包括阵列基板测试(array test,att)焊盘111和细缝垂直对准(fine slit vertical alignment,fsa)焊盘112。在其他实施方式中,测试焊盘11也可以只包括att焊盘111和fsa焊盘112其中一种类型。

52.att焊盘111用于在阵列工艺中检查阵列基板区域20像素的电学不良,例如像素之间的短路。将测试信号通过att焊盘111和传输走线输入至阵列基板区域20,通过非接触式传感器探测对比阵列基板区域20不同位置像素表面电压差异和分布规律率,进而判断是否有电学不良。

53.att焊盘111可以包括扫描线奇数短路测试焊盘、扫描线偶数短路测试焊盘、数据线奇数短路测试焊盘、数据线偶数短路测试焊盘或公共电极短路测试焊盘中的一种或者多种。

54.fsa焊盘112用于在成盒工艺中的细缝垂直对准制程,将外接电压通过fsa焊盘112传输到阵列基板区域20,对阵列基板区域20施加电压的情况下施以uv光照射,使盒内单体产生聚合反应,液晶形成预倾角。

55.本实施方式中,虚拟焊盘12包括att虚拟焊盘121和fsa虚拟焊盘122。att虚拟焊盘121为att焊盘111的备用焊盘,fsa虚拟焊盘122为fsa焊盘112的备用焊盘。

56.在一种实施方式中,虚拟焊盘12也可以只包括att虚拟焊盘121和fsa虚拟焊盘122其中的一种。

57.在本实施方式中,att焊盘111与att虚拟焊盘121在阵列基板母板100的基准面上的投影为矩形,长为4020μm,宽为2020μm。在其他实施方式中,att焊盘111与att虚拟焊盘121在阵列基板母板100的基准面上的投影也可以为其他尺寸的矩形,或者其他形状。

58.在本实施方式中,fsa焊盘112与fsa虚拟焊盘122在阵列基板母板100的基准面上

的投影为矩形,长为5000μm,宽为2500μm。在其他实施方式中,fsa焊盘112与fsa虚拟焊盘122在阵列基板母板100的基准面上的投影也可以为其他尺寸的矩形,或者其他形状。

59.在本实施方式中,att焊盘111有4个,att虚拟焊盘121有5个。fsa焊盘112有4个,fsa虚拟焊盘122有2个。

60.在一种实施方式中,att焊盘111有15个,att虚拟焊盘121有7个。fsa焊盘112有16个,fsa虚拟焊盘122有9个。设计者可以根据需求灵活选择焊盘的类型、数量、形状与尺寸,本技术不做限定。

61.请参阅图7和图8,图7是本技术实施例提供的阵列基板母板100部分剖面结构示意图,图8是本技术实施例提供的薄膜晶体管21的一种剖面结构示意图。

62.请再次参阅图7,阵列基板母板100在朝向彩膜基板母板200的方向依次设有设置有基板30、第一金属层40、第一金属绝缘层50、第二金属层60、钝化保护层70、透明导电膜层80。其中,基板30、第一金属层40、第一金属绝缘层50、第二金属层60、钝化保护层70以及透明导电膜层80均从测试区域10延伸至阵列基板区域20。

63.透明导电膜层80为阵列基板母板100中最接近彩膜基板母板200的层结构。以基板30所在的平面作为阵列基板母板100的基准面。基板30由透明无色绝缘材料制成,这样有利于光线的透过阵列基板区域20。在本实施方式中,基板30为透明的玻璃材质,这样基板30的硬度较高。在其他实施方式中,基板30也可以是石英材质。

64.在阵列基板母板100的制程中,第一金属层40、第一金属绝缘层50、第二金属层60、钝化保护层70与透明导电膜层80均经过图案化处理,在基板30上的投影具有图案形状。

65.第一金属层40在阵列基板母板100不同位置可以形成不同的功能结构。在一种实施方式中,部分第一金属层40形成传输走线,外界测试信号经过测试焊盘11,然后由传输走线传递到阵列基板区域20。在一种实施方式中,部分第一金属层40形成薄膜晶体管21的栅极211。

66.第一金属层40的材料可以为铝钕合金(alnd)、铝(al)、铜(cu)、钼(mo)等单种金属,也可以为铝钕合金(alnd)、铝(al)、铜(cu)、钼(mo)其中任意多个组合成的复合金属。

67.第一金属绝缘层50位于第一金属层40与第二金属层60之间,起到绝缘作用。第一金属绝缘层50的材质可以为氮化硅、氧化硅以及氮氧化硅中的一种或多种。

68.第二金属层60在阵列基板母板100不同位置可以形成不同的功能结构。在一种实施方式中,部分第一金属层40形成测试焊盘11的金属电极113与虚拟焊盘12的金属电极123。在一种实施方式中,部分第二金属层60形成薄膜晶体管21的源/漏电极212。第二金属层60的材料可以为钼(mo)、铬(cr)等。

69.钝化保护层70位于第二金属层60与透明导电膜层80之间,对第二金属层60起到保护和绝缘作用。钝化保护层70在阵列基板区域20设有第一贯穿孔71,第一贯穿孔71在基板30的投影与薄膜晶体管21的源/漏电极212在基板30的投影至少部分错开。

70.在一种实施方式中,虚拟焊盘12在基板30的投影与钝化保护层70在基板30的投影错开,钝化保护层70围绕虚拟焊盘12设置。

71.透明导电膜层80在阵列基板母板100不同位置可以形成不同的功能结构。在一种实施方式中,部分透明导电膜层80可以为薄膜晶体管21中的像素电极213。像素电极213通过第一贯穿孔71与薄膜晶体管21的源/漏电极212电连接。

72.本实施方式中,透明导电膜层80的材质为氧化铟锡(indium tin oxide,ito)。透明导电膜层80的材质还可以含有氧化钨、氧化钼、氧化镍及氧化铌中的一种或者多种。

73.在一种实施方式中,薄膜晶体管21包括部分第二金属层60、部分钝化保护层70以及部分透明导电膜层80。薄膜晶体管21的部分第二金属层60位于钝化保护层70靠近基板30一侧,薄膜晶体管21的部分透明导电膜层80位于钝化保护层70远离基板30一侧。

74.请再次参阅图2,第一金属绝缘层50在基板30的投影与测试焊盘11和虚拟焊盘12在基板30的投影重合。第二金属层60在基板30的投影与测试焊盘11和虚拟焊盘12在基板30的投影重合。钝化保护层70在基板30的投影与测试焊盘11和虚拟焊盘12在基板30的投影错开,也就是说钝化保护层70围绕测试焊盘11和虚拟焊盘12设置。钝化保护层70分别与测试焊盘11的金属电极113边缘与虚拟焊盘12的金属电极123边缘接触。

75.请再次参阅图2,在传统技术中,测试区域10的测试焊盘11和虚拟焊盘12的位置均设置有透明导电薄膜层。钝化保护层70设有第二贯穿孔72,第二贯穿孔72在基板30的投影与测试焊盘11和虚拟焊盘12在基板30的投影错开。测试焊盘11和虚拟焊盘12位置的透明导电膜层80通过第二贯穿孔72分别连接测试焊盘11的金属电极113和虚拟焊盘12的金属电极123。透明导电膜层80通过第二贯穿孔72将外界的信号传导到测试焊盘11的金属电极113,金属电极113通过传输走线传导至阵列基板区域20。

76.请参阅图9,图9是本技术实施例一提供的测试焊盘11部分剖面结构示意图。在本实施方式中,透明导电膜层80在基板30的投影与测试焊盘11和虚拟焊盘12在基板30的投影错开。也就是说,本技术在测试焊盘11和虚拟焊盘12位置不设置透明导电膜层80。首先,由于测试焊盘11的金属电极113同样可以起到传导信号作用,在接入外界信号时,探针的针头直接与测试焊盘11的金属电极113接触,因此在测试焊盘11的金属电极113位置不设置透明导电膜层80不影响测试焊盘11的功能。同时,虚拟焊盘12并不需要接受外界信号,那么在虚拟焊盘12的位置不设置透明导电膜层80也不会影响虚拟焊盘12的功能。

77.并且,由于测试焊盘11和虚拟焊盘12位置不存在透明导电膜层80,那么测试区域10的透明导电膜层80面积减少。不容易因为测试焊盘11和虚拟焊盘12位置的透明导电膜层80面积较大,且透明导电膜层80边缘成膜的质量不佳,导致这部分透明导电膜层80容易在清洗程序中从焊盘1上脱落,从而导致产生碎屑,影响阵列基板母板100的成品合格率。

78.在一种实施方式中,透明导电膜层80在基板30的投影与测试区域10在基板30的投影错开。也就是说,阵列基板母板100在测试区域10均不设置透明导电膜层80。这样,进一步降低了透明导电膜碎屑的发生概率。

79.上文结合相关附图具体介绍了阵列基板母板100的一种实施方式的结构。下文将结合相关附图再具体介绍阵列基板母板100另外一种实施方式的结构。

80.实施例二:与第一种实施方式相同的技术内容不再赘述:请参阅图10,图10是本技术实施例二提供的焊盘1部分剖面结构示意图。阵列基板母板100包括测试区域10和阵列基板区域20。测试区域10设有焊盘1,焊盘1包括测试焊盘11与虚拟焊盘12。

81.在本实施方式中,透明导电膜层80在基板30的投影与焊盘1在基板30的投影部分错开,可以理解地是,本实施方式中的透明导电膜层80的设置包括但不限于以下几种方案:

82.在一种实施方式中,透明导电膜层80在基板30的投影也可以与虚拟焊盘12在基板30的投影错开,透明导电膜层80在基板30的投影与测试焊盘11在基板30的投影重合。这样,

在测试焊盘11位置设置透明导电膜层80,透明导电膜层80不仅可以起到传导信号的作用,还可以保护测试焊盘11的金属电极113不受腐蚀,避免金属电极因为受到腐蚀而影响其导电性能。

83.在一种实施方式中,透明导电膜层80在基板30的投影还可以与虚拟焊盘12在基板30的投影部分错开。例如,透明导电膜层80在基板30的投影与att虚拟焊盘121在基板30的投影错开,透明导电膜层80在基板30的投影与fsa虚拟焊盘122在基板30的投影重合。

84.在一种实施方式中,透明导电膜层80在基板30的投影可以与测试焊盘11在基板30的投影完全错开,透明导电膜层80在基板30的投影与虚拟焊盘12在基板30的投影重合。

85.在一种实施方式中,透明导电膜层80在基板30的投影还可以与测试焊盘11在基板30的投影部分错开。

86.上述方案均可以减少在测试区域10的透明导电膜层80的面积,有利于减少透明导电膜碎屑的产生。并且,由于透明导电膜层80厚度较小,因此去除部分焊盘1的透明金属膜层,在探针传递外界信号时,扎针的高度总体变化不大。在一种实施方式中,透明导电膜层80厚度为50nm。

87.请参阅图11,图11是本技术实施例提供的阵列基板母板100的制备方法流程图。阵列基板母板100的制备方法包括以下步骤:

88.步骤s100:在基板的第一区域内形成测试焊盘11和虚拟焊盘12,以及在基板的第二区域形成薄膜晶体管21。

89.步骤s101:于基板30表面形成第一金属层40。

90.具体地,于基板30表面形成待处理第一金属层。经第一次图案化处理,形成第一金属层40。其中,部分第一金属层40在基板30的第二区域形成薄膜晶体管21的栅极211。部分第一金属层40在基板30的第一区域形成传输走线。

91.步骤s102:于第一金属层40远离基板30的表面形成第一金属绝缘层50。

92.具体地,第一金属层40远离基板30的表面形成待处理第一金属绝缘层。经第二次图案化处理,形成第一金属绝缘层50。

93.步骤s103:于第一金属绝缘层50远离基板30的一侧形成第二金属层60。

94.具体地,于第一金属绝缘层50远离基板30的一侧形成待处理第二金属层,经第三次图案化处理,形成第二金属层60。部分第二金属层60形成薄膜晶体管21的源/漏电极212。部分第二金属层60形成测试焊盘11的金属电极113与虚拟焊盘12的金属电极123。

95.步骤s104:于第二金属层60远离基板30的表面形成钝化保护层70。

96.具体地,于第二金属层60远离基板30的表面形成待处理钝化保护层。经第四次图案化处理,形成钝化保护层70。钝化保护层覆盖薄膜晶体管,钝化保护层70在基板30的投影与阵列基板测试虚拟焊盘和细缝垂直对准虚拟焊盘在基板30的投影错开。

97.步骤s200:于钝化保护层70远离基板30的表面形成透明导电膜层80。

98.具体地,于钝化保护层70远离基板30的表面形成待处理透明导电膜层,待处理透明导电膜层覆盖阵列基板测试焊盘11、虚拟焊盘12以及薄膜晶体管;

99.经第五次图案化处理,形成透明导电膜层80。部分透明导电膜层80形成薄膜晶体管21的像素电极213。

100.其中,在步骤s102和步骤s103之间还包括:

101.步骤

①

:于第一金属绝缘层50远离基板30的一侧形成待处理半导体层。经图案化处理,请再次参阅图6,形成半导体层90。

102.步骤

②

:于半导体层90远离基板30的一侧形成待处理欧姆接触层。经图案化处理,再次参阅图6,形成欧姆接触层91。在薄膜晶体管21位置的半导体层90与欧姆接触层91形成薄膜晶体管21的硅岛214。

103.请参阅图3,在传统工艺中,在步骤s101中还包括:在待处理第一金属层设有第一洗边标识41。第一洗边标识41用于在第一次图案化处理时,用于去除不需要的待处理第一金属层。

104.在步骤s103中还包括:在待处理第二金属层形成第二洗边标识61。第二洗边标识61用于在第三次图案化处理时,用于去除不需要的待处理第二金属层。

105.请参阅图12,图12是本技术实施例提供的洗边标识的一种实施方式示意图。与传统的洗边标识(如图3所示)相比,本技术在步骤s200中,在待处理透明导电膜层增设第三洗边标识81,第三洗边标识81用于在第五次图案化处理时,用于去除不需要的待处理透明导电膜层。

106.在一种实施方式中,第三洗边标识81在基板30的投影与测试焊盘11和虚拟焊盘12在基板30的投影重合,第三洗边标识81用于去除测试焊盘11和虚拟焊盘12上的待处理透明导电膜层。经第五次图案化处理,形成透明导电膜层80。形成的透明导电膜层80在基板30的投影与测试焊盘11和虚拟焊盘12在基板30的投影错开。最后得到本技术实施例一中的阵列基板母板100。

107.在一种实施方式中,第三洗边标识81在基板30的投影与虚拟焊盘12在基板30的投影重合,第三洗边标识81在基板30的投影与测试焊盘11在基板30的投影错开,第三洗边标识81用于去除虚拟焊盘12上的待处理透明导电膜层。形成的透明导电膜层80在基板30的投影与虚拟焊盘12在基板30的投影错开。透明导电膜层80在基板30的投影与测试焊盘11在基板30的投影重合。得到本技术实施例二中的一种阵列基板母板100。

108.在一种实施方式中,第三洗边标识81在基板30的投影与att焊盘111和fsa虚拟焊盘122在基板30的投影重合。同时,第三洗边标识81在基板30的投影与fsa焊盘112和att虚拟焊盘121在基板30的投影错开。第三洗边标识81用于去除att焊盘111和fsa虚拟焊盘122上的待处理透明导电膜层。形成的透明导电膜层80在基板30的投影与att焊盘111和fsa虚拟焊盘122在基板30的投影错开。透明导电膜层80在基板30的投影与fsa焊盘112和att虚拟焊盘121在基板30的投影重合。得到本技术实施例二中的一种阵列基板母板100。

109.在一种实施方式中,第三洗边标识81也可以设置于除测试焊盘11和虚拟焊盘12以外的区域,用于去除其他位置不需要的待处理透明导电膜层。

110.在一种实施方式中,第一洗边标识41、第二洗边标识61和第三洗边标识81均为具有均匀刻度的直线。刻度可以帮助设备更准确识别曝光位置,避免过度曝光。在一种实施方式中,还可以根据剩余曝光后剩余刻度的长度,判断曝光效果。

111.在一种实施方式中,第一洗边标识41、第二洗边标识61和第三洗边标识81也可以为其他形状。另外,第一洗边标识41、第二洗边标识61和第三洗边标识81三者的形状可以一样,也可以不一样。

112.第三洗边标识81的数量可以为多个,可以根据需求灵活设置。第一洗边标识41、第

二洗边标识61和第三洗边标识81三者的数量可以一样,也可以不一样。

113.在其他实施方式中,第一洗边标识41、第二洗边标识61和第三洗边标识81也可以仅设置其中的一个或者两个,还可以第一洗边标识41、第二洗边标识61和第三洗边标识81均不设置。

114.阵列基板母板100经过成盒工艺之后得到显示面板母板1000。显示面板母板1000经过切割,得到显示面板。

115.在一种实施方式中,测试区域10在基板30的投影与第一区域重合,阵列基板区域20在基板30的投影与第二区域重合。

116.实施例三:请参阅图13,图13是本技术实施例三提供的阵列基板母板100部分剖面结构示意图。步骤s104形成的钝化保护层70在基板30的投影与测试焊盘11的金属电极113与虚拟焊盘12的金属电极123在基板30的投影部分重合,同时透明导电膜层80在基板30的投影与测试焊盘11的金属电极113与虚拟焊盘12的金属电极123在基板30的投影重合。

117.也就是说,在测试焊盘11和虚拟焊盘12位置设置钝化保护层70。增加的这部分钝化保护层70可以起到加强这透明导电膜层80与测试焊盘11的金属电极113与虚拟焊盘12的金属电极123之间粘性的作用,这样测试焊盘11和虚拟焊盘12的透明导电膜层80不容易在清洗程序中,在毛刷以及气流水流的作用下从测试焊盘11和虚拟焊盘12上脱落,从而导致产生碎屑,可以提高阵列基板母板100的成品良率。同时,在测试焊盘11和虚拟焊盘12位置的钝化保护层70设有第三贯穿孔,这样透明导电膜层80可以通过第三贯穿孔与测试焊盘11的金属电极113与虚拟焊盘12的金属电极123接触,不影响外界信号的传输,还能保护金属电极不被腐蚀。

118.请参阅图14和图15,图14是本技术实施例三中的的钝化保护层70的一种剖面示意图,图15是本技术实施例三中的钝化保护层70的另一种剖面示意图。测试焊盘11和虚拟焊盘12位置的钝化保护层70可以呈网格状(请参阅图14),还可以为间隔排列的斜条纹状(请参阅图15)。

119.以上,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内;在不冲突的情况下,本技术的实施例及实施例中的特征可以相互组合。因此,本技术的保护范围应以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。